## Ruprecht-Karls-Universität Heidelberg Institute of Computer Science Research Group Parallel and Distributed Systems

#### Masterthesis

# Model and simulation of power consumption and power saving potential of energy efficient cluster hardware

Name Timo Minartz Student number 2676380

Supervised by Julian M. Kunkel, Prof. Thomas Ludwig

Date of submission | Heidelberg, August 27, 2009

Timo Minartz

Matrikelnummer: 2676380

Diese Masterarbeit ist von mir selbstständig angefertig und verfasst. Es sind keine anderen als die angegebenen Quellen und Hilfsmittel benutzt worden. Weiter wurden die Grundsätze und Empfehlungen "Verantwortung in der Wissenschaft" der Universität Heidelberg beachtet.

Unterschrift

Heidelberg, den 27. August 2009

## Danksagung

Herrn Prof. Ludwig danke ich für die Übernahme der Betreuung der Arbeit und seine Hilfestellungen und nützlichen Anregungen.

Entscheidend zum Gelingen dieser Arbeit beigetragen hat Julian Kunkel. Er hat mit mir fast täglich zusammengearbeitet und mich mit seinen Ideen, konstruktiven Beiträgen und seinem Engagement umfangreich unterstützt.

Stephan Krempel möchte ich für seine Hilfe bei der Nutzung der ResourceUtilizationTracingLibrary und der PowerTracingLibrary danken.

Jörg, Michael und Philipp möchte ich für das Korrekturlesen und den damit verbundenen Änderungsvorschlägen danken.

Der größte Dank gilt meinen Eltern und Großeltern, die mir das Studium in Heidelberg und Aachen überhaupt erst ermöglicht haben. Sie haben mir neben ihrer großzügigen finanziellen Unterstützung auch immer moralisch zu Seite gestanden.

Besonderer Dank gilt Isabell, für all ihre Geduld mit mir.

## **Abstract**

In the last years the power consumption of high performance computing clusters has become a growing problem because number and size of cluster installations raised and still is raising. The high power consumption of the clusters results from the main goal of these clusters: High performance. With a low utilization the cluster hardware consumes nearly as much energy as when it is fully utilized. In these low utilization phases the cluster hardware can theoretically turned off or switched to an lower power consuming mode.

In this thesis a model is designed to estimate the power consumption of the hardware with and without energy saving mechanism. With the resulting software it is possible to estimate the cluster power consumption for different configurations of a parallel program. Further energy aware hardware can be simulated to determine an upper bound for energy savings without performance leakage.

The results show that is a great energy saving potential for energy aware hardware even in high performance computing. This potential should motivate research in mechanism to control the energy aware hardware in high performance clusters.

## **Contents**

| 1. | Introduction                                             | 6               |  |  |  |  |  |  |  |  |

|----|----------------------------------------------------------|-----------------|--|--|--|--|--|--|--|--|

|    | 1.1. Definitions                                         |                 |  |  |  |  |  |  |  |  |

|    | 1.2. High Performance Computing Clusters                 |                 |  |  |  |  |  |  |  |  |

|    | 1.3. Project Goals                                       | 9               |  |  |  |  |  |  |  |  |

| 2. | Energy Aware Hardware                                    |                 |  |  |  |  |  |  |  |  |

|    | 2.1. Overview of Hardware                                | 11              |  |  |  |  |  |  |  |  |

|    | 2.2. Managing of Energy Aware Hardware with ACPI         | 13              |  |  |  |  |  |  |  |  |

|    | 2.3. Analysis of Energy Saving Potential                 |                 |  |  |  |  |  |  |  |  |

| 3. | Estimation of Cluster Power Consumption                  | 16              |  |  |  |  |  |  |  |  |

|    | 3.1. Model                                               |                 |  |  |  |  |  |  |  |  |

|    | 3.2. Determination of Component Power Consumption        |                 |  |  |  |  |  |  |  |  |

|    | 3.3. Power Consumption Estimation Strategies             |                 |  |  |  |  |  |  |  |  |

|    | 3.3.1. Simple Strategy                                   |                 |  |  |  |  |  |  |  |  |

|    |                                                          | $\frac{20}{20}$ |  |  |  |  |  |  |  |  |

|    | •                                                        |                 |  |  |  |  |  |  |  |  |

|    | 3.3.3. Approach Strategy                                 |                 |  |  |  |  |  |  |  |  |

|    | 3.3.4. Multiple State Strategy                           |                 |  |  |  |  |  |  |  |  |

|    | 3.4. Example Power Estimation                            | 23              |  |  |  |  |  |  |  |  |

| 4. | Software Design                                          | 26              |  |  |  |  |  |  |  |  |

|    | 4.1. Software environment                                | 26              |  |  |  |  |  |  |  |  |

|    | 4.2. Stresstest                                          | 26              |  |  |  |  |  |  |  |  |

|    | 4.3. Implementation                                      | 27              |  |  |  |  |  |  |  |  |

|    | 4.3.1. Interfaces                                        | 27              |  |  |  |  |  |  |  |  |

|    | 4.3.2. Model                                             | 28              |  |  |  |  |  |  |  |  |

|    | 4.3.3. Tests and Guidance                                | 29              |  |  |  |  |  |  |  |  |

| 5  | Assessing Energy Efficiency of Jacobi PDE Solver         | 30              |  |  |  |  |  |  |  |  |

| J. | 5.1. Cluster Environment                                 |                 |  |  |  |  |  |  |  |  |

|    | 5.2. Description of Jacobi PDE Solver                    |                 |  |  |  |  |  |  |  |  |

|    | 5.3. Methodology                                         |                 |  |  |  |  |  |  |  |  |

|    | 30                                                       |                 |  |  |  |  |  |  |  |  |

|    | 5.4. Experiments                                         |                 |  |  |  |  |  |  |  |  |

|    | 5.4.1. Fixed Problem Size                                |                 |  |  |  |  |  |  |  |  |

|    | 5.4.2. Increasing Problem Size with Number of Nodes      | 37              |  |  |  |  |  |  |  |  |

|    | 5.4.3. Communication Intensive vs. Calculation Intensive | 39              |  |  |  |  |  |  |  |  |

|    | 5.4.4. Non-Cached I/O                                    | 41              |  |  |  |  |  |  |  |  |

| 6. | Evaluation                                               | 43              |  |  |  |  |  |  |  |  |

|    | 6.1. Component Power Consumption                         | 43              |  |  |  |  |  |  |  |  |

|    | 6.2. Model Verification                                  | 47              |  |  |  |  |  |  |  |  |

|    | 6.3. Strategies Applied to Program Runs                  | 49              |  |  |  |  |  |  |  |  |

|    | 6.4. Energy Efficient Sleeping                           | 56              |  |  |  |  |  |  |  |  |

|    | 6.5. Efficient Devices                                   | 57              |  |  |  |  |  |  |  |  |

| 7  | Summary, Conclusion and Future Work                      | 60              |  |  |  |  |  |  |  |  |

| ٠. | Summary, Conclusion and Future Work                      | UU              |  |  |  |  |  |  |  |  |

| Α. | Appendix                                                 | 63              |  |  |  |  |  |  |  |  |

## 1. Introduction

In the last years the power consumption of high performance computing clusters has become a growing problem because number and size of cluster installations raised and still is raising. In times of "Green IT" the installations and especially their power consumption have to be legitimated.

For example the fastest public and official listed cluster has a peak power consumption of about 2483.47 kW (see table 1.2, discussed in section 1.2). If this cluster reaches a power saving of 1 %, this results in power savings of about 200 MWh per year (see equation 1.1). Assuming  $0.05 \in \text{per kWh}^{-1}$  these are savings of about  $10.000 \in \text{year}$ . This saving is equivalent to about 108 t CO<sub>2</sub> produced when generating the energy in a power plant. The same amount of CO<sub>2</sub> is produced when driving about  $630.000 \, \text{km}$  by car <sup>2</sup>. For the second listed cluster these values have to be triplicated based on the higher peak power consumption of this specific cluster.

$$2483.47 \text{ kW} * \frac{1}{100} * 24 \text{ h} * 365$$

$\approx 596.03 \text{ kWh per day} * 365$

$\approx 217.55 \text{ MWh per year}$  (1.1)

The high power consumption of the clusters results from the main goal of these clusters: High performance. This goal has impact on the hardware, the worst case cooling scenarios and the resulting energy consumption. If these clusters are fully utilized, this is maybe the most energy efficient way to get this calculation power. But with a low utilization the hardware consumes nearly as much energy as when it is fully utilized. Based on this relationship between peak and idle power consumption of components the loss of energy can take place. Of course it is tried to eliminate these low utilization phases, but they still arise due to hardware bottlenecks, load balancing problems and problem specific behavior.

In these low utilization phases the cluster hardware can theoretically turned off or switched to an lower power consuming mode if the component supports this feature.

In chapter 2 an overview of energy aware hardware in today's desktop and server systems is given to evaluate possible hardware for an energy efficient cluster.

Based on the approach to switch off unused hardware components a model is developed to estimate the power consumption of the hardware with and without energy saving mechanism in chapter 3. With "trace files" containing information about the utilization on the one hand and the knowledge of the components utilization based power consumption on the other hand the power consumption of each hardware component can be estimated. The component utilization based power consumption can be gained from experimental setups described in this work.

The software resulting from this model is described in chapter 4.

Chapter 5 assesses various parallel program runs on the cluster of the Research Group Parallel and Distributed Systems at the University of Heidelberg. Each program run and the associated measured power consumption is analyzed in consideration of the configuration, the run time and the power consumption.

With these program runs the model and the resulting software are evaluated in chapter 6, the measured power consumption values are compared with the estimated ones of the software. Further energy aware hardware is simulated to determine upper bounds for energy savings without performance leakage. This simulation is based on several strategies for switching to low power consuming

$<sup>^{1}</sup>$ a normal household price is about 0.15€, but cluster operators get special prices

<sup>&</sup>lt;sup>2</sup>based on average emission of vehicle registrations in Germany 2007, http://www.watt.de/CO2\_Rechner.aspx, last checked on August 27, 2009

modes in low utilization phases. The estimated power consumption under usage of the different strategies is analyzed based on different program and hardware configurations to show the potential of energy savings.

#### 1.1. Definitions

Table 1.1.: Definitions

| Name                       | Unit                | Description                                                                                                                                                                   |

|----------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Energy                     | J                   | 1 J = 1 kg m <sup>2</sup> s <sup>-2</sup> , one joule is defined as the amount of work done by a force of one newton moving an object through a distance of one meter [Phy04] |

| Power                      | W                   | V A, watt, equivalent to energy per second (J s <sup>-1</sup> ). Meaning the rate at which energy is generated and consumed [Phy04]                                           |

| Energy                     | $\operatorname{Wh}$ | 1  Wh = 3600  Ws = 3600  J  [Phy04]                                                                                                                                           |

| Thermal design power (TDP) | W                   | represents the average maximum power the cooling system in a computer is required to dissipate                                                                                |

| Performance                | Flops               | Floating point operations per second [Top]                                                                                                                                    |

| Power Efficiency           | Flops / W           | Power efficiency measured in performance per power [Gre]                                                                                                                      |

| Speedup                    | _                   | $t_1 t_n^{-1}$ , $t_1$ = run time for one process, $t_n$ = run time for $n$ processes [Lud08a]                                                                                |

## 1.2. High Performance Computing Clusters

This chapter gives an introduction into cluster computing. It starts with the formal definition followed by some applications to motivate the building of cluster systems. Further the problem of energy consumption and some methods to resolve it are described.

Cluster computing is defined as the usage of lots of connected and homogeneous hardware components for high performance computing (HPC) [Lud08a]. In earlier days, clusters were built by connecting normal desktop PCs by a network. These clusters are called Beowulf-Clusters. Each of these PCs is called cluster node. The nodes have common hardware components like CPU, main memory (RAM), hard disks, network cards (NIC), main board etc. Because a cluster usually is controlled by a master node over network, the other nodes do not have Human Interface Devices (HID) like keyboard, mouse or monitor. To manage and monitor the cluster and its components an operating system (usually UNIX based) and cluster software is required which isn't described in detail here.

Today high performance clusters are mainly built by special business units of different companies like HP, IBM, Cray and SGI. An overview of high performance cluster systems is given by the organization Top500.org [Top]. This organization biannually ranks clusters from all over the world by performing a benchmark called LINPACK and publishes the results at the International Supercomputing Conference <sup>3</sup>. The benchmark used in LINPACK is to solve a dense system of linear equations [Top]. Based on this specific calculation and the time needed to perform this task performance is calculated in Flops. The fastest system of the June 2009 list reaches 1105000 GFlops while normal desktop computers reach between 1 and 8 GFlops (mainly dependent on the CPU).

<sup>&</sup>lt;sup>3</sup>http://www.supercomp.de, last checked on August 27, 2009

Implied by the LINPACK benchmark HPC systems are mainly used for solving complex numerical problems. These problems are native to many domains of science like fluid mechanics, bio-informatics, physics, climate research etc.

For getting program code to run on a cluster environment, the original algorithm (called sequential program code) has to be parallelized. On these high performance clusters usually techniques such as MPICH <sup>4</sup>, OpenMP <sup>5</sup> or a combination of both (Hybrid Programming) are used. While MPI (Message Passing Interface) communicates as the name implies with sending messages to other processes possibly located on other nodes (distributed memory), OpenMP is used for communication among threads in the same address space (shared memory, mainly the same node).

To parallelize code for a high performance cluster the main challenge apart from producing a correct program is to create a scalable program. In this context scalable means that incrementing the number of nodes or processes proportionally decreases the run time of the algorithm. Scalability of some parallel algorithm is limited based on the particular sequential algorithm. But if an algorithm is scalable in general, the programmer's challenge is to locate and minimize waiting times resulting from communication or hardware bottlenecks. To understand a parallel program (especially its communication schema) and to locate the bottleneck of the program its code can be instrumented to generate a trace file. This trace file contains information about the communication schema of the processes, hardware usage etc. By analyzing this file potential bottlenecks (software and/or hardware based) can be identified and further analyzed.

Because of the performance driven development of the hardware (and the software) the energy consumption of the hardware has become a real problem in the last years. This is mainly based on the high power density. For example Intel's Pentium-I processor (1993) has a maximal power consumption of  $14\,\mathrm{W}$  at a chip size of  $292\,\mathrm{mm}^2$  and a resulting power density of about  $4.8\,\mathrm{W/cm}^2$ . Intel's Itanium2 processor (Fanwood, 2004) has a maximal power consumption of  $130\,\mathrm{W}$ , a chip size of  $374\,\mathrm{mm}^2$  and a resulting power density of about  $34.7\,\mathrm{W/cm}^2$  (about 7 times higher).

Out of this, not only the direct energy consumption of hardware has to be considered, the cooling of the hardware must be regarded as well. The power fed into the hardware results in heat which has to be dissipated. Because of the space requirement of a cluster installation which might be a few hundred square meters these rooms have to be fully air-conditioned. This results in a power consumption (for the Top 3 installations, see table 1.2) between 2 and 7 MW <sup>6</sup>. Interestingly, there is a big difference between the energy consumption of the three systems. While the peak performance differs in a range of 400 TFlops, especially the first and the second ranked systems differ in peak performance in about 70 TFlops (about 5 %). But the power consumption differs in about 4.5 MW (about 280 %).

**Table 1.2.:** Abstract of TOP500 List (June 2009) for supercomputers [Top]. The power value is given in kW for the entire system, the  $R_{peak}$  value is given in TFlops (10<sup>12</sup> floating point operations per second).

| Rank | Computer   | Vendor    | Year | Cores  | $ m R_{peak}$            | Peak power           |

|------|------------|-----------|------|--------|--------------------------|----------------------|

| 1    | Roadrunner | IBM       | 2008 | 129600 | $1456.70\mathrm{TFlops}$ | $2483.47\mathrm{kW}$ |

| 2    | Jaguar     | Cray Inc. | 2008 | 150152 | $1381.40\mathrm{TFlops}$ | $6950.60\mathrm{kW}$ |

| 3    | JUGENE     | IBM       | 2009 | 294912 | $1002.70\mathrm{TFlops}$ | $2268.00\mathrm{kW}$ |

To compare installations on the basis of their power consumption and their performance, there is another ranking called Green500 [Gre]. The installations are ranked by MFlops/W to get the performance in relation to the power consumption (power efficiency). In table 1.3 the top 3 systems from table 1.2 and the first rank system are listed. It is interesting to see that the first system in the

<sup>&</sup>lt;sup>4</sup>http://www.mcs.anl.gov/research/projects/mpi/mpich1, last checked on August 27, 2009

<sup>&</sup>lt;sup>5</sup>http://openmp.org/wp, last checked on August 27, 2009

<sup>&</sup>lt;sup>6</sup>enough to sustain a city of between 8,000 to 28,000 inhabitants

Green500 list nearly reaches 100 MFlops more per watt than the first system in the Top500 list. The aforementioned difference between the two first ranked systems in the Top500 list is clearly reflected in the Green500 list: The Jaguar system (with the highest peak power consumption of the system listed in table 1.2) only ranks at position 90.

**Table 1.3.:** Abstract of Green500 List (June 2009) for supercomputers [Gre]. The total power value is given in kW for the entire system, the efficiency is given in MFlops (10<sup>6</sup> floating point operations per second) per watt.

| Rank | Computer    | Efficiency                | Peak power           | TOP500 Rank |

|------|-------------|---------------------------|----------------------|-------------|

| 1    | BladeCenter | $536.24\mathrm{MFlops/W}$ | $34.63\mathrm{kW}$   | 422         |

| 4    | Roadrunner  | $444.94\mathrm{MFlops/W}$ | $1456.70\mathrm{kW}$ | 1           |

| 18   | JUGENE      | $363.98\mathrm{MFlops/W}$ | $1002.70\mathrm{kW}$ | 3           |

| 90   | Jaguar      | $152.36\mathrm{MFlops/W}$ | $1381.40\mathrm{kW}$ | 2           |

But the trend to save energy (and lower the costs) is not new to big computer system installations. Datacenters for example are cluster installations with more general purpose to store and analyze data (for example Google stores information about search queries in large datacenters) or to maintain different servers (for example an Internet service provider, ISP). These datacenters have a commercial use and have to be economically in their costs. Due to this, the performance is not the primary goal (as in HPC). Also the different usage of the cluster allows to develop energy saving mechanisms. For example a data center of an ISP which rents web servers. Each web server is realized as a virtual machine and multiple virtual machines are located on one node. This can be done because web servers often are under utilized and do not need the performance of a whole node. If a server needs more performance, the virtual machine can migrate to another (yet unused) node. If the performance is not necessary, the unused node can be turned off to conserve energy.

Another approach is to use the waste heat. This heat can be used to heat water (e.g. for a heating system or a swimming pool). It is also possible to use the environment for cooling (for example cold winter air) instead of mechanical cooling.

Some of these concepts are already applied to HPC, but with savings in the energy consumption of the hardware these concepts can be improved.

## 1.3. Project Goals

This project's main goal is to motivate further research of energy saving mechanism in high performance computing environments. The usage of energy efficient components have been rejected in reference to the possible performance loss and the higher acquisition costs. But it is possible that the increased calculation time due to reduced performance results in a even better energy efficiency of the hardware.

The approach based on reducing the component idle power consumption affects the total power consumption twice: First the component power consumption is decreased and second less lost heat has to be dissipated. The usage of hardware that support different working modes for high and low utilization times promises power savings with small or even without performance loss if used in the right way.

This work is a first step with the first intention to assess the energy consumption of different cluster components and program configurations.

The second intention is to simulate the power consumption and possible power savings with and without reducing performance for each component to motivate further research of the mentioned ideas.

For this purpose a model is designed which calculates the power consumption for each component based on the component's utilization. Further the components power consumption at zero utilization (idle) and full utilization (load) is used to estimate the power consumption. The information about the utilization is gained from trace files, while the zero and full utilization values are gained from experiments.

With different strategies it is possible to estimate the power consumption with different hardware and power saving characteristics.

The estimated power consumption must be interpreted as an upper bound for power savings that can be reached with energy aware hardware. Based on the specific program traces the monetary evaluation of these hardware components is possible: The energy savings can be compared with the acquisition costs of the specific hardware.

This is interesting for clusters built for different application types, because the different types have different utilization profiles. For example some applications are communication intensive (high utilization of the network card), some other applications are IO intensive (high utilization of the disk subsystem). With different utilization profiles from different workload some resources aren't fully utilized (for example the performant disk subsystem for the communication intensive application). For clusters built up for one application type the hardware is usually optimized for this workload to prevent idle times.

Especially for waiting times resulting from hardware bottlenecks and/or problem specific behavior the estimation of the power consumption is useful. Phases with partial utilization of specific hardware devices can be identified. With modification of the parallel algorithm the device utilization can be changed to phases with full and zero utilization respectively to make efficient device power state changes possible.

The power savings can be monetary calculated for the specific program, configuration and the hardware. This has advantages for the cluster operator, but also advantages for the hardware vendor and further researches.

## 2. Energy Aware Hardware

This chapter gives an overview of energy aware hardware components which can be used to build up an energy efficient cluster. For this purpose, the energy saving potential of each component is discussed by analyzing several research approaches.

Energy aware hardware in the context of this thesis is hardware, that supports different operating modes, each of these with a different power consumption. When decreasing the power consumption from one mode to another mode, some functions of the specific component must be changed or turned off to save energy. To reuse these functions the component must switch back to the previous mode. This switching can result in latency and additional energy consumption, because the hardware must be reactivated (e.g. spin up the hard disk). This trade-off has to be considered when using energy aware hardware. The concrete capabilities of hardware components are discussed in the following section.

#### 2.1. Overview of Hardware

#### **CPU**

The analysis starts with the most power consuming component, the Central Processing Unit (CPU). Because the CPU consumes between 15 % (in idle mode) and 50 % (CPU load) of a mobile device's power [MV04], a lot of research has already been done to reduce the energy consumption of this component. But until now, the developed energy saving mechanisms are not used in high performance cluster hardware because of potential performance loss.

The energy consumption of a CPU depends on several factors: The frequency f, the core voltage V, the level of chip activity  $\alpha$  and a factor C dependent on the capacitance of the chip [MV04]. Equation 2.1 describes the power consumption of a CPU.

$$P_{\text{CPU}} = \alpha \, C \, V^2 \, f \tag{2.1}$$

The linear effect of the "level of chip activity"  $\alpha$  shows that the CPU still consumes lots of energy, even if not utilized (because the chip is still active and  $\alpha$  is not zero). This is the main problem of components without energy saving mechanisms. The core voltage V effects the power quadratically, while the other factors only have a linear effect. Further reducing the core voltage results in a reduced frequency. Out of this, the main approach is to reduce the core voltage (and so the frequency) in phases of low utilization. These technologies are called "SpeedStep Technology" (for Intel processors) and "Cool'n'Quiet" (for AMD processors). To manage the energy consumption without lowering the frequency, today's processor hardware components can be switched on and off with fine granularity. This way it is possible to disable whole cores (in case of multicore processors) or core functions, such as first/second level cache or Hyperthreading. Intel already introduced a technology to manage the processor's energy consumption at this level called "Intelligent Power Capability". Newer desktop, server and especially notebook processors provide the introduced energy saving features.

#### Disk

In today's computer systems the hard disk drive is a moderate power consuming components [MV04]. But in idle mode (drive not serving any requests) the platters are still spinning. This leads to a great potential for energy saving when platters are spinned down for idle times. Servers with a low mean utilization do not use the disks frequently and the platters could spin down. This is one of the most popular approaches, because the angular velocity  $\omega$  of the motor has a quadratic effect on

the power consumption (see equation 2.2,  $K_e$  is the motor voltage constant and R is the motor resistance) [GSKF03].

$$P_{\text{disk}} = \frac{K_e^2 \,\omega^2}{R} \tag{2.2}$$

Today's hard disks support several modes to reduce energy consumption: Unloading the heads, parking the heads, reducing the RPM (revolutions per minute) when idle and powering of the motor. Reducing the RPM only is possible if the heads are parked in the parking zone because of the danger of head crashes.

The approach of DRPM (Dynamic Rotations Per Minute) [GSKF03] is a method explored for dynamically controlling the speed at which drives spin. With this approach, energy is saved while preserving high availability (because writing is still possible at lower RPM). But today's hard drives do not offer these multi-speed operating modes.

While most approaches try to reduce the power consumption of the mechanical parts of the disk, there also is an approach to reduce the power consumption of the electrical parts [HSRJ08]. This paper shows that the energy required to access data is affected by physical location on a drive. Also, the size of data transfers has measurable effects on power consumption.

#### Network

Research about the power consumption of the Internet [GS03] and Ethernet LANs [GS07b] shows that big networks like the Internet or even campus LANs have a low mean utilization, while network components like network interface cards and switches consume as much energy as when under load. Because of this, some research has been made in order to reduce power consumption of network interface cards and corresponding switches. Gupta and Singh designed a Dynamic Ethernet Link Shutdown (DELS) algorithm leading to significant benefits in energy savings with little noticeable impact on packet loss or delay [GS07a]. They also published an approach to use the low-power modes of network interfaces [GS07b]. This approach uses hardware that is designed to change link rate for saving power in battery-operated devices. They developed an algorithm to change the link rate if the link is idle or under-utilized. Another approach is to design a network interface card containing a secondary processor and an Embedded OS including the networking stack and a flash storage [AHC+09]. This NIC can handle network applications while the other components such as main CPU etc. are asleep. Under use of application-level triggers the host wakes up for specified applications or packets.

On the other hand research has been made for power management in LAN switches [GGS04]. This work examines methods to reduce the power consumption in switches dynamically using low-power states depending upon traffic activity at each interface and analyzes the impact of sleeping on layer 2 protocols (example for a layer 2 protocol: the Address Resolution Protocol (ARP)). Another approach is to manage the power consumption of network devices with power consumption policies. By monitoring the power consumption of "EnergyWise" devices it is possible to manually select different energy policy settings to start managing the network's energy consumption [Aud09].

#### Memory

Main memory of desktop or server systems often is optimized for performance. Out of this, at low utilization times the main memory only is partially used. Moona et al. [MCH07] analyzed the effect of changing memory performance for different applications and implemented Dynamic Memory Switching for Linux. A kernel daemon migrates pages to different banks (fixed sized sections of Rambus RDRAM modules) and turns unused banks off. Switching a bank off means that a bank switches from Active to Nap, similarly bank on means switching from Nap to Active (see table 2.1). The Nap state is a sleep state with a very small latency to wake up.

Another approach is based on the high peak power consumption of main memory. Diniz et al. propose techniques that limit consumption by adjusting the power states of the memory devices as a function of the load on the memory subsystem [DGJB07]. This leads to an optimization problem

**Table 2.1.:** Specifications of Rambus RDRAM for a 32 MB bank [MCH07], 2 GB RDRAM consumes approximately 16 W.

| Power State | Power            | Active Components                |

|-------------|------------------|----------------------------------|

| Active      | $300\mathrm{mW}$ | Refresh, clock, row, col decoder |

| Standby     | $180\mathrm{mW}$ | Refresh, clock, row decoder      |

| Nap         | $30\mathrm{mW}$  | Refresh, clock                   |

| Powerdown   | $3\mathrm{mW}$   | Refresh                          |

for the memory controller to select the different power states. This technique is not limited to RDRAM-based memory subsystems, they can treat entire DDR modules as well as single RDRAM chips.

#### Remaining components

There are some other remaining components in a cluster node which also consume energy, like the uninterrupted power supply (UPS), the main board with North- and Southbridge, various ports (USB etc.), graphics card and fans. These components are not discussed here because on one hand it is difficult to determine and control their actual power consumption, and on the other hand these components are more or less dependent on the already discussed components. But one component needs to be separately mentioned: the power supply. The power supply's task is to change the voltages from one level to another level, mainly from the power grid voltage (e.g. 220 V) to 3,5 V and 12 V for the node components. But this change is not lossless, this energy loss is generally transferred as heat to the power supply. The relation of the input and the output power of the power supply, called efficiency, ranges from 60 % up to 95 % (for a SMPS, switched-mode power supply) [AH03]. But the efficiency of the power supplies does not only differ from device to device, the main problem is that the efficiency depends on the load. So usually for low and high utilization the efficiency is better than for medium utilization. Due to the fact that there is no relation between the performance of a node and the efficiency of its power supply, there is no obstacle to use SMPS's (apart from the acquisition costs) in high performance clusters to reduce energy loss.

## 2.2. Managing of Energy Aware Hardware with ACPI

The presented energy saving mechanisms of the different components of a cluster are partially controlled by the component itself, but the operating system has a better overview over the components. Hence the energy management usually is performed by the operating system using the Advanced Configuration and Power Management Interface (ACPI) [CCC $^+$ 05]. The ACPI specification is an open standard for unified operating system-centric device configuration and power management. The system is divided into several states: The Global System States (G0-G3), the Device Power States (D0-D3), the Sleeping States (S1-S5), the Processor Power States (C0-C3) and the Device and Processor Performance States (P0-Pn). Generally state 0 is the "Working" state with the highest power consumption. To increase the state means to decrease energy consumption and to increase wake-up time (latency) of specified device or system. The last state implicates the "Mechanical Off" for the component (exception: Sleeping State S5 implies the "Soft Off" state). The Device and Processor Performance States imply the Processor State C0 and the Device State D0, but a different performance level (e.g. using a mobile device with battery or power supply).

An explicit overview of the different states is located in the appendix. Based on these state specifications, hardware vendors can implement reactions for state changes occurring for ACPI-aware components.

In reality in the power state the component could decide to disable internal circuits if it stays

ready all the time. For instance the processor could disable the ALU per instruction if it can turn it on rapidly, i.e. without performance loss, by knowing the future instructions in the pipeline.

### 2.3. Analysis of Energy Saving Potential

The introduced energy saving mechanisms for the different hardware components are yet partially under development in today's computer systems.

The mechanisms of the CPU are well developed and used in today's energy aware computer systems. This is based on three aspects: At first, the CPU is one of the most power consuming components. At second, the CPU is one of the most heat generating components, so reducing the power consumption for the CPU means reducing the heat which reduces the fan RPM. This in turn reduces the energy consumption and -especially for mobile devices- the noise of the whole system. The third aspect is that switching the different power states for a CPU has (compared to the other components) the lowest wake-up times ranging between a few nanoseconds and some milliseconds.

The hard disk mechanisms are also used in today's energy aware systems, especially mobile devices. The wake up time for the disks are a multiple of the wake-up time of a CPU, but the operative point are the caching capabilities of the main memory for hard disk tasks. Data can be written to the main memory while the disk is powering on and the writing task itself can wait until the disk is in operating mode. This can be handled in the background without users notice (with small amounts of data).

The mechanisms for main memory, network cards and switches are not used in today's systems, because the hard- and software for these tasks are still in development. In the past, there has only been small interest in developing algorithms for these components, because the power consumption is only a fractional amount of a mobile system [MV04]. Other components, that are not relevant for high performance computing (e.g. LCD panels) are more interesting concerning the energy consumption.

In today's research the main memory, network cards and switches are also included based on the growing networks like the Internet or campus LANs, the increasing number of datacenters, clusters and also personal computers and mobile devices.

For high performance clusters these parts are more relevant, because of the sum of the individual components. If a network card has an energy saving potential of maybe 5%, this is not really interesting for a desktop or even a mobile system. But for a cluster with about 6000 network cards, the aggregated savings are interesting.

But why are the mechanisms (e.g. for CPU and disk) not used in high performance clusters?

The main point is that in high performance computing the time overhead for switching between different power states can increase the computing time significantly even with small state change durations. High performance algorithms have lots of fine tuning to minimize time overheads. For this tuning, each algorithm is analyzed to find waiting times (e.g.  $MPI\_Barrier$ ) and these times have to be minimized. Lots of algorithms are also based on topology specific communication schemes and network responding times. Out of this, small influences for the responding time of components can significantly reduce the performance. If the performance is reduced, the calculating time for the whole cluster increases and hence the power consumption.

Another point is that the caching capabilities for the data to be written to disk are restricted. Some parallel programs are using the whole main memory for calculation. These parameters are specified by the developer to increase the calculating performance. A typical use case is called checkpointing. For this, the working datastructures (in this case, the bulk part of the main memory) are written to disk. This is done for backup purposes, because most algorithms calculate for days, weeks and even months or years. If the program crashes or a hardware failure occurs, the calculation can be restarted using the checkpoint data. If a checkpoint should be written, disks have to be in working state (because no caching is possible) to avoid performance degradation. Because usually the operating system manages the ACPI states of the hardware, no information for the future disk use is available and so the influence on the computing time can not be minimized.

The main requirements to control energy saving without reducing performance is the information which hardware component is used when. There are two main ideas how this information can be

gained: First, the programmer of the parallel algorithm knows when components are used, so he can publish this information (like instrumenting the code). Secondary the program trace can be analyzed to gain the typical usage of the components. A second run of the same (or similarly) program can use this profile created in the first run. With this information, the components can change their ACPI levels to decrease the power consumption and wake up before the specific component is used.

But these concrete approaches are not discussed in this work.

## 3. Estimation of Cluster Power Consumption

In this chapter different models for estimation of power consumption of a cluster environment are explained and discussed. After the discussion of these models the chosen model is described in detail. Section 3.2 contains an approach to determine the input values for the modeled components. To estimate the power consumption different strategies are described in sections 3.3 and 3.4.

There are two main ideas to estimate the power consumption of a specific program run on a cluster. The first idea is to gain knowledge about the power consumption of specific operations in a computer system (like writing a block to disk or assigning a variable). With this information, a program run can be simulated and the power consumption can be estimated. A simulator to analyze parallel programs and the underlying cluster hardware is in development at the Research Group Parallel and Distributed Systems. The power consumption has a high accuracy because the data about the specific operations is cumulated in a very granular way via the simulator. To calculate the power consumption with different energy-aware features of the hardware, the simulator offers a realistic environment to develop different strategies to use these features.

But this realistic environment has the disadvantage of its high complexity. Intelligent hardware and software is using lots of mechanisms to optimize the hardware access such as caches. Therefore, if a program for example writes a block on disk, there is almost no knowledge about when this block is really written on disk. It is possible that this block is held in the cache and only if enough blocks are in the cache, the data is written to disk. It is also possible that the block should be overwritten or deleted, so the writing does not have to be performed. The only way to sustain the real hardware access by the simulator is to implement the caching algorithms. But this a complex feature on the one hand and on the other hand the information about the caching algorithms is typically are kept secret by the hardware vendors.

Apart from the hardware caching mechanisms there are other optimizations on different layers, starting at the compiler optimizations over operating system based optimizations to optimizations of the file system, especially with intelligent cluster file systems such as PVFS <sup>1</sup>. Of course there are also optimizations for other hardware components, especially CPU and NIC, with similar behavior.

The second approach is to collect the utilization data in a coarse-granular way. This data can be collected in fixed timesteps (for example by the operating system) and appended to a trace file containing information about the specific program (such as MPI calls). The trace file can be analyzed after the program run to estimate the power consumption based on the components utilization. With this utilization data it is possible to evaluate the future component's utilization when analyzing the trace. The inactive times can be identified and considered in the calculation of the power consumption. It is possible to consider sleeping times for the affected devices without affecting the calculating time. In this way an upper bound for energy saving can be calculated.

The granularity of the utilization values is based on the mechanism used to collect the data. If data is collected too frequently, the CPU is busy with collecting the utilization data. That is why the frequency has to be adjusted to a level with adequate granularity without affecting the performance.

This second model will be described detailed in the next section.

<sup>&</sup>lt;sup>1</sup>http://www.pvfs.org, last checked on August 27, 2009

#### 3.1. Model

In general, the power consumption of a cluster environment is the sum of the power consumption of its components (nodes, switches and cooling environment). The power consumption for the cooling environment simply can be included in a model. This consumption depends on the power consumption of the other components. Every watt needed by a component like a CPU or a switch results in waste heat which has to be cooled down. The power consumption for cooling can be easily estimated by multiplying the consumption of all other components with an environment based factor. For today's HPC installations this usually is the factor 2, each watt produced has to be cooled down using one watt for air conditioning. But in future installations this factor will be decreased (e.g. increasing the operating temperature of cluster environments so that the outer air can be used for cooling).

The power consumption of the switch is nearly independent of the net utilization, it consumes as much power when active as when it is inactive. Hence, the power consumption of a switch is a constant, which can be added to the node's power consumption. For this reason, the estimation of the node's consumption is the main challenge. The power consumption of a node is the sum of the node's hardware power consumption. Some of these hardware components (like CPU or power supply) have a bigger effect on the power consumption than other components. And for almost every component the power consumption is based on the utilization (a calculating CPU uses more energy than an idle one).

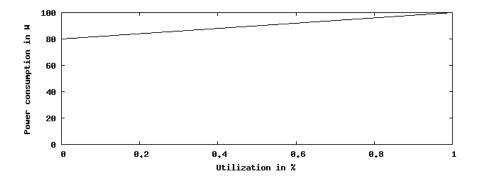

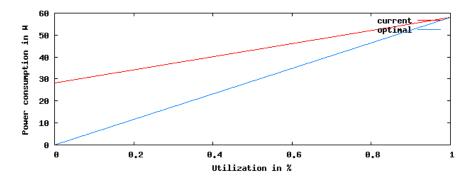

The chosen model contains abstractions for the following components: CPU, memory, disk, NIC and the power supply. These components are grouped to a node. The sum of the power consumptions for all components of a node is the node consumption. It is possible to include a percental overhead for other components like main board etc.. The power consumption of each component based on the utilization is linearly interpolated from two values: The first one is the power consumption at zero utilization and the second is the power consumption at full utilization. This results in a power consumption / utilization graph like shown in figure 3.1.

**Figure 3.1.:** Power consumption / utilization graph for a specific component. At zero utilization this component has a power consumption of 80 W, at full utilization 100 W. For every other utilization value the power consumption is interpolated linearly.

In reality, the power consumption / utilization graph is not linear and the characteristics are different for each component. But this information is not easy to obtain: The majority of hardware vendors does not publish this information and the equipment for taking detailed measurements has not been applicable. To measure an indicated value for a specific component special equipment is needed, because the power consumption for a CPU (without main board) for different utilization values is not measurable easily. Out of this, only the two values for high and low utilization are used. The concrete measuring is described in section 3.2.

Further the power consumption for modeling the different ACPI states is needed. The power consumption for Device Power State 0 is as already mentioned linearly interpolated. For all other non-working states (1-3) no interpolation has to be done, because the components are in a sleeping mode where the power consumption is independent from the utilization. Different working states where for example the CPU is used at a lower frequency (C-States) are not modeled here, because the trace file does not contain this information and the cluster's hardware (see next chapter) does

not support this feature (in general, it is possible to get statistics about the CPU frequency, e.g. with PowerTop <sup>2</sup>). To switch to a different ACPI Power State two further values are needed: The duration for switching and the energy consumption for switching. If a disk is switched from ACPI Device State 3 (deeper sleep) to Device State 0 (working), this takes a few seconds. And also some energy is needed to spin up the disk to the required revolutions per minute. These values are depending on the component and the concrete change, so for every state change (incrementing and decrementing) values can be considered. The switching between two not sequenced states is realized by sequential incrementing or decrementing respectively until the desired state is reached.

Because the components are grouped in nodes, the ACPI Global System States are all associated components in the equivalent ACPI Device State.

Based on this model for the power consumption in each ACPI Device State and the utilization from the trace file the power consumption can be estimated. This process is modeled as a Replay: For each fixed step (defined by the stepsize of the utilization values in the trace file) the power consumption for each component is calculated. This process (without usage of the ACPI Power States) is the simplest strategy for power estimation and adequate to the real power consumption, because the cluster hardware is (with one exception, see section 5.1) not ACPI capable. However with the input values of the different ACPI State consumptions a potential power saving can be calculated, when putting components to a higher ACPI State (e.g. lower power consumption) when inactive. Different strategies for putting components to sleep (mainly based on the character of the component and the utilization) have been developed and implemented. These strategies are described in detail in the next section.

#### 3.2. Determination of Component Power Consumption

As discussed in the last section the following values are needed to estimate the component power consumption:

- power consumption without utilization

- power consumption with full utilization

- power consumption in ACPI Device Power States 1-3 (sleeping states)

- energy consumption and duration for switching the ACPI Device Power States

One way to identify the power consumption can be using data sheets of each hardware vendor. But the data published in these data sheets is mainly based on marketing strategies. So nearly every vendor defines or re-defines some power consumption values, but the concrete data is not significant in most of the cases, especially for different utilization phases. To distinct these values standardized benchmarks are needed, but these benchmarks do not exist yet.

But if the power consumption of a component doesn't differ significantly between high and low utilization phases, or in general it has a low power consumption, benchmarks are too inaccurate. The measuring of the component based power consumption is in this respect a problem as not each component has a direct power cable supply. The components located on the main board (such as CPU, main memory, network card) are served by the main board, so the specifying energy into individual component consumption is only approximately possible. When using a stresstest for different components the relation between the components have to be considered (e.g. an Ethernet card possibly utilizes the CPU). This second level utilization is not insignificant, but is not easy to measure because of fast switching between high and low utilization.

Of course this component based measuring is the most accurate way, but is not possible without special measuring equipment.

With the measuring equipment available at Research Group Parallel and Distributed Systems it is possible to measure the power consumption at node level. The different utilization of each component

<sup>&</sup>lt;sup>2</sup>http://www.lesswatts.org/projects/powertop, last checked on August 27, 2009

has influence on the node power consumption and out of this the difference between the component power consumption with different utilization can be measured.

In this approach especially the characteristics of the power supply have to be considered. On one hand the power supply's overhead (for converting the voltage) have to be deducted to determine the components power consumption. On the other hand the charge process of the supply's capacitors is dependent on the specific device and not urgently results in equivalent power consumption. When components need more power for a short time period this is not recognizable when measuring the node consumption, because the needed power is stored in the power supply's capacitors. If for example a component increases its power consumption for 1 millisecond by 10 W, this can possibly result in a different power consumption for the power supply (e.g. increasing power consumption for 10 milliseconds by 1 W).

The resulting procedure to determine the power consumption of selective components is combination of measuring the node power consumption and using the hardware vendor data sheets. To determine the idle power consumption different sets of components can be removed from one cluster node and the power consumption can be measured when entering the BIOS (basic input/output system) of the node (each resulting power consumption is named  $BIOS_{components}$ ). For the utilized power consumption a stresstest has been implemented to stress different sets of components (each resulting power consumption is named  $STRESS_{components}$ ). Based on the limited capability to stress and remove components the modeling of components is limited (e.g. the stressing of the network card results amongst other in stressing the network controller whose increased power consumption is included in the power consumption of the network card).

The idle and utilized power consumption for each component based on the total power consumption is calculated as follows: At first, each measured value (from the stresstest and the idle power consumption) is multiplied by the power supply efficiency to get the power consumption without the overhead of the power supply. With the node consumption with different hardware configurations in idle mode the idle power consumption for each component (except the CPU) can be calculated ( $MEM_0 = BIOS_{MEM,others} - BIOS_{others}, DISK_0 = BIOS_{DISK,MEM,others} - BIOS_{MEM,others}, \dots$ ). Also the difference between the idle and utilized hardware can calculated subtracting the idle power consumption ( $CPU_{diff} = STRESS_{CPU} - BIOS_{ALL}, MEM_{diff} = STRESS_{CPU,MEM} - STRESS_{CPU}, \dots$ ). With these values and the idle power consumption the utilized power consumption for the components (without the CPU) can be calculated ( $MEM_1 = MEM_0 + MEM_{diff}, \dots$ ). When using the utilized power consumption for the CPU from the vendors data sheet the idle power consumption of the CPU can be calculated the same way.

The resulting power consumption values for idle and utilized components can be compared with further hardware vendor data sheets if available.

The power consumption for the other ACPI Device Power States (1-3) and the energy consumption and duration for switching the ACPI Device Power States must be extracted from various data sheets of comparable hardware, because the concrete hardware is not ACPI capable.

## 3.3. Power Consumption Estimation Strategies

To estimate the power consumption of a cluster four different strategies have been implemented. These strategies are component based, so every component in a node can use a different strategy. The four strategies are named Simple Strategy, Optimal Strategy, Approach Strategy and MultipleState Strategy.

The first strategy estimates the power consumption without the usage of any power saving mechanism. For the Simple Strategy, every single timestep is evaluated independently. The other strategies are look ahead strategies, which take different decisions based on future utilization values. The Optimal Strategy decides to put a component into sleep mode if the future utilization is zero for sufficient timesteps and wakes it up before it is used again. Because such zero utilization times are not frequently for some components such as a CPU, the Approach Strategy puts a component into sleep if the utilization is under a specified level, e.g. 5%. At the end of the low utilization phase an equivalent phase with high utilization is performed to adjust the utilization. The last strategy assigns

different levels of utilization to different ACPI Device States. This is useful for components like the main memory. If the main memory utilization is under 50%, half of the banks can theoretically be switched off to save energy. These four strategies are explained and discussed in detail in the next subsections. For this, an example utilization graph is created for a single component. Based on this utilization, for each strategy the resulting power consumption graph is shown to explain the differences between the strategies.

#### 3.3.1. Simple Strategy

To estimate the real power consumption without energy aware hardware the power consumption for each hardware component has to be interpolated. To interpolate, the consumption values for low and peak utilization have to be defined. The power consumption  $P_{\rm curr}$  for a given utilization  $u_{\rm curr}$  and the power consumption at ACPI Device State 0  $P_{\rm ACPIO_{0\%}}$  (zero utilization) and  $P_{\rm ACPIO_{100\%}}$  (full utilization) is calculated in equation 3.1.

$$P_{\text{curr}} = (P_{\text{ACPI0}_{100\%}} - P_{\text{ACPI0}_{0\%}}) u_{\text{curr}} + P_{\text{ACPI0}_{0\%}}$$

(3.1)

Each timestep of the given utilization is evaluated (the step power consumption is calculated with equation 3.1) independently, hence the power consumption values are as granular as the utilization values. The power consumption for the component is the accumulated sum of the step power consumptions (power consumption per step), the power consumption for the node is the accumulated sum of its components power consumption.

Because the calculated power consumption only depends on the utilization and the ACPI Device Power States this strategy can also be used to estimate the power consumption with energy efficient hardware. Energy efficient hardware means hardware that consumes less energy when not utilized.

#### 3.3.2. Optimal Strategy

The Optimal Strategy uses the different ACPI Device Power States of the component. This strategy calculates the minimal power consumption without reducing the performance, because components only change to sleep mode if the component is not used and wake up before the component is used again. Only the ACPI Device Power States 0 (working) and 3 (deepest sleep) are used. The decision if a component switches to sleep mode depends on different factors: The duration of the zero utilization phase, the power saving potential of the state change ( $P_{\rm diff}$ , difference of power consumption ACPI0 and ACPI3), the duration of the state change ( $t_{\rm change}$ , sum duration ACPI0 to ACPI3 and duration ACPI3 to ACPI0) and the energy of the state change ( $t_{\rm change}$ , also the sum of both changes). With these values the minimal duration of a zero utilization phase  $t_{\rm optimal}$  can be calculated, for which sleeping reduces the power consumption without reducing performance (see equation 3.2).

$$t_{\text{optimal}} = \frac{E_{\text{change}}}{P_{\text{diff}}} + t_{\text{change}}$$

(3.2)

The algorithm 1 describes the procedure in detail for a node with Optimal Strategy.

In difference to the power consumption with the Simple Strategy the component uses the sleep mode at the zero utilization phase and wakes up before it is used again. Therefore the power consumption is decreased without increasing the calculating time. Because the future utilization in concrete runs of parallel programs is not known, the output of the Optimal Strategy is an approximated upper bound for power saving.

#### Algorithm 1 Optimal Strategy

```

Require: All components in state ACPI0 (working)

for step = 1 to countSteps do

for device in nodeComponents do

if device is working then

if device's future utilization is zero for at least t_{optimal} steps then

device go to sleep mode (ACPI3)

end if

else

\{device is sleeping}

if device's future utilization is not zero for at least t_{ACPI3-ACPI0} steps then

device go to working mode (ACPI0)

end if

end if

end for

end for

```

#### 3.3.3. Approach Strategy

Because some components do not have zero utilization phases but low utilization phases, the Approach Strategy has been developed. The intention is to simulate more energy efficient characteristics. If a component works for example 10 seconds with a low utilization of 10%, the same work could be done working 1 second with a utilization of 100%. This results in 9 seconds with zero utilization where the component can switch to sleep mode. The rearrangement of load can be thought of reordering the code. However, in reality this might not be possible due to dependencies between calls etc..

The calculation of the minimal time for an efficient state change is now dependent on a tolerance value  $\delta$ . The timesteps with a utilization lower than  $\delta$  will be rearranged if the count of timesteps under the specified tolerance is greater or equal  $t_{\rm approach}$  (see equation 3.3). The rearrangement of load results in a zero utilization phase ( $t_{\rm optimal}$ ) and the utilization phase containing the equivalent load ( $t_{\rm load}$ ). The equivalent load is the aggregated utilization for the duration of  $t_{\rm optimal}$  before the rearrangement.

$$t_{\text{approach}} = t_{\text{optimal}} + t_{\text{load}}$$

(3.3)

The algorithm 2 describes the procedure in detail for a node with Approach Strategy.

This strategy provides also an upper bound for power saving. In contrast to the Optimal Strategy the strategy rearranges the utilization, which more likely than not affects the calculating time of the parallel program because of the dependencies inside the code and/or the hardware. If for example the CPU is utilized 10 seconds with a mean value of 10% for sending a message over network, the bottleneck is the NIC or the bus system. And a utilization of the CPU with 100% for one second would not solve that problem. In this case another approach is needed, so it could be determined if other calculations in the parallel program can be pushed to utilize the CPU with the remaining 90%. Out of this, the output produced by the Approach Strategy shows scopes where power saving could be scheduled. In the above example an approach to eliminate the bottleneck (e.g. a faster NIC) can increase the performance and possibly decrease the power consumption. It must be evaluated in the concrete use case if the faster NIC consumes more power than the CPU saves.

#### 3.3.4. Multiple State Strategy

The last strategy is an extension of the Optimal Strategy to use multiple ACPI Device Power States. This allows to model another use case: Its possible for a component to use different states with different power consumptions and wake up times. A component to use this strategy is the main memory, because the main memory will never reach a zero utilization phase. Neither could it be put

#### Algorithm 2 Approach Strategy

```

Require: All components in state ACPI0 (working)

for step = 1 to countSteps do

for device in nodeComponents do

if device is working then

if device's future utilization is lower than tolerance \delta for at least t_{\rm approach} steps then

device go to sleep mode (ACPI3)

rearrange device's utilization

end if

else

\{device \text{ is sleeping}\}

if device's future utilization is not zero for the next t_{ACPI3-ACPI0} steps then

device go to working mode (ACPI0)

end if

end if

end for

end for

```

to sleep if only utilized with 10 %. But if the memory is split into multiple banks on the main board, some of these banks can be turned off if not utilized. It is also possible to use this strategy for the ACPI Processor Performance States (P-States), because if the CPU is for example utilized about 50 %, it is possible to lower the frequency, but it is not recommended to go in sleep mode.

For the Multiple State Strategy multiple utilization levels  $(u_1, u_2, u_3, u_4)$  have to be defined to trigger a state change. If the utilization is under the specified value (for example  $u_1 = 0.75$ ) the state change from ACPI Device Power State 0 to ACPI Device Power State 1 is triggered. For increasing the ACPI Device Power State (and decreasing the power consumption) the time  $t_{\min}$  can be calculated based on the future utilization steps and the next higher utilization level. The algorithm 3 describes the procedure in detail for a node with Multiple State Strategy.

#### Algorithm 3 Multiple State Strategy

```

Require: All components in state ACPI0 (working)

Require: level[4] containing utilization levels u_1, u_2, u_3 and u_4

for step = 1 to countSteps do

for device in nodeComponents do

currentState = device's current ACPI Device Power State

if currentState < 3 then

calculate t_{\min} based on currentState and currentState+1

if device's future utilization is lower level [currentState + 1] for the next t_{\min} steps then

device go to State ACPIcurrentState + 1

end if

end if

if currentState > 0 then

for each state of the lower states do

calculate t_{\mbox{wakeUp}} for the change from currentState to state

if device's future utilization is greater level[state] in one of the next t_{wakeUp} steps then

device go to state ACPIstate

end if

end for

end if

end for

end for

```

#### 3.4. Example Power Estimation

In this section the previous described strategies are used to estimate the power consumption for an example component. Based on this component and a given utilization the different approaches of the strategies are visualized and compared.

First the input values for the example component have to be specified (see table 3.1). These values are chosen to see the difference of the strategies and aren't based on a real component.

**Table 3.1.:** Power schema for example power estimation component. The power schema contains the power consumption for the different ACPI Device Power States and the energy and duration for changing these.

| Power schema entry                                                             | Value                  |

|--------------------------------------------------------------------------------|------------------------|

| $P_{ m ACPI0_0\%}$                                                             | 80 W                   |

| $P_{\text{ACPI0}_{100\%}}$                                                     | $100\mathrm{W}$        |

| PACPI1                                                                         | $75\mathrm{W}$         |

| $P_{\text{ACPI2}}$                                                             | $50\mathrm{W}$         |

| $P_{\text{ACPI3}}$                                                             | $25\mathrm{W}$         |

| Level $u$                                                                      | [1.0, 0.75, 0.5, 0.25] |

| $E_{\text{ACPI0-ACPI1}}$ , $E_{\text{ACPI1-ACPI2}}$ , $E_{\text{ACPI2-ACPI3}}$ | $0\mathrm{Wh}$         |

| $E_{\text{ACPI3-ACPI2}}$ , $E_{\text{ACPI2-ACPI1}}$ , $E_{\text{ACPI1-ACPI0}}$ | $0.01\mathrm{Wh}$      |

| <sup>t</sup> ACPI0-ACPI1, <sup>t</sup> ACPI1-ACPI2, <sup>t</sup> ACPI2-ACPI3   | $0\mathrm{ms}$         |

| <sup>t</sup> ACPI3-ACPI2, <sup>t</sup> ACPI2-ACPI1, <sup>t</sup> ACPI1-ACPI0   | $500\mathrm{ms}$       |

Not all strategies are using all entries in the power schema, so the definition of the level u and the power consumption for the ACPI Device Power State 1 and 2 is only used for the Multiple State Strategy ( $P_{\rm ACPI1}$  and  $P_{\rm ACPI2}$  respectively). The energy consumption for switching the ACPI Device Power States and the associated duration is used in the strategies Optimal Strategy and Approach Strategy, because the energy consumption (and duration respectively) of the change from state 0 to state 3 is the sum of the changes from state 0 to state 1, 1 to 2 and 2 to 3. The specification of these values is of course not necessary for Simple Strategy, because no energy saving mechanism is considered in this strategy. Only the power consumption values for zero and full utilization in ACPI Device Power State 0 are used ( $P_{\rm ACPI0_{00\%}}$  and  $P_{\rm ACPI0_{100\%}}$  respectively).

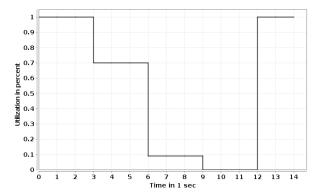

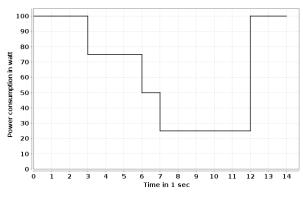

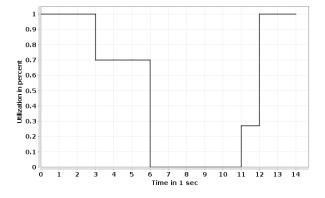

Second the input utilization has to be specified (see figure 3.2(a)). The domain axis is divided in timesteps, timestep 1 is the timestep from  $0 \to 1$  and so on. This utilization has been chosen to see effects for each strategy.

The resulting power consumptions for each strategy are summarized in table 3.2.

Table 3.2.: Summary of example component energy consumption and savings for each strategy.

| Strategy       | Total energy consumption | Saving |

|----------------|--------------------------|--------|

| Simple         | $0.38\mathrm{Wh}$        |        |

| Optimal        | $0.334\mathrm{Wh}$       | 12.1%  |

| Approach       | $0.303\mathrm{Wh}$       | 20.3%  |

| Multiple State | $0.278\mathrm{Wh}$       | 26.8%  |

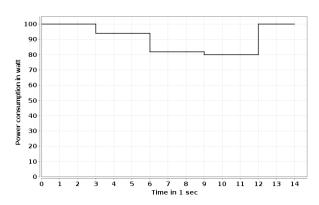

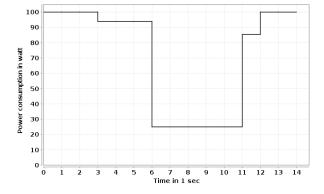

The energy consumption of 0.38 Wh for the Simple Strategy is equivalent to the energy consumption without using ACPI Device Power States. The visualization of the power consumption is shown in figure 3.2(b)). When comparing the power consumption with the utilization (figure 3.2(a)) the

characteristics are mainly the same, because the power consumption graph is the upset and shifted graph of the utilization. The maximal power consumption is 100 W at the full utilization phase at the beginning, decreasing with the utilization to 80 W after 10 seconds where the zero percent utilization phase occurs.

With the Optimal Strategy the power consumption of this zero utilization phase can be decreased to 25 W (see figure 3.2(c)) when switching to ACPI Device Power State 3. This results in savings of 12.1% compared to Simple Strategy. The switching is possible, because the duration of the zero utilization phase is 3 seconds, and the minimal duration for an efficient state change is  $t_{\rm optimal} = 2654\,{\rm ms}$  (see equation 3.4).

$$t_{\text{optimal}} = \frac{E_{\text{ACPI0-ACPI3}} + E_{\text{ACPI3-ACPI0}}}{P_{\text{ACPI0}} - P_{\text{ACPI3}}} + (t_{\text{ACPI0-ACPI3}} + t_{\text{ACPI3-ACPI0}})$$

$$= \frac{0.01 \,\text{Wh}}{80 \,\text{W} - 25 \,\text{W}} + 2000 \,\text{ms} = \frac{360000 \,\text{Wms}}{55 \,\text{W}} + 2000 \,\text{ms}$$

$$\approx 2654 \,\text{ms}$$

(3.4)

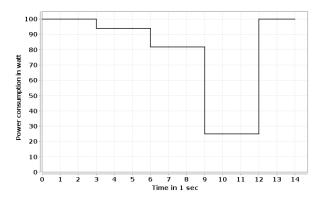

Using the Approach Strategy with a tolerance  $\delta=0.1$  phases with a utilization lower than  $10\,\%$  will possibly be rearranged. In this example the energy consumption can be decreased in the  $9\,\%$  utilization phase before the zero utilization phase when rearranging the utilization. The three steps with  $9\,\%$  utilization result in one step with  $27\,\%$  utilization, thus  $t_{\rm load}=1\,{\rm sec}$ .

The rearranging is possible, because the duration of the phase under the specified level  $\delta$  is 6 seconds, and the minimal duration for an efficient state change is  $t_{\rm approach} = 3654\,\mathrm{ms}$  (see equation 3.5).

$$t_{\text{approach}} = t_{\text{optimal}} * t_{\text{load}}$$

$\approx 2654 \,\text{ms} + 1 \,\text{sec}$

$= 3654 \,\text{ms}$  (3.5)

Figure 3.2(e) shows the recalculated utilization based on figure 3.2(a). The utilization phase lower than  $\delta$  (from timestep 7 to times step 12) is summarized in a 27% utilization phase at the end (timestep 12). The resulting power consumption is shown in figure 3.2(f) and is equivalent to the calculation with the Optimal Strategy and the rearranged utilization.

When comparing the Multiple State Strategy power consumption (see figure 3.2(d)) with the one calculated with Optimal Strategy multiple ACPI Device Power States are used. With this granular levels a energy saving of about 26.8% for this example is possible, because every utilization change in the example results in a different ACPI Device Power State.

As seen in the previous section the energy saving increases with each strategy, in the case of the Multiple State Strategy a saving of 26.8% is possible. But based on the input values a quantification of the energy saving potential is still not possible, but it comes clear that an energy saving potential is existent. Which the choice of the strategy the power saving varies: When using the Approach Strategy in the main case this strategy saves more energy as Optimal Strategy. But this strategy recalculates the utilization, thus the state changes of the Approach Strategy are hints for the developer of the algorithm to review possible code modifications to change the hardware utilization. The Optimal Strategy is an upper bound for energy saving because the hardware switches to power saving modes in every utilization phase where it is efficient possible. With Simple Strategy it is possible to estimate the power consumption of the hardware as granular as the input values (for the utilization and the state power consumption) is specified.

(a) Example utilization to compare the different strategies for power estimation.

(b) Power consumption with Simple Strategy based on utilization from figure 3.2(a).

(c) Power consumption with Optimal Strategy based on utilization from figure 3.2(a).

(d) Power consumption with Multiple State Strategy based on utilization from figure 3.2(a).

(e) Rearrangement of utilization with ApproachStrategy based on figure 3.2(a).

(f) Power consumption with Approach Strategy based on utilization from figure 3.2(e).

## 4. Software Design

This chapter is a description of the software design to realize the power estimation model and the stresstest. Furthermore the requirements for the implemented software are discussed. After describing the related projects at Research Group Parallel and Distributed Systems to create and analyze traces, the concrete implementation model of the software components and its interfaces will be illustrated. Hence an overview of the testing concept and the external package dependencies is given.

#### 4.1. Software environment

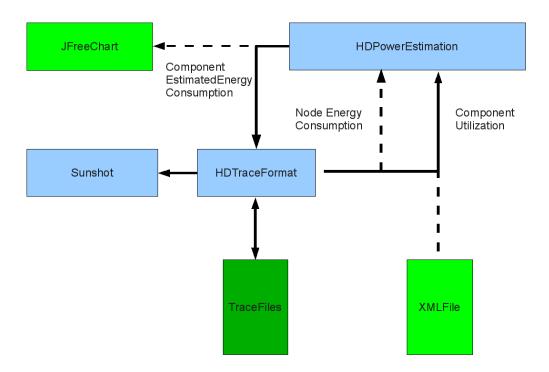

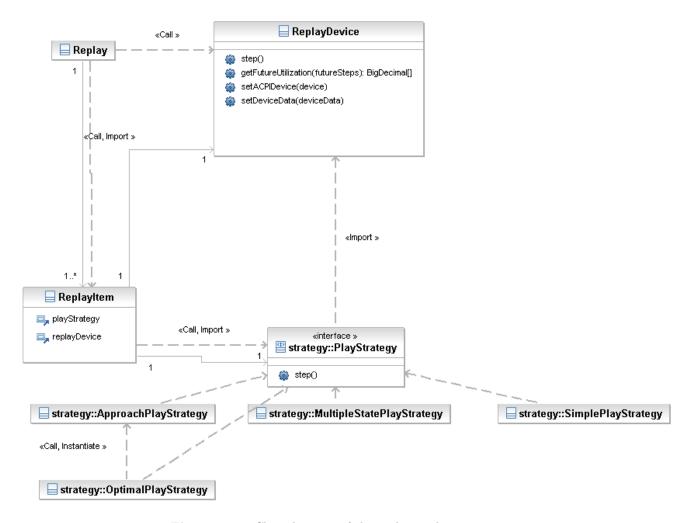

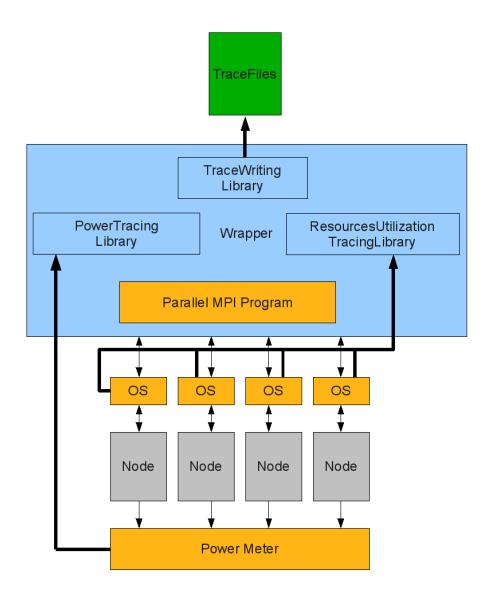

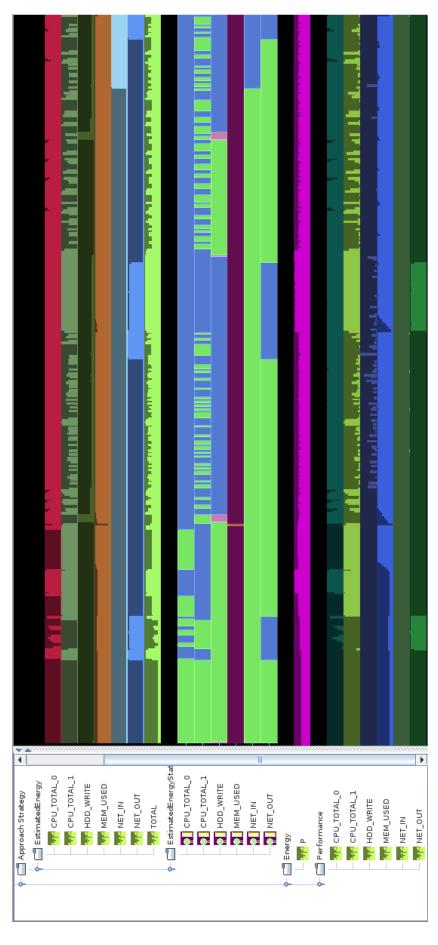

The project **HDPowerEstimation** has multiple related projects developed at the Research Group Parallel and Distributed Systems. These projects are used to create and visualize program traces. To create traces of MPI programs a wrapper has been implemented (**HDMPIwrapper**). This wrapper uses the **ResourcesUtilizationTracingLibrary** and the **PowerTracingLibrary** to capture utilization of components and the power consumption of nodes respectively. While the **ResourcesUtilizationTracingLibrary** queries the components utilization from the operating system, the **PowerTracingLibrary** uses an external power meter to measure the power consumption. The mentioned projects are building the tracing environment to generate traces. Each of these projects is implemented in the C programming language. A graphical overview of the tracing components is given in the next chapter in figure 5.1. To visualize the trace files a viewer has been implemented based on Jumpshot <sup>1</sup> named **Sunshot**. This viewer is implemented in Java. To support the traces the Java project **HDTraceFormat** has been implemented. This project includes the model of the trace data and reading, editing and writing support for the trace files. A detailed interaction description of the Java-based projects is given in the subsection "Interfaces" in this chapter.

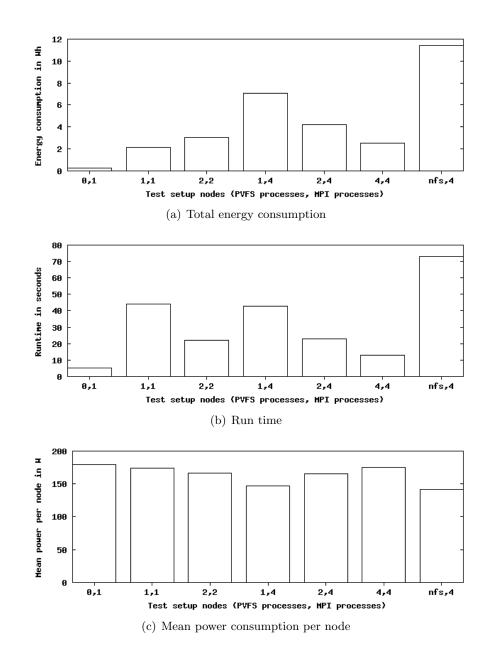

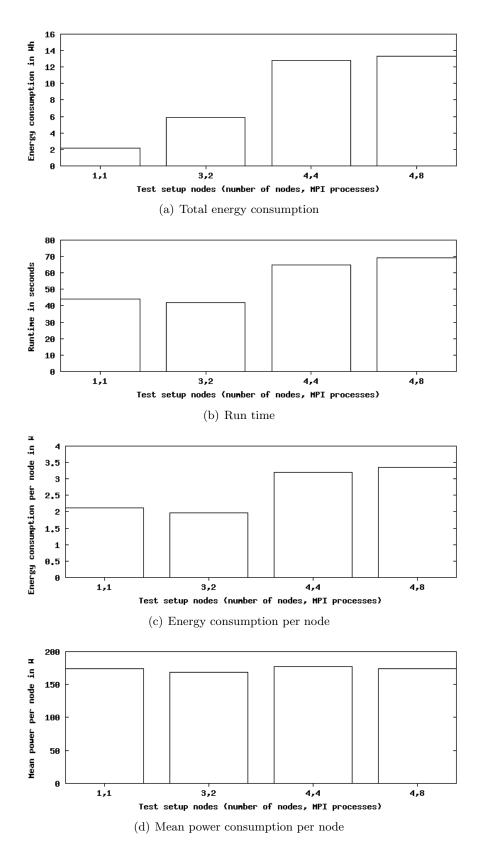

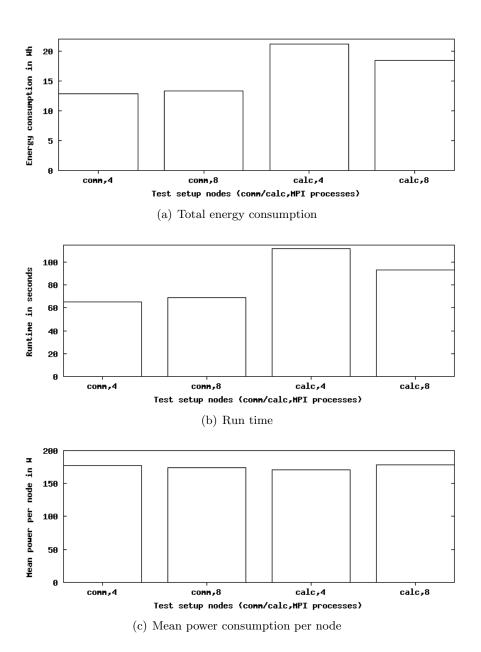

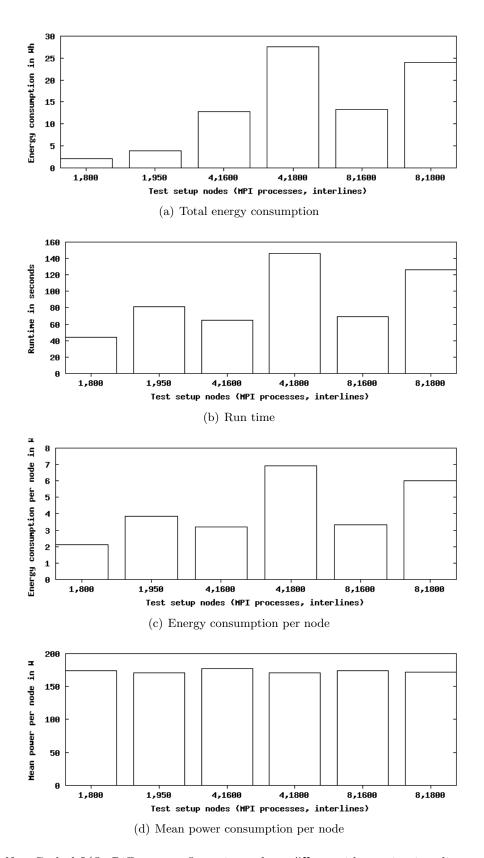

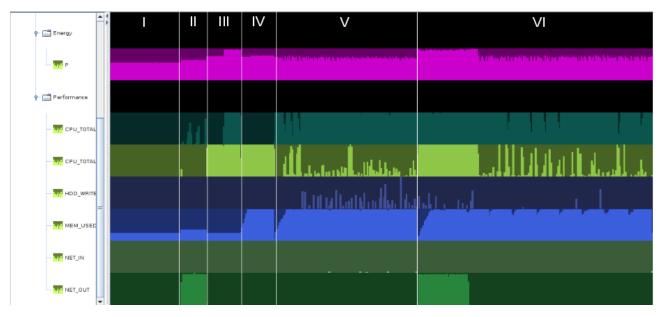

#### 4.2. Stresstest