# Dissertation

submitted to the Combined Faculties for the Natural Sciences and for Mathematics

of the

Ruperto-Carola University of Heidelberg, Germany

for the degree of Doctor of Natural Sciences

Presented by Dipl.-Phys. Sebastian Millner born in Witten, Germany

Date of oral examination: November 6, 2012

# Development of a Multi-Compartment Neuron Model Emulation

Referees: Prof. Dr. Karlheinz Meier Prof. Dr. Peter Fischer

#### **Development of a Multi-Compartment Neuron Model Emulation**

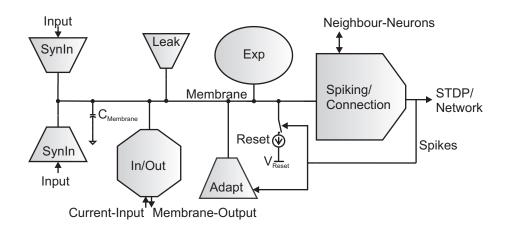

This work describes the design of an analog circuit emulating a multi-compartment neuron model on a microchip. Initially, the single-compartment adaptive exponential integrate-and-fire neuron model is implemented as a hardware model. Therefor, the differential equations describing the model dynamics are directly translated into an electronic circuit based on operational transconductance amplifiers. Consequently a close correspondence between model and circuit is achieved enabling references to experiments done with computer simulators. 512 of these neurons are implemented on a single micro-chip. Individual control of each neuron's biases is achieved by the use of analog floating-gate memory. In most cases, these biases directly correspondent to parameters of the model, hence simple translations are possible.

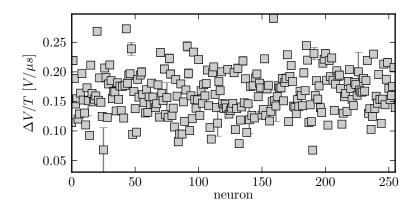

The single neuron implementation has been verified on a prototype chip in several experiments. Inter alia, its capabilities of reproducing biological neuron's behavior and the influence of fixed-pattern noise on the circuit are analyzed.

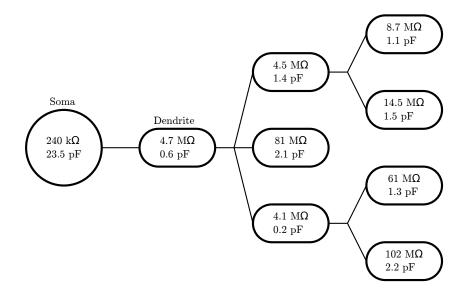

To step over to a multi-compartment circuit, the neuron has been enhanced by a resistive element and a routing network to build complex dendrite structures. Furthermore, the parameterization allows compartments of different sizes covering large somatic and small dendritic compartments. A dedicated test chip has been designed for the verification of the new model. Several simulations show the enhanced behavior of the multi-compartment emulation including dendritic attenuation and active spike propagation.

The neuron circuits are dedicated for a new kind of computer based on the cortex.

### Entwicklung einer Multi-Kompartiment-Neuronenmodel-Emulation

Diese Arbeit beschreibt den Entwurf einer analogen Schaltung zur Emulation eines Multi-Kompartiment-Neuronenmodels auf einen Mikrochip. Zunächst beschränkt auf einzelne Kompartimente wird das Adaptive Exponential Integrate-and-Fire Neuronenmodell implementiert. Hierzu werden die Differentialgleichungen des Modells durch Transkonduktanzverstärker direkt in elektrische Schaltungen übersetzt. Folglich wird eine enge Korrespondenz zwischen Schaltung und Model erreicht, wodurch es möglich wird, Ergebnisse aus Computersimulationen als Referenzen zu verwenden. 512 dieser Schaltungen werden auf einem Chip integriert. Für jedes einzelne Neuron können Steuerspannungen und Ströme individuel durch analoge Floating-Gates konfiguriert werden. In der Regel sind die Schaltungsparameter in direkter Beziehung zu den Modellparametern.

Durch Testchips wurde die Schaltung mit mehreren Experimenten verifiziert. Unter anderem wird das Reproduzieren spezieller Verhaltensmuster biologischer Neuronen gezeigt. Ferner wird das Verhalten bezüglich Produktionsschwankungen analysiert.

Um eine Multi-Kompartiment-Emulation zu konstruieren, wird die Schaltung im Weiteren um ein resistives Element und ein Schaltnetzwerk erweitert. Dadurch wird es möglich komplexe Dendriten nachzubilden. Außerdem wird die Parametrisierung so erweitert, dass sowohl große Somakompartimente, als auch kleine Dendritenkompartimente nachgebildet werden können. Zur Verifikation wurde ein Testchip entworfen. Mehrere Simulationen zeigen das erweiterte Verhalten des Multi-Kompartiment-Models. So werden Dämpfung, sowie die Weiterleitung von Aktionspotentialen im Dendrit gezeigt.

Die Neuronen wurden zur Integration in einen neuartigen Computer entworfen, dessen Funktion auf den Prinzipien des Gehirns basiert.

"Analog design is art and science at the same time. It is art because it requires creativity to strike the right compromises between the specifications imposed and the ones forgotten. It is also science because it requires a certain level of methodology to carry out a design, inevitably leading to more insight in the compromises taken."

Willy M. C. Sansen in Analog Design Essentials, Springer 2006

"Thus, we are no longer confident as we were 18 years ago that simplicity will eventually emerge from the complexity. The extreme sophistication of cellular mechanisms will challenge cell biologists throughout the new century [...]."

From the preface of *Molecular Biology of the Cell*, fourth edition by Bruce Alberts, Alexander Johnson, Julian Lewis, Martin Raff, Keith Robert, and Peter Walter, 2002

# Contents

| Introduction 1                                        |      |                                                              |                                         |                 |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|------|--------------------------------------------------------------|-----------------------------------------|-----------------|--|--|--|--|--|--|--|--|--|

| 1 Neuroscience, Circuits and Neuromorphic Engineering |      |                                                              |                                         |                 |  |  |  |  |  |  |  |  |  |

|                                                       | 1.1  | Biolog                                                       | ical Substrate                          | 5               |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.1.1                                                        | Neurons                                 | 5               |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.1.2                                                        | Synapses                                | 6               |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.1.3                                                        | Plasticity                              | 8               |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.1.4                                                        | Typical Cortical Neuron Behavior        | 8               |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.1.5                                                        | Measurement Capabilities                | 8               |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.1.6                                                        | High-Conductance State                  | 9               |  |  |  |  |  |  |  |  |  |

|                                                       | 1.2  | Single                                                       | Cell Modeling                           | 9               |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.2.1                                                        | The Hodgkin Huxley Model                | 9               |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.2.2                                                        | The Integrate-and-Fire Model            | 10              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.2.3                                                        | Adaptation                              | 11              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.2.4                                                        | Positive Feedback                       | 11              |  |  |  |  |  |  |  |  |  |

|                                                       | 1.3  | Techni                                                       | ical Substrate                          | 11              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.3.1                                                        | Transistors                             | 12              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.3.2                                                        | Basic Transistor Circuits               | 14              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.3.3                                                        | Simulation Techniques                   | 15              |  |  |  |  |  |  |  |  |  |

|                                                       | 1.4  | Rebuil                                                       | ding Biology - Neuromorphic Engineering | 16              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.4.1                                                        | Emulation                               | 16              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.4.2                                                        | Sensors, Neurons and Systems            | 18              |  |  |  |  |  |  |  |  |  |

|                                                       | 1.5  | Single                                                       | Cell Emulation                          | 18              |  |  |  |  |  |  |  |  |  |

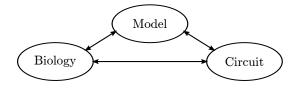

|                                                       |      | 1.5.1                                                        | The Design Approach Triangle            | 18              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 1.5.2                                                        | Ion Channel Implementation              | 20              |  |  |  |  |  |  |  |  |  |

| 2                                                     | Neu  | romorp                                                       | hic Environment                         | 25              |  |  |  |  |  |  |  |  |  |

|                                                       | 2.1  | The B                                                        | rainScaleS Project                      | 25              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 2.1.1                                                        | Interaction                             | 25              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 2.1.2                                                        | Hybrid Multi-Scale Computing Facility   | 25              |  |  |  |  |  |  |  |  |  |

|                                                       | 2.2  | The B                                                        | rainScaleS Wafer-Scale System           | 26              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 2.2.1                                                        | Communication                           | 27              |  |  |  |  |  |  |  |  |  |

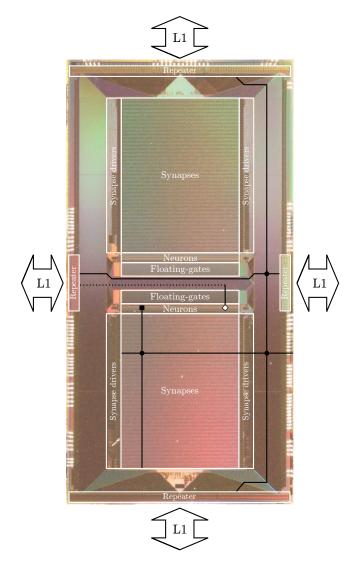

|                                                       | 2.3  | The H                                                        | ICANN Microchip                         | 28              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 2.3.1                                                        | Life Time of an Action Potential        | 29              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 2.3.2                                                        | High Input-Count                        | 30              |  |  |  |  |  |  |  |  |  |

| 3                                                     | Poir | nt Neur                                                      | on Emulation                            | 31              |  |  |  |  |  |  |  |  |  |

|                                                       | 3.1  | 3.1 The Adaptive Exponential Integrate-and-Fire Neuron Model |                                         |                 |  |  |  |  |  |  |  |  |  |

|                                                       |      | 3.1.1                                                        | Model Description                       | $\frac{31}{31}$ |  |  |  |  |  |  |  |  |  |

|                                                       |      | 3.1.2                                                        | Model Dynamics                          | 32              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 3.1.3                                                        | Synaptic Stimulation                    | 33              |  |  |  |  |  |  |  |  |  |

|                                                       |      | 3.1.4                                                        | Conclusion                              | 33              |  |  |  |  |  |  |  |  |  |

|   | 3.2   | Struct         | ure and Design Concept                                                                                                          |

|---|-------|----------------|---------------------------------------------------------------------------------------------------------------------------------|

|   | 3.3   | Operat         | tional Transconductance Amplifier and Leakage                                                                                   |

|   |       | 3.3.1          | Ideal Operation                                                                                                                 |

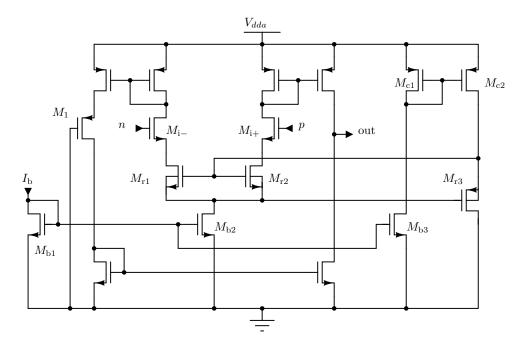

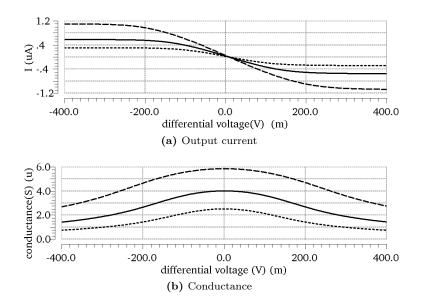

|   |       | 3.3.2          | Circuit                                                                                                                         |

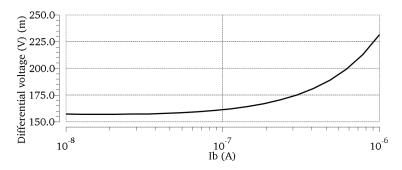

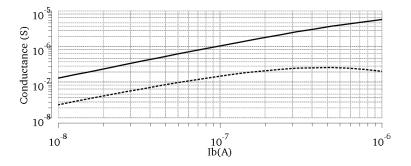

|   |       | 3.3.3          | Simulation Results                                                                                                              |

|   |       | 3.3.4          | Conclusion                                                                                                                      |

|   | 3.4   | Memb           | rane Capacitor                                                                                                                  |

|   | 3.5   | Adapta         | ation                                                                                                                           |

|   |       | 3.5.1          | Circuit and Theory                                                                                                              |

|   |       | 3.5.2          | Real Circuit Behavior                                                                                                           |

|   |       | 3.5.3          | Conclusion                                                                                                                      |

|   | 3.6   | Synapt         | tic Input                                                                                                                       |

|   |       | 3.6.1          | Conductance Shape: Theory 43                                                                                                    |

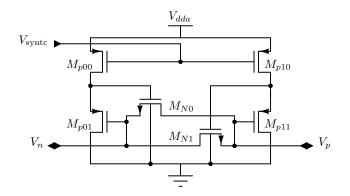

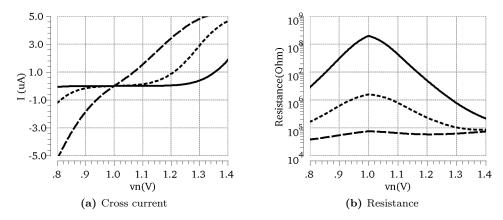

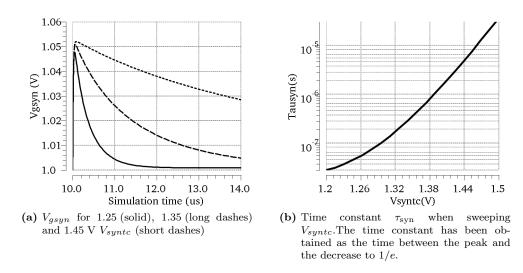

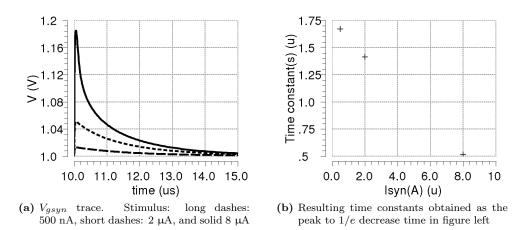

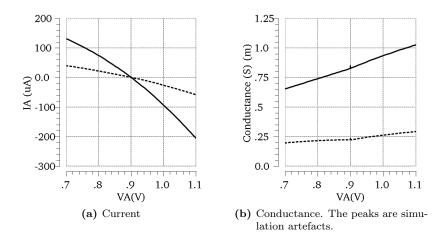

|   |       | 3.6.2          | The Resistive Element                                                                                                           |

|   |       | 3.6.3          | Conductance Shape: Simulated Circuit                                                                                            |

|   |       | 3.6.4          | Weight Saturation                                                                                                               |

|   |       | 3.6.5          | Delays                                                                                                                          |

|   |       | 3.6.6          | Conclusion                                                                                                                      |

|   | 3.7   |                | ential Term                                                                                                                     |

|   | 0.1   | 3.7.1          | Circuit Principle                                                                                                               |

|   |       | 3.7.2          | Voltage Divider   51                                                                                                            |

|   |       | 3.7.3          | Complete Circuit Simulation                                                                                                     |

|   |       | 3.7.4          | Conclusion                                                                                                                      |

|   | 3.8   |                | $\begin{array}{c} \text{Detection} & \dots & $                  |

|   | 3.9   | -              | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                           |

|   |       |                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                            |

|   | 0.10  |                | Circuit                                                                                                                         |

|   |       |                | Simulation                                                                                                                      |

|   | 2 1 1 |                | ut and Stimulation                                                                                                              |

|   | 0.11  |                | Analog Readout   59                                                                                                             |

|   |       |                |                                                                                                                                 |

|   | 9 10  |                |                                                                                                                                 |

|   | 3.12  |                | eterization $\dots \dots \dots$ |

|   |       |                | Biological Parameter Ranges                                                                                                     |

|   |       |                | Parameter Translation                                                                                                           |

|   |       |                | Realization                                                                                                                     |

|   |       | 3.12.4         | Hardware Parameter Summary 65                                                                                                   |

| 4 | Doin  | t Nour         | on Experiments 69                                                                                                               |

| - | 4.1   |                | $ds \dots \dots$          |

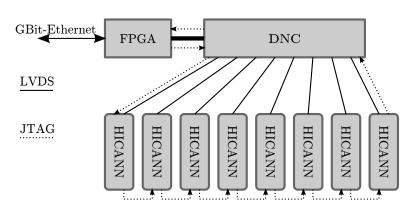

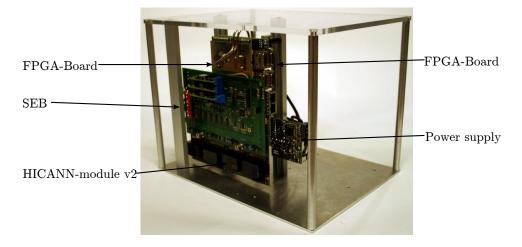

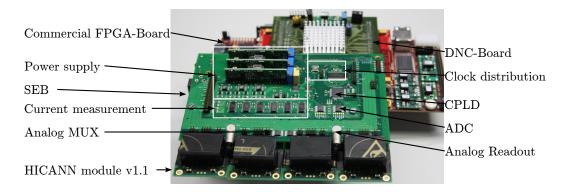

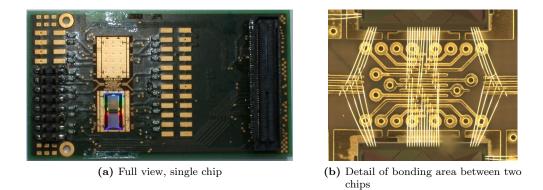

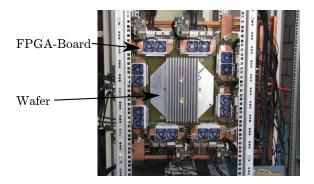

|   | 4.1   | 4.1.1          | Evaluation Setups                                                                                                               |

|   |       | 4.1.2          | Wafer-Scale Setup    72                                                                                                         |

|   |       | 4.1.2          | ASICs                                                                                                                           |

|   | 4.2   | -              | cterization of Output Capabilities                                                                                              |

|   | 4.2   |                |                                                                                                                                 |

|   |       | 4.2.1<br>4.2.2 |                                                                                                                                 |

|   |       |                |                                                                                                                                 |

|   | 4.9   | 4.2.3          | Conclusion                                                                                                                      |

|   | 4.3   |                | nce Emulation                                                                                                                   |

|   |       | 4.3.1          | Methods                                                                                                                         |

|   |       | 4.3.2          | Results                                                                                                                         |

|   |       | 4.3.3          | Conclusion                                                                                                                      |

|   | 4.4         | Characteristic Patterns                                                                                                                   |

|---|-------------|-------------------------------------------------------------------------------------------------------------------------------------------|

|   |             | 4.4.1 Methods                                                                                                                             |

|   |             | 4.4.2 Results                                                                                                                             |

|   |             | 4.4.3 Conclusion                                                                                                                          |

|   | 4.5         | Compartmental Effects                                                                                                                     |

|   |             | 4.5.1 Methods                                                                                                                             |

|   |             | 4.5.2 Results                                                                                                                             |

|   | 4.6         | Fixed Pattern Noise                                                                                                                       |

|   |             | 4.6.1 Methods                                                                                                                             |

|   |             | 4.6.2 Results                                                                                                                             |

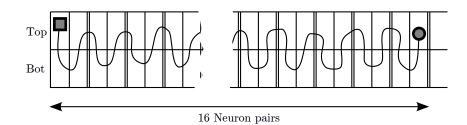

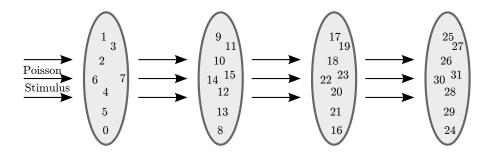

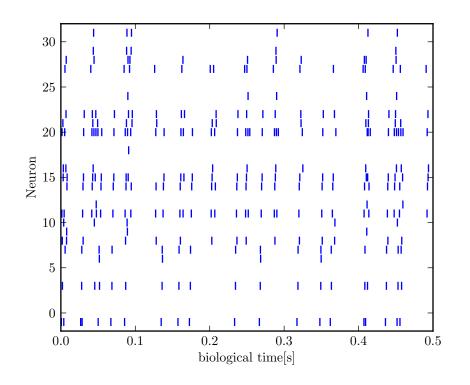

|   | 4.7         | Simple Networks                                                                                                                           |

|   |             | 4.7.1 Methods                                                                                                                             |

|   |             | 4.7.2 Results                                                                                                                             |

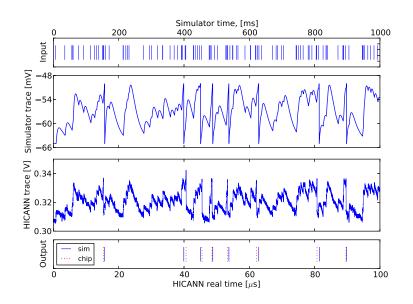

|   | 4.8         | Reproducing Computer Simulations                                                                                                          |

|   |             | 4.8.1 Methods                                                                                                                             |

|   |             | 4.8.2 Results                                                                                                                             |

|   |             | 4.8.3 Conclusion                                                                                                                          |

|   |             |                                                                                                                                           |

| 5 | Disc        | ussion: Single-compartment 101                                                                                                            |

|   | 5.1         | Model Implementation                                                                                                                      |

|   | 5.2         | Measurements                                                                                                                              |

|   | 5.3         | Comparison to Other Implementations                                                                                                       |

| c | N.A., L     | i Community Free Letion                                                                                                                   |

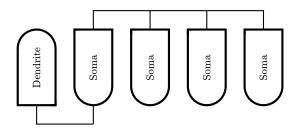

| 6 |             | ti-Compartment Emulation 105<br>Biological Concepts                                                                                       |

|   | 6.1         |                                                                                                                                           |

|   |             |                                                                                                                                           |

|   |             |                                                                                                                                           |

|   |             | 6.1.3 Active Channels $\dots \dots \dots$ |

|   |             | 6.1.4       Which Model to Use?       108         6.1.5       Where to Cut?       109                                                     |

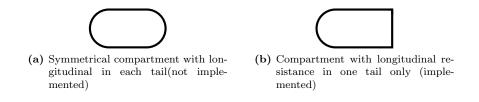

|   | 6.2         |                                                                                                                                           |

|   | 6.2         |                                                                                                                                           |

|   | 6.4         | I I I I I I I I I I I I I I I I I I I                                                                                                     |

|   | 0.4         | I I I I I I I I I I I I I I I I I I I                                                                                                     |

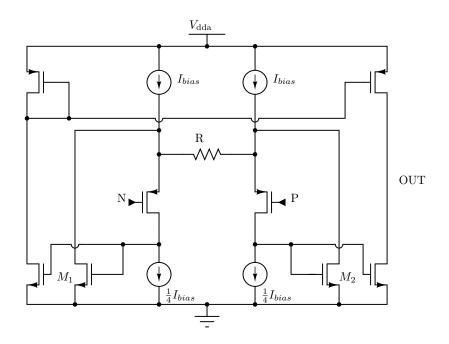

|   |             | 6.4.1       Transconductors       112         6.4.2       Besistive Element       113                                                     |

|   |             |                                                                                                                                           |

|   | 6.5         | 6.4.3 Conclusion                                                                                                                          |

|   | 0.0         | 8                                                                                                                                         |

|   |             | $6.5.1  \text{Spikes}  \dots  \dots  116$                                                                                                 |

|   | 66          | 6.5.2 Implementation                                                                                                                      |

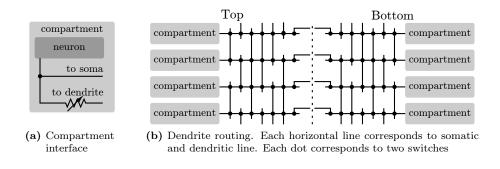

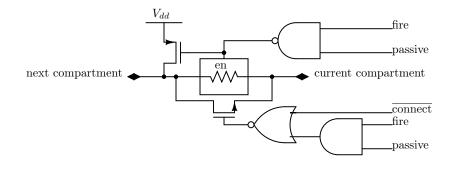

|   | 6.6         | Dendrite Routing                                                                                                                          |

|   |             | 6.6.1         Building Neurons         118           6.6.2         Pass Transistors         119                                           |

|   |             |                                                                                                                                           |

|   | 67          |                                                                                                                                           |

|   | 6.7         | Reset mechanism                                                                                                                           |

|   | 6.8         | Parameterization                                                                                                                          |

|   |             | 6.8.1 Range extraction                                                                                                                    |

|   |             | 6.8.2Parameter translation1226.8.3Realisation123                                                                                          |

|   | 60          |                                                                                                                                           |

|   | 6.9<br>6.10 | Additional Changes                                                                                                                        |

|   | 0.10        | The Multi-Compartment Chip 123                                                                                                            |

| 7 | Mul | -Compartment Experiments 12                                                                                                                          |

|---|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 7.1 | Four Compartment Reference Simulation                                                                                                                |

|   |     | 7.1.1 Methods                                                                                                                                        |

|   |     | 7.1.2 Results $\ldots \ldots \ldots$ |

|   | 7.2 | Action Potentials with Active and Passive Dendrites                                                                                                  |

|   |     | 7.2.1 Methods                                                                                                                                        |

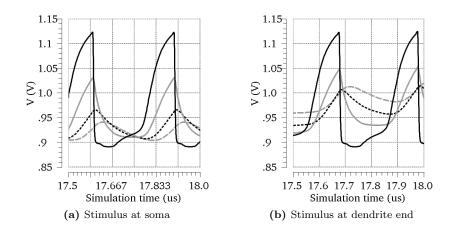

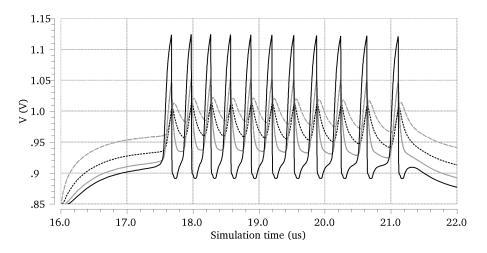

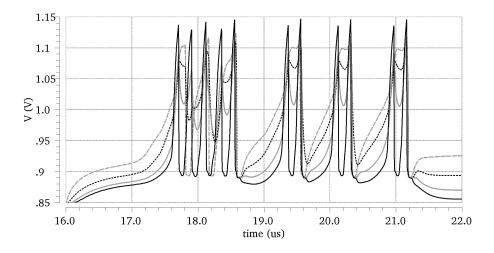

|   |     | 7.2.2 Results $\ldots \ldots \ldots$ |

|   |     | 7.2.3 Conclusion $\ldots \ldots 132$        |

| _ |     |                                                                                                                                                      |

| 8 |     | ssion: Multi-Compartment 13                                                                                                                          |

|   | 8.1 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                 |

|   | 8.2 | $Implementation \dots \dots$                   |

|   | 8.3 | Simulation Results                                                                                                                                   |

|   | 8.4 | Other Implementations $\dots \dots \dots$            |

|   | 8.5 | Conclusion                                                                                                                                           |

| 9 | Ana | g Floating-Gate Memory 13                                                                                                                            |

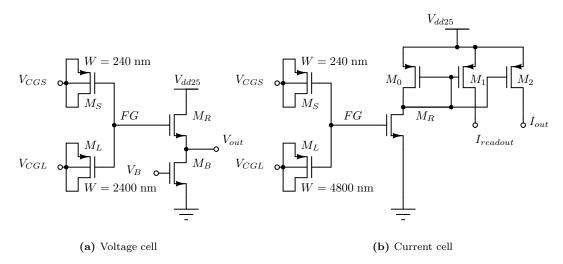

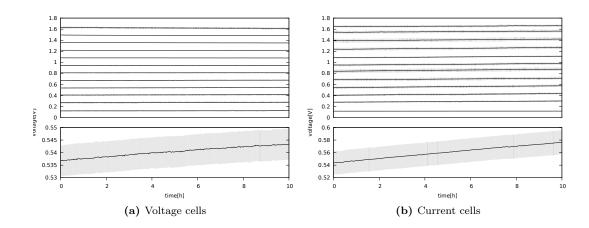

| - | 9.1 | Cells                                                                                                                                                |

|   |     | 9.1.1 Voltage Cells                                                                                                                                  |

|   |     | 9.1.2 Current Cells                                                                                                                                  |

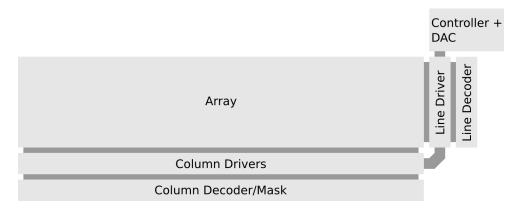

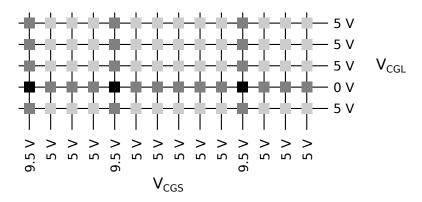

|   | 9.2 | Architecture                                                                                                                                         |

|   |     | 9.2.1 Array                                                                                                                                          |

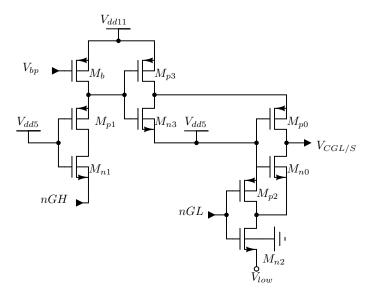

|   |     | 9.2.2 Driver                                                                                                                                         |

|   |     | 9.2.3 Decoder                                                                                                                                        |

|   |     | 9.2.4 Controller                                                                                                                                     |

|   | 9.3 | HICANN Integration                                                                                                                                   |

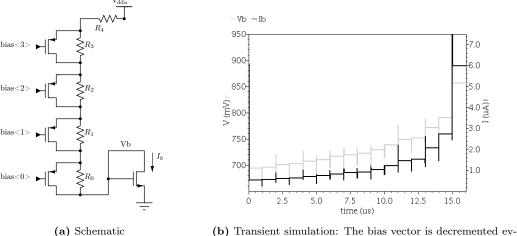

|   | 0.0 | 9.3.1 Biasing                                                                                                                                        |

|   |     | 9.3.2 Level shifter                                                                                                                                  |

|   |     | 9.3.3 Global Parameters                                                                                                                              |

|   |     | 9.3.4 Current Source                                                                                                                                 |

|   |     | 9.3.5 Layout                                                                                                                                         |

|   | 9.4 | Digital Controller                                                                                                                                   |

|   | 0.1 | 9.4.1 Programming Functions                                                                                                                          |

|   |     | 9.4.2 Additional Functions                                                                                                                           |

|   |     | 9.4.3 Detailed Implementation                                                                                                                        |

|   |     | 9.4.4 Test Environment                                                                                                                               |

|   | 9.5 | Sources of Variance                                                                                                                                  |

|   |     | 9.5.1 Parameter Drifts                                                                                                                               |

|   |     | 9.5.2 Crosstalk                                                                                                                                      |

|   |     | 9.5.3 Output Settling and Strobe                                                                                                                     |

|   |     | 9.5.4 Programming Limits                                                                                                                             |

|   | 9.6 | Improvements                                                                                                                                         |

|   |     | 9.6.1 Control, Driver and Decoder Revision                                                                                                           |

|   |     | 9.6.2 Cell Revision                                                                                                                                  |

|   |     | 9.6.3 Biasing Revision                                                                                                                               |

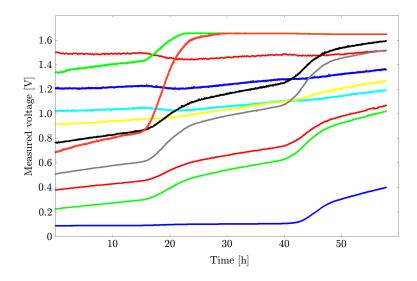

|   | 9.7 | Test Results   150     150   150                                                                                                                     |

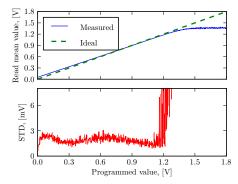

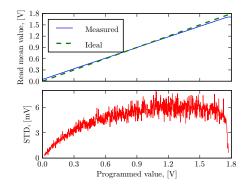

|   | 0.1 | 9.7.1 General Functioning                                                                                                                            |

|   |     | 9.7.2 Programming Schemes                                                                                                                            |

|   |     | 9.7.3 Precision                                                                                                                                      |

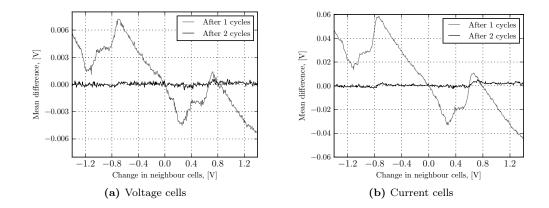

|   |     | 9.7.4 Crosstalk                                                                                                                                      |

|   |     |                                                                                                                                                      |

| 9.8          | 9.7.6                        | Stress Tes<br>New Cells<br>sion |  |  |  |  |  |  |  |  |  |  |  |     | • |  |  |  | • |  |  | 155 |

|--------------|------------------------------|---------------------------------|--|--|--|--|--|--|--|--|--|--|--|-----|---|--|--|--|---|--|--|-----|

| 10 Fina      | 10 Final Remarks and Outlook |                                 |  |  |  |  |  |  |  |  |  |  |  | 157 |   |  |  |  |   |  |  |     |

| Nomenclature |                              |                                 |  |  |  |  |  |  |  |  |  |  |  | 161 |   |  |  |  |   |  |  |     |

| Bibliography |                              |                                 |  |  |  |  |  |  |  |  |  |  |  | 163 |   |  |  |  |   |  |  |     |

| Acknow       | vledgme                      | ents                            |  |  |  |  |  |  |  |  |  |  |  |     |   |  |  |  |   |  |  | 169 |

# Introduction

Apart from the big bang and the question of how the material world is composed, the comprehension of the brain is probably one of the most important matters of today's science or science at any time. Although the brain it-self is as close to each single human as anything can be, even simple networks of neurons are treated as black-boxes without really analytical knowing whats going on. However, even without knowing the sense of detailed network connections, computation can be done with those black boxes[1]. Nevertheless, it might be unsatisfying to work with black boxes. Each single connection probability might be there for a reason in the end. Although hard to model and analyze, intuition tells it will be there for a reason.

Macroscopic modeling can be a successful method to describe a complex system. Probably the best example of this approach is the ideal gas described by properties like volume, temperature and pressure without accounting for the trajectory of each single molecule. However, information which might have been coded in the detailed molecule distribution is lost. For a system like the brain, macroscopic modeling can help but is apparently not sufficient as information is coded by microscopic elements. Macroscopic properties can be activities of complete brain areas or global connectivity probabilities for instance.

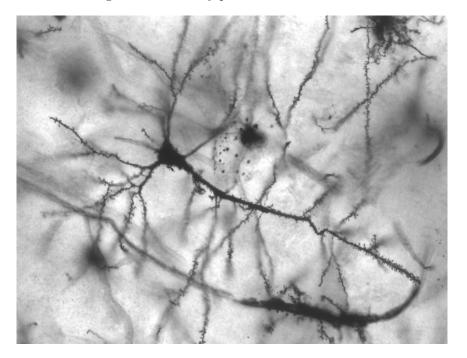

Figure 0.1: Pyramidal neuron from the hippocampus of an epileptic patient.(CreativeCommons Attribution-ShareAlike 2.5 licenced, created by MethoxyRoxy, from [2])

This thesis is about microscopic modeling and emulation of single neurons, which are the Single cells

Macroscopic and microscopic modeling most important cells of the brain. A photograph of such a neuron cell can be found in Figure 0.1. Neurons themselves are complex structures indeed. This raises the question which complexity needs to be retained in a model of the cell. The question is rather similar to the macroscopic microscopic question. A simplified model might forget important features necessary for the function of a brain. A more detailed model on the other hand might enlarge the effort drastically while using potentially unnecessary information. In addition, information necessary for the creation of the complex model might not be available at-all. There is obviously a trade-off.

Point and compartmentalmodels

> Brains and computers

Brains are more stable against errors.

> Saturation of single-core performance

Construction plans

Brain like machines

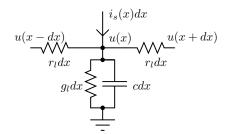

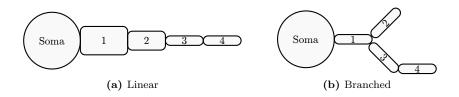

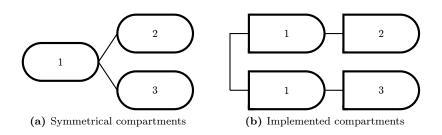

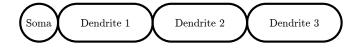

Two different models are used within this thesis. Using a point neuron model, the complete cell is assumed to be equipotential. Consequently, it is modeled as a single point. The second model assumes a relevance of the tree like structures of the neuron called dendrites. Here, the structure of the brain is modelled by the use of several interconnected so called compartments. Compartments are sections of the cell which are assumed equipotential.

The brain is different to a digital computer indeed. A classic single-core of a micro processor sequentially computes in nano seconds. Data and instructions are fetched from a memory; a result is computed and written back into memory. The brain on the other hand computes massively parallel in micro seconds.

The total energy consumption of the Human Brain and a current digital computer chip is in the same order of magnitude. However, the actual computational power is hard to compare as both systems are best in different tasks.

Cutting a wire or adding one in a digital computer chip usually results in a wrong behaviour or a completely broken chip. In contrast, a single connections or cell from the brain will hardly cause any harm due to redundancy of the massively parallel system. In fact, dying cells or connections are very common in the brain. This tolerance against errors is a major advantage of the brain in comparison to a computer.

In the last decade, Moore's law is saturating for single core performance due to the energy necessary for computation. However, the work-around is to use multi-core processors instead of single cores to achieve a continuous rise of computational power. Nevertheless, there will be limits for the classical van Neumann computer structure. A new kind of computer based on the structure and principles of the brain might be an alternative.

When building a computer, a complete schematic is necessary, to retain a certain working system. Computers are build as completed structures with the program and the memory status as its dynamical variables. The wiring of the brain is dynamic in contrast. There is no such thing as a complete construction plan. Connections are evolving. Learning occurs. There is no strict devision between hardware and software.

When building a brain-like machines with dynamical connections, the complete function of the brain and its networks does not need to be known from the beginning as long as realistic learning mechanisms are implemented. Indeed, the machine can be a tool to understand the function of the brain. In fact, special hardware based on the structure of the brain can enable neuroscientific experiments which have not been possible so far due to a lack of computational power for computer simulations.

This thesis describes how to build neurons on a standard micro-chip using transistors. The approach is called emulation. Instead of simulating a model on a digital computer, the model dynamics are rebuild using analog circuits. The subject is called Neuromorphic Engineering[3].

# Structure of this document

This dissertation is structured into 10 chapters. Here I will give a brief overview.

- 1 Neuroscience, Circuits and Neuromorphic Engineering: This chapter gives an introduction into the interdisciplinary field of Neuromorphic Engineering. I start with a brief introduction into neurons, synapses, plasticity. Neuron models are introduced next. Subsequently a contrast is given by micro-chips and the description of transistors. After these basics, the step to an emulation and Neuromorphic Engineering is done. I conclude the chapter with the discussion of different design approaches and implementations from literature. This chapter is very important for nomenclature definitions.

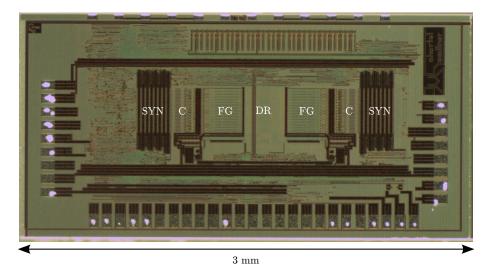

- 2 Neuromorphic Environment: I give an introduction into the system, the presented circuits are nested in. A top-down approach is taken during presentation. The HICANN microchip is introduced here for instance.

- **3 Point Neuron Emulation:** Starting with the introduction of the implemented model, now each single circuit part of the point-neuron implementation is described and discussed.

- 4 Point Neuron Experiments: This chapter describes some experiments performed with the point-neuron circuit. I present a basic benchmark experiment and some typical patters produced by the circuit for instance. A focus is laid on the analysis of fixed pattern noise. The chapter is concluded by a small network experiment.

- 5 Discussion: Single-Compartment

- 6 Multi-Compartment emulation: At the beginning of this chapter, the concept of compartmental modeling and the model choice are discussed. Furthermore, implementations from literature are presented. Subsequently, the changes necessary for a multi-compartment implementation are presented first in an overview and in detail next.

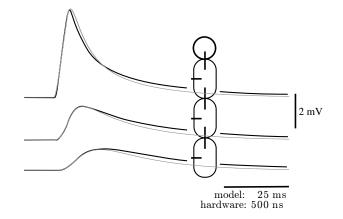

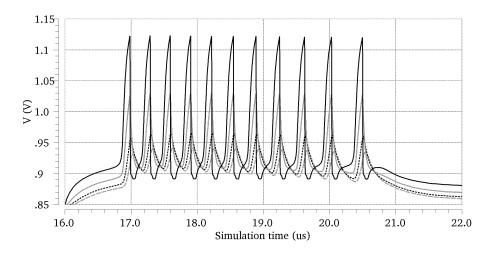

- 7 Multi-Compartment Experiments: Two small experiments are presented as simulations. The first experiments covers passive attenuation of dendritic stimulation. Subsequently, action-potential generation and propagation in the dendrite is observed.

- 8 Discussion: Multi-Compartment

- 9 Analog Floating-Gate Memory The immense parameterizability of the designed neuron circuits is only possible due to the use of analog floating-gate memory. These memory cells and the necessary periphery circuits are presented here. The chapter is concluded with some measurement results.

- 10 Conclusion and Outlook

This chapter provides the foundation to the subjects of this thesis. I start with a very brief introduction of the brain and neurons in particular as its main components. Subsequently, I introduce the Hodgkin and Huxley neuron model followed by the leaky Integrate-and-Fire model which is enhanced to reproduce real neurons' behaviour. The next section gives background on the main device of a microchip which is the transistor. The concept of emulation is an alternative procedure to the analytical solution or the simulation of a system. It is introduced next. In the same section, I introduce the work field of Neuromorphic Engineering. At last, to get an overview about the status in literature, design approach considerations and different neuron implementations are discussed.

# 1.1 Biological Substrate

The understanding of the brain and its computational powers is is one of the main topics of the work presented in this thesis. However, what is the brain? On an abstract level, the brain is a collection of specialized cells called neurons which are interconnected by synapses to form a large and complex network.

Information is interchanged by electro-chemical signals called action potentials or spikes which are the binary time continuous output signal of a single neuron. The brain is electric. Neurons are the basic internal information processing units of the brain. Three dimensions can be used for the positioning of individual neurons and the routing of connections<sup>1</sup>.

Each neuron has an internal membrane voltage V created by differences in ion concentration inside and outside of the cell. This voltage is referred to as membrane potential. There can be differences along the membrane surface. When a neuron receives an action potential from another neuron via one of its synapses, channels are opened allowing ions to flux into the neuron. These ions raise or lower the membrane potential. If the voltage of a neuron reaches a certain threshold, it creates an own action potential which is transported to other neurons. An action potential is a large transient membrane voltage spike.

This is a very brief conceptional introduction only. For details see [4] for instance.

## 1.1.1 Neurons

Neurons are cells. Cells are basically closed units surrounded by a lipid bi-layer. Lipids are molecules with a hydrophilic and a hydrophobic end which tend to build bi-layers with the hydrophobic end in the middle when exposed to water. This lipid bi-layer constitutes a membrane that divides the interior and the exterior of a cell. A lipid bi-layer alone close to an insulator. It can be modeled as a capacitor. However in biological cells, a variety of channels is present, which allow for passive and active transport through the cell.

Information processing

A "closed" system

<sup>&</sup>lt;sup>1</sup>Indeed, the cortex is organised in layers which can be thought as two dimensional. However, these layers as well as neurons are spacial objects.

Ions and reversal

Inside and outside of the cell in the brain are ions. The most important ones for the work presented here are potassium  $(K^+)$ , sodium  $(Na^+)$ , calcium  $(Ca^{2+})$  and chlorine (Cl-). potential The concentration of the these ions inside and outside of the cell is different. However, this concentration gradient tends balanced through open ion conducting channels. The balancing creates a voltage difference between the interior and the exterior due to the ion charge. Concentration gradients of ions are counterbalanced by this voltage differences. In equilibrium the dedicated voltage for an ion type is called Nernst Potential or reversal potential. A typical value for the reversal potential of the potassium channel of a cell is -89 mV [4] for instance.

Sodium concentrationgradient

Due to large charged macro molecules within the cell the ion concentration inside the cell tends to be larger than outside the cell. However, a larger ion concentration would cause the water influx by osmosis. If no mechanisms where to counterbalance this this influx the cell could burst[4]. Nevertheless, we know that it does not burst. In animal cells the main mechanism are special active channels constantly pumping sodium ions out of the cell. Consequently, there is a large sodium concentration gradient between the exterior and the interior of the cell and hence a large tendency of sodium to enter the cell. The reversal potential of sodium is 50 mV.

For neurons, this omnipresent gradient is very important. Synapses can mediate Ion flux which changes the membrane potential. If the membrane voltage reaches a certain threshold voltage<sup>2</sup>, special voltage-gated channels for sodium ions open and the membrane voltage sharply rises. Action-potentials are created in regions of high channel densities. The rise of the action potential is propagated avalanche. However, after a certain delay, the sodium channels close again and slower voltage-gates potassium channels open pulling the membrane down again. For a certain time, no further action potentials are possible as the equilibrium concentrations have to be maintained. This time span is called absolute refractory period. Due to their shape, action potentials are also called spikes. The creation of an action potential is referred to as spiking or firing. A spiking neuron fires spikes respectively action potentials.

Spacial structure

Generating action

potentials

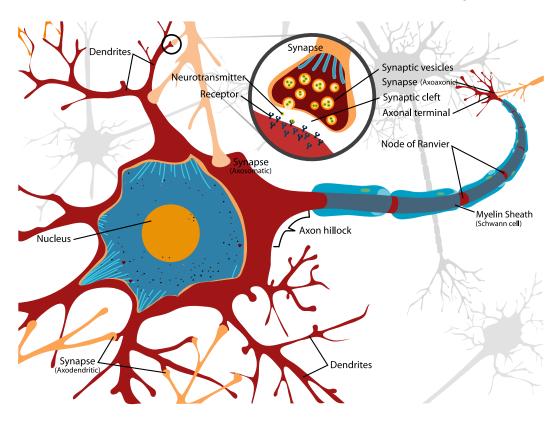

So far, our neuron did not have a special spacial shape. An exemplary schematic of a neuron can be found in Figure 1.1. Synapses from other neurons usually connect at the dendrites which are the tree like structures growing out of the cell body. The cell body is called soma. The axon hillock is the region with the highest concentration of voltage-gated channels. Action potentials are usually initiated in this region. They are propagated along the axon inducing ion influx into other neurons via synapses. A smaller action potential might also be back propagated into the dendrites. The axon can be surrounded by myelin sheath which accelerate the propagation by locally insulating the membrane. The section between the myelin sheaths is called node of Ranvier and is a region of high active channel density restoring the attenuated action potential.

## 1.1.2 Synapses

Synapses are the interface between neuron. There are electrical synapses directly interconnecting membranes and chemical synapses using molecules called neuron transmitter as mediator. Here I will concentrate on chemical synapses however.

The synapse at the end of the presynaptic neuron reaches close to the membrane of the postsynaptic neuron. The space separating the two neurons is called synaptic cleft (See Figure 1.1). When an action potential arrives at the synapse,  $Ca^{2+}$  enters the synapse at the postsynaptic neuron. So called vesicles carrying neurotransmitters are  $Ca^{2+}$  triggered to combine with the postsynaptic neuron's membrane and release the neurotransmitters into

Neurotransmitter

$<sup>^{2}</sup>$ The threshold can be variable.

1.1 Biological Substrate

Figure 1.1: Schematic of a neuron. (Reduced version of public domain figure from [2])

the synaptic cleft.

In the synaptic cleft at the postsynaptic neurons site are transmitter-gated-channels in a high density. These channels open a conductance if a neurotransmitter molecule is received. The conductance is selective for different types of ions and can inhibit or excite the postsynaptic neuron. Excitatory synapses mainly conduct Na<sup>+</sup> for instance while inhibitory synapses conduct Cl- for instance. The voltage response of the postsynaptic neuron is referred to as postsynaptic potential (PSP).

The neurotransmitter GABA<sup>3</sup> is the main transmitter for fast inhibitory synapses [5]. The conductance can be described by a rapid opening conductance which is exponentially decaying with a time constant of 5 ms. Excitatory transmitters are NMDA<sup>4</sup> and AMPA<sup>5</sup> for instance. AMPA synapses can open a conductance with a sharp exponential rise with a time constant below 10  $\mu$ s which is followed by a decay with 1.5 ms [5]. The behavior of NMDA synapses is more complicated however as they are membrane voltage dependent. They are stronger for higher membrane potentials [5]. A role of NMDA synapses can be the amplification of synaptic signals in apical dendrites [6].

A synapse's capability of changing the membrane potential of the presynaptic neuron is referred to as synaptic efficacy, or strength.  $Transmitter-gated \\ channels$

Different synapses

$<sup>^3\</sup>gamma\text{-aminobutyric}$  acid

<sup>&</sup>lt;sup>4</sup>N-methyl-D-aspartate

$<sup>{}^{5}\</sup>alpha$ -amino-3-hydroxy-5-methyl-4-isoxalone propionic acid

## 1.1.3 Plasticity

In fact, the synaptic connections and even the morphology of the neuron is not static. This temporal change is referred to as plasticity. Plasticity mechanisms can change the synaptic efficacy – which is a measure of the effect of a synapse on the postsynaptic neuron. Furthermore, new synapses are constantly created while other synaptic connections disappear. Here I will discuss the phenomenology of plasticity occurring on short time scales (hundreds of microseconds) [7,8] and spike-timing dependent plasticity (STDP).

The temporary change of synaptic efficacy depending on the previous reception of action potentials is called short term plasticity. Typically, the synaptic efficacy is increased or decreased at each single spike. If no further action potentials are received, the efficacy returns to a steady state efficacy. These mechanisms can for instance amplify low frequency stimulus or attenuate high frequency stimulus [7,8].

A very intuitive kind of plasticity is given by Hebbian Learning [9]. If a synapse is responsible for the firing of the postsynaptic neuron, its efficacy is increased. On the other hand, if the postsynaptic neuron fires acausally, meaning without any influence of the corresponding synapse, the efficacy is decreased.

A Hebbian Learning mechanism with real neurons has been confirmed by Bi and Poo [10]. It is called spike-timing dependent plasticity(STDP). The change of synaptic efficacy is weighted with an exponential function depending on the timing difference of the postand presynaptic spikes. Causal events result in a strengthening of the synapse. In addition, beyond Hebbian Learning, acausal events decrease its efficacy.

## 1.1.4 Typical Cortical Neuron Behavior

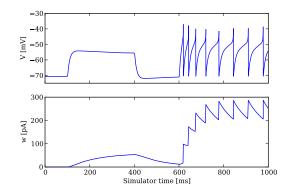

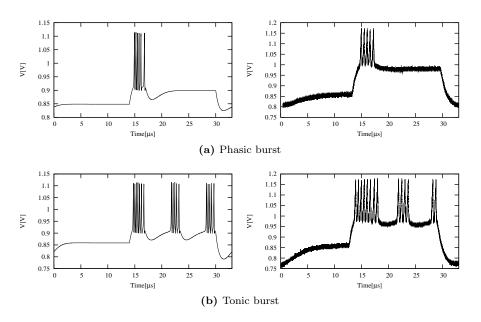

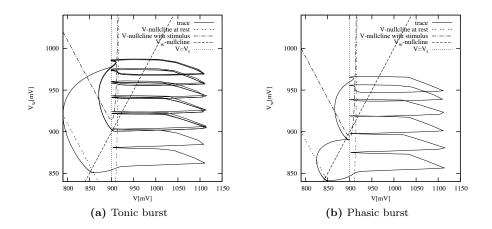

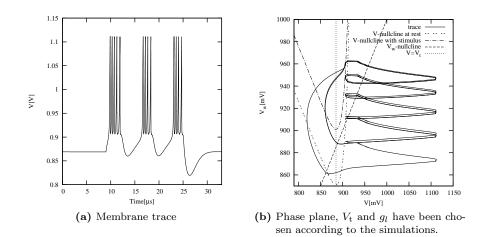

Here, I will discuss some typical neuron behaviors which are often referred in this thesis. In particular spike-frequency adaptation and bursting and derived behaviors. Indeed, there are many more possible patterns. For a comprehensive collection see [11] or Figure 4.11 in this work. The nomenclature follows [11] and [12].

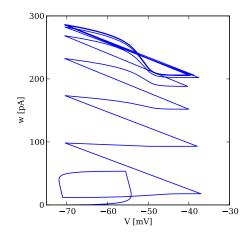

When a neuron is stimulated by an adequate current, it starts creating action potentials. After a short delay, another action potential will be created. This delay however can be adapted. At the beginning, the neuron spikes with a higher frequency which decreases with each additional spike until an equilibrium is reached. The frequency is adapted. This effect is called spike-frequency adaptation. An extreme case of spike-frequency adaptation would be the creation of one single spike at the beginning an no further action potentials. This effect is called phasic spiking. A neuron spiking with a regular frequency is called tonic spiking.

Some neurons tend to fire small groups of spikes with a high frequency. These groups are called bursts. The corresponding behavior is referred to as bursting. If bursts are created with a constant frequency, it is called tonic bursting. A single burst is a phasic burst. When bursts and single spikes are created, the behavior is called mixed-mode.

Bursting as well as single spikes can occur with a delay after the onset of stimulus.

## 1.1.5 Measurement Capabilities

In vivo, in vitro Measurements can generally be done in vivo, or in vitro. An in vivo measurement is carried out in an living animal. In vitro experiments are done with insolated cell cultures in a test-tube for instance. While the access to neurons with a defined stimulus is not possible in vivo by virtue of network activity, in vitro measurements miss the surrounding input of the network. When working in vivo, the model animals have to be anesthetized, which has an effect on the observed neurons.

Short term plasticity

Hebbian Learning

STDP

${\it Spike-frequency}\\ {\it adaptation}$

Bursting

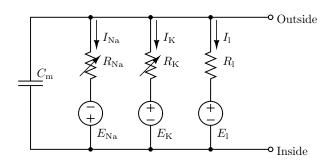

Figure 1.2: Schematic of the Hodgkin Huxley neuron model[19].

Several neurons can be measured in vivo using arrays of electrodes [13]. However, the Some methods measured neurons a random sample of all neurons. Detailed recordings and stimulations in vivo and in vitro are possible using the patch-clamp method [14] for instance. Furthermore, special molecules reflecting the membrane voltage in their florescence behaviour when excited can be used to measure the mean voltage of groups of neurons or even local voltages in dendrites[15].

A common approach to understand single cell or defined network behaviour is carried out Simulation using simulations in a neural simulator like the simulators NEST[16] or Neuron [17].

## 1.1.6 High-Conductance State

The high conductance state, as introduced in [18] for instance, is the state of a neuron receiving large amounts of synaptic input from other neurons. It is the suspected typical state of neurons measured *in vivo* due to the high number of connections from other neurons. A contrast is given by a neuron measures *in vitro*, where surrounding network activity is not given. The high synaptic input opens conductances enlarging the total conductances of the neuron. Consequently the nomenclature is high-conductance state.

# 1.2 Single Cell Modeling

Here I discus different neuron models. Starting with the complex mother of all neuron models - the Hodgkin Huxley Model[19], the simple phenomenological Integrate-and-Fire model is presented and enhanced by adaptation and positive feedback.

# 1.2.1 The Hodgkin Huxley Model

The Hodgkin Huxley Model (HHM), published by Alan Lloyd Hodgkin and Andrew F. Huxley in [19], is a sa model of the squid giant axon. The size of this axon allows for better experimental access. In particular, it has a diameter between 0.5 mm and 1 mm and a length of several centimeters[4].

In their experiments, Hodgkin and Huxley cut the axon from the cell body and retain an axon tube. To ensure a defined experimental setup the plasma inside the tube is replaced by a defined solution. The outside solution is usually sea water. This way ion concentration dependency measurements are possible[4].

To measure current and voltage dependencies, a long electrode is placed inside the axon. Additional electrodes are placed outside the axon.

Observed subject

A schematic of the resulting model is presented in Figure 1.2. The  $I_l$  branch is the passive Schematic leakage current which is ascribed to chloride and other ions in [19]. The adjustable conductances are actually voltage dependent conductances with a complex temporal deviation. Action potentials are created by these channels as described in Section 1.1. The description of the voltage gated Sodium and Potassium channels is the major accomplishment of the HHM

> Hodgkin and Huxley describe the conductances using an approach of so-called gating variables n, m, and h. The resulting conductances are:

$$g_{\rm K} = \bar{g}_{\rm K} n^4, \text{ and} \tag{1.1}$$

$$g_{\mathrm{Na}} = \bar{g}_{\mathrm{Na}} m^3 h. \tag{1.2}$$

The gating variables and there exponentiation can be understood as different conditions Gating variables necessary for an open channel. They are time varying and described by differential equations according to

$$\frac{dn}{dt} = \alpha_n (1-n) - \beta_n n. \tag{1.3}$$

The alphas and betas are voltages dependent but time independent properties. They are determined by measurements.

Action potential The gating variable h is one for small membrane voltages and decreases at about 50 mV. mgeneration on the other hand rises for voltages above -25 mV and reaches one close to 50 mV. However, the key is the temporal deviation. h reaches its final value much slower than m. Nevertheless, in an action potential, h blocks sodium influx enabled by m after a short time. The actual temporal course is complicated as  $\alpha$  and  $\beta$  are voltage dependent.

> n opens for large membrane voltages with a slow time constant and pulls down the membrane back to the resting potential.

The HHM describes axons of special neurons of squids. When analysing cortical neurons from the human brain, further channels have to be added for realistic modeling. In particular, calcium channels and calcium-concentration-dependent potassium channels can be important.[5].

# 1.2.2 The Integrate-and-Fire Model

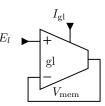

Each gating variable adds another differential equation to the HHM. It is neither optimized HHM not optimal for simulations for computer simulations, nor for model analyses. In [5], the authors describe how to retain the HHM dynamics using only two variables. I skip this step and directly come to the reduced phenomenological leaky Integrate-and-Fire neuron model (IIaF) [20] which is a drastic simplification.

> Basically, this model assumes that all spikes are equal. Consequently, there is no information in the shape of a spike and it can be omitted. In the IIaF, the potassium and the sodium channels have been removed from the HHM retaining only the leakage conductance. The result is a leaky integrator – a capacitor with a conductance to a leakage potential connected in parallel. It can be described by a single dynamic variable - the membrane voltage:

$$C_m \frac{dV}{dt} = g_l (E_l - V) + I.$$

$$\tag{1.4}$$

However, there is still the stimulus current. If the membrane voltage crosses a threshold  $\Theta$ Reseting it is reset to a certain reset potential  $V_{\text{reset}}$ , which is usually equal to the leakage potential. Thus, the membrane time course is not continuous.

Limitations

Removing active

channels

## 1.2.3 Adaptation

High-threshold voltage-gated calcium channels in cortical neurons allow the influx of  $Ca^{2+}$  Calcium channels into the neuron. In addition, there are low-threshold voltage-gated calcium channels allowing calcium influx at smaller voltages. Those can create a pull-up of the membrane if inhibiting input is removed[5].

Calcium concentration in a neuron is low and strongly interfered by calcium influx, while Calcium modulatedglobal sodium and potassium concentration stays nearly constant. Furthermore, there are calcium-concentration-gated K<sup>+</sup> channels [5]. Consequently, rising calcium concentration can induce a negative feedback onto the rising membrane potential.

This results in effects like spike-frequency-adaptation. When stimulated with a current pulse, the spike frequency is lowered with each action potential due to the enlarged calcium concentration.

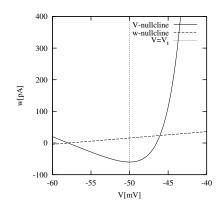

To account for this effect, a second variable can be added to the IIaF. The adaptation A second variable variable, or slow variable w [21, 22]. The new pair of equations is:

$$C_m \frac{dV}{dt} = g_l (E_l - V) + w + I \tag{1.5}$$

$$\tau_w \frac{dw}{dt} = a(E_l - V) - w.$$

(1.6)

In the steady state, w add another conductance a to the leakage potential. However, if the membrane is released from a lower potential very fast, the adaptation variable might not be able to follow due to its large time constant  $\tau_w$  (Its magnitude is 100 µs.). This way, the membrane reacts different to fast changing signals which is a behavior observed in cortical neurons [11]. Another effect caused this way is called inhibitory rebound. The removal of an inhibitory signal can cause an action potential. In addition to subthreshold effects, w needs to be enlarged at every action potential – this results in spike-frequency adaptation.

However, the addition of the adaptation variable is a phenomenological approach. It enhances the capabilities of the IIaF model to reproduce the behaviour of cortical neurons. Nevertheless, the direct biological correspondence with the calcium concentration is weak. In [21] it is referred to account for activation of  $K^+$  and the deactivation of  $Na^+$  channels.

## 1.2.4 Positive Feedback

Due to the removal of the voltage-gated channels, the membrane dynamics of the IIaF model cannot produce real spikes. Spikes might look similar. However, the onset of the spike can change the neurons dynamics completely as positive feedback is added by the voltage-gated sodium channels. The positive feedback can amplify stimulus close to the threshold for instance. In addition, the spiking threshold is more smooth this way.

Izhikevich used a quadratic feedback of the membrane voltage for instance to improve the capabilities of his model[21].

# 1.3 Technical Substrate

A microchip is the technical substrate of this thesis. Microchips are semi-conductor circuits. *Microchips* Indeed, microchips are apparently electric. Their main computational elements are transistors which have a far less complexity and function in comparison to a neuron. In addition to the active devices, components like fixed resistors or capacitors are available for circuit

Phenomenological approach

Re-adding $Na^+$ -channels

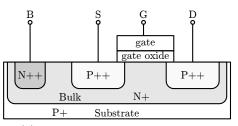

(a) Cross section of a PMOS transistor

Figure 1.3: Cross-section of a PMOS transistor. P+, P++, N+, and N++ denote positive respectively negative doping concentrations of different levels.

implementation. Capacitors can be implemented most precisely using two opposing metal plates for instance.

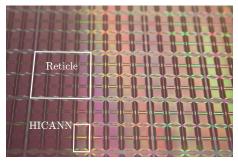

Usually microchips are produced on silicon wafers which are cut into the individual chips. These wafers are referred to as substrate. Devices are created using doting, evaporating and etching technologies. Fine structures can be produced using lithography techniques. Although, several different layers exist on a microchip, the basic structure of chips is usually two dimensional. Each device on a microchip is different as transistors are real physical devices exposed to production variations. These variations are called fixed-pattern noise.

The microchips used within this thesis are Application Specific Integrated Circuits (ASIC). These chips usually produced in a small small volume to solve special problems. For prototyping, our chips are produced with other designs on a single silicon wafer to save production cost. This design approach is called Multi-Project Wafer (MPW) prototyping.

Here I will give a very short introduction on transistors and the schematic nomenclature and some basic circuits used within this dissertation. Basic common circuits like logic gates, transmission gates are assumed as known and not introduced hence. For further introductions into circuits see e.g. [23–26].

## 1.3.1 Transistors

MOSFET The transistors discussed here and used in the circuits presented in this thesis are metaloxide-semiconductor field-effect transistors (MOSFET). There are two basic devices PMOS and NMOS (p respectively n-type metal-oxide-semiconductor device). The beginning letter denotes the charge of the conducting charge carriers in the corresponding device.

> The cross-section of a p-type MOSFET in a positive doted substrate is presented in Figure 1.3. Current flux between source (S) and drain (D) is maintained by the Gate (G) potential. The bulk contact (B) can be ignored for now. The isolating gate oxide is usually very thin (several atom layers), so there is a strong capacitive coupling between the gate and the area below the gate. The area below the gate oxide is called channel area. In the N areas, the charge carriers are given by additional electrons of the doting atoms which do not fit into the structure of the silicon. On the other hand, missing electrons are the positive virtual charge carriers in the P areas. They are called holes.

At first, I describe the case where, S, G and D are at the same voltage level. There are two opposing PN-junctions between source and drain. At these junctions, electrons from the negative doping atoms of the N+ area diffuse into P++ area and recombine with the atoms used for P++ doping. This way, positively charged ions are left in the N+ area while negatively charged ions are left in the P++ region. The ionized areas are called depletion zone. There is a barrier voltage between the ionized areas.

ASIC

Production

MOSFET structure

PN-junctions

Now, we set the drain potential D at a negative voltage e.g. -1.8 V. The depletion zone Diffusion at the drain junction grows and blocks electrons from D from entering the channel area. In addition, the depletion zone is enlarged. However, some electrons have enough energy to diffuse into the channel. Concentration gradients enhance the diffusion process in the channel. Electrons are pulled to the source by the source junction. A very small diffusion current can flux.

Adding a small negative voltage at the gate created a depletion zone below the gate. The Subthreshold ionized atoms in the depletion zone balance the negative gate voltage. Below a certain threshold voltage  $V_t$ , the diffusion current in the channel rises exponentially with the falling gate potential:

$$I_{\rm DS} = I_0 e^{\frac{-\kappa v_{GS}}{u_t}}.$$

(1.7)

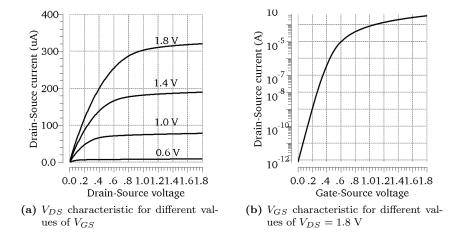

Here  $I_0$  is a constant current,  $u_t$  is the thermal voltage and  $\kappa$  is the subthreshold slope factor.  $I_{\rm DS}$  is the current between the terminals D and S and  $V_{\rm GS}$  is the voltage between the terminals G and S. For a detailed derivation see [24]. The exponential rise of the drain-source current of an NMOS transistor below the threshold voltage can be seen in Figure 1.4 b)

Figure 1.4: Simulation of an NMOS transistor.

For negative gate voltages below the threshold voltage, inversion occurs. The positive Inversion charges of the ionized doting atoms cannot compensate the gate potential anymore. Although, the charge carrier of negative doted silicon are electrons, free holes become available in the inversion layer. Now, current can be conducted by drifting holes in the channel now. The current is roughly proportional to the square of the gate-source voltage. This operating region is called strong inversion. It is the usual stable operation region of a MOSFET.

The contact B in Figure 1.3 is the connection to the bulk of the transistor. The bulk potential influences the effective threshold voltage drastically. This issue is called body effect. In some analog applications the bulk potential needs to be maintained to reduce the body effect. In Figure 1.3, the bulk is an n-well which is a negative doping area on the p-doted substrate. N-wells are used for the creation of PMOS devices. Several PMOS devices can share an n-well to allow a more compact design.

NMOS bulk N-mos devices are usually created directly on the positive doted substrate. Consequently, they share a bulk potential. However, special devices using an isolated p-well inside an n-well are available but area inefficient.

The bulk potential

13

$V_{DS}$  characteristic

Ohmic region

So far, the drain-source voltage has been kept constant. I will discus the drain-source voltage characteristic of a MOSFET now. It is shown in Figure 1.4 b).

For absolute drain source voltages below  $|V_{GS} - V_t|$ , the velocity of the moving holes in the PMOS respectively electrons in the NMOS transistor can still be increased with rising drain source voltage. In this region, called ohmic region or triode region, the drain-source current is roughly proportional to the drain-source voltage:

$$I_{DS} = K' \frac{W}{L} \left( (V_{GS} - V_t) V_{DS} - \frac{V_{DS}^2}{2} \right)$$

(1.8)

See [26] for instance. K' is a process parameter, W is the channel width, and L is the length of the channel. However, in fact there is a smooth transition to the saturation region which comes next. A linear dependency can only be assumed for small values of  $V_{GS}$ .

Saturation region

In the saturation region, the current can hardly be enlarged by larger drain-source voltages as interaction with the fixed atoms decelerated the charge carriers. However, larger voltage can shrink the channel itself and cause a small increase of the current this way. This effect is called channel length modulation. In the saturation region, the current can be described by:

$$I_{DS} = \frac{K'}{2} \frac{W}{L} \left( V_{GS} - V_t \right)^2 \left( 1 - \lambda V_{DS} \right).$$

(1.9)

For further details, compare [26].  $\lambda$  is called channel length modulation parameter. For small transistors channel length modulation has a drastic influence. Due to the flat characteristic in saturation, a transistor biased in this region can be used as a current source.

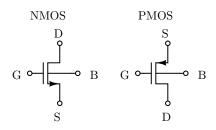

The used schematic symbols for MOSFET devices are shown in Figure 1.5. When they are used, the bulk connection is omitted in most cases however. If no bulk connection is shown, the bulk of NMOS devices is connected to the ground potential while the bulk of PMOS devices is connected to the corresponding power supply.

Figure 1.5: MOSFET schematic symbols

## 1.3.2 Basic Transistor Circuits

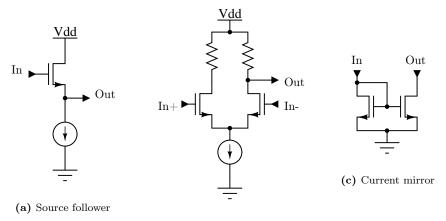

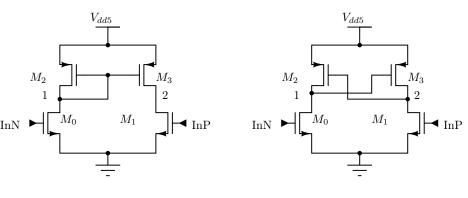

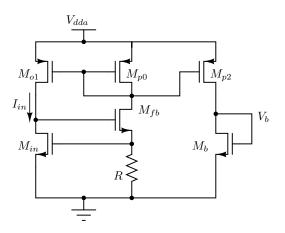

Here, I will briefly introduce source followers, differential pairs and current mirrors in the following. The circuits are shown in Figure 1.6.

A source follower consists of a single transistor and a current source, which is usually implemented by an additional transistor operated in strong inversion. A schematic is presented in Figure 1.6 a). The output voltage follows the input voltage as the gate source voltage is mainly defined by the cross current of the transistor. An application of the circuit is in impedance converter. The input voltage might be driven by a weak driver which is amplified by the circuit to drive larger loads. In this thesis, the circuit is used for the creation of biasing voltages in addition.

Nomenclature

Source follower

(b) Differential pair

Figure 1.6: Basic transistor circuits

The next circuit is a differential pair (Figure 1.6 b). Differential input voltages are amplified. When both input voltages are equal, half of the current from the current source will flow through each of the two transistors causing a voltage drop at the resistors. Subsequently, if a differential voltage is applied, less current will flow through one branch, while the same amount more current will flow through the other. For small differential voltages, the input voltage difference is linearly amplified. Indeed, the total current is limited by the current supplied by the current source. Furthermore, the characteristic of a MOSFET is not linear. Consequently, the linear range is limited. A differential pair will be discussed in more detail in Chapter 3.

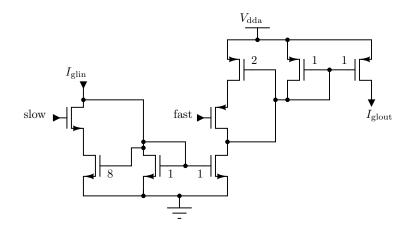

A current mirror is an essential circuit in analog circuit design. The circuit can be found *Current mirror* in Figure 1.6 c). It mirrors an input current to the output. A single mirror can have several outputs to create further incarnations of a biasing current. The gate-source voltage of both transistors is given by the input transistors. Consequently, if both transistors are equal and without channel length modulation, the output current matches the input current.

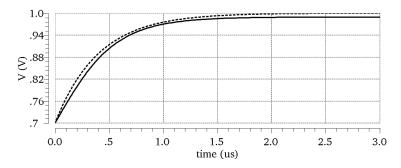

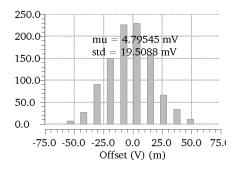

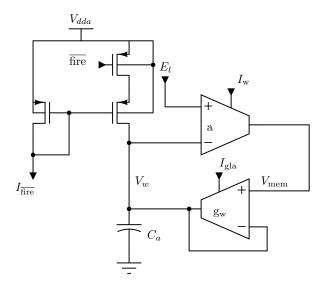

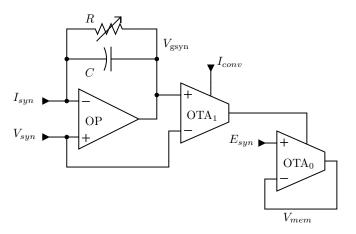

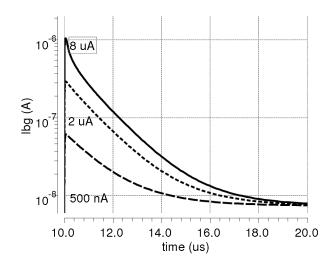

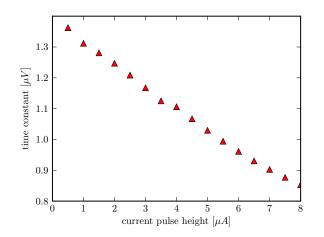

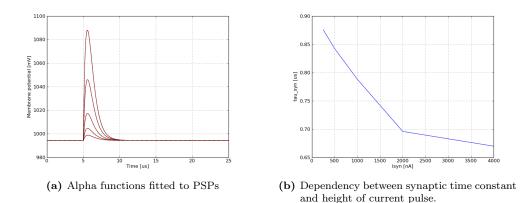

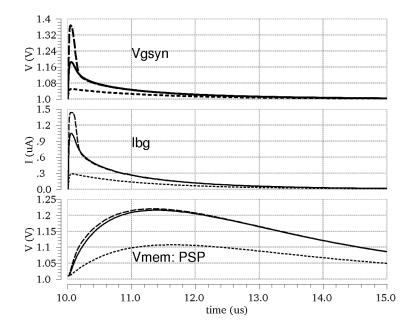

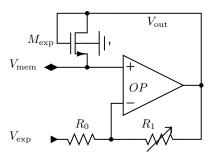

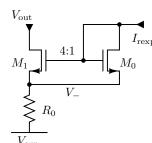

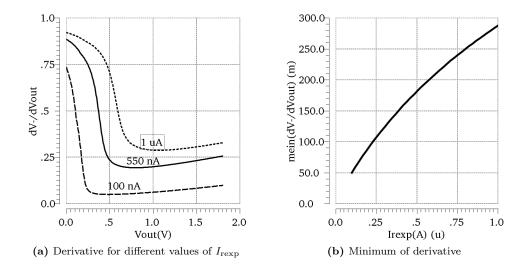

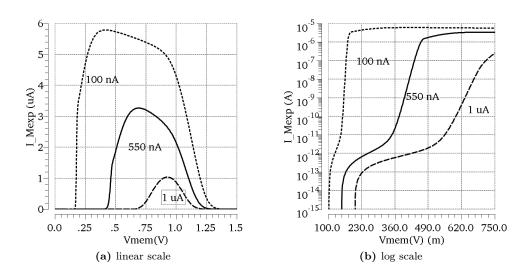

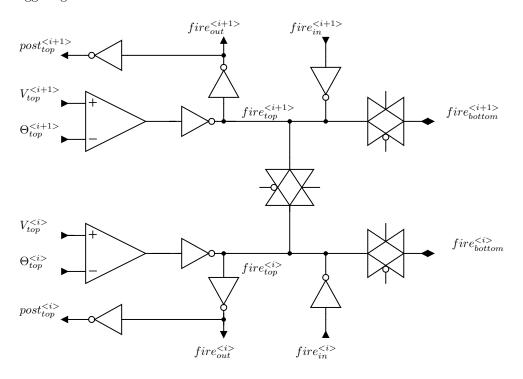

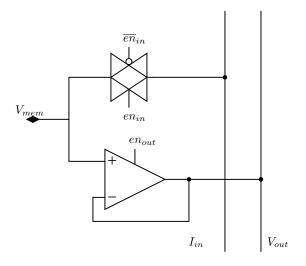

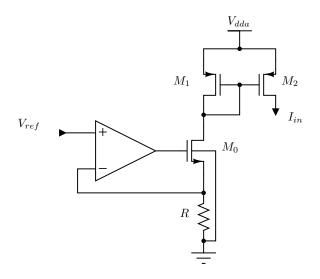

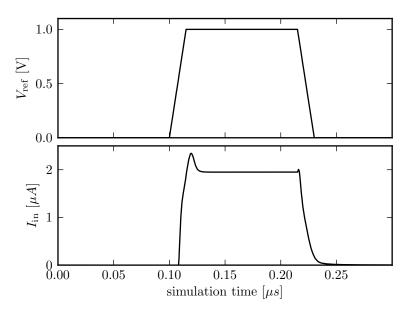

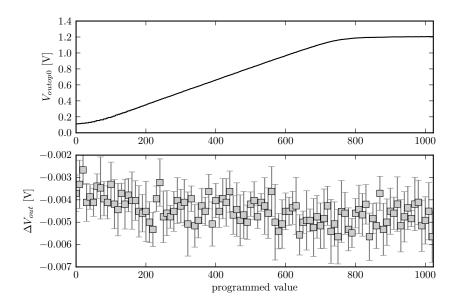

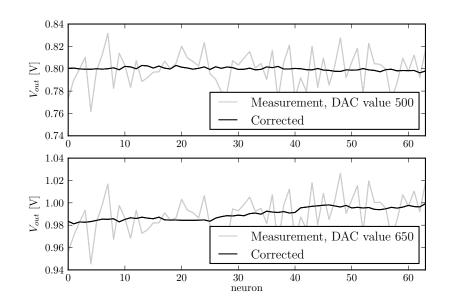

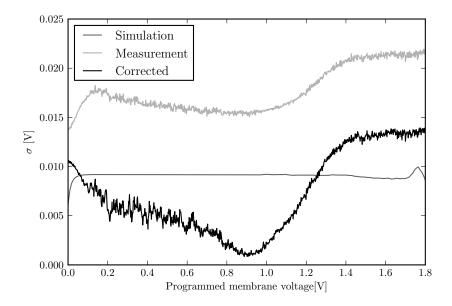

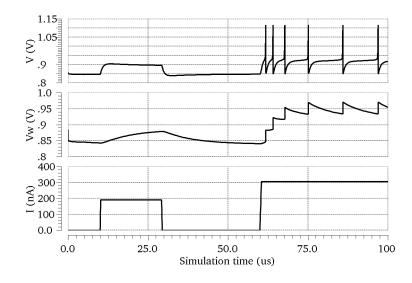

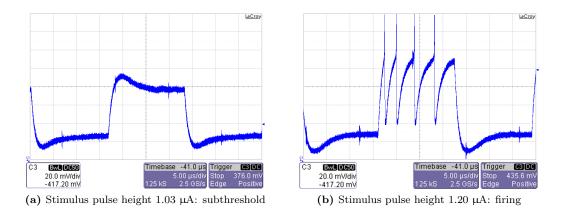

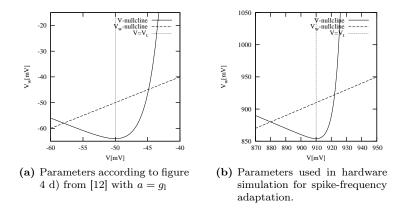

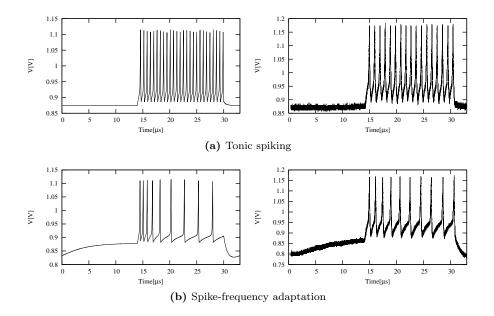

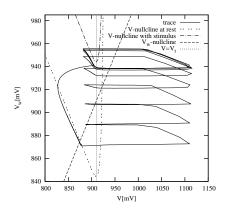

## 1.3.3 Simulation Techniques