# Dissertation

submitted to the Combined Faculties for the Natural Sciences and for Mathematics of the Ruperto-Carola University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

> Presented by **Dipl.-Phys. Matthias Hock** born in Munich, Germany

Date of oral examination: July 2, 2014

# Modern Semiconductor Technologies for Neuromorphic Hardware

Referees: Prof. Dr. Karlheinz Meier Prof. Dr. Peter Fischer

### Modern Semiconductor Technologies for Neuromorphic Hardware

Neuromorphic hardware is a promising tool for neuroscience and technological applications. This thesis addresses the question to what extent such systems can benefit from advances in CMOS scaling using the existing BrainScales Hardware System as a reference. A 65 nm process technology was selected and basic characteristics were evaluated using prototype chips. A system providing a large number of programmable voltage and current sources, based on capacitive storage cells, was developed. A novel scheme for refreshing the cells is presented. This system has been characterized in silicon. Two components required in a concept for synapse implementation, consisting of primarily digital circuits, were developed and tested in a prototype chip. One is an orthogonal dual-port SRAM with a specialized structure where every 8 bit word stored in the memory can be accessed by a single operation from either port. The second is an 8 bit current DAC which is used for generating postsynaptic events. Finally the analog neuron implementation from the existing system was transferred to the 65 nm process technology using thick-oxide transistors. Simulations suggest that comparable performance can be achieved. In conclusion, modern process technologies will contribute to successful realization of large-scale neuromorphic hardware systems.

### Moderne Halbleiter-Technologien für Neuromorphe Hardware

Neuromorphe Hardware ist ein vielversprechender Ansatz für neurowissenschaftliche und technische Anwendungen. Diese Arbeit behandelt die Frage, in welchem Umfang solche Systeme von Fortschritten in der CMOS Technologie profitieren können. Eine 65 nm Prozess-Technologie wurde ausgewählt und wesentliche Eigenschaften mit Hilfe von Prototypen-Chips untersucht. Ein System welches große Zahlen an programmierbaren Spannungs- und Stromquellen, basierend auf kapazitiven Speicherzellen, bereitstellen kann wurde entwickelt. Ein neuartiges Verfahren für das Auffrischen der Zellen wird vorgestellt. Das System wurde in silico getestet. Zwei Komponenten die für die Realisierung eines Synapsenkonzepts, basierend auf vorwiegend digitalen Schaltungen, benötigt werden wurden entwickelt. Eine davon ist ein orthogonaler dual-port SRAM mit einer speziellen Struktur, die es erlaubt, auf jede 8 bit Einheit mit einem einzelnen Speicherzugriff von jedem der beiden Ports zuzugreifen. Die zweite ist ein 8 bit Strom DAC, der für das Generieren von postsynaptischen Aktionspotentialen benötigt wird. Abschließend wurde die Neuron-Schaltung des existierenden Systems mit Hilfe von thick-oxide Transistoren in die 65 nm Prozess Technologie übertragen. Simulationen zeigen, dass vergleichbares Verhalten erreicht werden kann. Moderne Prozess-Technologien werden zur erfolgreichen Umsetzung von groß-skaligen neuromorphen Hardware Systemen beitragen.

# Contents

| 1 | Introduction 1                         |                           |                                                      |    |  |  |  |

|---|----------------------------------------|---------------------------|------------------------------------------------------|----|--|--|--|

|   | 1.1                                    | Outlin                    | e of This Work                                       | 2  |  |  |  |

|   | 1.2                                    | Non D                     | Disclosure Agreements                                | 3  |  |  |  |

| 2 | Existing Neuromorphic Hardware         |                           |                                                      |    |  |  |  |

|   | 2.1                                    | The H                     | ICANN Chip                                           | 4  |  |  |  |

|   |                                        | 2.1.1                     | Processing of Synaptic Events                        | 6  |  |  |  |

|   |                                        | 2.1.2                     | Plasticity                                           | 6  |  |  |  |

|   |                                        | 2.1.3                     | The Analog Parameter Storage System                  | 8  |  |  |  |

|   | 2.2                                    | Wafer-                    | Scale Integration                                    | 10 |  |  |  |

| 3 | Modern Process Technologies 13         |                           |                                                      |    |  |  |  |

|   | 3.1                                    | Evalua                    | ation of Different Process Technologies              | 13 |  |  |  |

|   | 3.2                                    | Main (                    | Characteristics of the TSMC 65 nm Process Technology | 15 |  |  |  |

|   | 3.3                                    | Analog                    | g Circuits in the 65 nm Process Technology           | 15 |  |  |  |

| 4 | Prototype Chips and Experimental Setup |                           |                                                      |    |  |  |  |

|   | 4.1                                    | Schem                     | atic Diagrams                                        | 16 |  |  |  |

|   | 4.2                                    | Design Flow               |                                                      |    |  |  |  |

|   | 4.3                                    | The First Prototype Chip  |                                                      |    |  |  |  |

|   | 4.4                                    | The Second Prototype Chip |                                                      |    |  |  |  |

|   | 4.5                                    |                           |                                                      |    |  |  |  |

|   |                                        | 4.5.1                     |                                                      | 24 |  |  |  |

|   |                                        | 4.5.2                     | Software Setup                                       | 24 |  |  |  |

| 5 | Initi                                  | ial Evalı                 | uation of the 65 nm Process Technology               | 26 |  |  |  |

|   | 5.1                                    | Custor                    | m Static Random Access Memory                        | 26 |  |  |  |

|   |                                        | 5.1.1                     | SRAM Operation                                       | 26 |  |  |  |

|   |                                        | 5.1.2                     |                                                      | 30 |  |  |  |

|   |                                        | 5.1.3                     | Implementation Details                               | 30 |  |  |  |

|   |                                        | 5.1.4                     | Experimental Results                                 | 31 |  |  |  |

|   | 5.2                                    |                           | Power Consumption of Custom SRAM                     | 32 |  |  |  |

|   |                                        | 5.2.1                     |                                                      | 32 |  |  |  |

|   |                                        | 5.2.2                     | Static Power Consumption of a Wafer-Scale System     | 34 |  |  |  |

|   | 5.3                                    | * *                       |                                                      |    |  |  |  |

|   |                                        | 5.3.1                     | Measuring the Mismatch in an Array of Transistors    | 36 |  |  |  |

|   | 5.4 | Integra                          | ated Power Management                                 | • | 40  |  |

|---|-----|----------------------------------|-------------------------------------------------------|---|-----|--|

|   |     | 5.4.1                            | Power Switches in the Current System                  | • | 40  |  |

|   |     | 5.4.2                            | Integrated Power Switches for Future Systems          | • | 41  |  |

|   |     | 5.4.3                            | Experimental Results for the 1.2 V Switch Circuit     | • | 45  |  |

|   |     | 5.4.4                            | Estimating the Area Consumption for on-chip Switches  | • | 47  |  |

|   | 5.5 | Transf                           | erring an Existing Operational Amplifier Design       | • | 47  |  |

|   | 5.6 | Digital                          | l Level Shifters                                      | • | 50  |  |

| 6 | Ana | Analog Parameter Memory System 5 |                                                       |   |     |  |

|   | 6.1 | The C                            | oncept of Capacitive Memory                           |   | 51  |  |

|   | 6.2 | The Fi                           | irst Generation of Capacitive Memory Cells            |   | 52  |  |

|   |     | 6.2.1                            | Choosing the Capacitor Technology                     |   | 52  |  |

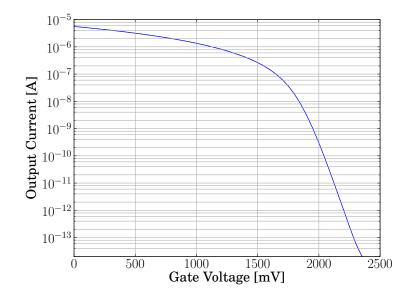

|   |     | 6.2.2                            | Optimizing the Switch                                 |   | 53  |  |

|   |     | 6.2.3                            | The Implemented Storage Cells                         | • | 55  |  |

|   |     | 6.2.4                            | Implementation Details                                |   | 56  |  |

|   |     | 6.2.5                            | Experimental Results                                  |   | 58  |  |

|   | 6.3 | The Pa                           | arameter Storage System                               |   | 61  |  |

|   |     | 6.3.1                            | Design Goals for the Parameter Storage System         |   | 61  |  |

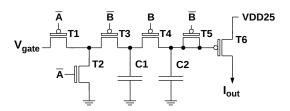

|   |     | 6.3.2                            | Analog Part of the Current Cells                      | • | 62  |  |

|   |     | 6.3.3                            | Analog Part of the Voltage Cells                      |   | 66  |  |

|   |     | 6.3.4                            | The Programming System                                |   | 68  |  |

|   |     | 6.3.5                            | Estimating the Setup Time                             |   | 75  |  |

|   |     | 6.3.6                            | Estimating the Output Resistance of the Voltage Cells |   | 78  |  |

|   |     | 6.3.7                            | Implementation of the Parameter Storage System        |   | 78  |  |

|   | 6.4 | Experi                           | imental Results                                       |   | 81  |  |

|   |     | 6.4.1                            | Test Circuits in the Prototype Chip                   | • | 81  |  |

|   |     | 6.4.2                            | Dynamic Range and Linearity for the Voltage Cells     | • | 83  |  |

|   |     | 6.4.3                            | Dynamic Range and Linearity for the Current Cells     |   | 88  |  |

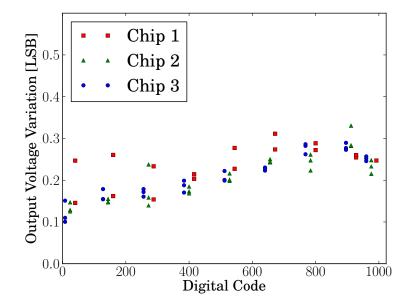

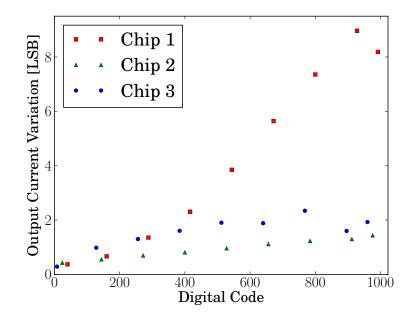

|   |     | 6.4.4                            | Cell-to-Cell Variation                                | • | 93  |  |

|   |     | 6.4.5                            | Reproducibility                                       | • | 96  |  |

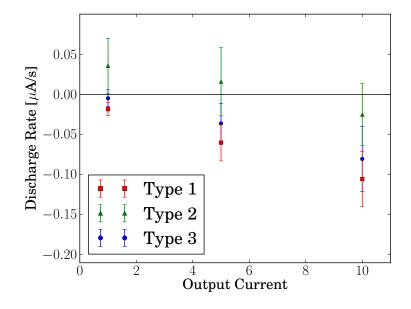

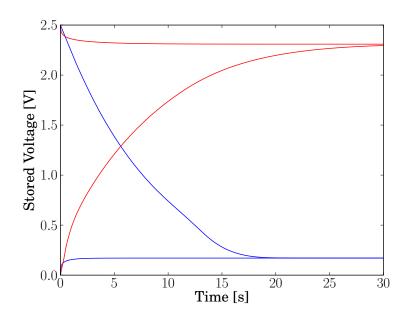

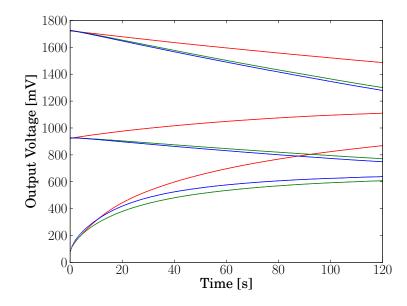

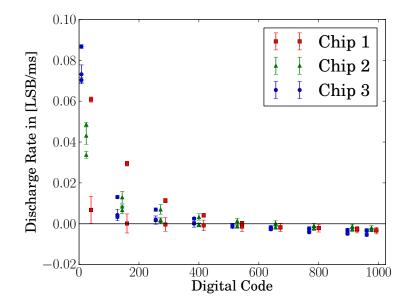

|   |     | 6.4.6                            | Storage Time                                          | • | 101 |  |

|   |     | 6.4.7                            | Temperature Dependence of the Storage Time            | • | 104 |  |

|   |     | 6.4.8                            | Reprogramming the Target Value of a Cell              | • | 108 |  |

|   |     | 6.4.9                            | Transient Distortions                                 | • | 112 |  |

|   |     | 6.4.10                           | Power Consumption                                     | • | 116 |  |

|   |     | 6.4.11                           | Defective Cells                                       |   | 119 |  |

|   | 6.5 | Modifi                           | cations for the Next Revision                         | • | 123 |  |

|   |     | 6.5.1                            | Comparison Logic                                      | • | 123 |  |

|   |     | 6.5.2                            | Update Pulse Generation                               | • | 124 |  |

|   |     | 6.5.3                            | Reference Voltage for the Current Cells               | • | 125 |  |

|   |     | 6.5.4                            | Improving the Reset for the Reference Voltages        | • | 127 |  |

|   |     | 6.5.5                            | Distortions affecting the Reference Voltages          | • | 129 |  |

|   |     | 6.5.6                            | Adding an Inactive Digital Code                       | • | 129 |  |

|   |     |                                  |                                                       |   |     |  |

|   | 6.6  | Introd         | ucing Different Types of Cells                    | . 129 |

|---|------|----------------|---------------------------------------------------|-------|

|   |      | 6.6.1          | Current Cells                                     | . 130 |

|   |      | 6.6.2          | Voltage Cells                                     | . 131 |

| 7 | Stra | tegies         | for a Future Synapse Array                        | 132   |

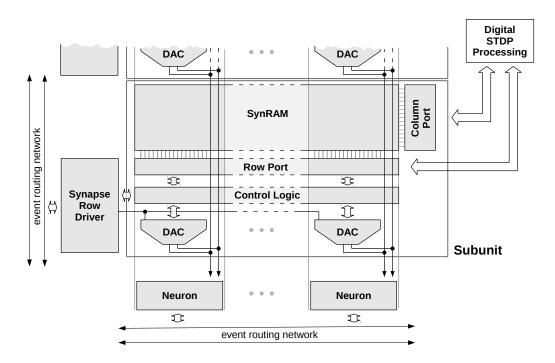

| • | 7.1  | -              | secture of the New Synapse Array                  |       |

|   |      | 7.1.1          | Increasing the Weight Resolution                  |       |

|   |      | 7.1.2          | Processing Synaptic Events                        |       |

|   |      | 7.1.3          | STDP in the New System                            |       |

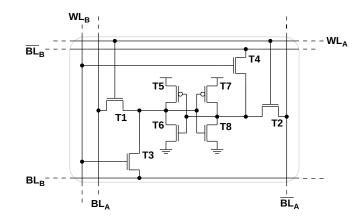

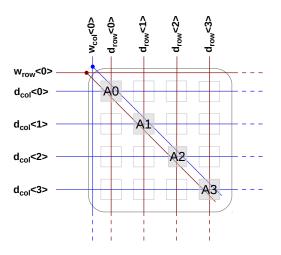

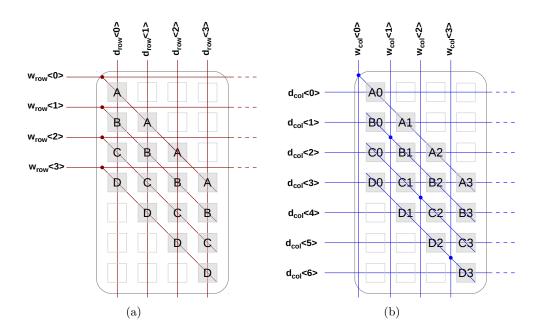

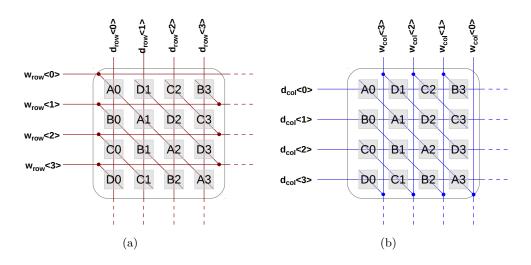

|   | 7.2  | Topolo         | bgy of the Synapse Memory                         |       |

|   |      | 7.2.1          | Dual-Port SRAM                                    |       |

|   |      | 7.2.2          | Modified Dual-Port Structure                      | . 137 |

|   | 7.3  | Contro         | olling the Access Operations                      | . 141 |

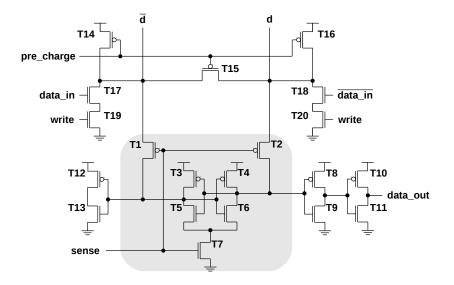

|   |      | 7.3.1          | The Sense Amplifier                               | . 141 |

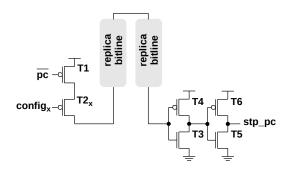

|   |      | 7.3.2          | Generating the Access Timing                      | . 144 |

|   |      | 7.3.3          | Control Logic                                     | . 148 |

|   |      | 7.3.4          | Interface to Digital Standard Cell Logic          | . 150 |

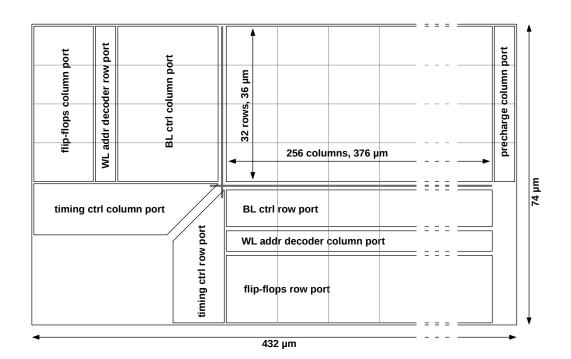

|   | 7.4  | Impler         | mentation Details for the Prototype Chip          | . 150 |

|   | 7.5  | Exper          | imental Results for the SynRAM                    | . 153 |

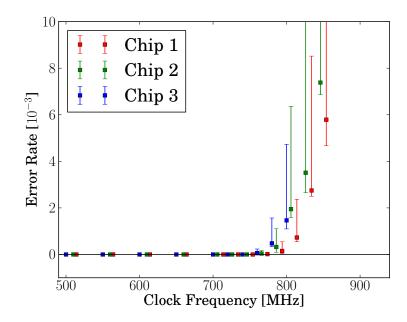

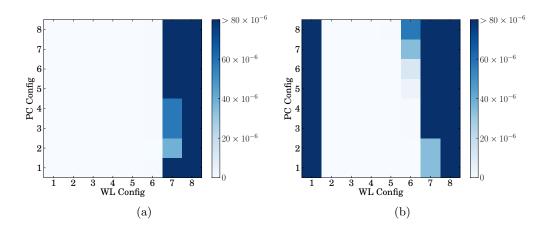

|   |      | 7.5.1          | Testing the Row Port                              | . 153 |

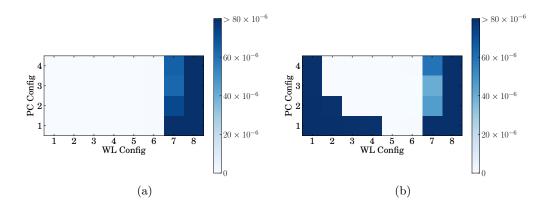

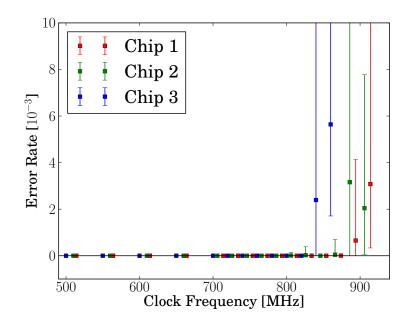

|   |      | 7.5.2          | Testing the Column Port                           | . 157 |

|   | 7.6  | ē              | AC                                                |       |

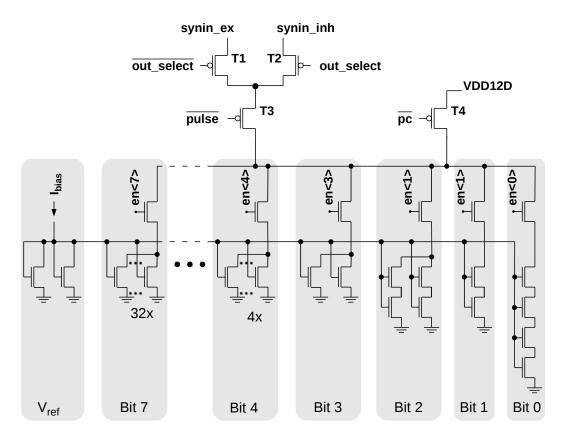

|   |      | 7.6.1          | Synapse DAC of the HICANN chip                    | . 162 |

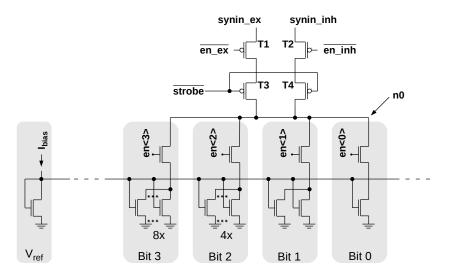

|   |      | 7.6.2          | Architecture of the Analog Part                   |       |

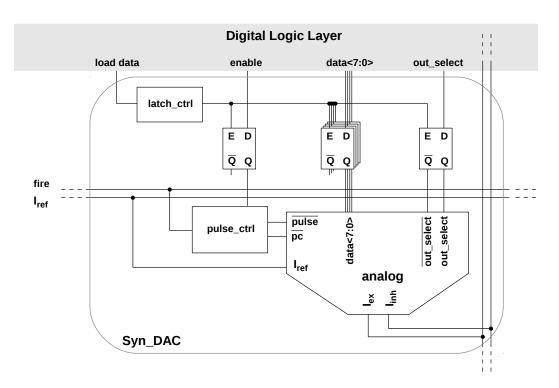

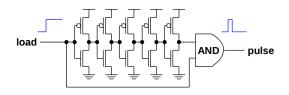

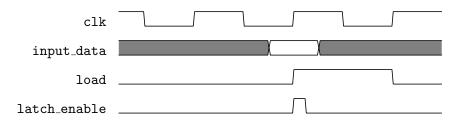

|   |      | 7.6.3          | Digital Interface                                 |       |

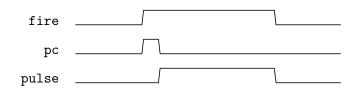

|   |      | 7.6.4          | Pulse Generation                                  |       |

|   |      | 7.6.5          | Accuracy                                          |       |

|   |      | 7.6.6          | Layout                                            |       |

|   |      | 7.6.7          | Implementation Details                            |       |

|   | 7.7  | -              | imental Results for the SynDAC                    |       |

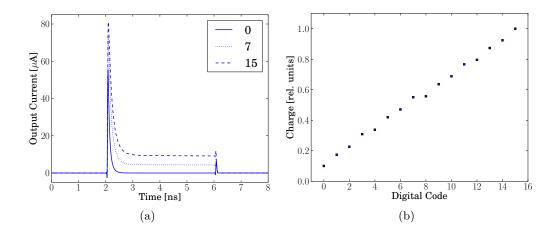

|   |      | 7.7.1          | Continuous Current Operation                      |       |

|   |      | 7.7.2          | Pulsed Operation                                  | . 174 |

| 8 | Neu  | rons in        | the 65 nm Process Technology                      | 178   |

|   | 8.1  | Transf         | fer of Neuron Components                          | . 179 |

|   |      | 8.1.1          | The Operational Transconductance Amplifier        | . 179 |

|   | 8.2  | The 65         | 5 nm Neuron Circuit                               | . 180 |

|   |      | 8.2.1          | Stimulating the 65 nm Neuron Circuit              | . 180 |

| 9 | Disc | cussion        |                                                   | 183   |

| 5 | 9.1  |                | Circuits Realized in the 65 nm Process Technology |       |

|   | 0.1  | 9.1.1          | Static Power Consumption of Custom SRAM           |       |

|   |      | 9.1.1<br>9.1.2 | Device Mismatch                                   |       |

|   |      | 9.1.2<br>9.1.3 | Integrated Power Management                       |       |

|   |      | -              |                                                   |       |

| 9.2           | 9.2 The Capacitive Parameter Storage System |                                                         |       |  |

|---------------|---------------------------------------------|---------------------------------------------------------|-------|--|

|               | 9.2.1                                       | Experimental Results                                    | . 185 |  |

|               | 9.2.2                                       | Setup Time                                              | . 188 |  |

|               | 9.2.3                                       | Comparison with the Existing Floating Gate-Based System | . 189 |  |

|               | 9.2.4                                       | Summary                                                 | . 189 |  |

| 9.3           | 3 SynAr                                     | ray                                                     | . 190 |  |

|               | 9.3.1                                       | SynRAM                                                  | . 191 |  |

|               | 9.3.2                                       | SynDAC                                                  | . 191 |  |

|               | 9.3.3                                       | Summary                                                 |       |  |

| 9.4           |                                             | n Implementations in the New Process Technology         |       |  |

| 9.5           | 5 Conclu                                    | usion                                                   | . 194 |  |

| 10 Oı         | utlook                                      |                                                         | 196   |  |

| Abbreviations |                                             |                                                         |       |  |

| Bibliography  |                                             |                                                         |       |  |

| Ackno         | owledgen                                    | nents                                                   | 211   |  |

# **1** Introduction

Understanding the human brain is a great challenge for science. Researchers from various disciplines have attempted to elucidate the structure and function of this highly complex system. Philosophers wonder at this very foundation of human nature. Physicians seek to cure neurological and psychiatric disorders such as Alzheimer's Disease and schizophrenia. Neuroscientists investigate the brain's components and their interaction by systematic experiments. The individual components, such as neurons and synapses, are understood fairly well, using sophisticated experimental methods such as the patch clamp technique. Characterizing the highlevel functions and interconnections of these components remains a challenge. However, the complex interactions between populations of neurons provide the basis for information processing within the brain. The possibilities of analyzing these processes in living subjects are limited. Therefore mathematical modeling is commonly used to investigate high-level brain functions. Early attempts date back to 1943, see McCulloch and Pitts [1943]. Many current models are based on work presented in Hodgkin and Huxley [1952]. Abstract mathematical descriptions can be used in computer simulations. The objectives of such models range from detailed descriptions, accounting for individual ion channels within single neurons to approaches covering entire functional units of the cortex. However, conventional computer systems operate sequentially, processing transitions between discrete states using only a limited number of processing units [von Neumann 1945]. In contrast, within the brain all neurons are processing information in parallel. This fundamental discrepancy leads to a limited efficiency of simulation systems based on standard computer hardware [Morrison et al. 2005].

An alternative, more efficient approach is the physical emulation of biological components. Processing and transmission of information in the brain is based on electrical phenomena. Each neuron posses a membrane which is characterized by a capacitance and a certain potential. The potential is modulated by currents resulting from the activity of ion channels located within the membrane. Whenever the membrane potential crosses a certain threshold, an action potential or so-called spike is generated by the neuron. This event is characterized by a sudden increase in the membrane potential, followed by a steep decrease and a relatively slow repolarization. This signal is transmitted via the neuron's axon to the dendrites of other, neighboring or distant neurons. The transmission of information between individual neurons occurs at synapses. These connect the axons of the presynaptic neuron to the dendrites of the postsynaptic neuron. Synapses are either excitatory or inhibitory. At excitatory synapses an incoming spike leads to an increase in the membrane potential of the postsynaptic neuron, whereas at inhibitory sy-

### 1 Introduction

napses a spike leads to a decrease in the membrane potential of the postsynaptic neuron. Spikes are considered as digital signals, the information transmitted is only encoded in the timing, not in amplitude or shape of the action potential. The synapses have a distinct property, referred to as the synapse's weight, characterizing its quantitative impact on the membrane potential of the postsynaptic neuron.

Electronic circuits can be designed to mimic the behavior of neurons and synapses, referred to as neuromorphic hardware. Early attempts to build such circuits were described e.g. by Mead in 1988 [Mead and Mahowald 1988, Mead 1990]. Currently various approaches to realize neuromorphic hardware are pursued, a selection is outlined in [Indiveri et al. 2011]. These systems are all based on integrated circuits, allowing for emulation of large neural networks operating at biological time-scales or even faster. In analogy to neurophysiology, all functional units in neuromorphic hardware can operate in parallel, which is an intrinsic advantage compared to simulations based on standard computer technology. However, the realization of networks of biologically relevant dimensions remains a challenge. The neocortex of the human brain contains roughly  $2 \cdot 10^{10}$  neurons [Pakkenberg et al. 2003]. None of the existing systems is able to emulate networks in this order of magnitude. Even the emulation of functional units such as the human visual cortex, containing  $5 \cdot 10^5$  neurons [Wandell et al. 2007], are currently out of reach. Advances in integrate circuit technology are one building block towards improved neuromorphic hardware.

Once available, such systems can be used as an efficient experimentation platform for neuroscientists. A large-scale system implementing biologically inspired information processing might not only be a valuable tool for neuroscientists. Moreover it offers the possibility to utilize this strategy for technical applications. Undoubtedly biology has better solutions for certain tasks in information processing than current efforts using standard computer technology. Typical examples are image processing or the control of complex patterns of physical movement. These are qualities required for instance in the field of robotics. A unique feature of biological systems is the ability of learning. Implementation of biologically inspired learning processes in technical applications would enable novel paradigms in information processing.

In summary, the development of large-scale neuromorphic hardware can be a powerful tool for neuroscientists and open new ways for information processing in technical applications.

## 1.1 Outline of This Work

This thesis evaluates to what extent large-scale neuromorphic hardware systems based on mixed-signal chips can benefit from recent progress in CMOS technology. The reference system for the evaluation is the currently available BrainScaleS Hardware System. Four different modern semiconductor manufacturing processes of the 45 nm and 65 nm node were evaluated based on process documentation and simulations. Based on this data a TSMC 65 nm low-power process technology was

selected for a more thorough investigation, including the development of prototype chips. Circuits for assessment of basic properties of this process technology, such as device mismatch and leakage currents, were integrated into a prototype chip. The question whether it is possible to transfer existing analog circuits to the new process technology using thick-oxide transistors was addressed. As a proof of concept an operational amplifier was successfully transferred. Further more complex components required in mixed-signal neuromorphic hardware were developed and tested. An analog parameter storage system based on capacitive memory cells which provides a large number of programmable voltage and current sources was designed. A novel scheme for programming and refreshing the individual cells is presented. The parameter storage system was integrated into a prototype chip and its performance was characterized. Currently the option of implementing a synapse array, based on the architecture of the existing design, but using mostly digital circuits is being developed. Two key components required for the new concept were developed and implemented. The first of these components is an SRAM block with two orthogonally orientated ports, with a novel, application-specific structure. The second component is a unit element current DAC, designed to produce short current pulses. Both circuits have been tested in a prototype chip. In conclusion, this thesis demonstrates that the 65 nm process technology is suited for implementation of mixed-signal neuromorphic hardware.

## 1.2 Non Disclosure Agreements

To develop circuits for implementation in modern semiconductor fabrication process detailed knowledge about some aspects of the underlying technology is required. Therefore the foundry offering the process usually provides a "Process Design Kit" (PDK) to the customer. This set of files contains general documentation on the process technology. Furthermore detailed simulation models for the transistors, typically based on BSIM models [Hu et al. 1998] described in the SPICE format [SPICE 2014], are included. Usually also libraries of standard cells for automated synthesis of digital designs are included. An important aspect are the design rules for drawing layouts. These are required by the routing software which automatically connects standard cells in digital design as well as for development of custom circuits. The information included in the PDK is typically considered a corporate secret that must not be shared with third parties, especially not with competing chip manufacturers. As a consequence, customers must accept a Non Disclosure Agreement (NDA) in order to access the PDK of a process technology. Due to Non Disclosure Agreements, some details of the process technologies discussed in the following cannot be published within this thesis.

## 2 Existing Neuromorphic Hardware

There have been various attempts to build electronic circuits mimicking the behavior of biological brains. Early work in this field has been conducted by VLSI pioneer Carver Mead in 1988 [Mead and Mahowald 1988, Mead 1990].

Since then, systems based on a wide variety of different approaches have been developed. These cover e.g. designs implementing small numbers of precise emulations of Hodgkin-Huxley models based on complex analog circuits [Chen et al. 2010]. An entirely different strategy is used in the SpiNNaker Project [Furber et al. 2013]. It uses large numbers of digital processors, which are combined to a massively parallel computing system, in order to model the behavior of large neural networks. A comprehensive overview, comparing multiple different approaches on the emulation of spiking neural networks, can be found in Indiveri et al. [2011].

For the work presented in this thesis the BrainScaleS Hardware System is used as a reference for the evaluation of different process technologies. The BrainScaleS Hardware System is a highly configurable VLSI<sup>1</sup> implementation of neuromorphic circuits, fabricated in a 180 nm process technology. It utilizes wafer-scale integration of mixed signal ASICs<sup>2</sup> in order to allow for the energy efficient emulation of large scale neural networks. In the following a general overview of the system is presented. The focus in this description however is on the circuits and concepts which are relevant for the work described in the following. Further information on the BrainScaleS Hardware System can be found in Schemmel et al. [2010] and Brüderle et al. [2011].

## 2.1 The HICANN Chip

The HICANN chip is the building block of the BrainScaleS Hardware System. It is a mixed signal chip, featuring 512 highly configurable analog neuron implementations as well as about 115 k synapse circuits. Additionally there is digital control logic for configuration of the analog circuits as well as the transmission of the neural events. The time constants of the all analog circuits are scaled compared to the time constants found in biology by a factor of about  $10^4$ . This speed up factor makes the system attractive for extensive parameter sweeps and to investigate longterm learning effects. The physical size of a single HICANN chip is  $5 \times 10 \text{ mm}^2$ .

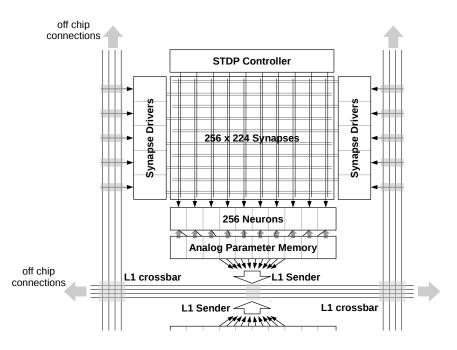

In Figure 2.1 an overview for the various parts of the chip is shown. The analog part of HICANN is build from two identical blocks, the so called Analog Neural

<sup>&</sup>lt;sup>1</sup>Very Large Scale Integration

<sup>&</sup>lt;sup>2</sup>Application Specific Integrated Circuit

Figure 2.1: Simplified diagram of the main building blocks of a HICANN chip. Only the upper half of the chip is shown. The lower half is identical but mirrored relative to the horizontal L1 lines in the center of the chip.

Network cores (ANN core). The description given in the following refers to the upper ANN core, the lower one is identically organized but its orientation is mirrored. Within one ANN core 256 neuron circuits are placed in a row. On top of the neuron row the synapse array, implementing  $256 \times 224$  synapse circuits, is located. Each neuron circuit receives input from the 224 synapses in the same column. In order to emulate neurons which receive input from more synapses, it is possible to connect multiple neuron circuits. Up to 64 neuron circuits can be configured to emulate a single neuron with up to 14336 synaptic inputs. Obviously the total number of neurons which can be emulated by one HICANN chip decreases accordingly.

The analog neuron circuit is based on the Adaptive Exponential Integrate-and-Fire model, published by R. Brette and W. Gerstner [Brette and Gerstner 2005]. A detailed description of the electronic implementation used in the HICANN chip can be found in Millner [2012]. An important aspect of the neuron circuit is its high flexibility. Each neuron can be configured by 22 individual analog parameters, it requires 11 programmable current sources and 11 programmable voltage sources. Furthermore there are 3 analog parameters which are shared among multiple neuron circuits. On the one hand, the high number of parameters offers various possibilities to modify the characteristics of the neurons, enabling the circuits to mimic the behavior of different types of neurons found in biology [Izhikevich 2004]. On the other hand, the individually adjustable parameters are important to compensate

### 2 Existing Neuromorphic Hardware

for neuron-to-neuron variation which is introduced by device mismatch. The work presented in Schwartz [2013] is dedicated to calibration of the neuron circuits by adjusting its parameters. In Section 2.1.3 the analog parameter storage system providing the individually programmable voltages and currents is described.

A flexible bus network, termed the Layer 1 (L1) bus, allows for routing of neural events within the HICANN chip. Further it provides the capability to directly connect multiple HICANN chips and exchange neural events between them. Information on the L1 system can be found in Schemmel et al. [2008] and Hock [2009]. The external interface of the chip is termed the Layer 2 (L2) bus which has been developed by the TU Dresden, [Hartmann et al. 2010]. It allows for transmission of configuration data to the chip but is also capable of exchanging neural events.

### 2.1.1 Processing of Synaptic Events

If the membrane voltage of a neuron circuit crosses its threshold voltage a spike is generated. The event is then digitally processed and sent to the asynchronous L1 bus network. The data transmitted on the bus is a 6 bit identification number which is statically assigned to the presynaptic neuron which emitted the spike. The event is routed in the L1 system to its target, a *synapse\_driver* circuit. The *synapse\_driver*, is the interface between the L1 communication network and the synapse array. It transmits the lower 4 bit of the received neuron number into an attached row of synapses. Each synapse circuit in the array features an address decoder which compares the data sent by the *synapse\_driver* to its address, which is stored in local SRAM cells. In case the numbers are matching, the synapse is activated and produces a postsynaptic event.

The postsynaptic events in the system are represented by current pulses. Every synapse features a unit element current DAC, offering 4 bit resolution. The amplitude of the pulses is proportional to the weight stored in the sending synapse. The length of the pulse is controlled by the *synapse\_driver* circuit. Along with the address it sends the **strobe** signal, gating the output of the DACs, to the synapse row. The outputs of all DACs in one column of the synapse array are connected to a shared wire which connects them to the synaptic input circuit of the postsynaptic neuron. This circuit evaluates the integrated amount of charge transfered by the postsynaptic current pulse.

### 2.1.2 Plasticity

In neural networks the properties of many components change over time, depending on of the activity in the network. These effects are summarized by the term *plasticity*. An overview for the various synaptic plasticity mechanisms observed in biology is presented in Morrison et al. [2008]. In the synapse array of the HICANN chip two plasticity mechanisms are implemented, Short-Term Plasticity (STP) and Spike-Timing Dependent Plasticity (STDP). The STP functionality is implemented in the *synapse\_driver* circuit, modulating the strength of the synaptic events by adjusting the length of the **strobe** signal. This mechanism is not further described as it is not relevant for the circuits discussed within this thesis. General information on STP can be found in Tsodyks and Markram [1997], the implementation in the HICANN chip is described in Schemmel et al. [2007].

STDP is a mechanism which changes the weight of individual synapses, dependent on the relative timing between pre- and postsynaptic events. The biological background is presented e.g. in Gerstner et al. [1996], Markram et al. [1997] or Bi and Poo [1998]. According to the concept of STDP, a synapse changes its weight wdepending on the correlation between pre- and postsynaptic events. The time difference  $\Delta t_{ij} = t_i - t_j$ , where  $t_i$  is the time at which the presynaptic event occurred and  $t_j$  the time of the postsynaptic event, is evaluated for each pair of pre/post spikes. In case the time difference  $\Delta t_{ij}$  is positive, i.e. the presynaptic event occures before the post synaptic event, a causal correlation between the events is assumed. For negative values  $\Delta t_{ij}$  the correlation is assumed to be acausal. The change of the synapse weight  $\Delta w_{ij}$ , triggered by a single pair of pre- and postsynaptic spike, can be described by the following model:

$$\Delta w_{ij} = \pm F_{\pm}(w) \exp\left(-\frac{|\Delta t_{ij}|}{\tau_{\pm}}\right)$$

(2.1)

F(w) describes a positive, weight dependent factor and  $\tau_{\pm}$  the time constants. The positive signs apply in case  $\Delta t_{ij}$  is positive, the negative ones apply for  $\Delta t_{ij}$  being negative. As a result, pre-before-post spike pairs lead to an increasing weight of the synapse, whereas post-before-pre pairs lead to a reduction of the weight. In literature many STDP rules, using different factors  $F_{\pm}(w)$ , can be found. Various examples are discussed in Morrison et al. [2008] or Abbott and Nelson [2000]. In the HICANN chip two different components are involved in the realization of STDP. The exponentially weighted time interval between pre- and postsynaptic events is evaluated locally in every synapse by an analog circuit. The results are accumulated and stored in the synapse, represented by the voltage on a capacitor. On top of the synapse array an digital STDP controller is located, implementing the term  $F_{\pm}(w)$ and performing the weight updates for the synapses. This controller sequentially processes the individual synapses by reading the accumulated correlation voltage stored on the capacitors and comparing it against an adjustable threshold. In case the value is above the threshold, the controller reads the current weight of the synapse, calculates an update and reprograms the weight of the synapse accordingly. After reading the accumulated voltage, the controller resets the storage capacitor in the synapse.

Accounting for the accumulation happening in the hardware implementation Equation 2.1 needs to be modified as follows:

$$\Delta w_{ij} = \pm F_{\pm}(w) \sum_{n} \exp\left(-\frac{|\Delta t_{ij,n}|}{\tau_{\pm}}\right)$$

(2.2)

In this context n is the number of pre-post spike pairs which occurred since the last reset of the accumulation capacitor. For detailed information about the STDP

### 2 Existing Neuromorphic Hardware

implementation used in the HICANN chip see Schemmel et al. [2006; 2007]. The concept used in the HICANN chip allows for an efficient implementation of STDP, however it lacks flexibility. The controller implemented in the HICANN chip supports only a fraction of the diverse rules which are discussed among neuroscientists. The work presented in Friedmann [2013] describes the development of a processor which can replace the currently used STDP controller in order to allow for a wide variety of STDP rules.

## 2.1.3 The Analog Parameter Storage System

As mentioned before, the analog circuits in the HICANN chip, especially the neuron circuits, require a large number of individually adjustable parameters. In total, each chip requires 12384 programmable voltage and current sources, more than 90 % of which are used for configuration of the neuron circuits. In the HICANN chip these adjustable parameters are provided by a system based on floating gate transistors. Today the usage of floating gate-based storage is a widespread technology in consumer electronics as non volatile digital memory. However, these devices can also be used to store continuous, analog values. In the following a brief overview of the floating gate parameter storage system is given. A more detailed descriptions can be found in Kononov [2011, Chapter 3] and Millner [2012, Chapter 9].

### **Basic Principle**

Floating gate devices are typically based on transistors featuring a completely isolated gate, referred to as *floating*. The amount of charge trapped on the floating gate determines the gate-source voltage of the transistor, controlling its drain current. Above the floating gate a second gate, termed the control gate, is located. A voltage difference between the control gate and the potential in the channel of the underlying transistor can be used to change the amount of charge trapped on the floating gate, utilizing either a process called Fowler-Nordheim tunneling [Lenzlinger and Snow 1968] or hot-electron-injection [Duffy and Hasler 2003].

Using a programming process including feed back, it is possible to set the drain current of the transistor to a predefined target value. This way floating gate devices can be used as programmable analog current sources. Integrating the floating gate device into a source follower circuit allows to read the voltage on the floating gate, the circuit can be used as a programmable voltage source. Once programmed, floating gate devices typically provide constant output over extended periods of time. Without any potentials applied to the control gate, the tunneling rates discharging the floating gate are negligible for most applications. The absolute numbers depend on thickness and quality of the material isolating the floating gate as well as the precision required.

In the 180 nm process used for the HICANN chip, only a single layer of polysilicon is available to form transistors gates. It is not possible to place an additional control gate on top of the floating one. A way how to integrate floating gate devices into a single-poly process has been demonstrated by K. Ohsaki [Ohsaki et al. 1994]. Instead of a single one, three transistors are required to realize a cell. The gates of these transistors are connected, forming the floating gate. Two of them, termed the *control gates*, are connected as MOS capacitors and required for programming the cells. The third transistor is used for readout. This concept is used for the parameter storage cells of the HICANN chip.

In general, floating gate transistors are an area and power efficient solution to realize programmable voltage and current sources. However, to achieve sufficient tunneling rates during the programming process, voltages significantly above the specified supply voltage range of the process are required [Wu et al. 2012]. The cells implemented in the HICANN chip require a programming voltage of about 11 V. The effective area consumption for a single parameter is  $210 \,\mu \text{m}^2$ . Once programmed, the drift of the output is negligible on the time scales of neuromorphic experiments.

### **Programming Scheme**

On the HICANN chip the floating gate cells in the parameter storage system are organized in four arrays, each holding 1548 voltage and 1548 current cells. The output values of the cells are changed by applying short voltage pulses to the control gates of the individual cells. The process is controlled by comparing the output of the individual cells against a reference generated by a 10 bit voltage DAC after each programming pulse. The output of current cells is converted to a voltage by connecting it to a 150 k $\Omega$  resistor to allow for comparison with the reference voltage. Number and duration of the pulses required to reach a target value strongly depend on the absolute voltage on the gate. To reduce the number of pulses required to program it to high values the duration of the individual pulses is doubled in case a cell does not reach its target value within a specified number of pulses. Controlling the programming pulse the DAC and comparator need to sequentially process all of the individual cells in the array.

### Limitations of the Floating Gate System

As mentioned before, floating gate devices provide an area efficient way to implement programmable current and voltage sources. Once programmed, no power is consumed by the storage devices themselves. However, several limitations are observed in the system which is currently used.

Since every cell in the array is read out by the controller after each individual pulse the programming process is rather slow. With the currently used settings for the controller, writing a full set of parameters takes about 4 s [Hartel 2014]. Due to the high speed up of the neuronal circuits in the chips, the duration of individual experiments is very short. In case each experiment requires a different

#### 2 Existing Neuromorphic Hardware

parameter setup, the reprogramming process might take significantly longer than the experiment itself. In such a scenario the user can not exploit the high speed-up factor of the neural circuits on the hardware.

Changing of parameters during an experiment is not possible with the floating gate-based system. The programming controller applies high voltage pulses to the control gates of the cells when changing their value. As a result, voltages and currents outside the regular operating range are observed at the output of the cells during the process. It can be expected that this has a severe impact on any running experiment.

Furthermore the implementation of floating gate devices increases the overall complexity of the hardware system. In total three additional supply voltages are required to operate the floating gate parameter system in the HICANN chip. Two of these supply voltages are significantly higher than the regular supply voltage. As a consequence specialized  $\text{ESD}^3$  protection mechanisms are required and it is essential to follow the correct power up sequence for the individual voltages.

## 2.2 Wafer-Scale Integration

In order to build a system large enough to allow for the emulation of biologically relevant networks, multiple HICANN chips need to be combined. Due to the accelerated operation, the communication bandwidth required to transmit neural events in the system is very high. According to Schemmel et al. [2010] the presynaptic event rate easily reaches 1.5 Gevents/s per HICANN. Therefore the BrainScaleS Hardware system uses wafer-scale integration to provide the required bandwidth between the individual chips at a reasonable power efficiency.

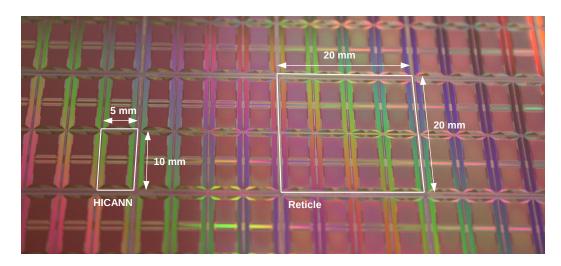

The HICANN chips are produced on standard 20 cm wafers in a 180 nm CMOS process technology. However, the wafer is not cut into individual dies after fabrication, but used as one unit. As mentioned before, the HICANN chips include an interface, the L1 bus, which allows for direct connection between individual chips. Eight HICANN chips which are placed within a an area of  $20 \times 20 \text{ mm}^2$ , a so called "reticle", and their L1 links are directly connected. Figure 2.2 shows a photo of such a wafer. A single chip as well as a reticle are highlighted. For technical reasons, no electrical connections between the in total 48 reticles per wafer can be realized during manufacturing. An additional metal layer, called the post processing layer in the following, is therefore applied to the wafers at the Fraunhofer Institute for Reliability and Microintegration, Berlin. It creates connections between the L1 links of adjacent HICANN chips located in different reticles. Additionally it provides contact pads on the wafers surface which are used for power supply and to provide an external communication interface. Via these pads the wafer is connected to the main PCB using elastomeric connectors<sup>4</sup>. The external communication interface,

<sup>&</sup>lt;sup>3</sup>Electro Static Discharge

$<sup>^{4&</sup>quot;}$ Zebra elastomeric connectors", www.fujipoly.com

Figure 2.2: Photograph showing a section of a wafer with HICANN chips before the additional post processing layer is applied. A single HICANN chip and a reticle are highlighted.

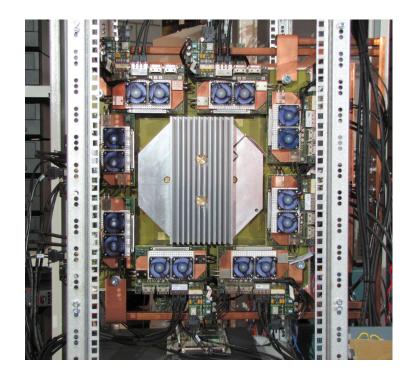

the L2 bus, connects the individual HICANN chips to FPGA<sup>5</sup> based communication units, which have been developed by the TU Dresden [Hartmann et al. 2010]. These are connected to a cluster of conventional PCs via Ethernet. The communication units also provide the option of interconnecting multiple wafer modules. The host PCs are used to configure the circuits on the wafer and control the execution of experiments. Figure 2.3 shows a photograph of an assembled wafer module. Overall, one wafer module features 348 HICANN chips, providing total numbers of about 200 k neurons and 60 M synapses. The power supplies, the main PCB and the cooling system a designed to allow for a maximum power consumption of 1 kW per wafer. Further there are plans to interconnect multiple wafer modules, to allow for emulation of even larger networks. This can be realized by digital high-speed links between the FPGA based communication units.

<sup>5</sup>Field Programmable Gate Array

Figure 2.3: Photograph showing an assembled wafer module mounted in a rack. The wafer is covered by the central aluminum bracket, it is surrounded by eight communication units.

## 3 Modern Process Technologies

The demand for evermore powerful digital circuits has motivated scaling of the CMOS technology throughout the past four decades. These developments were accompanied by multiple challenges. However, with higher resolution in lithography, the introduction of new materials and better understanding of the underlying physics, these challenges could be met and the performance of the resulting systems continually increased, as proposed by Moore's Law [Moore 2006]. Given the high packing density, fast circuit speed, and lower power dissipation, CMOS technology has become the prevailing technology for VLSI applications.

However, these considerations apply mainly for digital circuits. In mixed-signal systems also functional units built from analog circuits are integrated. The performance of these analog building blocks does not necessarily improve with newer CMOS technologies. With every new generation of CMOS processes, the minimum transistor dimensions are constantly decreasing. Simultaneously the nominal supply voltages are also constantly decreasing. This is required to limit the dynamic power consumption of digital circuits, despite the growing numbers of transistors. While the overall performance of digital circuits benefits from the reduced supply voltage, it imposes challenges for analog designs.

The effects of CMOS scaling on analog circuit performance is dealt with in many studies. For reference, see e.g. Annema et al. [2005], Young [2010], Kinget [2007], Sansen et al. [1998]. Taken together, these studies indicate that lower supply voltages are associated with additional effort for the design of analog circuits.

When transferring an exiting mixed-signal system to newer process technology, the performance of the digital components will improve, whereas the realization of analog circuits with equal functionality will require additional design effort.

## 3.1 Evaluation of Different Process Technologies

The existing BrainScaleS Hardware System is manufactured in a 180 nm process technology, available since 1999. To justify the associated efforts, a considerable advantage should be anticipated when transferring the existing system to a more recently developed process technology. As of today (2014) mass production for processes technologies of the 22 nm node is established [ITRS 2011]. The development of a new system requires the evaluation of multiple prototype chips. Therefore, an important condition for the selection of a new process technology, which is not directly related to any technical characteristics, is that the fabrication of prototype chips based on Multi-Project Wafers (MPWs) has to be offered. For multi-project

### 3 Modern Process Technologies

wafers organizations such as e.g. CMP<sup>1</sup>, EUROPRACTICE IC Service<sup>2</sup> or MOSIS<sup>3</sup> collect multiple designs of small chips from various customers and send them to the process vendor as a single design. That way the mask production costs can be split among all participants, allowing for reasonably priced prototype chips. Only process technologies for which MPW runs are offered on a regular basis are interesting candidates for future neuromorphic hardware projects.

Four different process technologies of either the 65 nm or the 45 nm node were preselected. For all of them MPW runs for prototyping are offered by one of the organizations mentioned above and a PDK for the Virtuoso IC Design Platform<sup>4</sup> is available. These process technologies were evaluated based on the documentation included in the PDK and simulation results. First of all basic characteristics such as the maximum possible number of metal layers or the diameter of the wafers were compared. Furthermore a small custom layout was drawn in each of the process technologies to test complexity of the design rules. As expected the design rules for the 45 nm were more restrictive, slightly increasing the effort for the development of custom circuits.

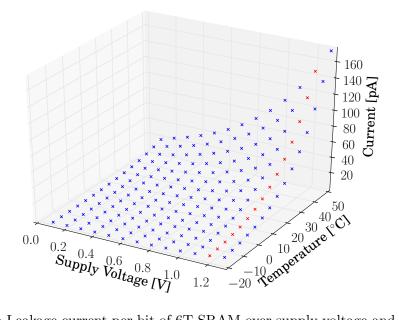

More than half of the overall wafer area of the BrainScaleS Hardware System is covered by digital circuits. These circuits strongly benefit from the increased device density offered by a new process technology. This suggests employing one of the 45 nm process technologies which provide higher integration density. However, static leakage currents in digital devices need to be considered. A significant proportion of the digital part is custom SRAM which is used to store configuration data for analog circuits. Therefore custom SRAM was used as an example for a digital component in simulations for the estimation of leakage currents. These simulations indicate that leakage of the digital components has the potential to substantially contribute to the overall power consumption.

Finally a 65 nm low power process technology offered by  $TSMC^5$  was selected as a promising candidate for future large-scale neuromorphic systems. The main advantage is the anticipated leakage current. Simulations suggest that leakage within the 65 nm TSMC process is by more than one order of magnitude lower than within the alternative process technologies. This process was characterized more thoroughly, including the development of prototype chips, to evaluate whether the effort of porting the system is justified.

<sup>&</sup>lt;sup>1</sup>Circuits Multi-Projets, http://cmp.imag.fr

$<sup>^{2}</sup>$  http://www.europractice-ic.com

<sup>&</sup>lt;sup>3</sup>http://www.mosis.com

<sup>&</sup>lt;sup>4</sup>Cadence Design Systems, Inc., San Jose, CA, USA

<sup>&</sup>lt;sup>5</sup>Taiwan Semiconductor Manufacturing Company, Ltd., Hsinchu, Taiwan

## 3.2 Main Characteristics of the TSMC 65 nm Process Technology

Several key features of the new process technology offer benefits compared to the 180 nm process used so far. These are detailed in the following. The BrainScaleS Hardware System uses wafer-scale integration, see Schemmel et al. [2010] and Chapter 2.2. This allows to realize a high communication bandwidth between the individual components with adequate power efficiency. The new process is based on 30 cm wafers offering about twice the area per wafer compared to the 20 cm wafers which are currently used. Therefore a significantly larger number of devices can be connected using power-efficient on-wafer communication. On the other hand, without substantial changes to the design of the underlying chips, the demands for the supporting structures like the main PCB, the cooling system and the mechanical mounting of the system will increase with wafer size. The standard transistors in the process are designed to operate at 1.2 V. The higher speed of the transistors helps to increase the performance of the digital part significantly. Additionally there is the option to use thick-oxide transistors which are optimized for 2.5 V operation. With decreasing size of the transistors the density of digital components increases. For instance the area covered by a single bit of custom SRAM decreases by a factor of about 9, see Chapter 5.1. Standard cell logic is also assumed to offer a 8-fold higher density compared to the former process. The number of metal layers available increases from 6 to 9, improving the routing resources. This simplifies the realization of the long-range connections required for the transmission of neural events. Further the additional metal resources can allow for thorough shielding of sensitive signals. In the BrainScaleS Hardware System a crosstalk problem has been identified, see Friedmann [2013, Section 5.3.4]. In this case sufficient shielding cannot be provided due to limited resources.

Overall, the new process offers considerable improvements in the digital domain.

## 3.3 Analog Circuits in the 65 nm Process Technology

As mentioned before the development of complex analog circuits in modern process technologies is challenging, mainly due to the low supply voltage. However, the development of analog low voltage circuits is not within the scope of this thesis. An alternative option to realize analog circuits in the 65 nm process technology is to use a higher supply voltage in conjunction with the thick-oxide transistors available. This offers the possibility to operate circuits with a supply voltage of up to 2.5 V. Considering the fact that this is even more than the supply voltage used for the analog circuits in the BrainScaleS Hardware System, it seems feasible to transfer these circuit designs to the new process technology. This option has been investigated within this work. In Chapter 5.5 the transfer of an existing operational amplifier design is described. In Chapter 8 the transfer of the full circuit used for neuron emulation in the BrainScaleS Hardware System is described.

# 4 Prototype Chips and Experimental Setup

After an initial evaluation of different process technologies, the focus was shifted towards the TSMC 65 nm low power process. Various circuits have been developed for this technology within this thesis and their performance has been evaluated in simulations. Additionally two prototype chips have been developed and tested. The aim was not only to verify the simulation results but also to test the full design flow required to bring the circuits to silicon. The prototype chips developed in the TSMC 65 nm process were submitted for fabrication within the MiniASIC program of EUROPRACTICE<sup>1</sup>.

Here a short overview of the circuits implemented in the individual chips is presented. All prototype chips have been tested using the same experimental setup which is described afterwards.

## 4.1 Schematic Diagrams

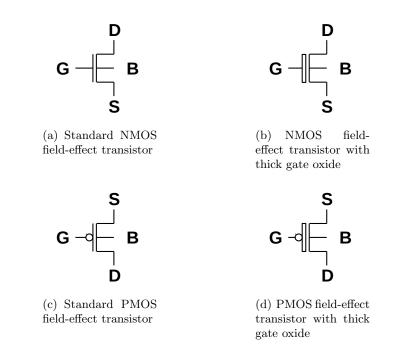

For most of the circuits presented within this thesis the corresponding schematic diagrams are shown. The term *schematic* will be used in the following as an abbreviation for *schematic diagram*. All transistors available in the TSMC 65 nm process technology are enhancement type metal-oxide-semiconductor field-effect-transistors (MOSFETs). In literature many different symbols representing MOS transistors in schematic diagrams can be found. To avoid confusion, the symbols used in the following are presented in Figure 4.1. Additionally the following conventions apply: If no bulk contact is shown for an NMOS transistor, its bulk is connected to ground. In case no bulk contact is shown for a standard PMOS transistor, its bulk is connected to the 1.2 V supply. For thick-oxide PMOS transistors the bulk is connected to the 2.5 V supply. In integrated circuits MOS transistors are usually completely symmetric regarding drain and source contact. Consequently there is no marking in the symbols distinguishing these terminals of the transistor. The terminal connecting to the channel of an NMOS transistor which is at the lower potential is considered to be the source contact, the one at the higher potential is referred to as the drain contact. For PMOS transistors the channel contact at the higher potential is referred to as source contact and the one at the lower potential is considered to be its drain.

<sup>&</sup>lt;sup>1</sup>www.europractice-ic.com

Figure 4.1: Symbols used in the schematics shown within this thesis. All transistors in the TSMC 65 nm process technology are enhancement type metaloxide-semiconductor field-effect-transistors.

As it is common practice, an inverted digital signal is marked by a bar over the signal's name.

## 4.2 Design Flow

The full process from simulating a few transistors of a simple analog circuit to a final mixed-signal chip containing several million transistors involves many different design steps which rely on correct usage of multiple software tools. In the following a short overview of the tools used for the implementation of the prototype chips in the TSMC 65 nm process technology is presented. A detailed description of the steps required to realize VLSI mixed-signal chips can be found in Grübl [2007, Chapter 2].

The analog circuits of the prototype chips have been designed and simulated using Virtuoso Analog Design Environment<sup>2</sup>. Additionally digital designs, described in the high-level hardware description languages Verilog [Verilog 2006] and System Verilog [SystemVerilog 2004], have been integrated into the chips. These are syn-

<sup>&</sup>lt;sup>2</sup>Cadence Design Systems, Inc., San Jose, CA, USA

thesized into a gate-level netlist using Design Compiler<sup>3</sup>. The synthesized netlist is mapped to a library of standard cells provided by TSMC and implemented by the Encounter Digital Implementation<sup>2</sup> tool. For the static timing analysis Prime-Time<sup>3</sup> is used. The layout of the final chip is checked for violations of the design rules provided by TSMC by Calibre DRC<sup>4</sup>. Calibre is also used for checking the equivalence of the layout against the toplevel netlist of the full design. The implementation flow was created by A. Grübl<sup>5</sup> and A. Hartel<sup>5</sup>. The digital logic in all test chips is designed for reliable operation at a clock frequency of 500 MHz.

## 4.3 The First Prototype Chip

The first prototype chip contains several analog circuits that allow for testing of basic characteristics of the process technology. In order to test the full design, optimization and verification flow for a digital design of reasonable complexity, an early version of the embedded plasticity processor developed within the Brain-i-Nets project [Brain-i Nets 2012] is included. Details on this 32-bit CPU<sup>6</sup>, which has been developed for implementation in the BrainScaleS wafer-scale hardware system, can be found in [Friedmann 2013, Chapter 5.2].

Several analog test circuits are implemented, the individual blocks are listed below. The digital circuits used to configure and control the analog blocks have been written in Verilog based on an example design provided by S. Friedmann<sup>5</sup>. For configuration of the digital control logic a JTAG interface is implemented [JTAG 2001]. The physical implementation of the digital circuits and the overall assembly of the components was done by G. Sidlauskas<sup>5</sup> and A. Grübel.

Analog and digital circuits on the chip are supplied by separate power nets in order to isolate the analog circuits from noise generated by the digital circuits. For both domains a 1.2 V supply as well as a 2.5 V supply, used in conjunction with thick-oxide transistors, are implemented. The in total four different power nets are termed VDD12D, VDD25D, VDD12A and VDD25A. Consequently there are also two separate ground nets, GNDD and GNDA, used for either digital or analog circuits.

In the first version of the chip, the processor was not working due to a mistake in the interface connecting it to the instruction memory. The memory was generated using a memory compiler tool provided from TSMC. The mistake in the interface was not discovered during simulations because the memory model from TSMC, delivered along with the memory macro, behaves differently than the actual memory. As a consequence TSMC offered a free run to submit a new version of the chip with a fixed memory interface. This opportunity was also used to include some minor changes in the analog part of the chip for the second revision. When describing

<sup>&</sup>lt;sup>3</sup>Synopsys, Inc., Mountain View, CA, USA

<sup>&</sup>lt;sup>4</sup>Mentor Graphics, Inc., Wilsonville, OR, USA

<sup>&</sup>lt;sup>5</sup>Kirchhoff Institute for Physics, Heidelberg University

<sup>&</sup>lt;sup>6</sup>Central Processing Unit

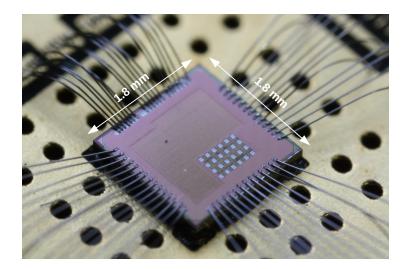

Figure 4.2: Photograph of the first prototype chip. In the lower right corner, the separate bond pads for the floating gate cells are visible. All other circuitry is covered by a grid of wires on the uppermost metalization layer, which distributes the supply voltage.

experimental results, the chips of the first revision are tagged by the number 1a.x where 1 refers to the first prototype chip, *a* refers to the version and *x* specifies the number of the individual chip. Accordingly results obtained from a chip of the second version will be tagged by 1b.x. Figure 4.2 shows a photograph of the first prototype chip bonded to a PCB using wedge bond technology. The physical size of the chip is  $1.8 \times 1.8 \text{ mm}^2$ .

The following list presents an overview for the circuits which have been implemented into the first version of the first prototype chip.

- The first prototype chip contains different designs of capacitive current storage cells. These devices can be used as programmable current sources which are typically required for adjustable analog circuits. The integrated circuits and experimental results are presented in Chapter 6.2.

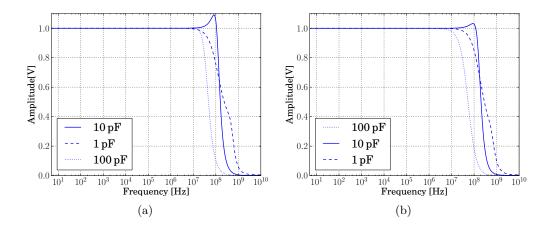

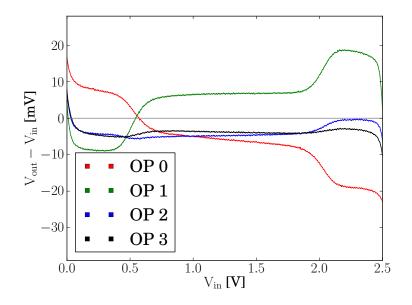

- An operational amplifier, originally designed for the 180 nm process, see Millner [2008], has been transferred to the new process using thick-oxide transistors. Information on the transfer process and measurement results are presented in Chapter 5.5.

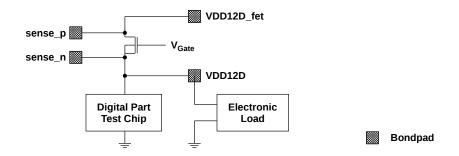

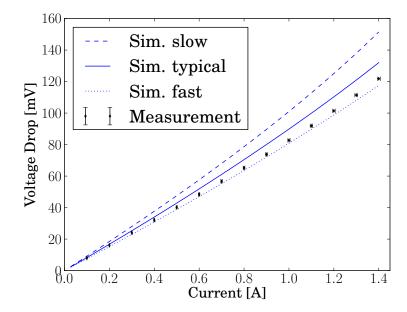

- To simplify the power management in future wafer-scale systems the option of integrated power switches is evaluated. The 1.2 V supply voltage of the test chip can be switched using an internal transistor, see Chapter 5.4.

- In modern semiconductor fabrication processes device mismatch is an important issue. To explore the properties of the process and compare the results

### 4 Prototype Chips and Experimental Setup

against the predictions of Monte Carlo simulations, 4 different sets of 256 identical transistors are implemented. All transistors are supplied with the same gate potential and the resulting drain currents can be measured individually for every transistor. Experimental results obtained from this circuit are not presented within this work but can be found in Graf [2011].

- A small array of 8 × 8 custom SRAM cells is implemented and tested. Information on the design of the cells as well as experimental results are presented in Chapter 5.1.

- In the BrainScaleS Hardware System programmable analog parameters are realized using floating gate devices. To see if this is an option also in the new process, 8 simple single-poly floating gate cells have been integrated. The contacts of the cells are connected to separate bond pads. Experimental results are presented not within this work but can be found in Hüll [2014].

The following changes have been made to the analog circuits for the second version:

- Two separate sense wires are added for the power switching transistor in order to measure the voltage drop over the transistor directly and without any deviations caused by the ohmic resistance of the metal routing and the bond wires, see Section 5.4.3.

- To investigate the spatial distribution of transistor mismatch in 2 dimensions the linear arrangements of transistors were replaced by an array of  $48 \times 128$  identical transistors, measurement results are discussed in Chapter 5.3.

- The floating gate cells have been replaced by an array of 3072 custom-designed SRAM bits. The supply voltage pin of the memory has been connected to a separate bond pad, allowing for direct measurements of the leakage current drawn in a static situation, see Chapter 5.2.

## 4.4 The Second Prototype Chip

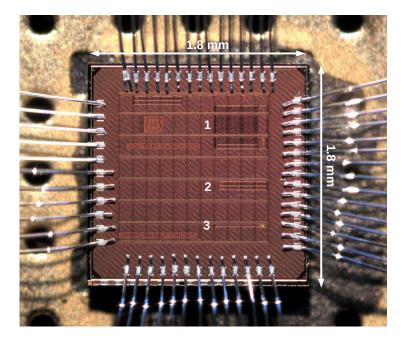

The circuits in the second test chip are focused on the development of more complex circuits, aiming directly at neuromorphic hardware as a target application. The analog circuits implemented are listed below. The digital control logic required for configuration and operation of the analog circuits has been written by A. Hartel. The general characteristics of the second chip are similar to the first one. The physical size is identical as well as the structure of the power and ground nets. Again a JTAG interface is used to control the digital part of the chip. Figure 4.3 shows a photo of the second prototype chip.

Correct operation of the analog circuits in conjunction with the digital control logic has been verified by a mixed-signal simulation environment. It combines

Figure 4.3: Photograph of the second prototype chip. The relative dimensions of the analog circuits on the chip are visible. 1: Array of  $32 \times 24$  capacitive memory cells, 2: Synapse RAM, 3: 32 Synapse DACs.

### 4 Prototype Chips and Experimental Setup

an analog simulation of the custom analog circuits, using Spectre<sup>2</sup> or Ultrasim<sup>2</sup>, with a event driven RTL<sup>7</sup> simulation of the digital components. This simulation environment was set up by A. Hartel. The physical implementation of the digital parts and assembly of all components of the chip was done by A. Hartel and A. Grübel.

The following circuits are integrated into the second prototype chip:

- An array of  $32 \times 24$  analog voltage and current storage cells, including control circuits that manage the programming and refreshing of the cells. The design and experimental results are discussed in Chapter 6.3.

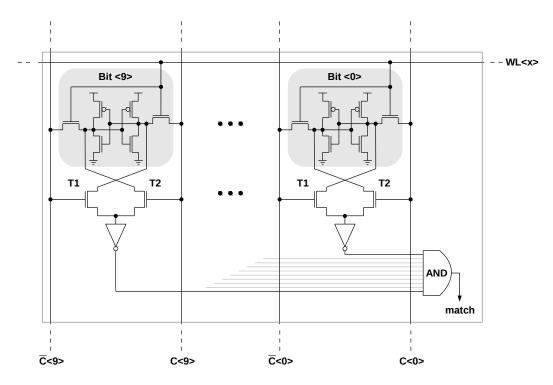

- A block of custom dual port SRAM, holding 256 × 32 bits, is tested. The timing for the SRAM operation is generated by analog circuits to allow for accesses within a single clock cycle. The internal structure of the memory is different from regular dual port SRAM. Specific modifications were made to fit the demands of storing synapse weights in an array optimized for digital processing of synaptic events. Details can be found in Chapter 7.2.

- A row of 32 unit-element current DACs with a resolution of 8 bit is integrated. It is designed to generate postsynaptic pulses in a synaptic array. A description of the design and experimental results are presented in Chapter 7.6.

Four individual chips, tagged chip 2.0 to 2.3, have been used for experiments. Chip 2.0 was severely damaged during testing, therefore results from this chip are only available for a limited number of measurements. Chip 2.1 shows an internal defect, the current consumption on the analog 2.5 V analog supply is 10 mA higher than for the other test chips. This observation is probably related to the fact that one of the output amplifiers which buffers an internal voltage is not working. The exact cause or characteristics of the defect could not be determined. Nevertheless, reasonable measurement results were obtained from chip 2.1 in most cases. However, some results show a high noise level, compared to the other test chips, which is considered to be a result of the internal defect.

## 4.5 The Experimental Setup

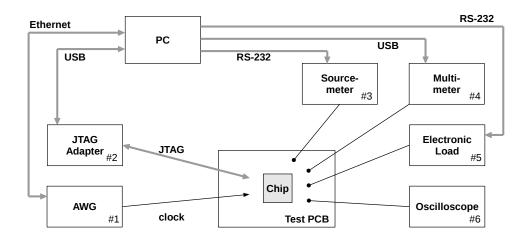

For testing of all prototype chips a basically identical experimental setup was used. Therefore a general description is given in the following. Figure 4.4 presents an overview of the experimental setup. In Table 4.1 the measurement instruments and signal generators used are listed.

<sup>&</sup>lt;sup>7</sup>Register Transfer Level

Figure 4.4: Overview for the setup used to test the prototype chips. Detailed information on the devices is given in Table 4.1

| # | Device             | Model                            |

|---|--------------------|----------------------------------|

| 1 | Waveform Generator | Tektronix AWG 7102               |

| 2 | USB-JTAG Adapter   | Xilinx Platform Cable USB II     |

| 3 | Sourcemeter        | Keithley 2635 SYSTEM Sourcemeter |

| 4 | Electronic Load    | BK Precision 8500                |

| 5 | Oscilloscope       | LeCroy Wave Runner HRO 64Zi      |

| 6 | Multimeter         | Keithley 2100 Multimeter         |

Table 4.1: Measurement devices and signal generators used for testing of the prototype chips.

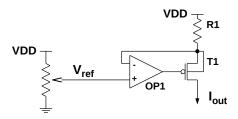

Figure 4.5: Schematic of the circuit used to generate bias currents for the prototype chips.

## 4.5.1 The Printed Circuit Boards

For testing, each of the prototype chips is glued to a custom-designed Printed Circuit Board (PCB). Wedge bonding technology is used to create electrical connections between the chips and the PCB. The two different versions of the first prototype chip use the same PCB, for the second prototype chip a similar one was designed.

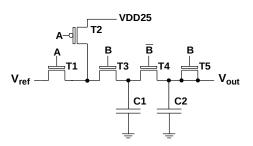

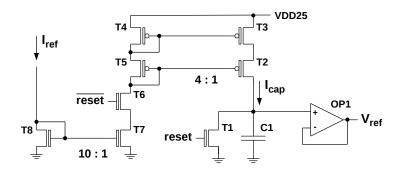

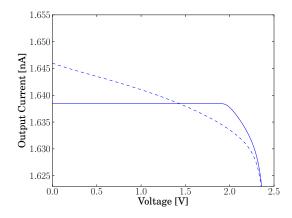

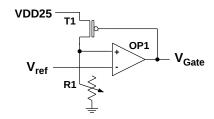

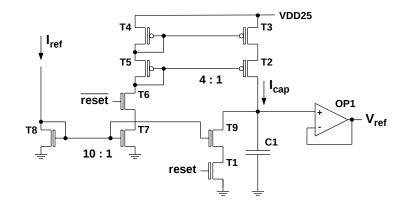

The main function of the test boards is to provide the connectors required for attachment of the measurement instruments and signal sources. Only a small number of active components is used on the boards. To achieve a low noise level, the analog supply voltages at levels of 1.2 V and 2.5 V for the chips are generated locally by linear voltage regulators. The digital supply voltages are directly generated by a standard laboratory voltage source. For several circuits implemented on the chips precisely adjustable bias currents in a range down to 20 nA are required. These are generated on the PCB by standard voltage-to-current converting circuits using operational amplifiers. The schematic of such a current source is shown in Figure 4.5. The operational amplifier OP1 controls the gate voltage of the transistor T1 such that the voltage drop over the resistor is equal to the reference voltage connected to its positive input. A corresponding circuit based on an NMOS transistor is used to provide adjustable current sinks. The reference voltages for the current sources as well as bias voltages for the chips are generated using precision potentiometers.

### 4.5.2 Software Setup

The experimental setup is controlled by a software program running on the host PC. It is written in C++ [cpp] and controls the operation of the digital part of the test chips via the implemented JTAG interface. The connection between chip and the host PC is realized using the Xilinx Platform Cable USB II. To control the USB-JTAG adapter cable the open source software UrJTAG [UrJTAG 2014] is integrated into the software framework. The general setup, especially the integration of the UrJTAG software, was done by S. Friedmann for testing of the processor implemented in the first prototype chip.

Additionally the software framework allows to control most of the other instru-

ments and devices, read back the measured data and stores it for further processing. The interfaces used for the individual devices are shown in Figure 4.4. The clock for the digital part of the prototype chip is generated by an Arbitrary Waveform Generator (AWG), it is configured by the PC over its Ethernet interface. Internship student J. Kunz helped to integrate the remote control functions of the AWG into the software framework. The integration of the Sourcemeter and the Electronic Load into the software framework was supported by internship student C. Graf.

# 5 Initial Evaluation of the 65 nm Process Technology

## 5.1 Custom Static Random Access Memory

Static Random Access Memory (SRAM) is typically the most efficient way to implement digital data storage into mixed signal VLSI chips. The term "static" refers to the fact that it reliably holds the stored data as long as it is powered, however it is volatile. In general it provides fast operation, a rather low static power consumptions and a reasonable density of bits per area.

In general, other memory concepts, such as Dynamic Random Access Memory (DRAM), provide a higher density. However DRAM is typically not suited for implementation into mixed signal chips. The single bits only have a limited storage time, a controller that performs regular refresh operations is required. This increases the overall complexity of the memory significantly and leads to a rather high static power consumption. The maximum possible density for DRAM is only achieved in chips fabricated in a technology that offers special process options.

In highly configurable neuromorphic mixed-signal circuits, configuration data for analog circuits is typically stored in custom SRAM. The internal state of the SRAM bits needs to be connected to the circuit which is configured, therefore the individual bits are integrated into the full custom layouts of the analog circuits. In the BrainScaleS Hardware System more than 38 MB of custom SRAM are integrated per wafer, covering approximately 10% of the total silicon area.

Custom cells of standard 6T SRAM have been designed in the 65 nm process technology and implemented into the first prototype chip.

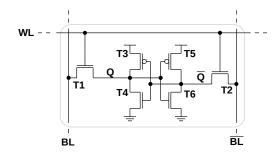

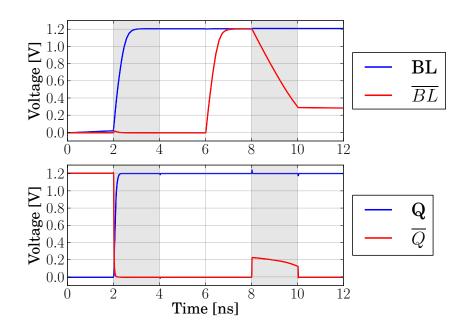

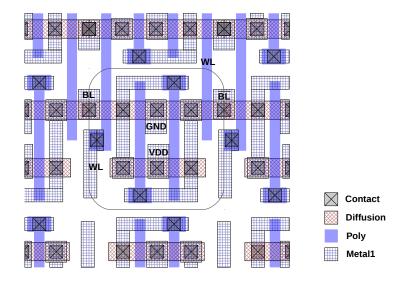

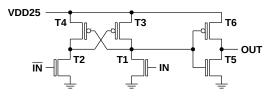

## 5.1.1 SRAM Operation

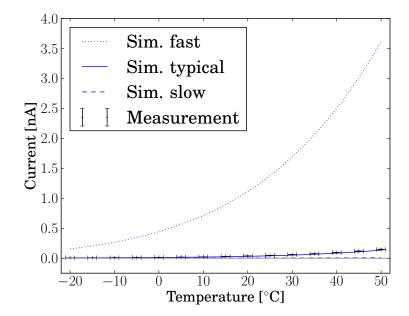

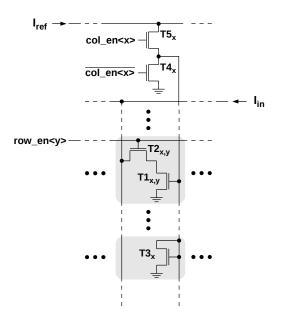

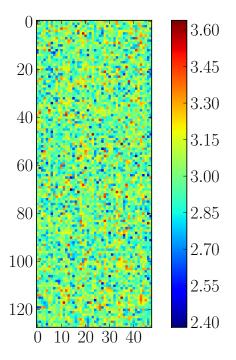

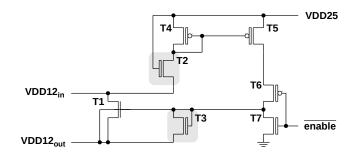

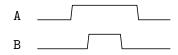

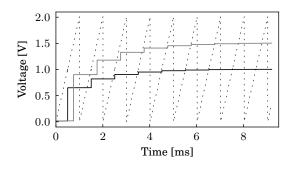

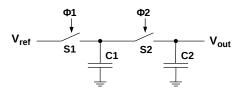

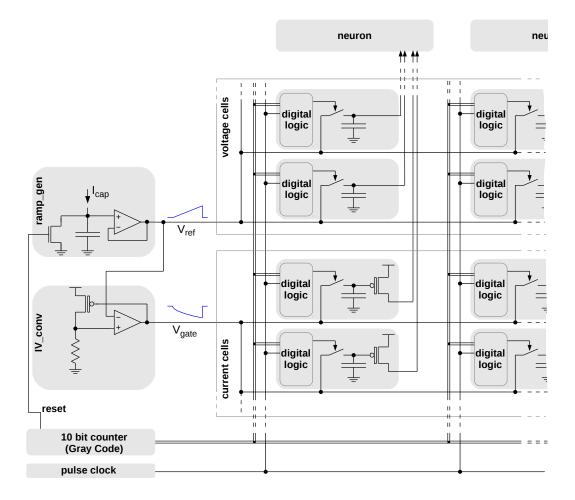

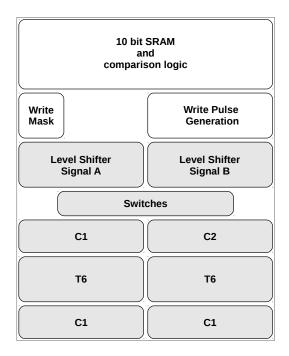

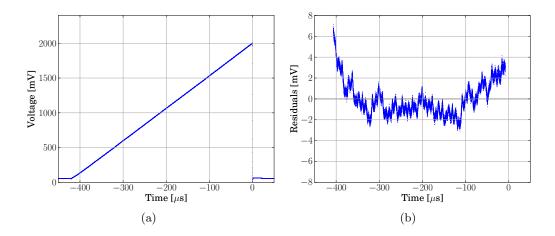

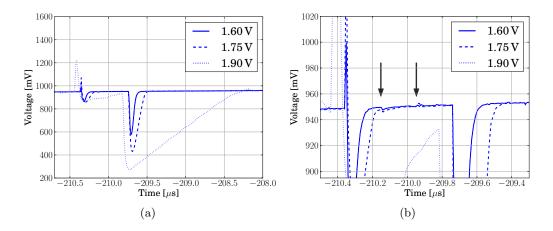

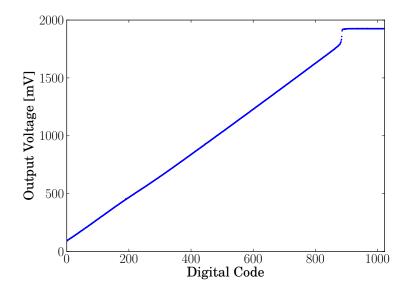

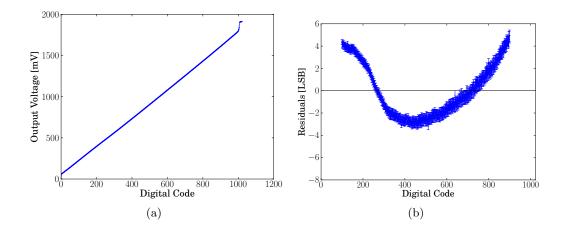

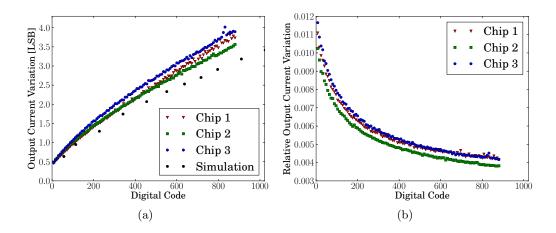

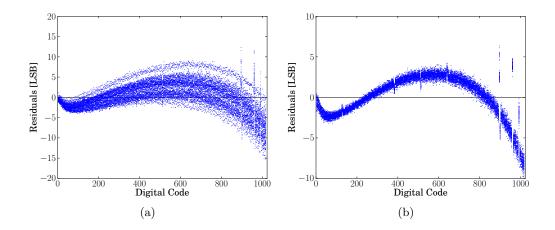

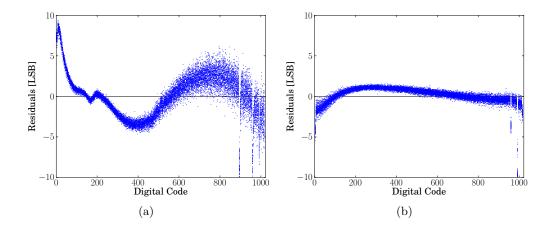

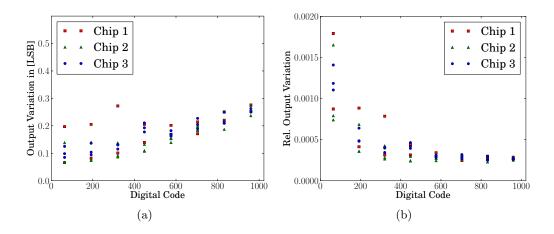

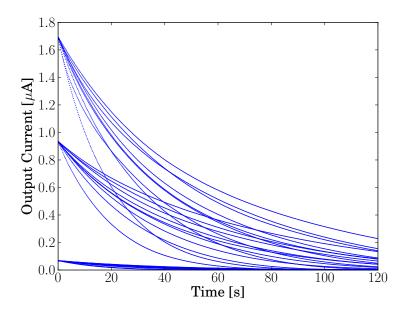

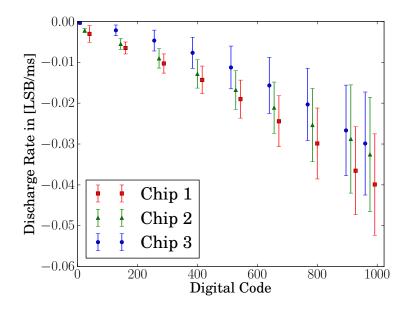

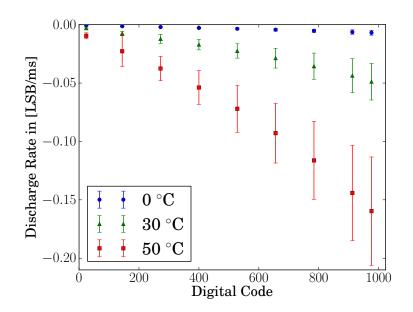

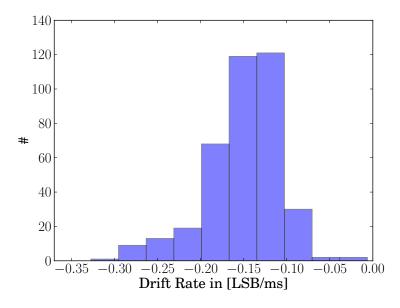

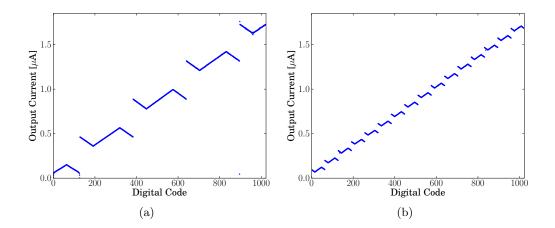

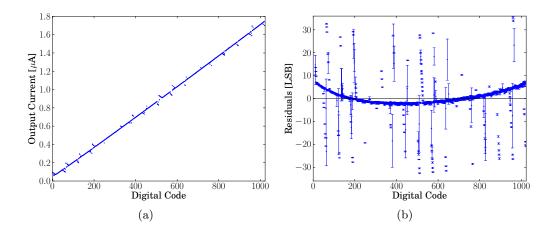

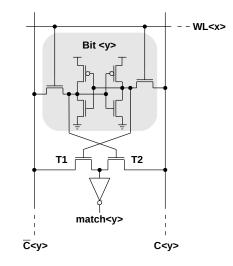

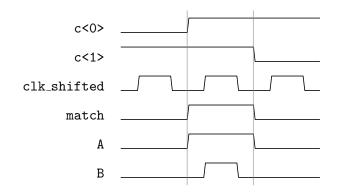

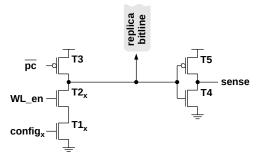

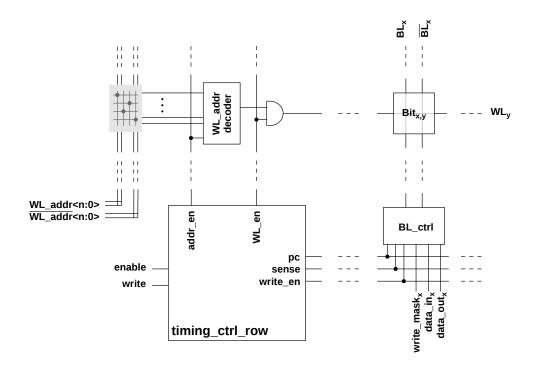

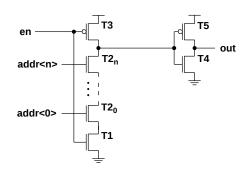

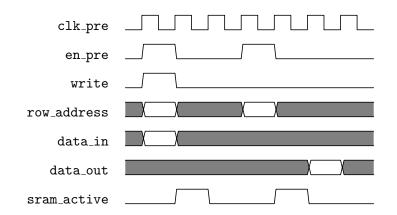

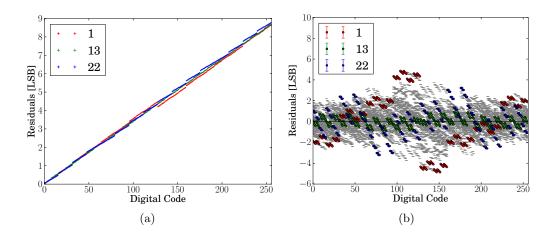

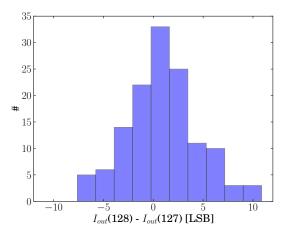

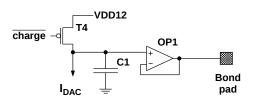

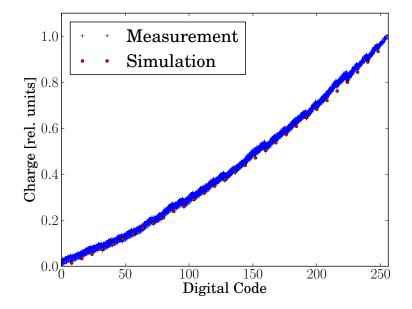

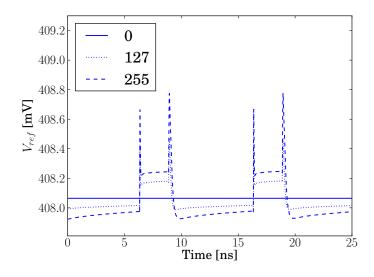

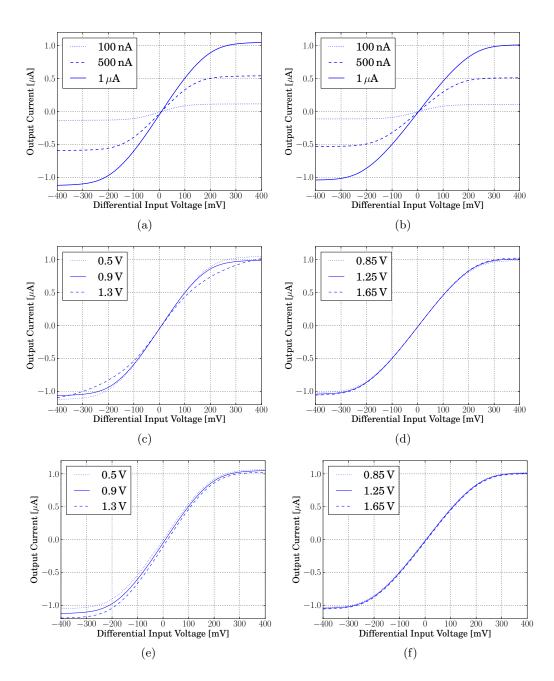

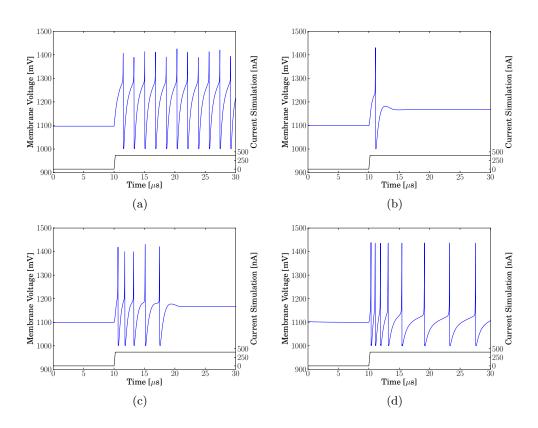

Figure 5.1 shows a schematic of a standard 6 transistor SRAM cell. The central element of SRAM cells is the latch built from transistors T2 to T6. These are connected to form two cross coupled inverters. Once written to one configuration, the latch holds its state, presenting a logical 1 at the output of one inverter ( $\mathbb{Q}$ ) and a logical 0 at the output of the other  $\overline{\mathbb{Q}}$ . In order to write or read the state of the latch, two additional transistors, T1 and T2, are required. These are typically termed the *access transistors* of the cell and connect the nodes  $\mathbb{Q}$  and  $\overline{\mathbb{Q}}$  to external signals.