### Dissertation

submitted to the

Combined Faculties for the Natural Sciences and for Mathematics

of the Ruperto-Carola University of Heidelberg, Germany

for the degree of

Doctor of Natural Sciences

Put forward by Dipl.-Phys. Paul Müller

born in Kujbyschew, Russia

Oral examination: 2017-11-02

# Modeling and Verification for a Scalable Neuromorphic Substrate

Referees: Prof. Dr. Karlheinz Meier

Prof. Dr. Michael Hausmann

#### Modeling and Verification for a Scalable Neuromorphic Substrate

Mixed-signal accelerated neuromorphic hardware is a class of devices that implements physical models of neural networks in dedicated analog and digital circuits. These devices offer the advantages of high acceleration and energy efficiency for the emulation of spiking neural networks but pose constraints in form of device variability and of limited connectivity and bandwidth. We address these constraints using two complementary approaches: At the network level, the influence of multiple distortion mechanisms on two benchmark models is analyzed and compensation methods are developed that counteract the resulting effects. The compensation methods are validated using a simulation of the BrainScaleS neuromorphic hardware system. At the single neuron level, calibration procedures are presented that counteract device variability for a new analog implementation of an adaptive exponential integrate-and-fire neuron model in a 65 nm process. The functionality of the neuron circuit together with these calibration methods is verified in detailed transistor-level simulations before production. The versatility of the circuit design that includes novel multi-compartment and plateau-potential features is demonstrated in use cases inspired by biology and machine learning.

#### Modellierung und Verifikation für ein skalierbares neuromorphes Substrat

Beschleunigte, digital-analoge neuromorphe Hardware ist eine Klasse von Systemen, welche physikalische Modelle neuronaler Netzwerke in dedizierten, analogen und digitalen Schaltungen implementiert. Diese Systeme bieten die Vorteile von Energieeffizienz und hoher Beschleunigung bei der Emulation von aktionspotenzial-basierten neuronalen Netzen, aber besitzen Einschränkungen bezüglich Konnektivität, Bandbreite und der Variation einzelner Komponenten. Der Einfluss dieser Einschränkungen wird in zwei komplementären Ansätzen behandelt: Auf der Netzwerkebene wird der Einfluss mehrerer Störmechanismen auf zwei Benchmarkmodelle analysiert und durch modellspezifische Kompensationsmethoden minimiert. Diese Methoden werden auf einem Simulationsmodell des neuromorphen BrainScaleS-Systems validiert. Auf der Neuronebene werden Verfahren zur Kalibration entwickelt, die der Komponentenvariation in einer Neuentwicklung eines analogen AdEx-Neuronmodells in einem 65 nm-Prozess entgegenwirken. Die Funktionalität der Neuronschaltung und der Kalibration wird in detaillierten Simulationen auf Transistorebene vor der Produktion verifiziert. Die Vielseitigkeit der Schaltung wird in Anwendungfällen demonstriert, welche von biologischen und abstrakten Modellen inspiriert sind.

# **Contents**

| C | Contents |                             |                                                               | 3  |  |  |

|---|----------|-----------------------------|---------------------------------------------------------------|----|--|--|

| 1 | Intr     | troduction                  |                                                               |    |  |  |

|   | 1.1      | Biolog                      | gical neurons                                                 | 10 |  |  |

|   | 1.2      |                             | eaky integrate-and-fire neuron model                          | 10 |  |  |

|   | 1.3      |                             | daptive exponential integrate-and-fire neuron model           | 13 |  |  |

|   | 1.4      |                             | ls of synaptic interaction                                    | 13 |  |  |

|   |          | 1.4.1                       | Current-based synapse model                                   | 14 |  |  |

|   |          | 1.4.2                       | Conductance-based synapse models                              | 14 |  |  |

|   | 1.5      | Synap                       | otic dynamics                                                 | 15 |  |  |

|   |          | 1.5.1                       | Tsodyks-Markram mechanism                                     | 15 |  |  |

|   |          | 1.5.2                       | Spike-timing-dependent plasticity                             | 16 |  |  |

|   | 1.6      | Comp                        | partmental models                                             | 16 |  |  |

|   | 1.7      | Accele                      | erated physical models                                        | 17 |  |  |

|   |          | 1.7.1                       | Hardware devices                                              | 18 |  |  |

|   | 1.8      | Samp                        | ling with leaky integrate-and-fire neurons                    | 18 |  |  |

| 2 | Con      | npensa                      | tion of network-level effects on a neuromorphic platform      | 23 |  |  |

|   | 2.1      | Wafer                       | -scale neuromorphic hardware                                  | 24 |  |  |

|   |          | 2.1.1                       | Hardware implementation                                       | 24 |  |  |

|   |          | 2.1.2                       | Supporting software                                           | 26 |  |  |

|   | 2.2      | 2 Structure of the analysis |                                                               |    |  |  |

|   | 2.3      | Simul                       | ation results                                                 | 29 |  |  |

|   |          | 2.3.1                       | Synfire chain with feed-forward inhibition                    | 29 |  |  |

|   |          |                             | Network description                                           | 29 |  |  |

|   |          |                             | Synapse loss                                                  | 31 |  |  |

|   |          |                             | Weight noise                                                  | 31 |  |  |

|   |          |                             | Non-configurable axonal delays                                | 34 |  |  |

|   |          |                             | Combined compensation on simulated hardware                   | 35 |  |  |

|   |          | 2.3.2                       | Cortical network with self-sustained asynchronous activity in |    |  |  |

|   |          |                             | a random network                                              | 36 |  |  |

|   |          |                             | Non-configurable axonal delays                                | 40 |  |  |

|   |          |                             | Weight noise                                                  | 40 |  |  |

|   |          |                             | Synapse loss                                                  | 40 |  |  |

4 CONTENTS

|   |     |         | Compensation method based on mean-field approach .      | . 44 |

|---|-----|---------|---------------------------------------------------------|------|

|   |     |         | Iterative compensation                                  | . 44 |

|   |     |         | Combined compensation on simulated hardware             | . 45 |

|   | 2.4 | Sumn    | nary                                                    | . 45 |

| 3 | Sim | ulation | n-based characterization of neuron circuits             | 49   |

|   | 3.1 | Introd  | duction                                                 | . 49 |

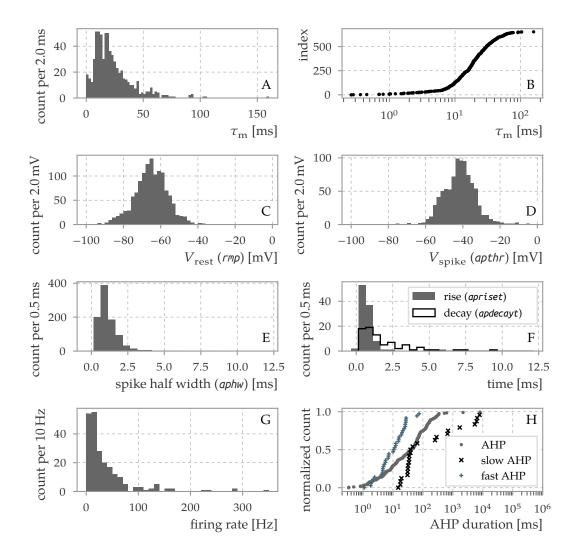

|   |     | 3.1.1   | Parameterization for biologically-inspired modeling     | . 50 |

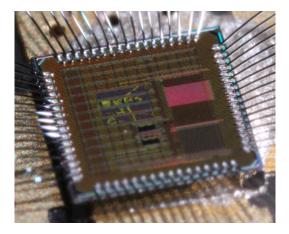

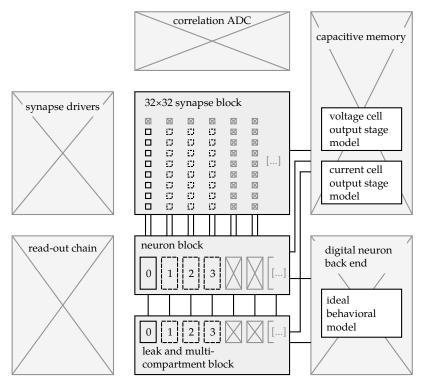

|   |     | 3.1.2   | Neuromorphic prototype chip                             | . 58 |

|   |     | 3.1.3   | Simulation setup                                        | . 59 |

|   |     |         | Integrated scope of simulation                          | . 59 |

|   |     |         | Software interface                                      | . 61 |

|   |     |         | Notation                                                | . 62 |

|   |     |         | Mismatch and process variations                         | . 64 |

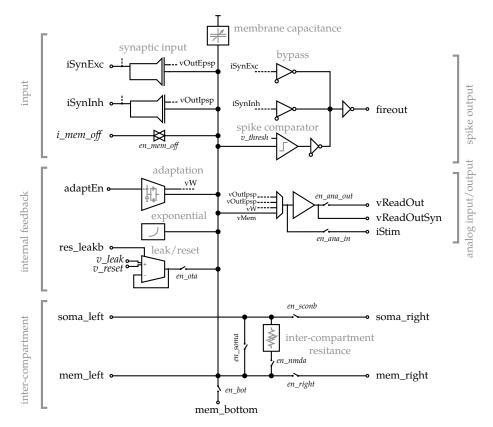

|   | 3.2 | The D   | DLS3 neuron                                             | . 65 |

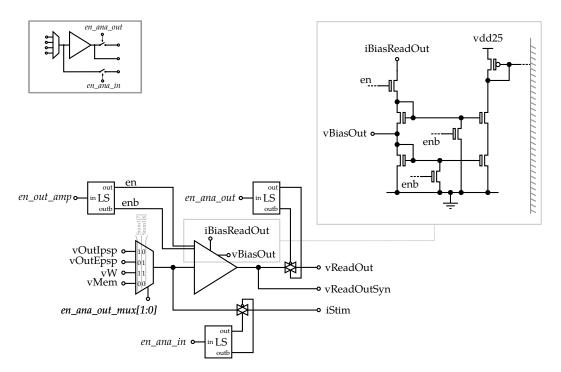

|   |     | 3.2.1   | Interface to the digital back end                       | . 67 |

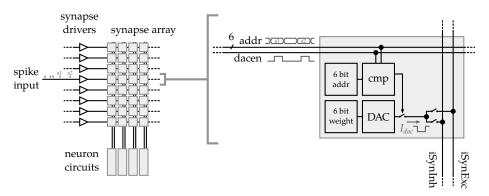

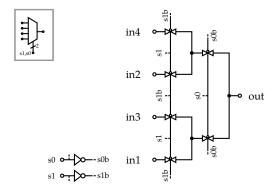

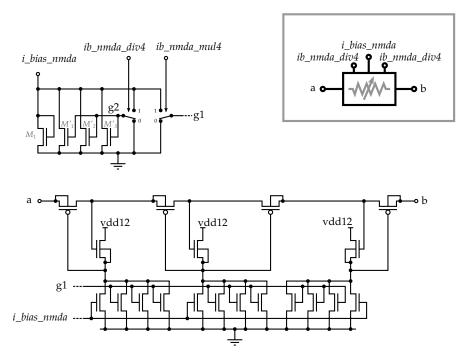

|   |     | 3.2.2   | Synaptic input                                          | . 69 |

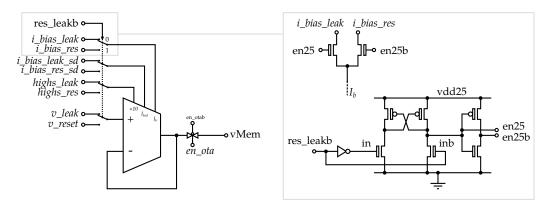

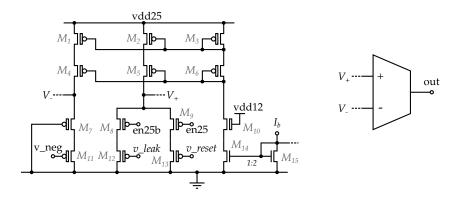

|   |     | 3.2.3   | Leakage and reset transconductance amplifier            | . 71 |

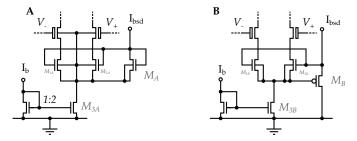

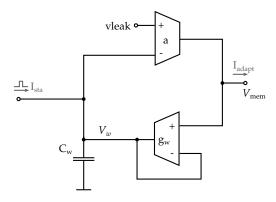

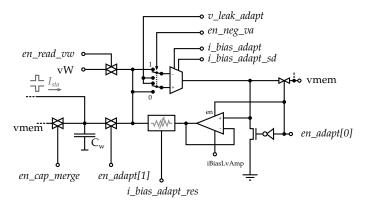

|   |     | 3.2.4   | Adaptation term                                         |      |

|   |     | 3.2.5   | Circuit implementation of sub-threshold adaptation      | . 74 |

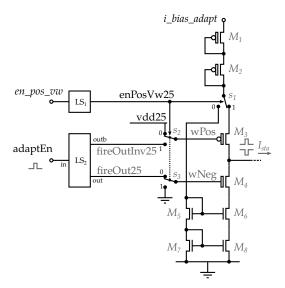

|   |     | 3.2.6   | Circuit implementation of spike-triggered adaptation    |      |

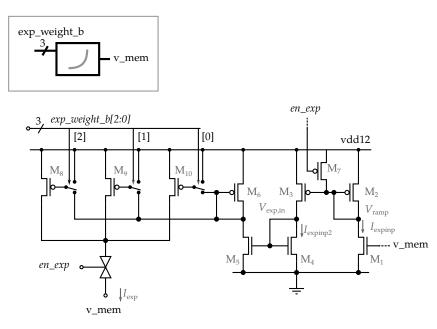

|   |     | 3.2.7   | Exponential term                                        | . 76 |

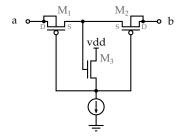

|   |     | 3.2.8   | Inter-compartment connectivity                          |      |

|   | 3.3 | Monte   | e-Carlo calibration                                     |      |

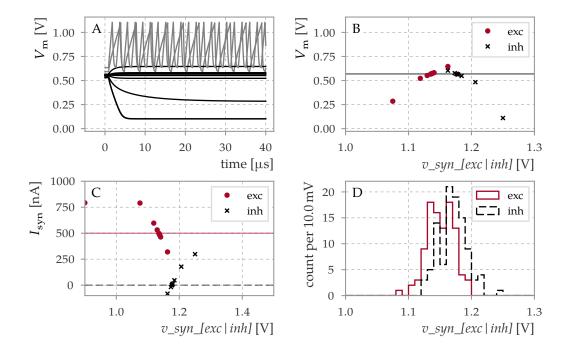

|   |     | 3.3.1   | Synaptic input                                          |      |

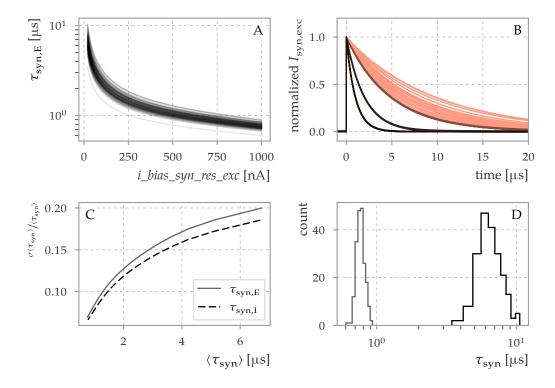

|   |     | 3.3.2   | Synaptic time constant                                  |      |

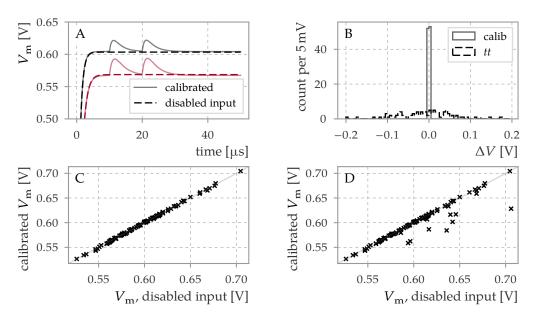

|   |     | 3.3.3   | Leakage and reset transconductance                      |      |

|   |     |         | Membrane time constant                                  |      |

|   |     |         | Resting potential                                       |      |

|   |     |         | Verification of leak calibration                        |      |

|   |     | 3.3.4   |                                                         |      |

|   |     | 3.3.5   | Synaptic efficacy                                       |      |

|   |     | 3.3.6   | Spike threshold                                         |      |

|   |     | 3.3.7   | Adaptation                                              |      |

|   |     |         | Adaptation coupling parameter <i>a</i>                  |      |

|   |     |         | Voltage-based calibration method for subthreshold adap- |      |

|   |     |         | tation                                                  |      |

|   |     |         | Adaptation time constant $\tau_w$                       |      |

|   |     |         | Spike-triggered adaptation $b$                          |      |

|   |     | 2.2.2   | Application of calibration                              |      |

|   | o . | 3.3.8   | Exponential term                                        |      |

|   | 3.4 | -       | roduction circuit verification                          |      |

|   |     | 3.4.1   | Test of digital configuration                           |      |

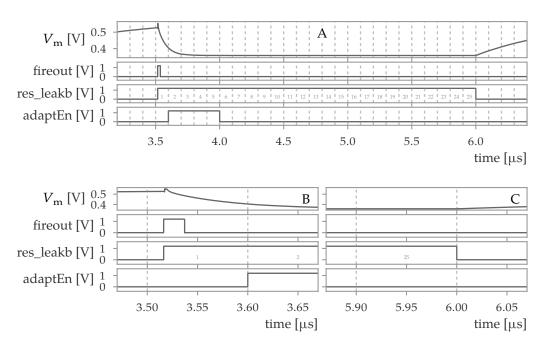

|   |     | 3.4.2   | Adaptation term                                         | 120  |

CONTENTS 5

|     |         | Leakage in the capacitance merge switch                              | 120 |

|-----|---------|----------------------------------------------------------------------|-----|

|     |         | Leakage through read-out multiplexer                                 | 120 |

|     |         | Leakage onto capacitive memory cell                                  | 121 |

|     |         | Digital-analog adaptation pulse interface                            | 121 |

|     |         | 3.4.3 Spike-triggered adaptation signal                              | 121 |

|     |         | 3.4.4 Leak and reset term                                            | 122 |

|     |         | Leakage between analog memory cells                                  | 122 |

|     |         | Process corner dependency of level shifter                           | 123 |

|     |         | 3.4.5 Summary                                                        | 123 |

|     | 3.5     | Full neuron test cases                                               | 125 |

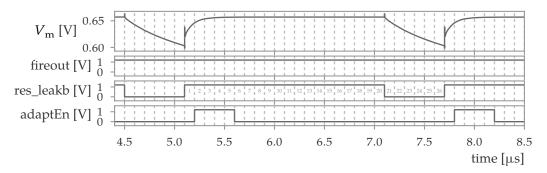

|     |         | 3.5.1 Firing patterns in the AdEx model                              | 125 |

|     |         | 3.5.2 LIF-sampling calibration using novel reset functionality       | 129 |

|     | 3.6     | Multi-compartment simulations                                        | 136 |

|     |         | 3.6.1 Inter-compartment conductance circuit                          | 136 |

|     |         | 3.6.2 Active neuron compartments                                     | 136 |

|     |         | 3.6.3 Backpropagation-activated calcium spike firing                 | 139 |

|     |         | Active and nonlinear currents in compartmental models .              | 139 |

|     |         | Circuit simulation                                                   | 141 |

|     |         | Stability of the configuration                                       | 142 |

|     |         | 3.6.4 Summary                                                        | 145 |

|     | 3.7     | Chip measurements                                                    | 147 |

|     |         | 3.7.1 Adaptation and exponential term                                | 147 |

|     |         | 3.7.2 Inter-compartment conductance                                  | 147 |

|     |         | 3.7.3 Erroneous capacitive memory interface                          | 149 |

|     | 3.8     | Summary                                                              | 151 |

| 4   | Con     | clusion and outlook                                                  | 155 |

| Re  | ferer   | nces                                                                 | 163 |

|     |         |                                                                      |     |

| Lis | st of 1 | Figures                                                              | 179 |

| Lis | st of [ | Tables                                                               | 182 |

| A   | Add     | litional data and figures                                            | 183 |

|     | A.1     | Synfire chain with feed-forward inhibition                           | 183 |

|     |         | A.1.1 Model parameters                                               | 183 |

|     |         | A.1.2 Filtering of spontaneous activity                              | 183 |

|     | A.2     | Cortical network with self-sustained asynchronous activity in a ran- |     |

|     |         | dom network                                                          | 185 |

|     |         | A.2.1 Model parameters                                               | 185 |

|     | A.3     | Default parameters for DLS3 testbench                                | 186 |

|     | A.4     | LIF sampling                                                         | 188 |

|     | A.5     | Reset current                                                        | 189 |

|     | A.6     | Adaptation calibration                                               | 190 |

|     |         |                                                                      |     |

6 CONTENTS

| <b>A</b> .7 | Bistable firing                                          | 190 |

|-------------|----------------------------------------------------------|-----|

| A.8         | Alternative implementation concept of adaptation circuit | 191 |

| A.9         | Calibration of synaptic weight                           | 193 |

| A.10        | Distribution of maximal synaptic input currents          | 194 |

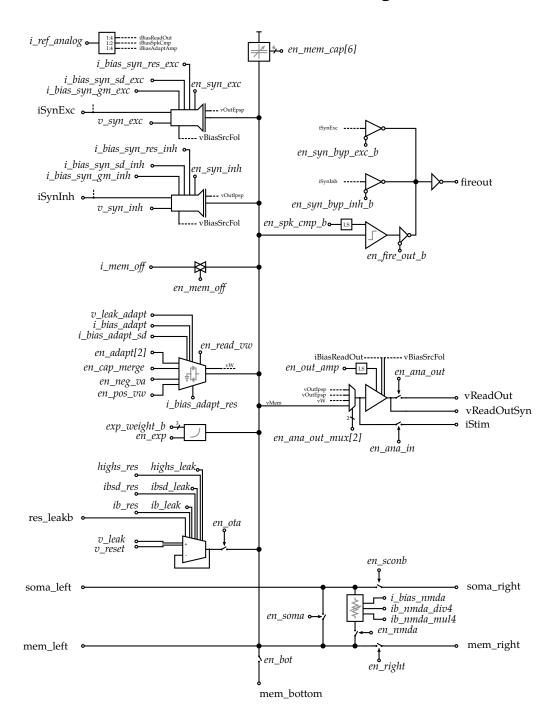

| A.11        | DLS3 neuron schematic with configuration variables       | 195 |

## Chapter 1

## Introduction

The advancement of the information age is characterized by the dependency of the global society on the reliable handling and processing of ever growing volumes of data. Driven by the exponential increase in computing power and storage capacity (Mack, 2011; Moore, 1965; Leventhal, 2008), mechanized data processing becomes ever more impressive, affecting not only our day-to-day life but also being deployed in contexts with high demands on reliability to guarantee human safety or economic efficiency. This is made apparent by the progress of, for example, simple automatic brakes on railway trains (De Nicola et al., 2005) to fully automatic vehicles navigating normal road traffic, a colossal computational difference between the correlation of a semaphore signal and the speed of a railroad cart and the real-time processing of high-bandwidth input signals under greatly varying environmental conditions (Bojarski et al., 2016). From automatically sorting mail using handwritten text to recognizing human faces and understanding voice commands on mobile devices, from beating novice players at checkers (Samuel, 1967) to winning against world-class players in the games of chess (Deep Blue vs. Kasparov, 1997) and Go (Silver et al., 2016), from simple dictionary-based translation to automatic subtitle generation for video footage, a significant part of the machine learning field is dominated by algorithms based on neural networks. Prominent examples of network models are LSTM, convolutional neural networks and Deep Boltzmann Machines (Hochreiter and Schmidhuber, 1997; Salakhutdinov and Hinton, 2009). These networks are the mathematical successors of networks loosely based on the structure that is observed in the human brain. Each neuron possesses a state which is determined by the state of the neurons connected to it and the properties of the connection. The ability to tune this connectivity - in many models represented as a connection matrix - to make an abstract network perform its desired task is one of the key components to making them so successful in a variety of tasks.

The human brain is an exceptional information processing and learning machine by itself. Humans can learn to perform a multitude of highly different tasks, and do so with a comparatively low power consumption, commonly given as 20 W (Raichle and Gusnard, 2002, 20 % of calorie intake). This kind of generality and efficiency makes understanding the computation in the human brain a highly valuable effort,

in addition to the possible positive effects on health and society. It is not clear yet to what extent the difference between the comparatively simple representation of neurons and synapses in abstract neural networks and the complex dynamics of biological neurons is rooted in the disparity of the underlying substrates – and in how far the biological realization is optimized by evolution for the information processing tasks the brain has to perform.

The field of computational neuroscience is dedicated to understanding the individual and collective behavior of biological neurons as well as their computational potential. A central tool for this endeavor is the simulation of spiking networks. The time evolution of a network of neurons – modeled by mathematical descriptions of neurons and synapses of a highly varying degree of simplification – is solved numerically to obtain insight into the emergent behavior of the system. This numeric solution is costly in terms of computational resources, time and power consumption. Kunkel et al. (2014), for example, demonstrate a large-scale simulation with  $1.86 \times 10^9$  neurons which requires approximately 40 minutes for one second of simulated time on the K supercomputer.

One alternative is the construction of dedicated hardware which is designed to optimize the simulation of spiking networks. As it is not meaningful to try to compete with the generality of simulations running on conventional compute clusters, such devices are typically specialized for a set of tasks. One such approach is *neuromorphic computing* with mixed-signal devices. One core characteristic is that neurons are represented by a *physical model*, a dedicated analog circuit that mimics the dynamics of a biological neuron. The membrane capacitance of the neuron is represented by a physical capacitor and the currents that govern the neuron's behavior are emulated by analog circuits. The possible values of specific capacitance and utilized currents in standard VLSI processes make it easy to realize time constants far below those of typical biological neurons. Exploiting this fact, mixed-signal accelerated neuromorphic systems are constructed which implement analog neurons with a configurable connection matrix that allows to realize networks of vastly different topologies.

Each neuron and network model possesses an intrinsic level of deviation from the system it models: The simple leaky integrate-and-fire point neuron model, for example, does not capture the complex nonlinearities and spatial extent of the biological reference. Even a numerical model does not, in general, exactly capture its mathematical archetype, but rather is built to allow a control over the resulting error due to, e.g., discretization in time, space or limited resolution of values. The final appearance of any given model is driven not only by the faithful reproduction of the investigated system but, to a large extent, by what is easy to implement and control while still capturing the essential behavior of the system. For mathematical models it may be the existence of a mathematical tool set that facilitates the analysis of the given structure, such as the Rall model (Rall, 1959) for dendritic structures, the Ising model for the understanding of magnetism or the mean field approach to the description of neural networks (Brunel, 2000). For simulation, it is the availability of appropriate algorithms as well as software packages that allow the efficient implementation

of the model (Eppler et al., 2008; Hines and Carnevale, 2003). Valuable insights which result from the analysis of these models are characterized by their capacity to generalize to similar systems, the Ising model, for example, being a fundamental example of phase transitions in magnetic materials.

In the case of mixed-signal accelerated neuromorphic systems, the components that are promising to construct are energy- and area-efficient circuits with a high speedup compared to their biological counterparts. The advantages of the speedup and power consumption are gained at the cost of flexibility of implementation and parameterization, and at the cost of the homogeneity of the underlying substrate: First, the flexibility of implementation is limited to the amount that is provided by the circuit designer. In contrast to a software simulation, where, in principle, an arbitrary part of the model can be replaced quickly, the circuit implementation on a chip can not be modified once it is produced. To provide a flexible substrate for the user, the circuits are made configurable by including parameters which can be changed at runtime. Second, this parameterization does not achieve the gigantic range of double-precision floating-point numbers one is used to in software simulations, but is limited to few orders of magnitude at best. Finally, the size reduction is usually carried to a domain where device mismatch becomes significant (Pelgrom et al., 1989). Thus, the user has to cope with the fact that identically parameterized components behave differently due to variations in production.

We emphasize that the goals of neuromorphic computing are twofold, namely to help identify and understand effective paradigms of spike-based computation, and to uncover efficient hardware implementations of these computational concepts. Overcoming the constraints that are outlined above is an important step on the path to achieving these goals.

This thesis approaches the problems described above in two complementary ways. In the first part, we start from network models that are used in existing computational studies of spiking neural networks. Distortions that are expected and measured on neuromorphic hardware devices are identified and modeled in an idealized way. The effect of these distortions is investigated for each mechanism individually, providing compensation methods that counteract each distortion. In a final step, the developed compensation methods are validated with all modeled distortions using a simulated neuromorphic hardware. The result is a set of exemplary compensation methods for different network models.

In the second part of this thesis, the performance of individual neuron circuits is examined in more detail. The distortion mechanisms used in the initial study are idealized and do not cover the full range of possible effects. In the second part, a detailed transistor-level simulation of the neuron implementation in development is performed. Use cases derived from biological and abstract models are used to test the operation of the circuit in simulation, testing novel features that implement multi-compartment functionality and plateau-potentials as well as the re-implementation of features from a previous hardware generation. A detailed analysis of the expected parameter ranges, limitations and variation in the circuit is presented, along with a simulation-based pre-production verification which helped remedy mistakes in the

circuit design.

This document is organized as follows: The last part of this chapter provides an introduction to the mathematical and electronic modeling of spiking neurons. In chapter 2, the study of network-level anomalies introduced by their emulation on neuromorphic devices is presented. The simulation-based characterization and pre-production verification is discussed in chapter 3.

#### 1.1 Biological neurons

The human brain contains approximately  $86 \times 10^9$  neurons (Azevedo et al. (2009)) which form the computational substrate for the complex cognitive tasks that humans can perform. The cell body of the neuron is called the *soma*, from which long extensions, the axon and dendrites protrude (fig. 1.1). A voltage is maintained across the cell membrane by active ion pumps, leading to a decreased concentration of Na<sup>+</sup> and an increased concentration of  $K^+$  ions inside the cell. The resting potential is given as negative by convention and amounts to approximately -70 mV. The soma can generate a sharp voltage peak, called action potential, which is transported along the axon. Synapses are formed between the axon and dendrites of other neurons. The pre- and postsynaptic cell membranes are in close proximity at the synaptic cleft. When an action potential propagates along the axon it triggers the release of neurotransmitters at the presynaptic site which bind to and activate receptor molecules within the membrane of the postsynaptic neuron. The receptors can open ligand-gated ion channels, leading to a flux of ions through the membrane and leading to a post-synaptic potential (PSP), which can be positive (excitatory) or negative (inhibitory) in voltage. The PSPs are summed electrically at the soma where an action potential is generated when - in the simplest possible model the membrane potential exceeds a certain threshold. One of the most influential models for the computational investigation of neurons is the Hodgkin and Huxley model (Hodgkin and Huxley (1952)), which explains the mechanism behind the generation of the action potential in the giant axon of the squid. Their experimentally validated model contains sodium and potassium conductances which open and close according to an intrinsic, time- and voltage dependent dynamics.

For the investigation of large networks on an abstract level, the mechanism of spike generation is far less important than the interaction between neurons. Simple neuron models offer the advantages of requiring less computational resources for simulation and are easier to handle analytically. Two of such low-dimensional, threshold-based neurons models, leaky integrate-and-fire (LIF) and adaptive exponential integrate-and-fire (AdEx), are described in the following.

#### 1.2 The leaky integrate-and-fire neuron model

The LIF neuron model is one of the simplest models that capture the basic properties of temporal integration and all-or-none spike emission. It describes a passive leaky

**Figure 1.1:** Morphology of a layer 5 neuron from rat neocortex (Chen et al. (2014)). Data provided by Ascoli et al. (2007) via *NeuroMorpho.org*. The rectangle on the right represents the area of a single hardware neuron on the HICANN DLS2 chip (Aamir et al. (2016)), without synapses, at the same scale with a length of 200 μm.

integrator, in which the time constant  $\tau_m$  is given by  $\frac{C_m}{g_1}$ , the membrane capacitance and the leakage conductance of the membrane (Stein, 1967; Gerstner and Kistler, 2002):

$$C_{\rm m} \frac{\mathrm{d}V_{\rm m}}{\mathrm{d}t} = -g_{\rm l}(V_{\rm m} - V_{\rm leak}) + I \tag{1.1}$$

The current I comprises the synaptic input and, e.g., external stimulus current that is applied to the neuron.  $V_{\text{leak}}$  is leak potential of the neuron.

This linear differential equation is expanded to a spiking neuron model by introducing an explicit firing mechanism: The membrane potential is reset immediately after it reaches the firing threshold  $V_{\rm thresh}$ . After each spike, the membrane potential is held constant at the reset potential  $V_{\rm reset}$  (fig. 1.2).

$$\begin{split} &V_{\rm m}(t_{\rm spike}) = V_{\rm thresh} \\ \Rightarrow & \forall t \in \left(t_{\rm spike}; t_{\rm spike} + \tau_{\rm ref}\right] : V_{\rm m}(t) = V_{\rm reset} \end{split} \tag{1.2}$$

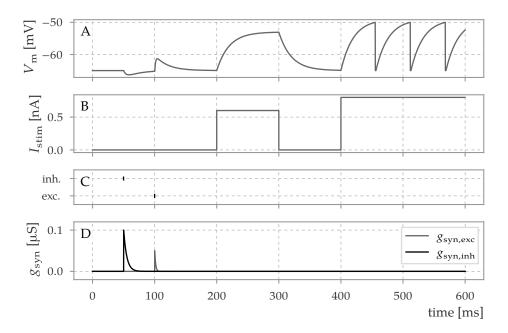

Figure 1.2: Leaky Integrate-and-Fire neuron model with exponential, conductancebased synapses. A: Membrane potential  $V_{\rm m}$  of the simulated neuron. **B**: Stimulus current of 600 pA between 200 ms to 300 ms and 800 pA between 400 ms to 600 ms is added to the membrane capacitance, causing an exponential approach of the membrane voltage towards the new resting state. When the membrane voltage reaches the firing threshold of  $V_{\rm thresh} = -50 \,\mathrm{mV}$  it is held at the reset voltage  $V_{\rm reset} = -65 \,\mathrm{mV}$  for the duration of  $\tau_{ref} = 1$  ms. **C**: The neuron is stimulated by inhibitory and excitatory input at 50 ms and 100 ms. **D**: Each synaptic event causes an instantaneous increase of the synaptic conductance  $g_{\text{syn,I}}$  and  $g_{\text{syn,E}}$  by the corresponding synaptic weight, here  $w_{\rm I}=100\,{\rm nS},\,w_{\rm E}=50\,{\rm nS}.$  When no input arrives, each synaptic conductance variable decays to zero with its synaptic time constant  $\tau_{\text{syn,I}}$  and  $\tau_{\text{syn,E}}$ . Note that the PSP of the inhibitory input is smaller than that of the excitatory one, even though the inhibitory weight and time constant are greater. This is caused by the inhibitory reversal potential  $E_{\text{rev,I}} = -70 \,\text{mV}$  being closer to the resting potential  $V_{\text{leak}} = -65 \,\text{mV}$  than the excitatory reversal potential  $E_{\text{rev,E}} = 0 \,\text{mV}.$

# 1.3 The adaptive exponential integrate-and-fire neuron model

The one-dimensional LIF model is a simple and widely used model of spiking neurons that provides an easy approach to simulation and analytical investigations. The observation of widely varying, complex responses in cortical neurons (Markram et al., 2004) has driven the investigation of simple neuron models that can expand the diversity of the model dynamics while still being computationally affordable (Izhikevich, 2004). One prominent model is described in (Izhikevich, 2003). It extends the LIF model by adding a non-linear, quadratic term to the derivative of the membrane potential and introducing an adaptation variable, which gives the neuron model a memory beyond the time of its last reset.

The AdEx model introduced in (Brette and Gerstner, 2005) is a similar nonlinear, adaptive two-dimensional neuron model. However, it employs an exponential function as nonlinearity for the voltage feedback, which conforms to experimental data (Badel et al., 2008).

$$C_{\rm m} \frac{\mathrm{d}V_{\rm m}}{\mathrm{d}t} = -g_{\rm l}(V_{\rm m} - V_{\rm leak}) + g_{\rm l}\Delta_{\rm T} \exp\left(\frac{V_{\rm m} - V_{\rm T}}{\Delta_{\rm T}}\right) - w + I \tag{1.3}$$

$$\tau_{\rm w} \frac{\mathrm{d}w}{\mathrm{d}t} = a(V_{\rm m} - V_{\rm leak}) - w \tag{1.4}$$

The adaptation current w is coupled linearly to the membrane potential via the subthreshold adaptation a and has a time constant  $\tau_{\rm w}$ . The width of the exponential current is controlled via the slope factor  $\Delta_{\rm T}$  while the spike threshold  $V_{\rm T}$  controls the location of its onset. The factor in front of the exponential term  $g_1\Delta_{\rm T}$  is chosen such that  $\frac{\rm d}{{\rm d}V_{\rm m}}\frac{{\rm d}V_{\rm m}}{{\rm d}t}=0$  at  $V_{\rm m}=V_{\rm T}$ . An explicit threshold voltage as in eq. (1.2) is used in practice, even though one could formally define the spike time as the time at which  $V_{\rm m}$  grows towards infinity (Brette and Gerstner, 2005).

#### 1.4 Models of synaptic interaction

The neuron models that are presented in section 1.2 and section 1.3 are missing an essential detail to use them for simulating network activity: the synaptic interaction between neurons. We enumerate the spike times of neuron j in a network

$$t_{\text{sp},ji}$$

$i \in \{1, \dots, \text{number of spikes of neuron } j\}$

A simple interaction model would be to directly increment the membrane voltage of the postsynaptic neuron proportionally to the synaptic weight of the coupling (e.g. Brunel, 2000). This is equivalent to a synaptic current that is a sum of delta functions:

$$I_{\text{syn},k}(t) = \sum_{j} \sum_{i} w_{jk} \delta(t - t_{\text{sp},ji} - \Delta)$$

(1.5)

Here,  $\Delta$  stands for the transmission delay between pre- and postsynaptic neuron.

#### 1.4.1 Current-based synapse model

In biological neurons, the time scale of synaptic interaction is not negligibly short. This is accommodated by replacing the delta function in eq. (1.5) by an interaction kernel with a finite length.

$$I_{\text{syn},k}(t) = \sum_{i} \sum_{i} w_{jk} \kappa(t - t_{\text{sp},ji} - \Delta)$$

(1.6)

A common interaction kernel is a step in the current, followed by an exponential decay.

$$\kappa(t) = \theta(t) \exp\left(\frac{-t}{\tau_{\text{syn}}}\right) \tag{1.7}$$

with  $\theta$  being the Heaviside step function.

Other interaction kernels are used to, e.g, include the rise time of the synaptic interaction, leading to a difference-of-exponentials or alpha-shaped kernels

$$\kappa_{\alpha}(t) = \theta(t) \frac{1}{\tau_{s}} \exp\left(\frac{-t}{\tau_{s}}\right)$$

(1.8)

$$\kappa_{\rm de}(t) = K * \theta(t) \left[ \exp\left(\frac{-t}{\tau_1}\right) - \exp\left(\frac{-t}{\tau_2}\right) \right].$$

(1.9)

The kernels shown above possess the helpful property that they are the Green's function of a low-dimensional differential operator. Assuming equal time constants for all synapses this allows one to equivalently write, e.g., eq. (1.6) with the exponential kernel eq. (1.7) as

$$\frac{\mathrm{d}I_{\mathrm{syn}}}{\mathrm{d}t} = \frac{-1}{\tau_{\mathrm{syn}}}I_{\mathrm{syn}} + \sum_{i}\sum_{i}w_{jk}\delta(t - t_{\mathrm{sp},ji} - \Delta) \tag{1.10}$$

This formulation allows to combine the effect of all synaptic interactions with the same synaptic time constant into one dynamic variable, which can reduce the memory requirement in the simulation of spiking neurons. (See, e.g., Brette (2006) for an in-depth description of an efficient simulation of neuron models.) The time constants of synaptic ion channels are different for different synaptic transmission mechanisms, such as relatively fast dynamics AMPA and GABA<sub>A</sub> and slower dynamics in NMDA and GABA<sub>B</sub> receptors (Destexhe et al., 1998). Because of this, separate time constants are typically provided for the simulation of spiking neurons. The software package PyNN (Davison et al., 2008), for example, provides separate parameters for excitatory and inhibitory synaptic time constants in its default neuron models.

#### 1.4.2 Conductance-based synapse models

A more realistic model of synaptic interaction is that of *conductance-based* synapses (Meffin et al., 2004). Synaptic interaction causes the opening of ion channels for specific ion types, which possess distinct reversal potentials. One consequence of

this is the observation of the so-called *high-conductance state* in neocortical neurons (Destexhe et al., 2003), where an increased total conductance changes the effective input resistance and the temporal resolution of a neuron.

In conductance-based models, the synaptic conductance takes the place of the linear summation of individual post-synaptic kernels eq. (1.6):

$$\frac{\mathrm{d}g_{\mathrm{syn}}}{\mathrm{d}t} = \frac{-1}{\tau_{\mathrm{syn}}} g_{\mathrm{syn}} + \sum_{j} \sum_{i} w_{jk} \kappa (t - t_{\mathrm{sp},ji} - \Delta)$$

(1.11)

The synaptic current is given by

$$I_{\text{syn}}(t) = g_{\text{syn}}(t)(V_{\text{m}} - E_{\text{rev}}).$$

(1.12)

Here, the current is dependent on the membrane potential. The newly introduced parameter  $E_{\rm rev}$  is the reversal potential of the ion type that is associated with the synaptic ion channels. As above, in simulations, per-channel-type parameters for the time constants are typically used; for one inhibitory and one excitatory synapse type the nomenclature is  $E_{\rm rev,E}$ ,  $E_{\rm rev,I}$ ,  $\tau_{\rm syn,E}$ ,  $\tau_{\rm syn,I}$ .

#### 1.5 Synaptic dynamics

The models in section 1.4 are formulated assuming static synaptic weights which are constant throughout the course of the simulation. In computational neuroscience, and even more so in machine learning, an interesting field is the process of learning – the dynamic reconfiguration of the network to fulfill its intended functionality. Two plasticity mechanisms are singled out due to their relevance to the hardware platforms that are presented in the following chapters: The Tsodyks-Markram mechanism of short-term plasticity and spike-timing-dependent plasticity.

#### 1.5.1 Tsodyks-Markram mechanism

The PSP after a synaptic event is observed to depend on the history of spikes arriving at that synapse (Tsodyks and Markram, 1997). This is explained by the following kinetic model: Each synapse possesses resources which are separated in to the fractions of recovered (R), effective (E) and inactive (I) states. When a presynaptic event arrives at time  $t_{\rm AP}$ , a fraction ( $U_{\rm SE}$ , synaptic utilization) of remaining recovered resources moves from I to E. Using the notation from Tsodyks and Markram (1997):

$$\frac{\mathrm{d}R}{\mathrm{d}t} = \frac{I}{\tau_{\rm rec}} \tag{1.13}$$

$$\frac{\mathrm{d}E}{\mathrm{d}t} = \frac{-E}{\tau_{\rm in}} + U_{\rm SE} \cdot R \cdot \delta(t - t_{\rm sp}) \tag{1.14}$$

$$I = 1 - R - E \tag{1.15}$$

The net postsynaptic current is proportional to *E*.

This model is extended in Tsodyks et al. (cf. 1998, 2.1) to include synaptic facilitation by making  $U_{SE}$  a dynamic variable alongside I, R and E.

#### 1.5.2 Spike-timing-dependent plasticity

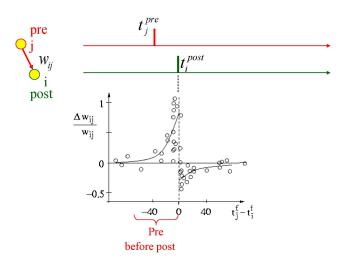

**Figure 1.3:** Used with permission from Sjöström and Gerstner (2010) (CC BYNC-SA 3.0, https://creativecommons.org/licenses/by-nc-sa/3.0/deed.en\_US), which is redrawn after Bi and Poo (1998). The unit on the time axis is ms.

One prominent model of long-term plasticity is based on the measurement of changes in synaptic efficacy in dependence of the relative timing of pre- and postsynaptic spikes (Markram et al., 1997; Bi and Poo, 1998). When neurons are stimulated by a series of presynaptic events followed or preceded by a series of induced postsynaptic events, a change of the synaptic efficacy is measured (fig. 1.3). The synaptic effect increases when the presynaptic event precedes the postsynaptic event in a given time window. Likewise, the effect decreases when the postsynaptic event is triggered earlier.

The effect is frequently modeled by an exponential dependency of the weight change on the timing of pre- and postsynaptic spikes, with variations on, e.g., whether the weight change is additive, multiplicative or whether the spike pairing is considered in an all-to-all or nearest-neighbor fashion (Morrison et al., 2007).

#### 1.6 Compartmental models

The neuron models described in section 1.2 and section 1.3 above reduce the spatial structure to a single point for which the membrane potential is evaluated; they are thus called *point neuron models*. Biological neurons display a complex morphology with branching dendritic trees and dendrite diameters which are far smaller than the distance between the soma and the distal end of the dendrite. For a single, linear section of dendrite, the cable equation (cf. Gerstner et al., 2014, sec. 3.2) is

an adequate, analytically tractable model. For investigations of complex branching topologies or nonlinear terms in the transmembrane conductance, compartmental models are a useful approach (Gerstner et al., 2014, sec. 3.2.3, 3.4). The voltage along the branching neuron is discretized into a finite number of elements, e.g. segments of dendrites. The membrane voltage  $V_{i\mu}$  at compartment  $\mu$  of neuron i is governed by the differential equation

$$C_{i\mu} \frac{d}{dt} V_{i\mu} = -g_{T,i\mu} \cdot V_{i\mu} + \sum_{\nu} g_{L,i\mu\nu} \cdot (V_{i\nu} - V_{i\mu}) + I_{i\mu}$$

(1.16)

with the membrane (transversal) conductance  $g_{T,i\mu}$ , the core (longitudinal) conductance  $g_{L,i\mu\nu}$  between compartments  $\mu$  and  $\nu$  and the compartment input current  $I_{i\mu}$  which can contain synaptic input, external stimulus or nonlinear membrane currents (Gerstner and Kistler, 2002, sec. 4.4.1).

#### 1.7 Accelerated physical models

An alternative approach to numerical modeling of neural circuits has been pioneered by Carver Mead (Mead, 1990). Rather than solving the differential equations of the time evolution of the membrane (eq. (1.1)), a physical, electrical model is constructed that solves the differential equation due to its intrinsic dynamics (Mahowald and Douglas, 1991; Farquhar and Hasler, 2005; Arthur and Boahen, 2007). The result of the time evolution of voltages in the physical model is called *emulation* to differentiate it from the numerical simulation. One possible approach is to create devices with time constants that match the time constants of biological neurons (Benjamin et al., 2014; Livi and Indiveri, 2009). Because small capacitances and resulting *RC* time constants are comparatively easy to realize in very-large-scale integration (VLSI) circuits, an alternative approach is promising that implements an accelerated dynamics; the equations eq. (1.1) are kept the same but the dynamics of the physical model is  $10^3$  to  $10^5$  faster than that of the biological system. This is the approach taken by Schemmel et al. (2008), the system that is described later in chapter 2.

Formally, the hardware dynamics  $V_{\rm hw}$  is scaled by an acceleration factor  $\alpha_t$  as compared to the original. In addition, the voltage level and scale is arbitrary, so it can be shifted by an offset  $\omega_v$  and scaled by a factor  $\alpha_V$ , so the relation between hardware voltage  $V_{\rm hw}$  and biological voltage V is:

$$V_{\text{hw}}(t) := V(\alpha_t \cdot t) \cdot \alpha_V + \omega_v \tag{1.17}$$

The hardware capacitance  $C_{\text{hw}}$  also differs from typical biological values C. From this we can derive the scaling rules for currents and conductances of the hardware

device:

$$\frac{\mathrm{d}V_{\mathrm{hw}}}{\mathrm{d}t}(t) = \alpha_V \alpha_t \frac{\mathrm{d}V}{\mathrm{d}t}(\alpha_t t) \tag{1.18}$$

$$I_{\text{hw}} = C_{\text{hw}} \frac{\text{d}V_{\text{hw}}}{\text{d}t} = \frac{C_{\text{hw}}}{C} \alpha_V \alpha_t \cdot I \tag{1.19}$$

$$g_{l,\text{hw}} = \frac{C_{\text{hw}}}{C} \alpha_t \cdot g_1 \tag{1.20}$$

where I and  $g_1$  are the original, biological quantities. The scaling factor for time constants is evidently  $\alpha_t$ . It is noteworthy that conductances do not scale with  $\alpha_V$  but only with  $\alpha_t$ .

#### 1.7.1 Hardware devices

Different hardware devices are used and analyzed within this thesis. The nomenclature that refers to these devices is outlined in the following:

The HICANN chip is a neuromorphic chip that was developed in the FACETS and BrainScaleS projects in a 180 nm complementary metal–oxide–semiconductor (CMOS) process (Millner et al., 2010). The chip has a targeted acceleration factor  $\alpha_t$  of  $10^4$ .

The *BrainScales system* is a large-scale system, consisting of 384 HICANN chips and the required supporting infrastructure (Schemmel et al., 2008). The properties of this system are investigated in chapter 2.

The successor of the BrainScaleS system, BrainScaleS 2, is based on the HICANN DLS chip, implemented in a 65 nm process (Friedmann et al., 2016; Hock et al., 2013; Schemmel et al., 2017). The targeted acceleration factor is 10<sup>3</sup>. This chip is referred to as HICANN DLS, or DLS in short, and the neuron architecture for its third prototype is examined in chapter 3.

#### 1.8 Sampling with leaky integrate-and-fire neurons

A method to transfer the machine learning concept of Boltzmann Machines to networks of spiking neural networks has been recently proposed by Petrovici et al. (2016). A Boltzmann Machine (Ackley et al., 1985) is a stochastic network of binary units. The probability distribution of the state vector of N units  $\mathbf{z} = \{z_1, z_2, ...\} \in \{0, 1\}^N$  is given by

$$p(\mathbf{z}) = \frac{1}{Z} \exp\left[\frac{1}{2}\mathbf{z}^T \mathbf{W} \mathbf{z} + \mathbf{z}^T \mathbf{b}\right] . \tag{1.21}$$

Here, Z is the partition function that normalizes the sum of the probability of all possible states to one. The probability distribution is parameterized by W, the connection matrix and b, the bias vector. This is exactly the probability distribution of a physical system with the states z in the canonical ensemble, the Boltzmann distribution

$$p(\mathbf{z}) = \frac{1}{Z} \exp\left[-\beta E(\mathbf{z})\right]$$

(1.22)

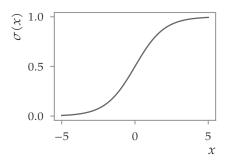

**Figure 1.4:**  $\sigma(x) = \frac{1}{1 + \exp(-x)}$

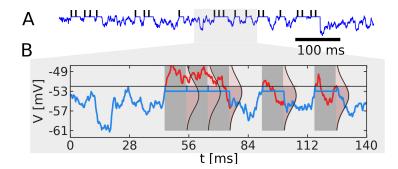

**Figure 1.5:** Dynamics of an LIF neuron model configured for LIF sampling (Petrovici, 2015). **A**: membrane potential and resulting spike train. **B**: Magnified excerpt of the voltage time course in A. The membrane voltage of the neuron (blue) follows the free membrane potential (red), except during spiking, where it is clamped to the reset potential. Taken from Petrovici (2015, Figure 6.31)

if one chooses  $\beta$  as  $\frac{1}{kT} = \beta = 1$  and defines the energy as the negative argument of the exponential function in eq. (1.21):

$$E(\mathbf{z}) = -\frac{1}{2}\mathbf{z}^T \mathbf{W} \mathbf{z} - \mathbf{z}^T \mathbf{b} \quad . \tag{1.23}$$

This relation to statistical physics gives the model its name.

An intuitive relation to neural networks can be established by calculating the conditional probability of unit *j* being on given the remaining state of the network

$$p(z_j = 1 \mid \mathbf{z}_{\setminus j}) = \frac{p(\mathbf{z}_{\setminus j}, z_j = 1)}{p(\mathbf{z}_{\setminus j}, z_j = 0) + p(\mathbf{z}_{\setminus j}, z_j = 1)} = \frac{\exp(u_j)}{1 + \exp(u_j)}$$

(1.24)

$$=\sigma(u_j) \tag{1.25}$$

defining the sigmoid function (fig. 1.4)

$$\sigma(x) := \frac{1}{1 + \exp(-x)} \quad . \tag{1.26}$$

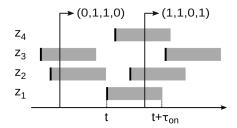

**Figure 1.6:** Interpretation of neuronal activity as sampling from a binary distribution. After a neuron fires it is considered active for a time  $\tau_{\rm on}$ , which corresponds to the refractory period in fig. 1.5. At any point in time, the state vector is the vector of active neurons (arrows). Taken from Petrovici (2015, Figure 6.25)

$u_i$  is given by

$$u_j = b_j + \sum_{k=1}^{N} w_{jk} z_k \quad . \tag{1.27}$$

Thus, the probability of unit j to be active is a nonlinear function  $\sigma$  of the linearly weighted activity of the rest of the network.

The numerical solution of eq. (1.21) becomes impractical for even moderate Ndue to the requirement of representing the probabilities for each of the  $2^N$  states. An alternative representation of the probability distribution is the sampling of states. A process is defined that produces samples from  $\{0,1\}^N$  with a probability that corresponds to eq. (1.21). Markov chain Monte Carlo (MCMC) methods can be used for this purpose. Here, a Markov chain is constructed which has the desired probability distribution as its stationary distribution. A common choice is Gibbs sampling (Geman and Geman, 1984) which updates individual variables  $z_i$  using the marginal distribution (eq. (1.24)) to update the full vector of random variables. This sampling method in conjunction with eq. (1.27) reminds of a stochastic neuron model with membrane potential  $u_i$  and activation probability  $\sigma(u_i)$ . The sampling representation has advantageous properties: Only those states that have a comparatively high probability, and thus are relevant during the evolution of the system, are represented. Further, the computation of marginal distributions is elementary, as one can omit the unneeded variables during the collection of samples. Clamping parts of the system allows to calculate the conditional distribution of the remaining system.

An approach to map the system to more realistic stochastic neuron models incorporating long refractory times and relative refractoriness is described in Buesing et al. (2011) and is not discussed here in detail. It is one of the foundations for Petrovici et al. (2016) to implement Boltzmann Machines using deterministic LIF neurons. Here, input from background Poisson processes provides stochasticity to each neuron. Figure 1.5 shows the behavior of an LIF neuron in the LIF sampling regime. The neuron is stimulated by Poisson input such that the total conductance exceeds the leak conductance and thus lowers the effective time constant. This can

be understood by rewriting eq. (1.1) with conductance-based synapses eq. (1.11) as

$$C_{\rm m} \frac{\rm d}{\rm d}t V_{\rm m} = -g_{\rm l}(V_{\rm m} - V_{\rm leak})$$

$$-g_{\rm syn,E}(t)(V_{\rm m} - E_{\rm rev,E})$$

$$-g_{\rm syn,I}(t)(V_{\rm m} - E_{\rm rev,I})$$

$$= \underbrace{\left(g_{\rm l} \cdot V_{\rm leak} + g_{\rm syn,E}(t) \cdot E_{\rm rev,E} + g_{\rm syn,I}(t) \cdot E_{\rm rev,I}\right)}_{g_{\rm tot}(t) \cdot V_{\rm eff}(t)}$$

$$-\left(g_{\rm l} + g_{\rm syn,E}(t) + g_{\rm syn,I}(t)\right) \cdot V_{\rm m}$$

$$(1.29)$$

$$-\underbrace{\left(g_1 + g_{\text{syn,E}}(t) + g_{\text{syn,I}}(t)\right)}_{g_{\text{tot}}(t)} \cdot V_{\text{m}} \tag{1.29}$$

$$= g_{\text{tot}}(t) \cdot V_{\text{eff}}(t) - g_{\text{tot}}(t)V_{\text{m}}$$

(1.30)

defining

$$g_{\text{tot}}(t) := g_1 + g_{\text{svn,E}}(t) + g_{\text{svn,I}}(t)$$

(1.31)

$$V_{\text{eff}}(t) := \frac{g_{\text{l}} \cdot V_{\text{leak}} + g_{\text{syn,E}}(t) \cdot E_{\text{rev,E}} + g_{\text{syn,I}}(t) \cdot E_{\text{rev,I}}}{g_{\text{tot}}(t)}$$

(1.32)

$$\tau_{\rm eff}(t) := \frac{C_{\rm m}}{g_{\rm tot}(t)} \tag{1.33}$$

one obtains the time evolution of the membrane potential

$$\tau_{\rm eff}(t)\frac{\rm d}{{\rm d}t}V_{\rm m} = V_{\rm eff}(t) - V_{\rm m} \quad . \tag{1.34}$$

In the case of current-based synapses, the effective membrane time constant does not change with the input, and the equilibrium potential is

$$V_{\text{eff,curr}}(t) = V_{\text{leak}} + \frac{I_{\text{syn}}}{g_1}(t)$$

(1.35)

and the time evolution of the system is given by

$$\tau_{\rm m} \frac{\mathrm{d}}{\mathrm{d}t} V_{\rm m} = V_{\rm leak} + \frac{I_{\rm syn}}{g_{\rm l}}(t) - V_{\rm m} \quad . \tag{1.36}$$

As the Poisson input rate increases, the equilibrium distribution of  $V_{\rm eff,curr}$  (or  $g_{\rm syn}$  in the conductance based case) converges to a normal distribution. This can be seen from the central limit theorem – for a proof see, e.g., (Petrovici et al., 2016, 4.3.2) – or by approximating the input current as Ornstein-Uhlenbeck process (Ricciardi and Sacerdote, 1979). The step that joins the sampling representation of eq. (1.21) and the activity of LIF networks is shown in fig. 1.6: Each neuron is defined to be active during its refractory period  $\tau_{\rm ref}$  and the set of the activity vectors from the time evolution of the network constitutes a sampling representation of the underlying probability distribution. The spike-based interaction between different neurons

raises (or lowers) the total input current shifting the membrane potential distribution in analogy to the effect of active variables in eq. (1.27) on any given variable j.

In fig. 1.5, further features of the setup are seen. The free membrane potential (red curve) is faithfully followed by  $V_{\rm m}$  due to a low effective time constant  $\tau_{\rm eff}$ . The refractory period of the neuron is close to the synaptic time constant. This choice facilitates the matching of the internal on-state of a neuron, given by the refractory period  $\tau_{\rm ref}$ , and the on-state seen by other neurons in the network, given by the exponential decay of the post-synaptic current with the time constant  $\tau_{\rm syn}$ . For a more detailed investigation of, e.g., different PSP kernels or a variation of time constants we refer to (Petrovici et al., 2016, 6.5).

## **Chapter 2**

# Compensation of network-level effects on a neuromorphic platform

The BrainScaleS system is a large-scale, accelerated neuromorphic device that was created to investigate the dynamical and computational properties of networks of spiking neurons. At its core lies a full-custom VLSI implementation of abstract neuron models and a communication infrastructure that connects these neurons. The design of the system results from a trade-off between two goals: first, providing a versatile and configurable substrate for the investigation of spiking neural networks, and second, to establish an implementation which is fast and efficient in energy and cost. The implemented neuron models and the connectivity is developed to accommodate biological parameter ranges (Millner et al. (2010); Fieres et al. (2008)). On the other hand, the implementation must adhere to strict limits concerning die area of the involved components and their power consumption, to pose a viable alternative to conventional computing architectures with regard to the simulation of spiking neural networks. The outcome of the trade-off manifests in a large speed-up in comparison to biological real time of approximately 10<sup>4</sup> which comes at the cost of certain limitations: Neuron and synapse parameters have finite precision. For digital parameters this is caused by discretization of values. For analog parameters, fixedpattern variability occurs due to device mismatch during chip manufacturing. The communication infrastructure that transports spike events also underlies constrains in terms of the number of possible realizable connections and in the bandwidth that is available for spike data.

A large effort is put into making the system accessible for non-hardware-experts: The top-level software interface for users is *PyNN* (Davison et al. (2008)), an application programming interface (API) that allows defining networks of spiking neurons and execute that definition on several simulation back ends, the BrainScaleS system being one of them. The back end includes algorithms to map the abstract network description into a configuration of the hardware device (Brüderle et al. (2011)). Additional software layers handle the communication with the system to actually perform the

configuration, transport input data to the device and return the emulation result to the user (see Brüderle (2009); Jeltsch (2014); Müller (2014)). The translation between biological and hardware time and voltage domains (section 1.7) is also handled at this point. Issues of variability are addressed by applying a *calibration*, a collection of methods to measure device properties on the level of individual sub-circuits and translate the desired neuron properties entered by the user to a corresponding hardware configuration. Typically, even after calibration, some variability remains which must be taken into account by the user of the system (see, e.g., Brüderle et al. (2011); Schwartz (2013); Koke (2017)). In the end, the user of the neuromorphic device has to deal with distortions due to limited communication resources, limited bandwidth and parameter precision in the design of their network.

During the production and commissioning phase of the BrainScaleS system, the impact of these limitations was analyzed in Petrovici et al. (2014) using a bottom-up approach. Three network models, which are derived from previous studies, are used to investigate the effect of idealized distortion mechanisms on their network dynamics. Compensation strategies that restore the original functionality of the network are proposed and tested in simulation. As a final step, all compensation mechanisms are verified using the Executable System Specification (ESS), a simulated hardware back end. Because the ESS faithfully represents the behavior of digital components of the hardware device and is interfaced using the same software as the hardware device, this serves as test of the combined stack of configuration software, mapping algorithms and hardware constraints.

#### Contribution

In the following, the analysis of two of the networks is presented which was carried out in large part by the author of this thesis. The analysis of the random network with self-sustained activity was performed in equal parts with Bernhard Vogginger and Lyle Muller; all ESS simulations were performed by Bernhard Vogginger.

#### 2.1 Wafer-scale neuromorphic hardware

#### 2.1.1 Hardware implementation

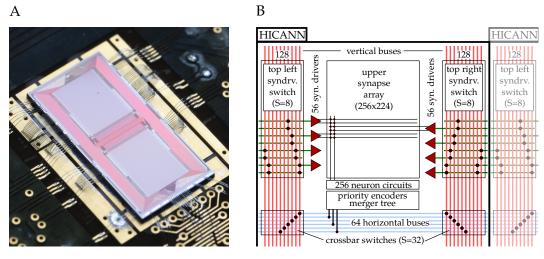

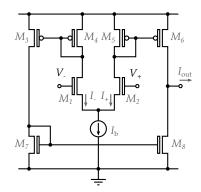

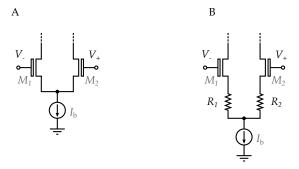

The BrainScaleS system is the reference neuromorphic system that is being used for the study in this chapter. It is an accelerated, continuous-time, mixed-signal neuromorphic system. At the core of the system lies the HICANN chip (fig. 2.1 A). It contains 512 neuron circuits which implement the AdEx neuron model (eq. (1.4)) as analog electronic circuits (Millner et al. (2010)). The intrinsic *RC* time constants of these circuits are approximately 10<sup>4</sup> smaller than those of biological neurons. Each neuron circuit receives 24 adjustable parameters as analog currents and voltages, which are used to control the neuron's properties. The parameters are provided by an array of floating gate cells (Srowig et al., 2007; Ehrlich et al., 2007; Millner, 2012).

**Figure 2.1:** A: Photograph of a bonded HICANN chip die (taken by Matthias Hock). **B**: Schematic representation of components and connectivity of the HI-CANN building block, and its interconnection to other HICANNs within a wafer module. (The upper half of the chip is represented.) Most of the chip area is occupied by the synapse array. Each synapse column is connected to one of 256 neuron circuits, from which up to 64 can be interconnected to form larger neurons with up to 14336 input synapses. The horizontal and vertical buses transport spike events in the form of 6-bit addresses, which means they can be used to deliver spikes of up to 64 different sources. Sparse, statically configurable switches connect horizontal and vertical bus lines (called crossbar switches) and vertical bus lines with the input of the synapse drivers. The synapse driver and the synapses filter incoming events according to their 6-bit address, so that each synapse forwards events from exactly one source address. The layer 1 (L1) buses of adjacent HICANNs are interconnected with repeaters, which enables the wafer-wide signal transport by L1. The figure on the right and corresponding caption are modified with permission from (Petrovici et al., 2014, Figure 3).

A large part of the chip area is occupied by communication infrastructure which transports spikes emitted by neuron circuits to other neurons within the system (fig. 2.1 B). Each neuron circuit is connected to a column of 224 synapses in the synapse array which provide the input from the presynaptic partners of the neuron and store the corresponding synaptic weight. Adjacent neuron circuits (neighboring on one half of the chip or opposing on the upper and lower half) can be interconnected to form a larger logical neuron to increase the number of synapses per neuron. When a neuron fires, it emits a signal with a 6-bit address which is merged with the output of other neurons onto a horizontal L1 bus. An L1 bus can be connected to a crossing bus using statically configurable sparse switches (denoted by black dots in fig. 2.1 B). A vertical L1 bus can be connected to synapse drivers, which pass the events into the synapse circuits. The drivers and synapses filter the incoming address packets so that

Figure 2.2: Wafer-scale integration and off-chip communication. Left: The L1 connections span over the whole wafer. For this, chips on different reticles, the largest unit of the photolithographic process, are electrically connected in a post-processing step. Right: Off-wafer connectivity by dedicated DNC chips (Ehrlich et al. (2007); Scholze et al. (2010)) and FPGAs to host computers controlling the experiment. Used with permission from (Petrovici et al., 2014, Figure 2)

in general, each synapse transports events from one presynaptic to one postsynaptic partner. The scalability of the architecture stems from wafer-scale integration: After production on a silicon wafer, the HICANN chips are not cut apart and the wafer is left intact (fig. 2.2). The HICANN chips are connected by additional wiring using a post-processing step, making it possible to transmit L1 packets between neighboring chips (Schemmel et al. (2008)). Thus, the static switches described above can be used to configure outgoing trees of connections that span the whole wafer. The realizable internal and external connectivity poses complex constraints due to the limited number of buses per chip, the number of synapse drivers and synapses, and the sparseness of switches which connect vertical bus lanes to horizontal buses and synapse drivers.

#### 2.1.2 Supporting software

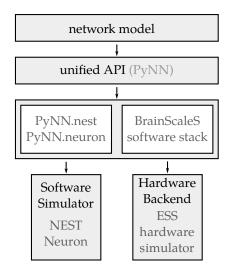

The software framework for the hardware system handles these constraints by automating the mapping of network architectures to the hardware substrate. It is interfaced using the network description API, PyNN (fig. 2.3), which also has several software-based simulator back ends. A general description of a spiking network

**Figure 2.3:** Software used for the analysis. The software simulators NEST (Gewaltig and Diesmann (2007)) and NEURON (Hines and Carnevale (2003)) and the BrainScaleS system simulator ESS are both interfaced using the *PyNN* API (Davison et al. (2008)).

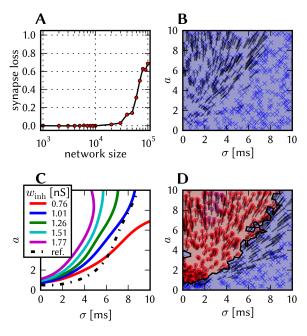

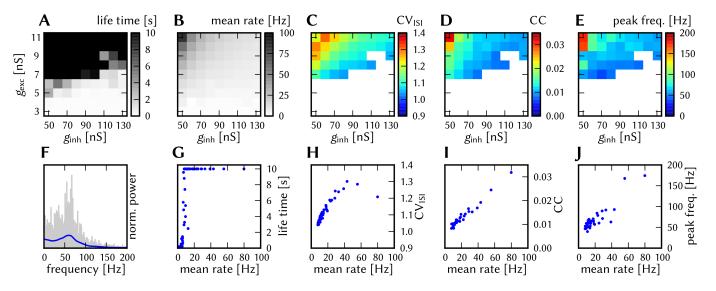

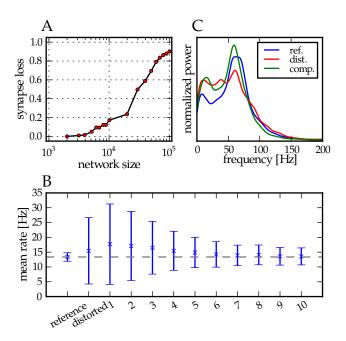

is mapped to the hardware by first allocating neuron circuits for each neuron in the abstract network (*placement* step). Then, connections between the neurons are realized in the *routing* step. It can occur that some synapses can not be realized due to limited resources. These synapses effectively disappear from the network; this effect is thus called *synapse loss* from here on. For complex networks, the loss does not start abruptly with an increase in the number of neurons, but a small percentage of synapses can not be realized even for comparatively small networks, the proportion rising slowly with network size (see fig. 2.17 A), so it is not feasible to treat this effect as an error. Within the following study, synapse loss is sometimes enforced by using only a part of a wafer to test the presented compensation strategies with a network of a given size.

The ESS (Brüderle et al., 2011; Ehrlich et al., 2007; Vogginger, 2010) is an essential part of the investigation as the part of the software that simulates the hardware system. It provides a detailed, executable model of the spike transmission in individual hardware modules for on- and off-wafer communication. It further faithfully maps the configuration space of the hardware such as the interconnection topology, parameter discretization and sharing of parameters. The neuron circuits are represented numerical models of the ideal AdEx equation. In the simulations described below, parameter variations are artificially imposed for synaptic weights but not for neuron parameters.

#### 2.2 Structure of the analysis

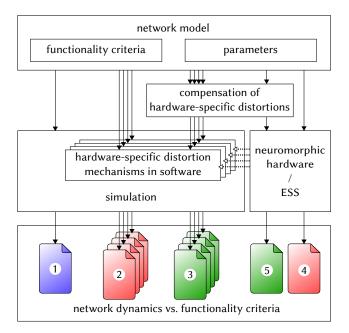

Figure 2.4 shows an outline of the analysis workflow. The investigated network models are selected and for each network, a set of functionality criteria is defined that

**Figure 2.4:** Outline of the distortion analysis workflow. A detailed description is given in section 2.2. Used with permission from (Petrovici et al., 2014)

capture essential characteristics of those models (1). The most important distortion mechanisms for emulating networks are identified and modeled in an abstract way. The effect of each distortion mechanism on the functionality criteria is investigated in simulation (fig. 2.4 2) using a software simulator back end (fig. 2.3). Compensation methods are developed and verified in simulation for the distortion mechanisms individually (3). In a last step, a simulation with all modeled distortions using the ESS is conducted, once without and once with all compensation mechanisms.

The distortion mechanisms that typically occur on mixed-signal neuromorphic devices are:

- 1. Fixed neuron and synapse models, i.e., only LIF and AdEx neurons with conductance-based synapses are available on the device

- 2. Limited parameter ranges

- 3. Limited number of components, such as neurons, synapses or spike routing resources.

- 4. Non-configurable transmission delays

- 5. Bandwidth constraints within the wafer and for external spike stimulus and readout.

The following three effects are isolated as being the most generalizable, i.e., which are expected to be present in most neuromorphic devices with analog components, and are expected to significantly affect most network models:

- 1. Synapse loss is modeled by randomly deleting a fraction of synapses in a network. The magnitude is denoted as percentage, which corresponds to the probability that a synapse is lost ( $p_{loss}$ ).

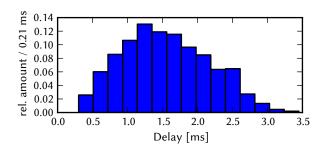

- 2. Non-configurable delays, implemented by enforcing a constant delay of 1.5 ms in the biological time domain, the mean expected value of delay on the wafer system.

- 3. Synaptic *weight noise*, which models a fixed-pattern variation of the strength of synaptic weights due to transistor mismatch and weight discretization. The value is implemented as Gaussian random variable with the mean of the original synaptic weight and standard deviation proportional to the original weight. (Negative samples can occur and are clipped to zero.)

For ESS simulations, the synapse loss and delay constraints result implicitly from the realistic model of component behavior and routing constraints, while the weight noise is implemented as described in the list above.

#### 2.3 Simulation results

In this section we describe two of the network models that were investigated in Petrovici et al. (2014). First we outline the functionality criteria which are derived from the dynamics of the undistorted network. Then, the effects of the distortion mechanisms and possible compensation methods are analyzed.

#### 2.3.1 Synfire chain with feed-forward inhibition

#### **Network description**

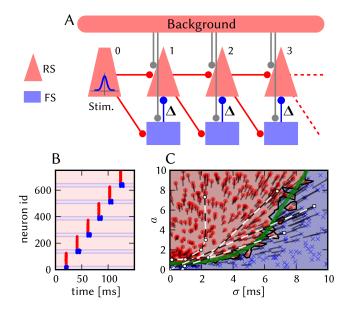

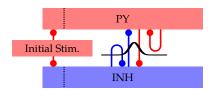

The first model that is being investigated is a feed-forward chain based on the study presented in Kremkow et al. (2010). One of the core points of that study is the effect of feedforward inhibition on signal propagation through consecutive groups of neurons. Disynaptic inhibition, where excitatory connections trigger inhibitory neurons, is a connection scheme that has been observed in cortical structures (Silberberg and Markram (2007)), and is the mechanism of feedforward inhibition in the network model. On a functional level, it has been shown experimentally that stimulus in cat visual cortex evokes excitation shortly followed by inhibition, recorded hundreds of micrometers from the stimulus site Hirsch and Gilbert (1991).

Figure 2.5 A shows the structure of the network and the simulation setup. The network consists of consecutive groups, each group containing 100 regular spiking (RS) and 25 fast spiking inhibitory (FS) cells. All cells are modeled using LIF neurons with identical parameterization (table A.1). The disynaptic, feedforward inhibition scheme is implemented as follows: Neurons from the excitatory population within each group project onto both populations of the consecutive group, while the inhibitory population projects within the group only. The connectivity is dense, with 60 connections from the RS and 25 from the FS population to each RS population

**Figure 2.5: A**: Schematic representation of excitatory (regular spiking (RS)) and inhibitory (fast spiking inhibitory (FS)) populations within the synfire chain network model. **B**: Example propagation of a pulse packed through individual groups of the synfire chain. **C**: Evolution of the strength and width of a pulse packet as it propagates through the chain, depending on the initial parameters. The marker is placed corresponding to the properties of the initial stimulus pulse,  $(\sigma_0, a_0)$ . The evolution of the pulse packet properties is shown exemplarily for four stimulus parameters as black-and-white lines. Each marker is colored according to the activation of the last group in the simulation, red for  $a_6 \ge 1$ , blue for  $a_6 = 0$  and linearly interpolated between the two colors for  $0 < a_6 < 1$ . To improve visibility, the background is colored using the same color as the nearest point. The green line represents a fit to the boundary between the region of stable and unstable propagation. Used with permission from (Petrovici et al., 2014, Figure 13)

(table A.2). The local delay  $\Delta$  from the FS to the RS population is an important quantity that affects the functionality of the network (fig. 2.8); it is set to 4 ms in the default case. The inter-group delay is not relevant for the functionality, because there are no feedback connections. This delay only affects the time shift of the neuron's responses, and is set to 20 ms for visualization purposes, as in Kremkow et al. (2010). The background stimulus is implemented as Gaussian background noise in the original model in Kremkow et al. (2010), and is replaced by spiking background that is adjusted to keep the original mean and variance of the membrane potential distribution. This was achieved by an input firing rate of 2 kHz with a synaptic weight of 1 nS.

The input to the network is provided by a population of 100 spike sources, which are connected identically to an RS population within the chain. This input population emits a test pulse that is parameterized as follows: Each neuron within the

population emits  $a_0$  spikes. Each spike time is drawn from a Gaussian distribution with a common mean and standard deviation  $\sigma_0$ . The functionality criteria for this network are based on the propagation properties of this pulse packet through the chain (fig. 2.5 B): The mean number of spikes in group i is denoted  $a_i$  and the standard deviation of the spike times  $\sigma_i$ . In the default configuration, the input converges to a=1 and  $\sigma$  close to zero, i.e., each neuron in the chain spikes exactly once and the firing is nearly synchronous. Due to this behavior, the network is referred to as synfire chain from here on. The dynamics of the convergence to this state is shown in fig. 2.5 C. The initial stimulus parameters  $a_0$ ,  $\sigma_0$  are drawn from a range of [0, 10] resp. [0 ms, 10 ms]. Depending on the starting position in the  $(\sigma, a)$ space, the activity parameters either converge to the stable point as the pulse is passed through the network, or the propagation stops. Exemplary trajectories of the activation properties in successive groups are shown as black-and-white lines. In fig. 2.5 C, points representing initial parameters that lead to an activation of the last group  $(a_6)$  are colored red, otherwise blue. The region in the stimulus space that leads to stable propagation is sharply separated. The approximate separation line between the two regions, called *separatrix* from here on, is shown in green in fig. 2.5 C. The presence of stable propagation and the location of the separatrix are defined as functional criteria for this network.

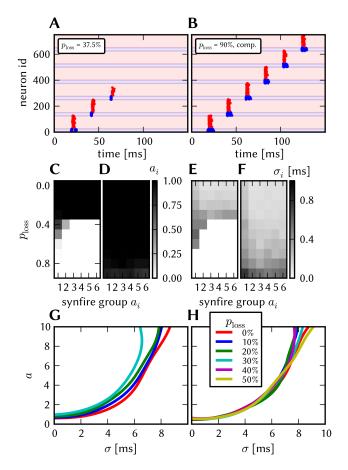

#### Synapse loss

The effect of synapse loss on the behavior of the network is shown in fig. 2.6. Homogeneous deletion of synapses is applied to all internal connections as well as the synchronized stimulus, but not to the background. The propagation for a synchronous pulse with a=1 fails between 40 % and 50 % synapse loss (panels A, C, E). Compensating this by scaling all weights with the ideal factor  $\frac{1}{1-p_{\rm loss}}$  restores propagation (panels B, D), while increasing the pulse width for high values of synapse loss (panel F). The separatrix is affected in a minor way in the distorted case (panel G) until the region of stable propagation disappears altogether. The location of the separatrix at  $\sigma=0$  moves to higher a values, until it reaches the fixed point at a=1 and the stable region disappears (not shown). In the compensated case, the separatrix location is not significantly affected by the distortion (panel H).

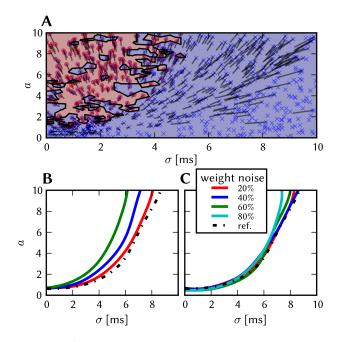

#### Weight noise

The effect of weight noise is shown in fig. 2.7. Panel A shows a representative stimulus state space for a high value of noise of 80 %. The primary cause of the distortion is the variation of the background stimulus weight. One solution to remedy the effect to keep the distribution of membrane potential values at a given point in time at its original, undistorted value. When the input spike volley arrives, the membrane voltages of the individual neurons are spread out, because they each receive different random background stimulus and because, due to weight noise, the magnitude of the background input varies. As the variation that is caused by synaptic weight heterogeneity increases, the variation caused by time-dependent

**Figure 2.6: A**: Pulse propagation in the synfire network with 37.5 % synapse loss, without compensation. **B**: Pulse propagation in the network with 90 % synapse loss and active compensation by increased synaptic weights. **C**: Activation  $a_i$  in each group i for different values of synapse loss. **D**: Activation  $a_i$  in each group i for different values of synapse loss and with active compensation. **E**: Pulse width  $\sigma_i$  in each group i for different values of synapse loss. **F**: Pulse width  $\sigma_i$  in each group i for different values of synapse loss and width active compensation. **G**: Approximate separatrix locations for different values of synapse loss. For 40 % and 50 % synapse loss no stable region exists, so no line is present. **H**: Approximate separatrix locations for different values of synapse loss with active compensation. Used with permission from (Petrovici et al., 2014, Figure 14)

**Figure 2.7: A**: State space for 80 % weight noise. **B**: Approximate separatrix locations for smaller values of weight noise. **C**: Approximate separatrix locations for the compensated case. The separatrix from the reference simulation is shown as a dashed line. A spike filter with parameters  $T = 10 \,\text{ms}$ ,  $N = 25 \,\text{is}$  applied for these figures (cf., section A.1.2). A comparison with and without filter is shown in fig. A.1. Used with permission from (Petrovici et al., 2014, Figure 15)

Poissonian background stimulus is reduced. This can only work due to the short time during which the propagating pulse acts, so that the time-dependent variation of the background stimulus does play a significant role. The parameter  $V_{\rm leak}$  is increased and the background synaptic weight is lowered to achieve this. The approximation of current-based neurons (linear addition of PSP kernels) is used to calculate the required factor. Then, the membrane potential of a neuron stimulated by background spikes can be approximated as

$$V_{\rm m} \approx w \cdot \sum_{j \in \text{backg. spikes}} \kappa(t - t_j) + V_{\text{leak}}$$

=  $w \cdot K(t) + V_{\text{leak}}$  , (2.1)

where  $\kappa$  is the post-synaptic kernel and K(t) the sum of the kernels. The average over the time and weight distribution is then

$$\langle V_{\rm m} \rangle \approx \langle w \rangle \cdot \langle K(t) \rangle + V_{\rm leak}$$

The variance of w is given by  $Var[w] = w_0^2 s^2$ , where s denotes the relative weight noise and  $w_0$  the original, undistorted weight. The variance of  $V_m$  then follows from

eq. (2.1)

$$\operatorname{Var}\left[V_{\mathrm{m}}\right] \approx \langle w \rangle^{2} \operatorname{Var}\left[K(t)\right] + \operatorname{Var}\left[w\right] \left(\langle K(t) \rangle^{2} + \operatorname{Var}\left[K(t)\right]\right) \tag{2.2}$$

$$= w_0^2 \left\{ \text{Var} \left[ K(t) \right] + s^2 \left( \langle K(t) \rangle^2 + \text{Var} \left[ K(t) \right] \right) \right\}$$

(2.3)

With increasing  $s^2$ ,  $w_0$  must decrease to keep Var  $[V_{\rm m}]$  constant. This changes  $\langle V_{\rm m} \rangle$  which is compensated by modifying  $V_{\rm leak}$  accordingly. Panels B and C of fig. 2.7 show the location of the separatrix in the distorted and compensated cases, demonstrating the viability of the method.

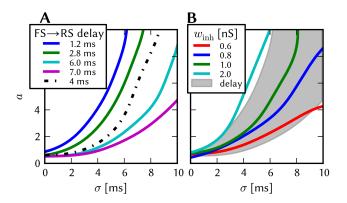

#### Non-configurable axonal delays

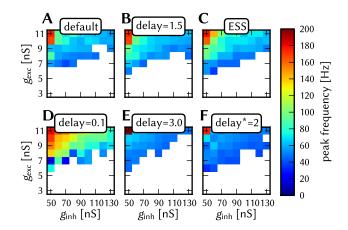

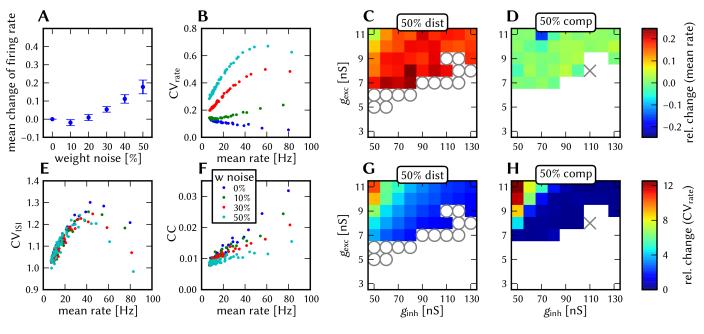

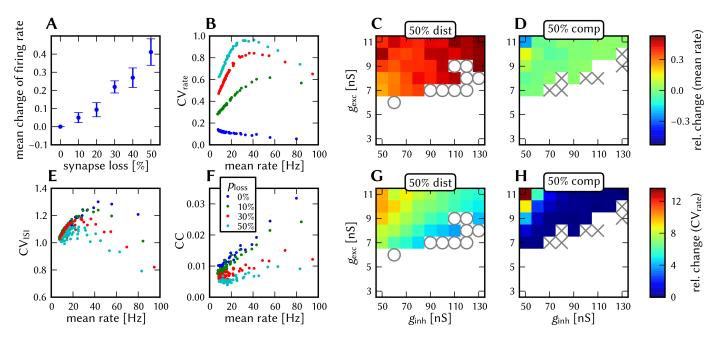

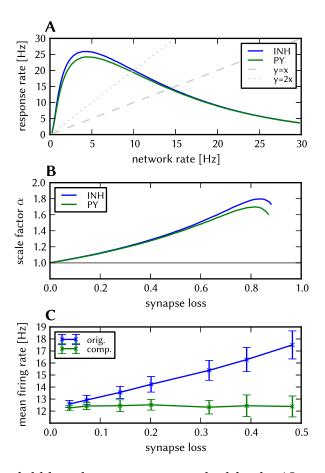

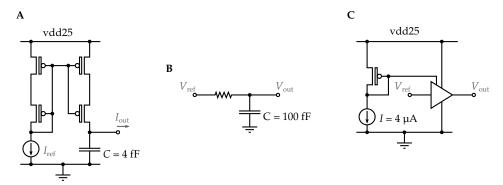

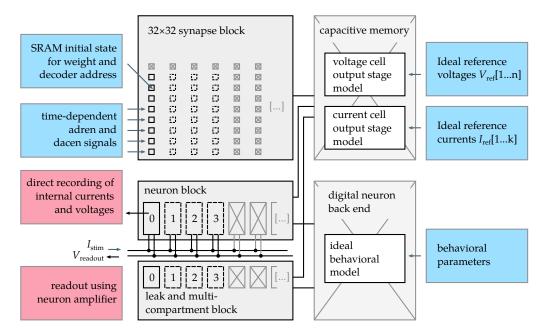

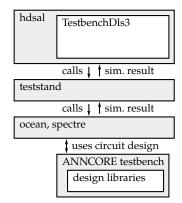

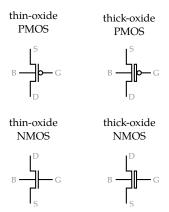

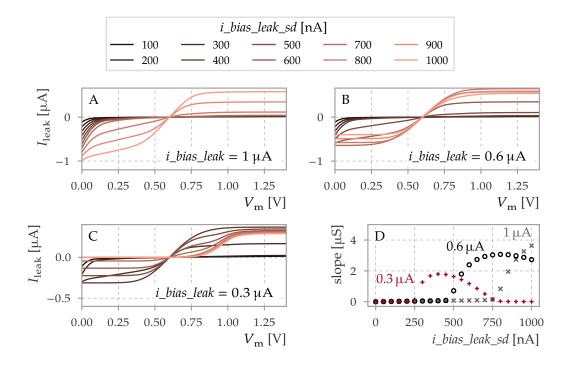

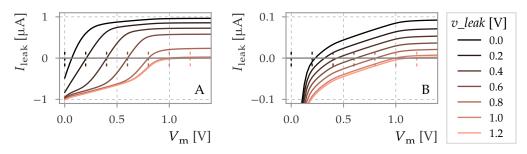

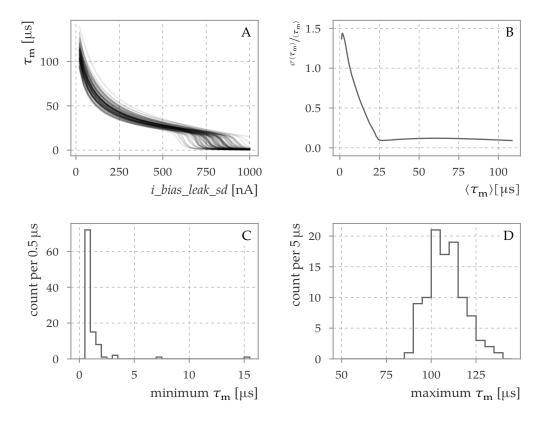

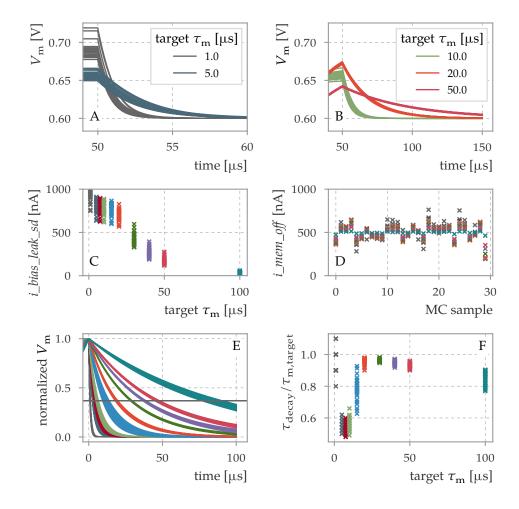

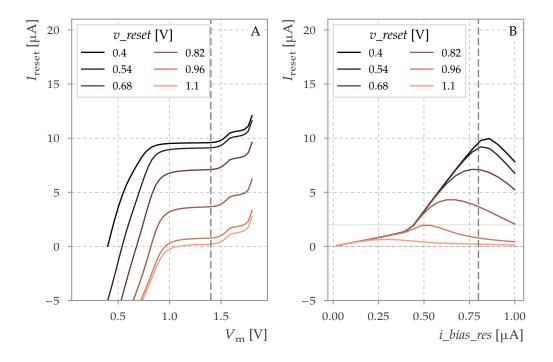

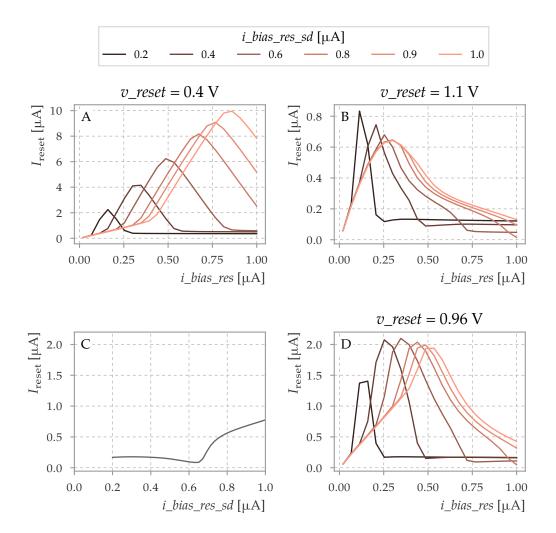

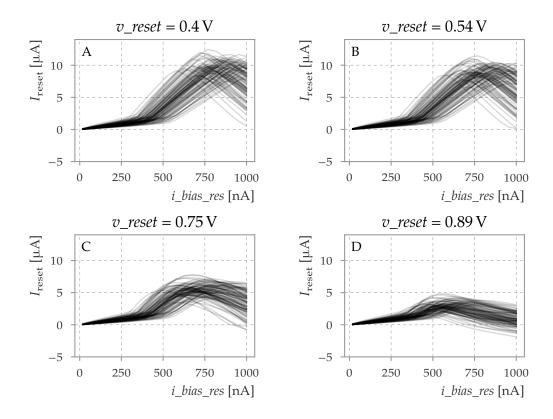

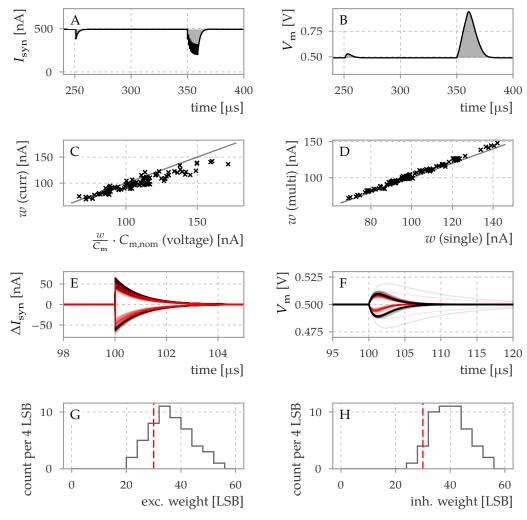

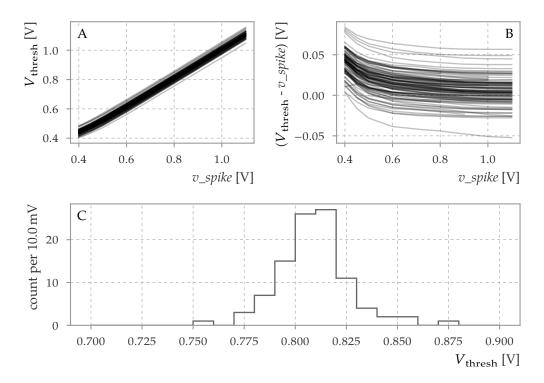

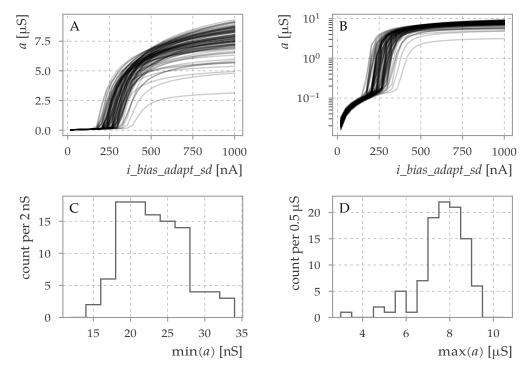

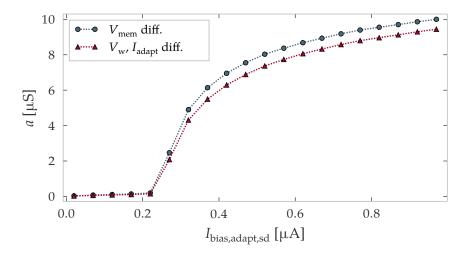

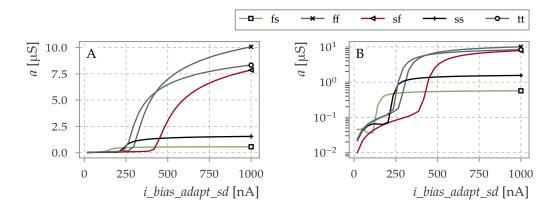

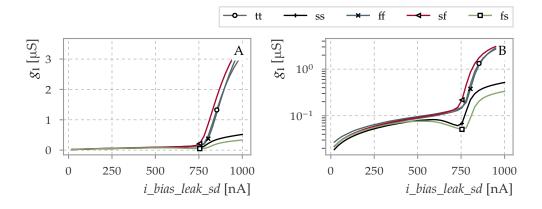

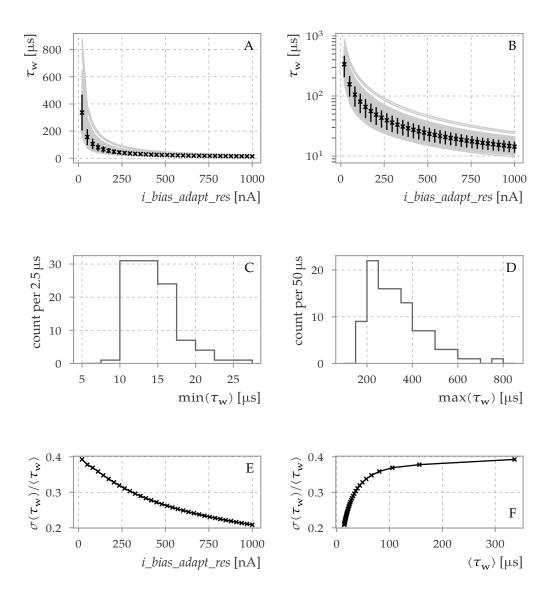

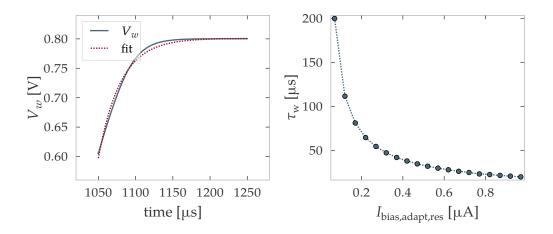

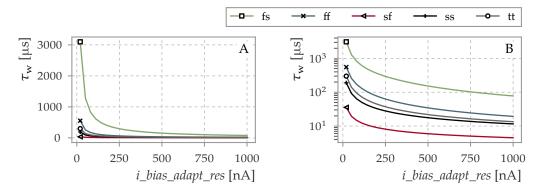

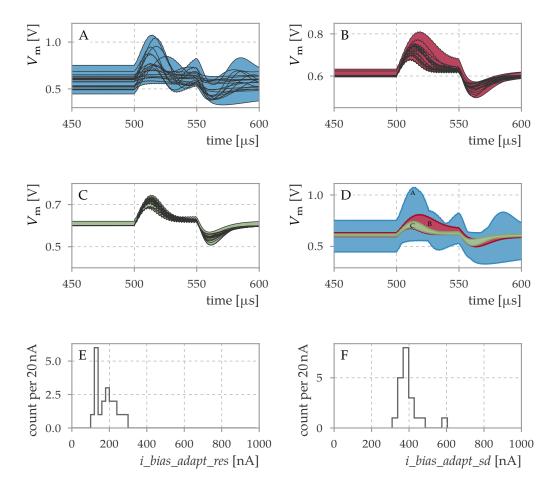

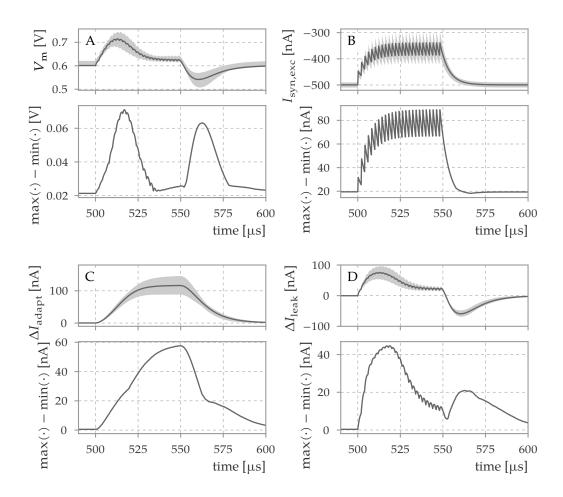

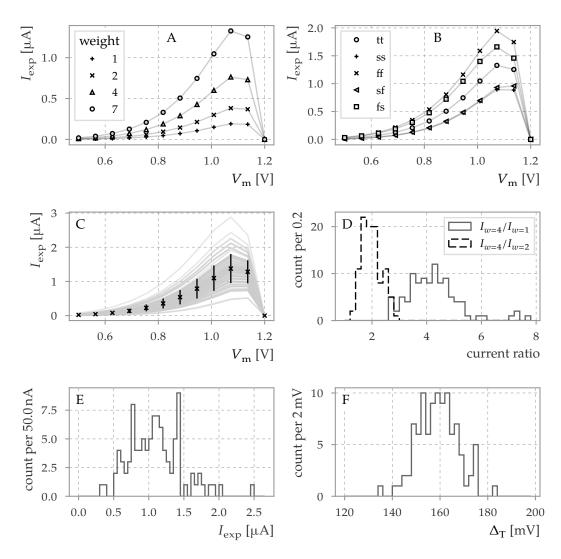

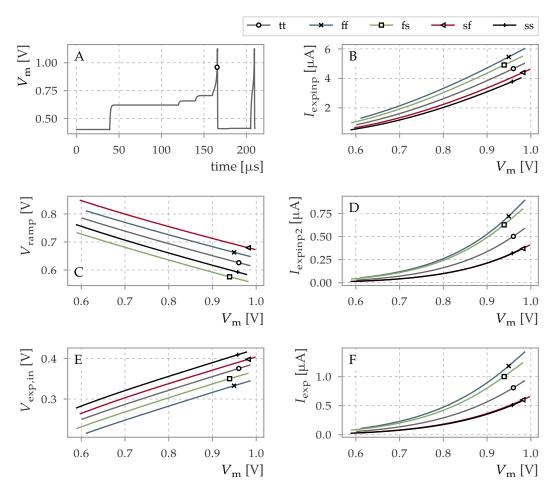

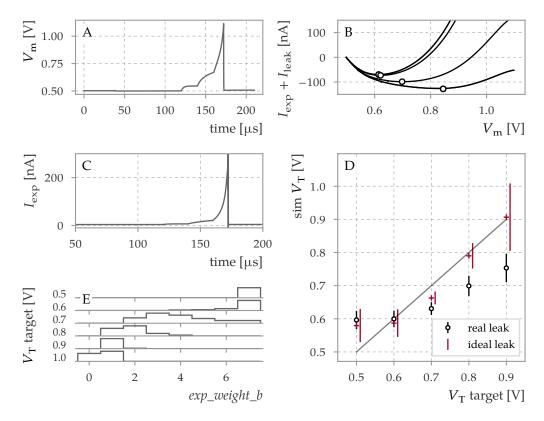

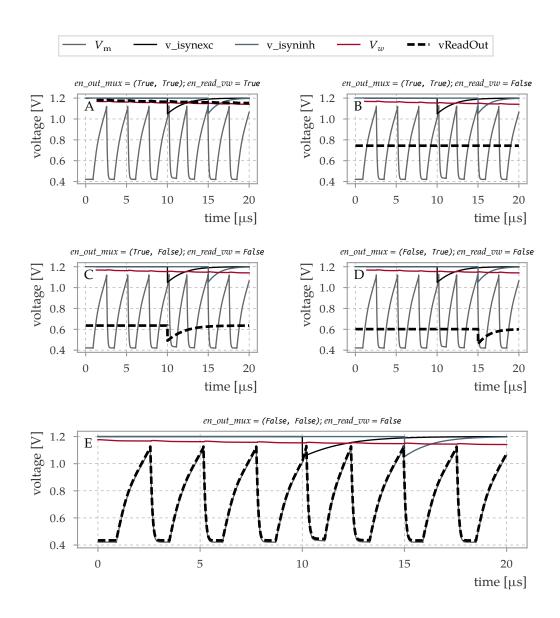

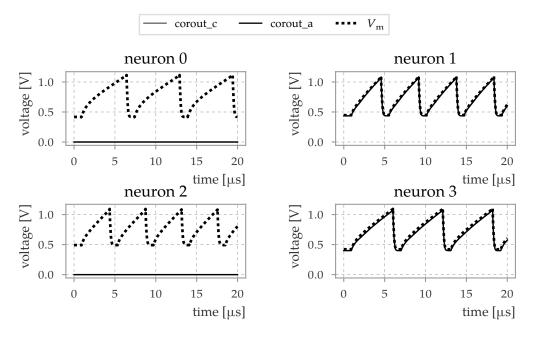

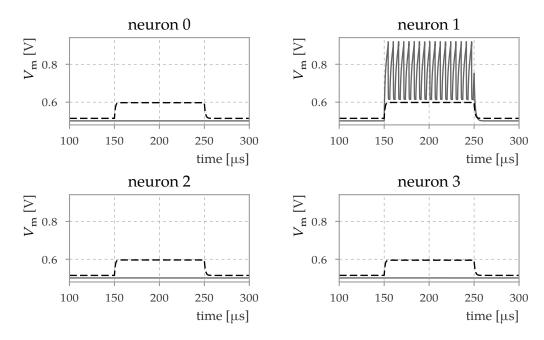

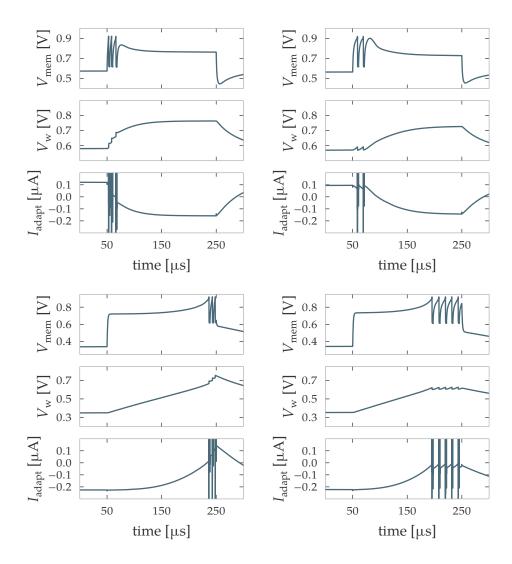

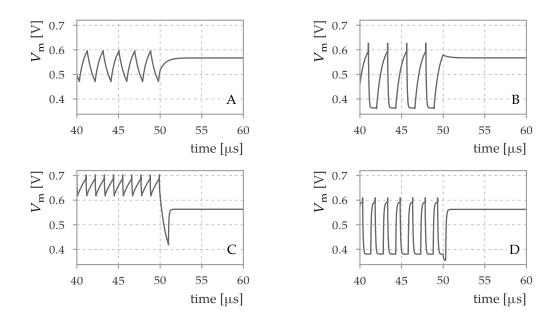

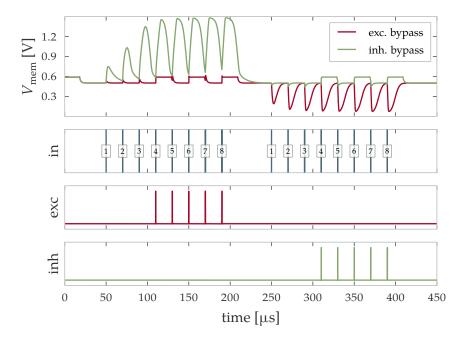

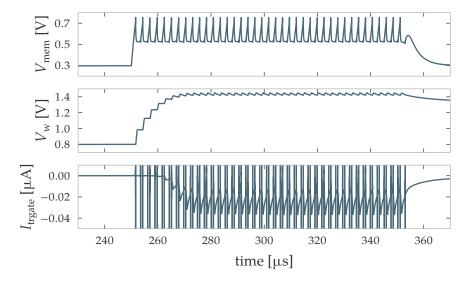

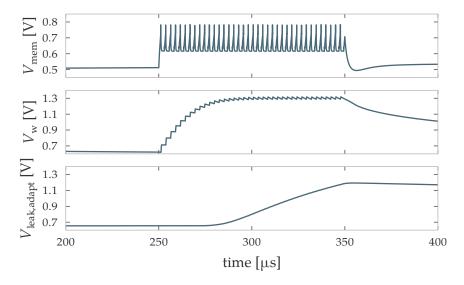

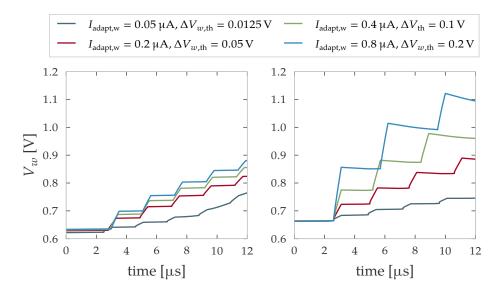

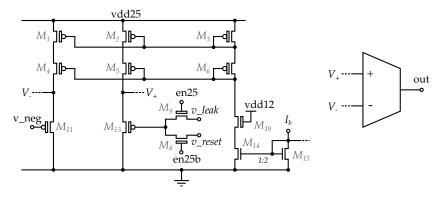

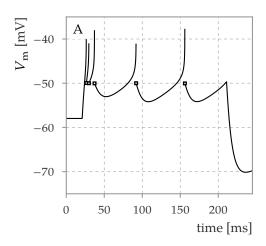

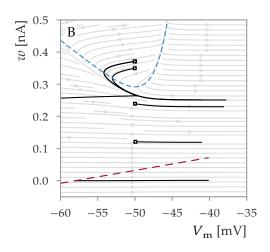

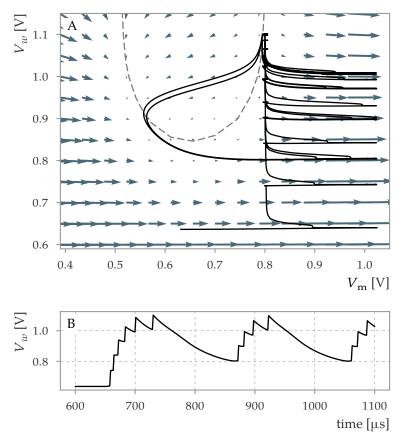

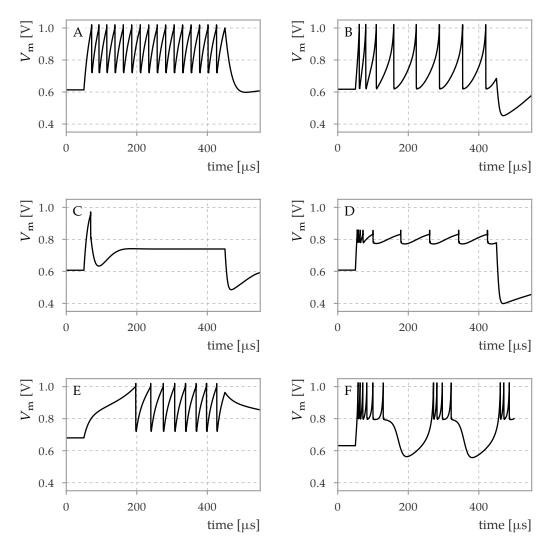

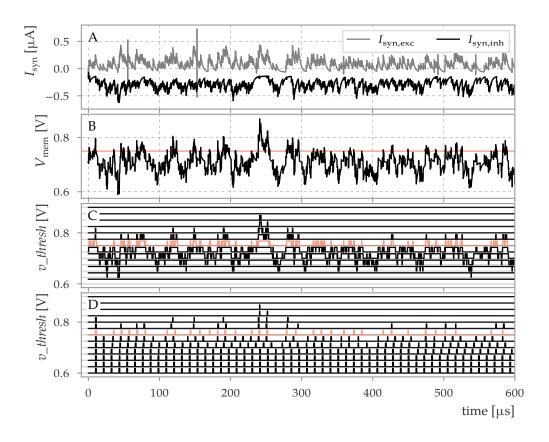

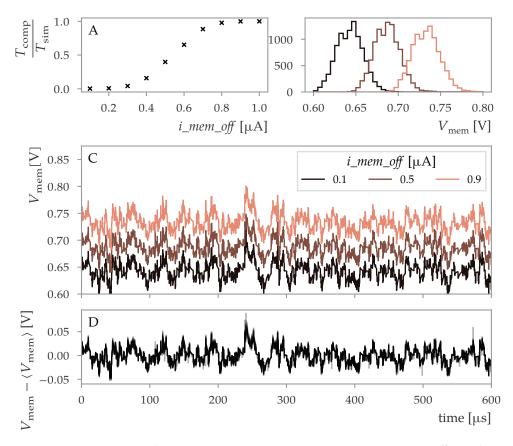

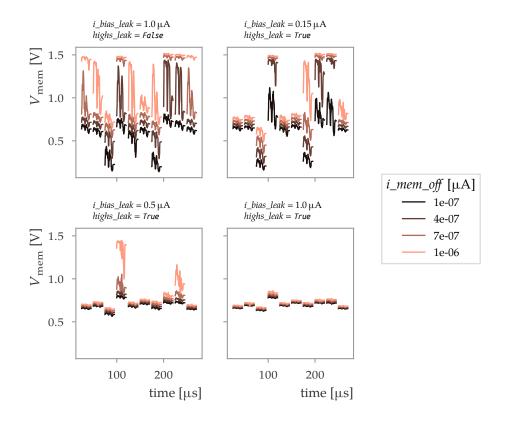

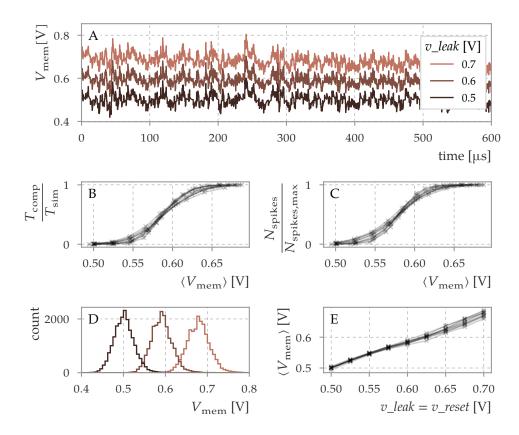

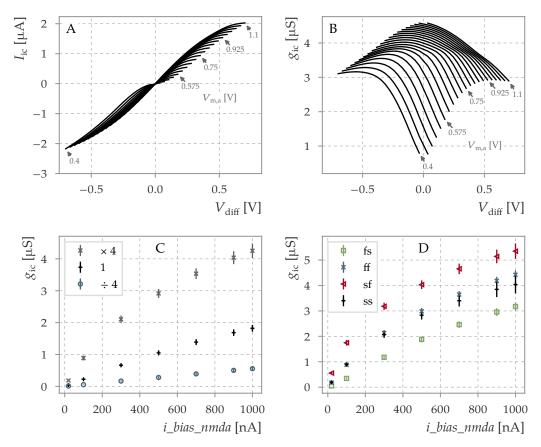

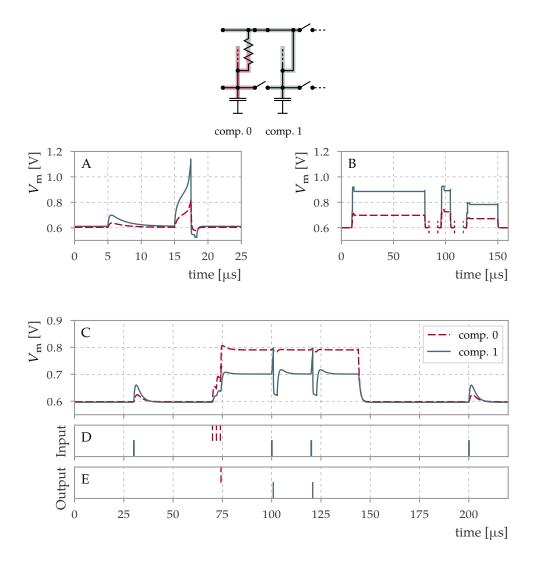

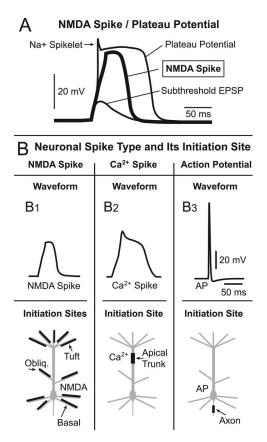

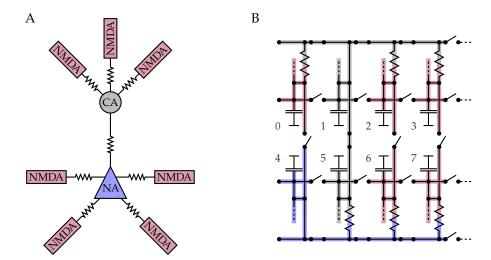

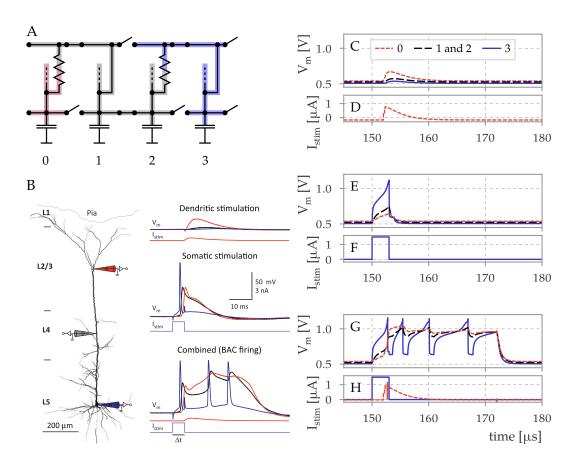

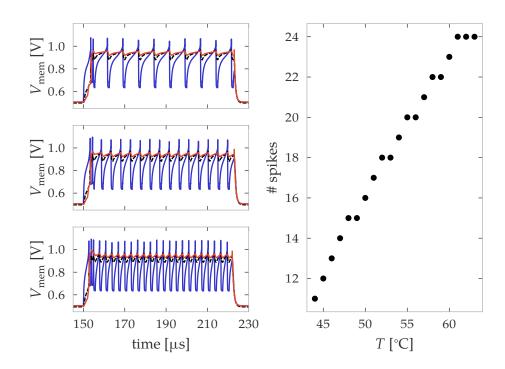

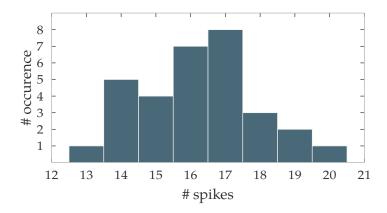

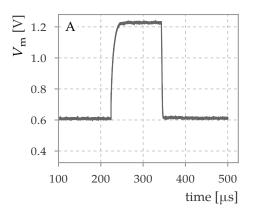

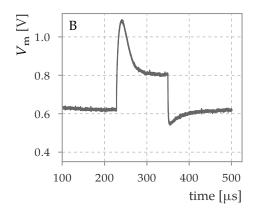

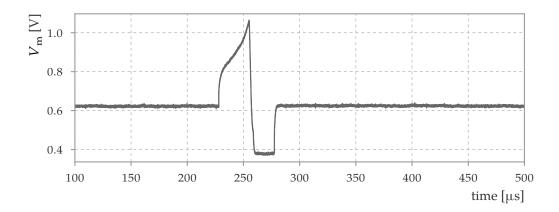

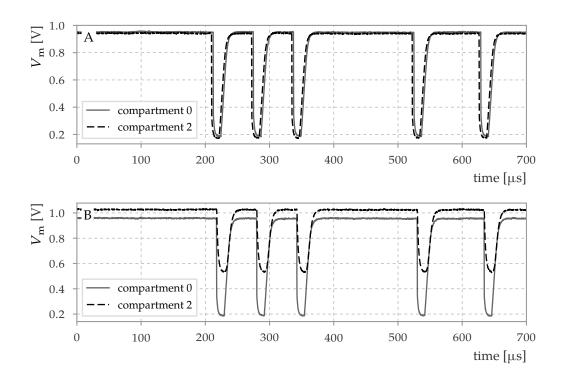

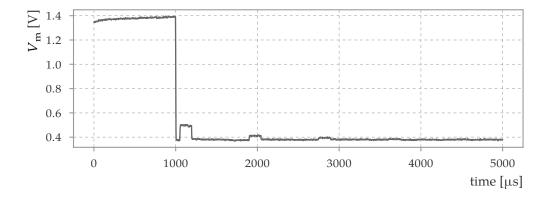

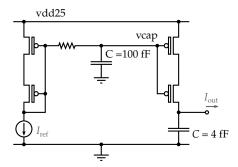

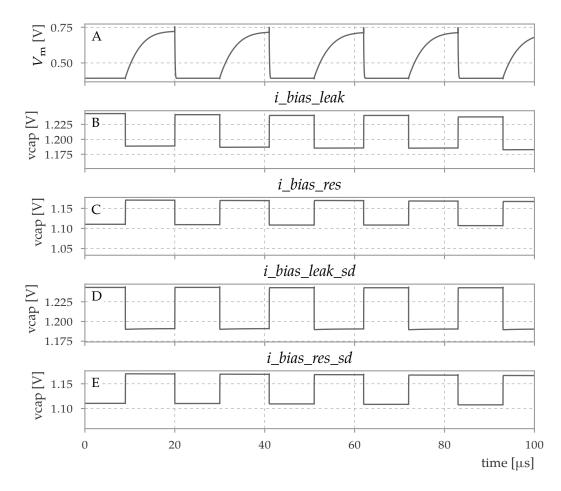

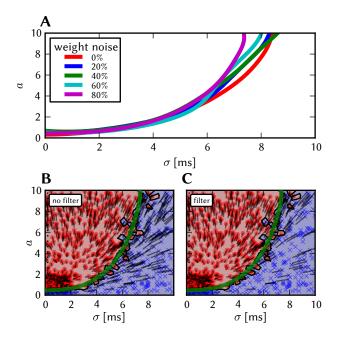

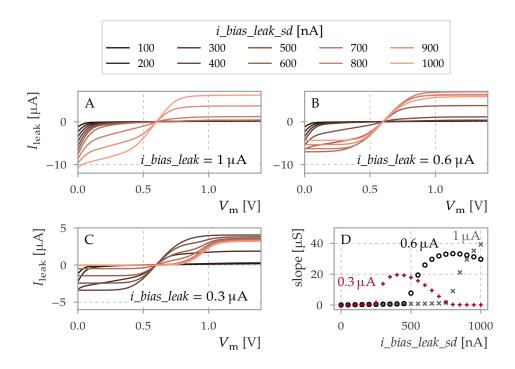

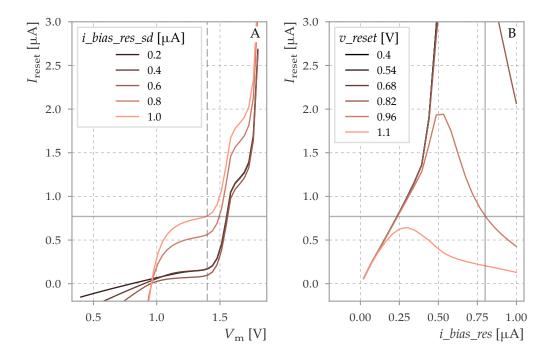

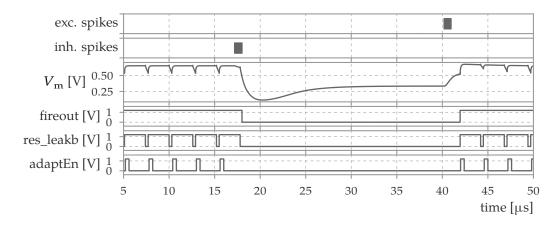

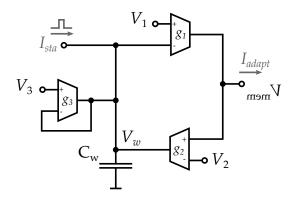

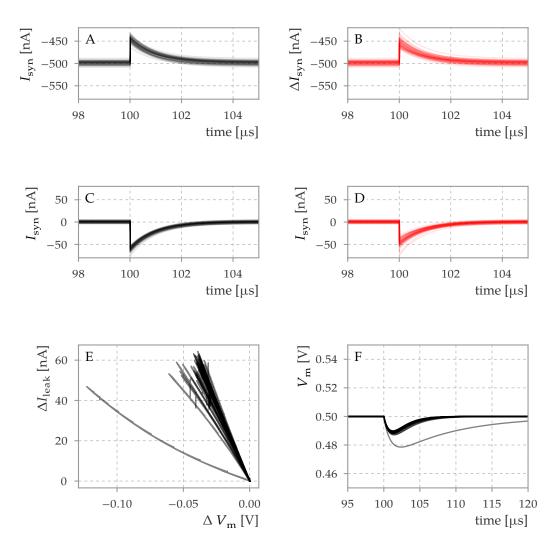

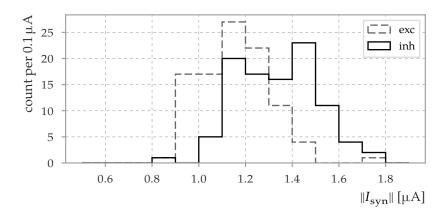

**Figure 2.8: A**: The location of the separatrix is controlled by the local axonal delay  $\Delta$ . **B**: A comparable control is achieved by varying the inhibitory synaptic weight at a fixed delay of 1.5 μs. The inhibitory synaptic time constant is increased by a factor of three for this simulation. The gray region covers the extent of separatrix locations in A. Used with permission from (Petrovici et al., 2014, Figure 16)