# Fakultät für Physik und Astronomie

Ruprecht-Karls-Universität Heidelberg

Diplomarbeit im Studiengang Physik

vorgelegt von **Boris Glass** aus Welzheim

September 1997

# Analoge Auslese- und Triggerelektronik für Mikrostreifen-Gaszähler

Die Diplomarbeit wurde von Boris Glass ausgeführt am Physikalischen Institut unter der Betreuung von Herrn Prof. Ulrich Straumann

Das Hera-B Experiment am Deutschen Elektronen-Synchrotron in Hamburg soll die CP-Verletzung am Zerfall von B-Mesonen nachweisen. Das Physikalische Institut der Universität Heidelberg beteiligt sich daran mit der Entwicklung eines Spurverfolgungssystems (Inner Tracker). Als Detektoren sind noch in der Entwicklung befindliche Mikrostreifengaszähler (MSGC) vorgesehen. In Zusammenarbeit mit dem Max-Planck-Institut für Kernphysik in Heidelberg wird eine anwendungsspezifische integrierte Schaltung (ASIC) als Ausleseelektronik entwickelt, die für Inner Tracker und Silizium-Vertex-Detektor eingesetzt werden soll.

Die vorliegende Diplomarbeit befaßt sich mit dem Design eines Komparators. Diese Baugruppe ist Teil der oben genannten integrierten Schaltung und dient dazu, vorverstärkte analoge Signale mit einer Referenzspannung zu vergleichen und so ein Triggersignal abzuleiten. Bestandteil meiner Arbeit waren außerdem Messungen an verschiedenen Prototypen integrierter Schaltungen sowie Mitarbeit beim Bau der elektronischen Infrastruktur von MSGCs und Ausleseelektronik.

Analog readout and trigger electronics for micro strip gas chambers:

The experiment HERA-B, which is currently under construction at DESY in Hamburg, is designed to measure a violation of the CP symmetry in the system of neutral B mesons. The "Physikalisches Institut der Universität Heidelberg" is contributing the development of the inner tracking system. The inner tracking detector will consist of micro strip gas chambers (MSGC) with custom made readout electronics. These application specific integrated circuits (ASICs) are designed in cooperation with the "Max-Planck-Institut für Kernphysik".

This thesis documents the development and testing of a fast comparator circuit to be integrated in the readout chip HELIX. The circuit compares pre-amplified analog detector signals with a programmable reference voltage and delivers a fast digital signal to the first level trigger (FLT). Different prototypes of ASICs were tested, and a PCB for readout and electronics tests was developed.

# Inhaltsverzeichnis

| 1 | $\mathbf{Ein}$ | leitung 1                                                    |

|---|----------------|--------------------------------------------------------------|

|   | 1.1            | Verletzung der CP-Symmetrie                                  |

|   | 1.2            | B-Meson-Fabriken                                             |

|   | 1.3            | Das HERA-B Experiment                                        |

|   | 1.4            | Inner Tracker                                                |

|   | 1.5            | Aufbau und Funktionsprinzip eines Mikrostreifen-Gaszählers   |

|   | 1.6            | Anbindung der Ausleseelektronik an die MSGC                  |

| 2 | Sim            | ulation der MSGC-Signale 12                                  |

|   | 2.1            | Monte Carlo Simulation der Signalentstehung                  |

|   | 2.2            | Netzwerksimulation der Signalfortpflanzung                   |

| 3 | Hoo            | chspannungstests mit Keramik-Adaptern 17                     |

|   | 3.1            | Adapter in Dickfilmtechnik                                   |

|   | 3.2            | Untersuchung von Schutzstrukturen an den Verstärkereingängen |

|   | 3.3            | Adapter in Dünnfilmtechnik                                   |

| 4 | Diff           | Gerentieller Komparator 22                                   |

|   | 4.1            | Differenzverstärker                                          |

|   |                | 4.1.1 Funktionsweise                                         |

|   |                | 4.1.2 Schaltungsentwurf                                      |

|   |                | 4.1.3 Großsignalmodell                                       |

|   |                | 4.1.4 Kleinsignalmodell                                      |

|   | 4.2            | AC-Kopplung                                                  |

|   | 4.3            | 4fach-Oder und D-Flip-Flop                                   |

|   | 4.4            | Layout                                                       |

|   | 4.5            | Simulation                                                   |

| 5 | Tes            | tchip Idefix 39                                              |

|   | 5.1            | Komponenten                                                  |

|   | 5.2            | Design                                                       |

|   | 5.3            | Testplatine                                                  |

|   | 5.4            | Messungen                                                    |

|   |                | 5.4.1 Aufbau                                                 |

|   |                | 5.4.2 Funktionstest                                          |

|   |                | 5.4.3 Schwellenverhalten                                     |

|   |                | 5.4.4 Rückkopplungsschaltung                                 |

|   |                | 5.4.5 AC-Kopplung                                            |

|   |                | 5.4.6 Flankensteilheit                                       |

|   |                | 5.4.7 Frequenzgang des Komparators                           |

|   |                | 5.4.8 Helix-Vorverstärker                                    |

|   |                | 5.4.9 Offsetschwankungen                                     |

|   |                | 5.4.10 Temperaturverhalten                                   |

| 6            | Helix 128S-2                                                     | 60 |

|--------------|------------------------------------------------------------------|----|

|              | 6.1 Selektion funktionsfähiger Chips zur Leiterplattenbestückung | 61 |

|              | 6.2 Leiterplatte für Betrieb des Helix 128S-2 an der MSGC        | 63 |

| 7            | Zusammenfassung                                                  | 69 |

| $\mathbf{A}$ | Wahrscheinlichkeitsverteilungen                                  | 70 |

|              | A.1 Fischle-Verteilung                                           | 70 |

|              | A.2 Verteilung der durch Ionen verzögerten Elektronen            | 70 |

| $_{ m Li}$   | teraturverzeichnis                                               | 72 |

## 1 Einleitung

Das erste Kapitel führt von der Physik der B-Mesonen über das Konzept von HERA-B zum inneren Spurkammersystem. Insbesondere wird ein Überblick über den Signalweg vom ionisierenden Teilchen in der Spurkammer bis zur Ausleseelektronik geboten.

Das zweite Kapitel beschäftigt sich mit der Signalentstehung in den Mikrostreifen-Gaszählern (MSGC).

Im dritten Kapitel geht es um Belastungstests an Keramik-Adaptern, die neben ihrer Hauptfunktion, die Mikrochips an die MSGC anzuschließen, auch für den Hochspannungsschutz der Elektronik eine Rolle spielen.

Der Schwerpunkt der Arbeit liegt in Kapitel vier. Hier wird der Entwurf einer differentiellen Komparatorschaltung und deren Umsetzung in ein Layout beschrieben.

Das fünfte Kapitel dokumentiert Design eines Testchips und Messungen an diesem Testchip zur Charakterisierung des Komparators.

Die Integration des Komparators in den Auslesechip Helix 128S-2 und Messungen an diesem Chip ergeben das sechste Kapitel.

Schließlich bietet das siebte Kapitel eine Zusammenfassung über die gewonnenen Ergebnisse.

## 1.1 Verletzung der CP-Symmetrie

Eine zentrale Rolle beim Verständnis der Physik spielen Symmetrien. Die wichtigsten diskreten Symmetrien sind die räumliche Spiegelung P, die Umkehr der Zeitrichtung T und die Ladungskonjugation C, die die Symmetrie zwischen Teilchen und Antiteilchen ausdrückt. Wenn sich Teilchen und Antiteilchen in der Natur völlig symmetrisch verhalten, haben wir keine Möglichkeit festzustellen, ob wir in einer Welt von Teilchen oder einer Welt von Antiteilchen leben. Tatsächlich scheint die Ladungskonjugation von der Natur nicht konsequent respektiert zu werden. Das Universum besteht überwiegend aus Materie und enthält fast keine Antimaterie, und auch im Bereich der Elementarteilchen wurde beim Zerfall von K-Mesonen eine Symmetriebrechung, nämlich die CP-Verletzung, beobachtet [SP97].

Eine theoretische Erklärung der CP-Verletzung wurde 1973 von M. Kobayashi und T. Maskawa vorgeschlagen. Sie hatten erkannt, daß die Theorie der Schwachen Wechselwirkung unter gewissen Vorraussetzungen automatisch zur CP-Verletzung führt, falls mindestens sechs Quarks existieren. Dies war 1973 eine mutige Spekulation, denn damals waren erst drei Quarks bekannt. Inzwischen kennt man sechs Quarks, womit eine entscheidene Voraussetzung für diese Erklärung erfüllt ist.

Ein Quark mit der Ladung  $\frac{2}{3}$  (u, c, t) kann durch Schwache Wechselwirkung in ein Quark mit der Ladung  $-\frac{1}{3}$  (d, s, b) übergehen, oder auch umgekehrt. Es gibt daher neun mögliche Quarkumwandlungen, die durch denselben Mechanismus vollzogen werden, sich aber in der Wahrscheinlichkeit der Umwandlung unterscheiden. Die Wahrscheinlichkeit des Übergangs von einem Quark q in ein anderes Quark q' ist proportional zum Betragsquadrat der Wahrscheinlichkeitsamplitude:  $P_{qq'} \sim |V_{qq'}|^2$ . Diese neun  $V_{ik}$  lassen sich in einer  $3 \times 3$ -Matrix zusammenfassen. Diese Matrix nennt man "Cabibbo-Kobayashi-Maskawa Matrix" (CKM-

2 1 EINLEITUNG

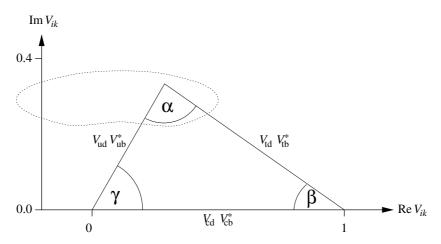

**Abbildung 1:** Das Unitaritätsdreieck veranschaulicht eine der Unitaritätsbeziehungen der CKM-Matrix (Glg. 1). Der Winkel  $\beta$  ist ein direktes Maß für die gesuchte CP-Verletzung [SP97]. Die gepunktete Linie umschließt qualitativ das Gebiet, in der die Spitze des Dreiecks vermutet wird [pro94].

Matrix) [PRSZ95]:

$$V_{

m CKM} = \left( egin{array}{ccc} V_{

m ud} & V_{

m us} & V_{

m ub} \ V_{

m cd} & V_{

m cs} & V_{

m cb} \ V_{

m td} & V_{

m ts} & V_{

m tb} \end{array}

ight)$$

Im Rahmen des Standardmodells der Elementarteilchenphysik muß die CKM-Matrix unitär sein, also die Beziehungen

$$\sum_{j} V_{ji} V_{jk}^* = \delta_{ik}$$

erfüllen. Damit verringert sich die Zahl unabhängiger Parameter der CKM-Matrix auf vier, die als drei reelle Winkel und eine imaginäre Phase gewählt werden können. Die im folgenden wichtige Unitaritätsbeziehung lautet

$$V_{\rm ud}V_{\rm ub}^* + V_{\rm cd}V_{\rm cb}^* + V_{\rm td}V_{\rm tb}^* = 0. (1)$$

Sie läßt sich als "Unitaritätsdreieck" in der komplexen Ebene veranschaulichen (Abb. 1).

Durch die Anwendung der CP-Operation auf einen Prozeß der Schwachen Wechselwirkung gehen die  $V_{ik}$  der CKM-Matrix in ihr Komplex-Konjugiertes über:

$$V_{ik} \xrightarrow{\mathrm{CP}} V_{ik}^*$$

.

Eine rein reelle CKM-Matrix bedeutet also, daß die Schwache Wechselwirkung CP-invariant ist. Kommt ein imaginärer Anteil in den Matrixelementen vor, kann die CP-Symmetrie nicht erhalten sein.

Auf der Suche nach CP-Verletzung in B-Systemen geht es daher um den Nachweis dieses Imaginärteils in der CKM-Matrix. Dazu wird eine besondere Zerfallsreaktion der B-Mesonen untersucht, nämlich der Zerfall eines B<sup>0</sup>-Mesons ( $\bar{b}d$ ) in ein J/ $\Psi$ -Teilchen ( $\bar{c}c$ ) und ein K<sup>0</sup><sub>S</sub>-Meson ( $\bar{s}d + s\bar{d}$ )/ $\sqrt{2}$ :

$$B^0 \longrightarrow J/\Psi K_S^0$$

Bei einem einfachen Prozeß der Schwachen Wechselwirkung tritt nur ein einziges  $V_{ik}$  auf. Die Übergangswahrscheinlichkeit ist dann proportional zu  $V_{ik}V_{ik}^*$  und damit offenbar CP-invariant. Erst durch die Überlagerung von mehr als einer Amplitude kann ein CP-verletzender Effekt entstehen

Die CP-Verletzung bei der Reaktion  $B^0 \longrightarrow J/\Psi K_S^0$  tritt nicht beim Zerfall des  $B^0$ -Mesons auf, sondern kommt durch eine vorangegangene  $B^0 \longleftrightarrow \bar B^0$  Teilchen-Antiteilchen-Umwandlung [Alb87] zustande. Es kann nicht unterschieden werden, ob der Endzustand direkt erreicht wurde oder ob zwischendurch eine  $B^0 \longleftrightarrow \bar B^0$ -Umwandlung stattfand. Durch das quantenmechanische Verhalten entsteht aber eine Interferenz der beiden Reaktionszweige. Nur durch diese Interferenz wird die CP-Verletzung beobachtbar. Der zeitliche Verlauf der CP-Verletzung wird durch die Interferenz mit der Umwandlungsfrequenz  $\omega = \Delta M \approx 0,5\,\mathrm{ps^{-1}}$  moduliert.  $\Delta M$  ist dabei die Massendifferenz zwischen dem kurzlebigen  $B_S^0$ -Meson und dem langlebigen  $B_L^0$ . Diese beiden  $B^0$ -Mesonen-Zustände sind Mischungen aus  $B^0$  und  $\bar B^0$ .

Die B<sup>0</sup>  $\longleftrightarrow$   $\bar{\rm B}^0$ -Umwandlung verläuft vor allem durch den Austausch des Top-Quarks. Entscheidend beim t-Quark-Austausch zwischen  $\bar{\rm b}$ - und d-Quark des B-Mesons sind die CKM-Matrixelemente  $V_{\rm td}V_{\rm th}^*$ .

Der Formalismus der CP-Verletzung im Standardmodell liefert für die Zerfallsrate eines  $B^0$ -Mesons in einen Endzustand f als Funktion der Zeit [SP97]:

$$N(\mathrm{B}^0 \longrightarrow f) = N_0 \, \mathrm{e}^{-\frac{t}{\tau}} \left( 1 - \mathrm{Im} \frac{V_{\mathrm{td}} V_{\mathrm{tb}}^*}{V_{\mathrm{td}}^* V_{\mathrm{tb}}} \sin(\Delta M \, t) \right)$$

und

$$\bar{N}(\bar{\mathbf{B}}^0 \longrightarrow f) = N_0 e^{-\frac{t}{\tau}} \left( 1 + \operatorname{Im} \frac{V_{\mathrm{td}} V_{\mathrm{tb}}^*}{V_{\mathrm{td}}^* V_{\mathrm{tb}}} \sin(\Delta M t) \right).$$

$N_0$  ist die Anzahl der erzeugten  $B^0$ -Mesonen und  $\tau \approx 1,6$  ps ihre mittlere Lebensdauer. Man sieht, daß sich die Zerfallsraten des  $B^0$  und seines Antiteilchens nur dann unterscheiden, wenn der Imaginärteil der CKM-Matrixelemente von Null verschieden ist. Aus dem Unitaritätsdreieck (Abb. 1) geht die Beziehung

$$\operatorname{Im} \frac{V_{\mathrm{td}} V_{\mathrm{tb}}^*}{V_{\mathrm{td}}^* V_{\mathrm{tb}}} = \sin 2\beta$$

hervor. Ziel des HERA-B-Experimentes ist es, die Asymmetrie der Zerfallsraten

$$\frac{\bar{N} - N}{\bar{N} + N} = \sin 2\beta \, \sin \Delta M \, t$$

zu messen, und damit gegebenenfalls die CP-Verletzung bei B-Mesonen zu entdecken.

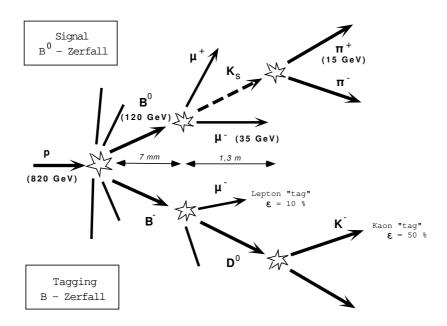

Die Reaktion  $B^0 \longrightarrow J/\Psi K_S^0$  nennt man auch den "goldenen" Zerfallskanal (Abb. 2). Sie hängt direkt und ohne komplizierte Korrekturen mit den fundamentalen Parametern der Schwachen Wechselwirkung zusammen. Vor allem aber ist der Endzustand des Zerfalls ein CP-Eigenzustand. Dadurch wird die Beobachtung der CP-Verletzung der  $B^0 \longleftrightarrow \bar{B}^0$ -Umwandlung nicht verfälscht.

Dieser ladungssymmetrische Endzustand bringt allerdings auch einen schweren Nachteil mit sich. Es läßt sich nur indirekt bestimmen, ob die beobachtete Reaktion von einem  $B^0$  oder

1 EINLEITUNG

Abbildung 2: Der B<sup>0</sup>-Zerfall

einem  $\bar{B}^0$  stammt. Dazu nutzt man aus, daß b-Quarks immer als b $\bar{b}$ -Paar entstehen und daher bei der Bildung eines B-Mesons immer auch das Antiteilchen erzeugt wird. Wählt nun ein B-Meson den goldenen Zerfallskanal, können durch Untersuchung des Zerfalls des Partnerteilchens die Ausgangsteilchen  $B^0$  und  $\bar{B}^0$  identifiziert werden. Als Signatur (Erkennungsmerkmal) für den Zerfall des Partnerteilchens eignet sich vor allem die Ladung von Kaonen oder Leptonen, die im Endzustand identifiziert werden können.

#### 1.2 B-Meson-Fabriken

Zu einer genauen Untersuchung des Zerfalls  $B^0 \to J/\Psi\,K_S^0$  müssen wegen des sehr geringen Verzweigungsverhältnisses von  $10^{-12}$  in diesem Kanal große Mengen von B-Mesonen erzeugt werden. Gegenwärtig entstehen weltweit vier Experimente zum Nachweis von CP-Verletzung.

- BABAR am SLAC in Stanford/USA,

- BELLE am KEK in Tsukuba/Japan,

- HERA-B am DESY in Hamburg und

- LHC-B am CERN in Genf/Schweiz (in Planung).

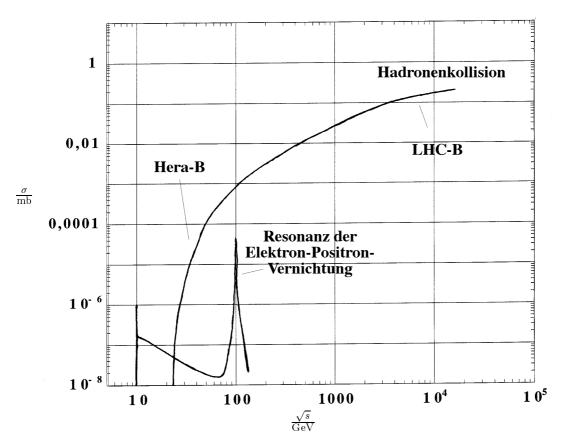

BABAR und BELLE nutzen e<sup>+</sup>e<sup>-</sup>-Paarvernichtung zur Erzeugung einer b<del>b</del>-Resonanz (Abb. 3). Ein sehr hoher Anteil von 60% des gesamten Wirkungsquerschnitts entfällt auf die gewünschten B<sup>0</sup><del>B</del><sup>0</sup>-Ereignisse. Unter Berücksichtigung der begrenzten Luminosität der Beschleunigers erwartet man bis zu 10<sup>8</sup> Ereignisse pro Jahr.

Abbildung 3: Wirkungsquerschnitt bei der b-Produktion (Skizze) [Str97]

HERA-B und LHC-B erzeugen B-Mesonen durch Hadronenkollisionen. Je nach Schwerpunktsenergie sind sehr viel höhere Wirkunsquerschnitte als bei der e<sup>+</sup>e<sup>-</sup>-Paarvernichtung möglich (Abb. 3). Das noch in der Planung befindliche LHC-B Experiment wird voraussichtlich ab 2004 in Betrieb gehen und mit wesentlich größeren Raten als HERA-B erstmalig Präzisionsmessungen ermöglichen. HERA-B soll ab 1999 die ersten Ergebnisse liefern.

#### 1.3 Das HERA-B Experiment

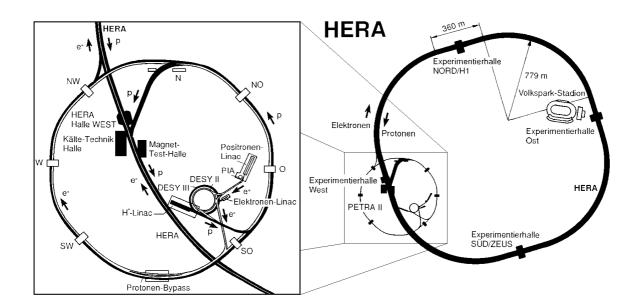

Abbildung 4 zeigt eine Übersicht der Beschleuniger, Speicherringe und der Experimentierhallen am DESY in Hamburg. HERA-B wird zur Zeit in Experimentierhalle West am HERA-Ring aufgebaut, an dem bereits die Experimente H1, ZEUS und HERMES betrieben werden. Im Gegensatz zu H1 und ZEUS kollidieren bei HERA-B nicht zwei Teilchenstrahlen miteinander. Vielmehr ragen acht Metalldrähte als festes Target in den Halo des Protonenstrahls, also in einen Randbereich, der für den Speicherring ohnehin verlorengeht. Damit wird der Teilchenfluß für die übrigen Experimente nicht beeinträchtigt.

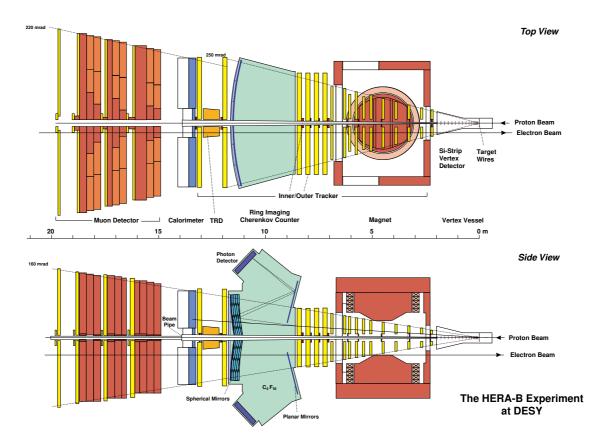

In Abbildung 5 ist der Aufbau des Detektors zu sehen. Im Einzelnen enthält HERA-B folgende Komponenten:

• Das Target besteht aus acht Metalldrähten, die im Abstand von einigen Millimetern um

6 1 EINLEITUNG

Abbildung 4: Beschleuniger, Speicherringe und Experimentierhallen am DESY. Der HERA-Ring besitzt einen Umfang von 6,3 km und befindet sich in einem unterirdischen Tunnel. In diesem Ring werden Protonen mit 820 GeV und Elektronen mit 28 GeV auf gegenläufigen Bahnen gespeichert. Die Ringe DESY und PETRA dienen zur Beschleunigung der Teilchen.

den Protonenstrahl herum gespannt sind.

- Ein Vertexdetektor aus Siliziumstreifendetektoren (SVD) ermöglicht die Bestimmung des genauen Wechselwirkungspunktes und der Sekundärvertices der B-Mesonen.

- Das innere Spurkammersystem (ITR) dient zur Spurrekonstruktion der Sekundärteilchen in einem Winkel zur Strahlachse von 10...40 mrad.

- Das äußere Spurkammersystem (OTR) ergänzt den ITR im Bereich von 40 bis 220 mrad.

- Mit einem magnetisches Spektrometer aus einem Dipolmagneten und Teilen des Trackingsystems werden die Impulse der Teilchen gemessen.

- Ein Čerenkov-Licht-Zähler (RICH) unterscheidet Protonen, Kaonen und Pionen.

- Ein elektromagnetisches Kalorimeter (ECAL) detektiert Elektronen.

- Schließlich identifiziert ein Myonen-Detektor Myonen-Paare.

Wegen des starken Lorentz-Boosts beschränkt sich der ganze Detektor auf einen Winkel von 220 mrad um die Strahlachse.

#### 1.4 Inner Tracker

Die Anforderungen an den Inner Tracker sind hoch. Teilchenraten bis zu  $10^4$  mm $^{-2}s^{-1}$  werden erwartet. Um Spuren eindeutig rekonstruieren zu können, ist daher eine hohe Granularität

1.4 Inner Tracker 7

Abbildung 5: Schnitt durch den Detektor (oben: Aufsicht, unten: Seitenansicht)

erforderlich. Außerdem darf die Strahlenbelastung nicht zu einem Ausfall des Inner Trackers führen. Ein noch sehr junges Detektorkonzept verspricht diese Anforderungen zu erfüllen. Sogenannte Mikrostreifengaszähler (MSGC) stellen eine Art vielkanalige Weiterentwicklung des Proportionalzählers dar.

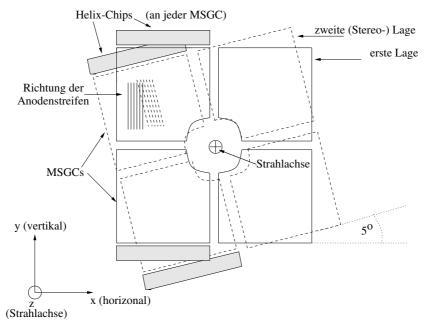

Der Inner Tracker dient sowohl zur Spurrekonstruktion, als auch zur Erzeugung des First-Level-Triggers. Rund 74.000 MSGC-Kanäle werden zur Erzeugung von Triggersignalen ausgewertet. Eine Detektorlage besteht aus vier aneinandergrenzenden MSGCs und deckt einen Radius von sechs bis 25 cm ab (Abb. 8). Jede dieser Lagen muß eine Nachweiswahrscheinlichkeit von 80% leisten. Insgesamt 192 MSGC überdecken eine Fläche von 17 m². Obwohl der Inner Tracker nur einen kleinen Raumwinkel abdeckt, erwartet man hier beinahe die Hälfte aller Teilchenspuren. Dies liegt an der nach außen stark abnehmenden Spurdichte.

Wegen großen Schwierigkeiten mit Hochspannungsüberschlägen (Sparks) in den MSGCs [Bre97] im Winter 1996/97 schien dieses Detektorkonzept jedoch nicht einsatzfähig zu sein. Eine modifizierte MSGC mit einer gelochten Elektrodenfolie als Gasvorverstärker (GEM) löste die Probleme mit den "Sparks" und begeisterte durch stabilen Betrieb in einem Teststrahl.

Die vorliegende Arbeit bezieht sich stellenweise noch auf die einfache MSGC ohne Gasvorverstärker. Dies ist jedoch kein Nachteil, da sich beide Kammertypen, aus der Sicht der Elektronik, nur in der erreichbaren Gasverstärkung unterscheiden.

8 1 EINLEITUNG

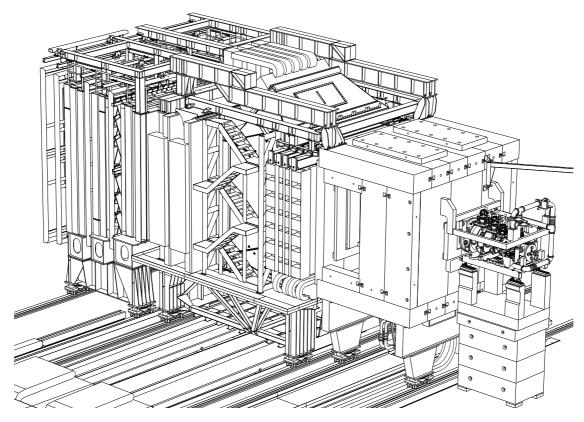

Abbildung 6: Schrägansicht des Detektors

## 1.5 Aufbau und Funktionsprinzip eines Mikrostreifen-Gaszählers

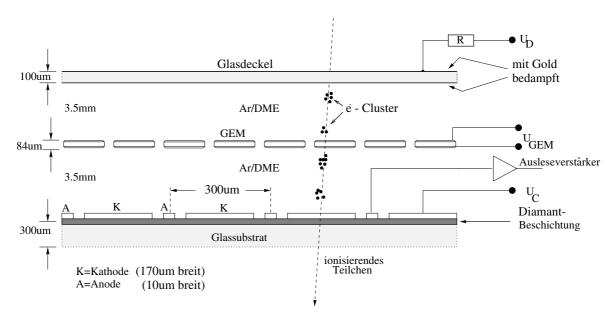

Die MSGC besteht im wesentlichen aus den folgenden Teilen (Abb. 7):

- Der Boden der Kammer wird aus aus einem  $300\,\mu\mathrm{m}$  dicken Glaswafer geschnitten.

- Dieser Boden wird mit Gold, Aluminium oder Chrom beschichtet und anschließend photolithographisch strukturiert. Dabei entstehen streifenförmige Anoden und Kathoden

- Darüber wird die Kammer im Abstand von einigen Millimetern durch einen vollflächig metallisierten Deckel abgeschlossen, der gleichzeitig als Driftelektrode dient.

- Im Falle einer MSGC mit GEM (Gas-Elektronen-Multiplier) [Oed97] wird zwischen Boden und Deckel eine perforierte und beidseitig metallisierte Kaptonfolie gespannt, die zur Gasvorverstärkung dient.

- Die Unterseite des Glasbodens ist ebenfalls metallisch beschichtet. Diese "Backplane" verringert das Übersprechen zwischen den Anoden und die Einkopplung von Störsignalen der Umgebung auf die Anoden.

- Eine schwach leitende Schicht (coating) über oder unter den Anoden und Kathoden dient zur Ableitung statischer Ladungen auf dem Glassubstrat, die die Feldkoniguration ändern und langfristig das Substrat elektrochemisch beschädigen würden.

Abbildung 7: Querschnitt durch eine MSGC mit Gasvorverstärkung

Zwischen den beiden Seiten der Gasverstärkungsfolie (GEM) wird eine Spannung von 300 bis 500 V angelegt. Typische Betriebsspannungen der MSGC mit GEM sind 500 V zwischen Kathoden und Anoden und 6 kV zwischen Driftelektrode und Anoden. Die Backplane liegt auf Anodenpotential. Bei der MSGC ohne GEM muß die gesamte Gasverstärkung im Feld zwischen Kathode und Anode stattfinden.

Durchquert ein ionisierendes Teilchen den Gasraum einer MSGC kommt es in folgenden Schritten zur Entstehung eines Signals:

- Ein durch die Kammer fliegendes Teilchen erzeugt auf seiner Bahn im Gasgemisch Ionen-Elektronen-Paare. Bei dieser *primären Ionisation* entstehen im allgemeinen mehrere Gruppen (cluster) ionisierter Teilchen, die wiederum aus mehreren Ionen-Elektronen-Paaren bestehen.

- Zwischen Deckel und Boden der Kammer liegt eine Spannung an, wodurch ein Driftfeld von etwa 10 kV/mm auf die getrennten Ionen und Elektronen wirkt. Dadurch wird eine Rekombination verhindert, die Ionen wandern zum Deckel und die Elektronen driften in Richtung der Kathoden und Anoden.

- Bei einer MSGC mit einer Gasvorverstärkungsfolie (GEM) müssen Elektronen aus dem oberen Gasraum die Folie durchqueren. Durch die an die GEM angelegte Spannung wird das Driftfeld deformiert, sodaß die Feldlinien stark eingeschnürt durch die Löcher der Folie verlaufen. Die Elektronen werden durch das Feld in den Löchern so stark beschleunigt, daß sie selbst ionisierend wirken und eine Lawine ionisierter Teilchen erzeugen. Je nach Einstellung der Kammerparameter wird jedes Primärelektron im Mittel durch 20 weitere Elektronen verstärkt Nach dem Austritt aus der Folie driften die Elektronen weiter zum Boden der Kammer.

- Auch zwischen den eng nebeneinanderliegenden Anoden und Kathoden wird eine Spannung angelegt. Auch hier ist das elektrische Feld so stark, daß es zur Gasverstärkung

1 EINLEITUNG

kommt.

• Nicht alle Sekundärelektronen treten sofort in die Anode ein. Vielmehr verzögert sich ein Teil durch die attraktive Wirkung der positiven Ionen.

Abschnitt 2.1 beschäftigt sich mit der Simulation dieses Vorgangs.

## 1.6 Anbindung der Ausleseelektronik an die MSGC

Abbildung 8: Montage einer Doppellage mit Stereowinkel. Die Ausleseelektronik wird direkt an die Kammern montiert.

Abbildung 8 zeigt, wie eine Doppellage aus acht MSGCs um das Strahlrohr montiert wird. Die Anodenstreifen laufen längs der y-Achse und ergeben dadurch eine Ortsauflösung von  $300\,\mu\mathrm{m}$  in x-Richtung. Durch die Verdrehung einer Lage um  $5^{\circ}$  wird durch Auswertung einer Doppellage die Bestimmung der y-Koordinate einer Teilchenspur bis auf etwa 1 mm möglich.

Zur Auslese der MSGCs wurde am "ASIC Labor Heidelberg" ein anwendungsspezifischer integrierter Schaltkreis entwickelt (ASIC: application specific integrated circuit). Der sogenannte "Helix128S-2" stellt die aktuelle Version dieses Mikrochips dar. Die Verbindung der MSGCs mit den ASICs kann nicht auf konventionelle Weise erfolgen. Jede MSGC besitzt 768 Anoden mit einem Anschlußpitch von 300  $\mu$ m. Diese müssen an die Eingänge von sechs Helix-Chips mit je 128 Eingängen und einem Pitch von 41,4  $\mu$ m angeschlossen werden. Realisiert wurden diese Verbindungen durch ein Folienkabel aus Kapton mit Kupferleiterbahnen und ein aus Keramik hergestelltes Fan-In, das gemeinsam mit den Helix-Chips auf eine Platine geklebt wird. Das Kaptonkabel verringert den Pitch von 270  $\mu$ m auf 200  $\mu$ m. Mit einem speziellen

<sup>&</sup>lt;sup>1</sup>Das Asic-Labor Heidelberg wurde 1994 als gemeinsame Einrichtung des Instituts für Hochenergiephysik, des Max-Planck Instituts für Kernphysik und des Physikalischen Instituts gegründet. Zielsetzung des ASIC-Labors sind die Entwicklung und der Test von ASICs und FPGAs (field programmable gate arrays).

Klebstoff, der kleine Metallkugeln enthält, wird das Kabel als Brücke zwischen MSGC und Fan-In geklebt ("Z-Bonding"), womit gleichzeitig die elektrischen Verbindungen hergestellt werden. Zusätzlich enthält der Keramik-Adapter je einen Widerstand pro Kanal, der zum Hochspannungsschutz des Auslesechips beiträgt. Bei der Beschichtung der Keramiken und Strukturierung der gewünschten Leiterbahnen und Bondflächen kommen Dick- oder Dünnfilmtechnologien in Frage. Kapitel 3 enthält außer einem Überblick über beide Techniken jeweils die Ergebnisse von Messungen der elektrischen Belastbarkeit.

Die elektrische Verbindung zwischen Keramik-Adapter und Helix-Chips wird durch "Wire-Bonden" hergestellt. Darunter versteht man die Verbindung mit einem feinen Gold- oder Aluminiumdraht von etwa  $25\,\mu\mathrm{m}$  Durchmesser, der nicht angelötet, sondern mit einem speziellen Werkzeug auf das Pad gedrückt und mit einem Ultraschallimpuls erhitzt wird.

Die durch ein ionisierendes Teilchen in der MSGC verursachte Ladung fließt von der Anode der MSGC zum Vorverstärker des Helix-Chips. Der Vorverstärker und der nachfolgende Impulsformer erzeugen einen Spannungsimpuls, dessen Amplitude linear zur eingekoppelten Ladung abhängt. Dieses Signal wird gleich zweifach verwendet:

- Der analoge Pfad dient zur Auswertung der Signalhöhe. Er enthält eine Speicherkette (Pipeline), mit der die Spannungspegel bis zu einer eventuellen Auslese zwischengespeichert werden.

- Der Triggerpfad vergleicht das Signal mit einer Triggerschwelle und erzeugt aus jeweils vier benachbarten Kanälen ein digitales Triggersignal.

Der Vergleich des Signals mit einer Referenzspannung im Triggerpfad geschieht durch einen Komparator, der in Kapitel 4 beschrieben wird. Ein Testchip ermöglicht Messungen zur Charakterisierung dieses Komparators. Entwurf und Layout dieses Testchips und einer zugehörigen Platine werden in Kapitel 5 dargestellt.

Der Komparator wurde schließlich in den Helix 128S-2 integriert. Kapitel 6 faßt die Funktionen des Helix 128S-2 zusammen, soweit sie den Triggerpfad betreffen. Außerdem wird der Prototyp einer Leiterplatte für den Betrieb der Auslesechips mit der MSGC am HERA-B Experiment beschrieben.

# 2 Simulation der MSGC-Signale

Um die Ausleseelektronik für einen Detektor optimieren zu können, muß man verstehen, wie Signale im Detektor entstehen und auf dem Weg zur Elektronik verändert werden.

Im Laufe der Entwicklung der MSGC für HERA-B wurde versucht, mit Hilfe von Anoden und Kathoden aus Chrom oder Rhodium statt Gold robuste MSGCs herzustellen, die nicht durch Sparks zerstört werden. Rhodium und erst recht Chrom besitzen aber einen wesentlich höheren elektrischen Widerstand. Das führt im Zusammenhang mit den unvermeidbaren Kapazitäten von Anode und Kathode zu einer drastischen Verschlechterung der Signalfortpflanzung. Daher sollte im Rahmen dieser Arbeit untersucht werden, ob eine MSGC aus Chrom oder Rhodium mit der nötigen Effizienz ausgelesen werden kann.

## 2.1 Monte Carlo Simulation der Signalentstehung

Mit einer Monte-Carlo-Simulation soll der in Kapitel 1.5 beschriebene Vorgang der Signalentstehung in der MSGC nachvollzogen werden. Mit dieser Methode können zufällige, statistische verteilte Ereignisse gemäß den angenommenen Wahrscheinlichkeitsverteilungen nachvollzogen werden. Diese Simulation wurde im November 1996 erstellt und beschreibt daher noch eine MSGC ohne GEM.

Zunächst wird für die primäre Ionisation bestimmt, wieviele Cluster enstehen, wo die Cluster entstehen und wieviele Elektronen die einzelnen Cluster enthalten [Sch96]:

• Die Anzahl der Cluster ist Poisson-verteilt:

$$P_k = \frac{\overline{n}_{\rm C}^k}{k!} e^{-\overline{n}_{\rm C}} \longrightarrow n_{\rm C}$$

$\overline{n}_{\rm C}=13,8$  ist ein empirischer Mittelwert für den Betrieb mit dem Gasgemisch Argon/DME im Verhältnis 1:1, bei einer Höhe des Gasraumes von  $h=3,3\,\mathrm{mm}$  und einer zum Deckel und Boden senkrechten Bahn des Teilchens.

• Die Orte der einzelnen Cluster sind über die Flugbahn des Teilchens gleichverteilt. Da das Teilchen senkrecht durch die Kammer laufen soll, sind x = y = 0. Die z-Koordinate kann alle Werte zwischen 0 und h annehmen. Die Wahrscheinlichkeitsdichte p der Gleichverteilung ist konstant:

$$p_z = \frac{1}{h} \longrightarrow z$$

• Jeder Cluster besteht aus unterschiedlich vielen Elektronen. Hierfür wird eine empirische Verteilung ("Fischle"-Verteilung) herangezogen (siehe Anhang A.1).

Nun wird die Drift der einzelnen Cluster bis zur Anode modelliert.

• Jeder Cluster benötigt für seinen Weg bis zur Anode die Driftzeit  $\overline{t}_{\rm A}=\frac{z}{v}$ . Die Driftgeschwindigkeit zur Anode kann als konstant angenommen werden:  $v=57\frac{\mu{\rm m}}{{\rm ns}}$ . Der

Cluster hat allerdings eine Ausdehnung, die im Laufe des Driftens wegen der elektrischen Abstoßung und Stößen mit dem Gas zunimmt. Es wird angenomen, daß die Ankunftszeit der einzelnen Elektronen eines Clusters gaußverteilt ist:

$$p(t_{\mathrm{A}}) = \frac{1}{\sqrt{2\pi} \ \sigma_{t_{\mathrm{A}}}} \exp\left(-\frac{1}{2} \frac{(t - \overline{t}_{\mathrm{A}})^2}{\sigma_{t_{\mathrm{A}}}^2}\right)$$

An dieser Stelle wird aber keine Zufallsvariable aus der Verteilung bestimmt, sondern die Ankunftsdichte  $\delta(t-\overline{t}_{\rm A})\cdot n_{\rm C}$  (ohne Diffusion) der einzelnen Cluster mit der Gaußkurve gefaltet. Das Simulationsprogramm baut eine Tabelle endlich großer Zeitabschnitte auf und speichert darin die Anzahl der im jeweiligen Zeitabschnitt angekommenen Elektronen.  $\sigma_{t_{\rm A}} \approx \sqrt{\frac{z}{\rm mm}} \cdot 0$ , 7 ns ist ein empirisch bestimmter Parameter. Eine transversale Diffusion, die zur Verteilung eines Clusters auf mehrere Anodenstreifen führen kann, soll nicht berücksichtigt werden.

• Nicht alle Sekundärelektronen treten sofort in die Anode ein. Vielmehr verzögert sich ein Teil durch die attraktive Wirkung der positiven Ionen. Es wird angenommen, daß die Hälfte der Elektronen sofort freigegeben wird, die andere Hälfte aber erst nach einer Zeit, die durch eine weitere empirische Verteilung bestimmt wird (siehe Anhang A.2).

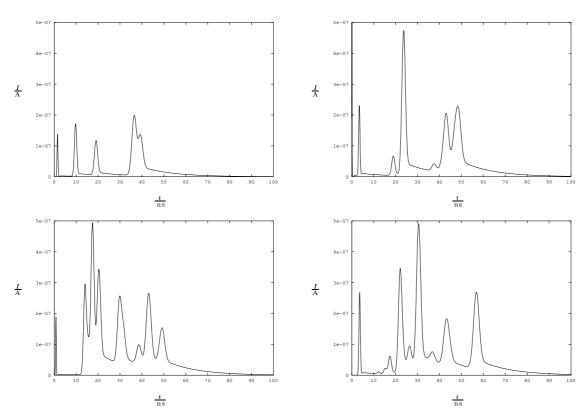

Abbildung 9: Vier Beispiele eines simulierten MSGC-Signals, die durch mehrmaligen Ablauf desselben Programms entstanden sind.

Läßt man die Simulation sehr oft ablaufen und führt dabei ein Histogramm über die Gesamtladung der Ereignisse, erhält man eine Verteilung, die der Landau-Verteilung [Leo87] nahekommt:

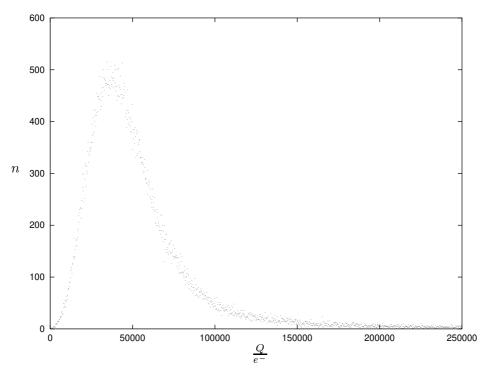

**Abbildung 10:** Verteilung der Gesamtladung bei 10<sup>5</sup> Ereignissen.

Anhand dieses Plots (Abb. 10) läßt sich gut erklären, was bei Spannungs- oder Ladungsangaben in Zusammenhang mit einem "MIP" (minimal ionisierendes Teilchen) gemeint ist. Bei der hier simulierten Kammer ist die wahrscheinlichste Ladung, die durch ein MIP verursacht wird  $4, 0 \cdot 10^4 e$ . Der Erwartungswert ist  $5, 3 \cdot 10^4 e$ . Das gleiche Teilchen könnte auch ein nicht meßbar kleines Signal erzeugen oder eine Ladung von mehreren  $10^5 e$ .

### 2.2 Netzwerksimulation der Signalfortpflanzung

Nachdem die Elektronen aus dem Gasraum in die Anode eingetreten sind, verteilt sich die Ladung über die Anode und fließt letztendlich über den Eingang des angeschlossenen Verstärkers ab. Anode und Kathode haben einen nur geringen Querschnitt und damit einen nennenswerten ohmschen Widerstand. Außerdem kommt es zwischen Anode, Kathode und Backplane zur gegenseitigen kapazitiven Kopplung.

In den beiden folgenden Tabelle sind die Kapazitäten zwischen Anode, Kathode und Backplane und die Widerstände einer Anode aus Gold, Rhodium und Chrom für die Geometrie nach Abbildung 7 jeweils pro Länge der Streifen angegeben [Sch96]:

| $C_{ m AK}$         | $C_{ m AB}$         | $C_{ m KB}$         |

|---------------------|---------------------|---------------------|

| $20, 3\frac{pF}{m}$ | $11.0 \frac{pF}{m}$ | $31, 2\frac{pF}{m}$ |

| $R_{ m Au}$                             | $R_{ m Rh}$                             | $R_{ m Cr}$                               |

|-----------------------------------------|-----------------------------------------|-------------------------------------------|

| $20\frac{\mathrm{k}\Omega}{\mathrm{m}}$ | $60\frac{\mathrm{k}\Omega}{\mathrm{m}}$ | $1500\frac{\mathrm{k}\Omega}{\mathrm{m}}$ |

Zu beachten ist, daß jede Anode zwei Kathoden als Nachbarn besitzt.  $C_{\rm AK}$  tritt also gleich zweimal pro Anode auf. Die ohmschen Widerstände hängen nicht nur vom verwendeten Material und Querschnitt der Streifen sondern auch von der Herstellungsmethode ab.

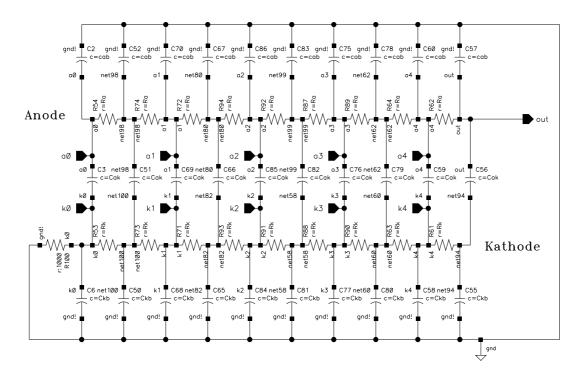

Abbildung 11: R-C-Netzwerk als elektrisches Modell einer MSGC

Um das System aus kontinuierlichen Widerständen und Kapazitäten simulieren zu können, wird ein diskretisiertes Modell verwendet (Abb. 11). Eine Anode und eine benachbarte Kathode werden in Reihenschaltungen aus jeweils 9 Widerständen zerlegt. Die Summe der Widerstände ergibt den Anoden- bzw. Kathodenwiderstand bei gegebener Länge. Die Kapazität zwischen Anode und Kathode wird entsprechend in 10 Kondensatoren zerlegt, die die Anoden- und Kathodenketten verknüpfen. Schließlich stehen jeweils 10 Kondensatoren für die Kapazität von Anode und Kathode mit der Backplane. Die Backplane ist für die Simulation als Nullpotential ("gnd") definiert.

Das Eintreten von Elektronen in die Anode wird durch eine Stromquelle zwischen Anode und Kathode simuliert. Interessante Signale, die damit eingekoppelt werden können, sind  $\delta$ - und Rechteck-Impulse oder Signale, die durch Simulation der Signalentstehung in der MSGC erzeugt wurden. Entsprechend der Anodenunterteilung in neun Widerstände kann das Signal an zehn verschiedenen Stellen eingespeist werden (Im Netzwerk Abb. 11 sind fünf davon als Anschlüsse a0/k0 bis a4/k4 vorgesehen).

Eine Seite der Anode ist mit dem Eingang des Vorverstärkers verbunden. Als einfacher Ersatz für die Belastung durch den Verstärker können auch ein Kondensator und ein Widerstand gegen Masse verwendet werden.

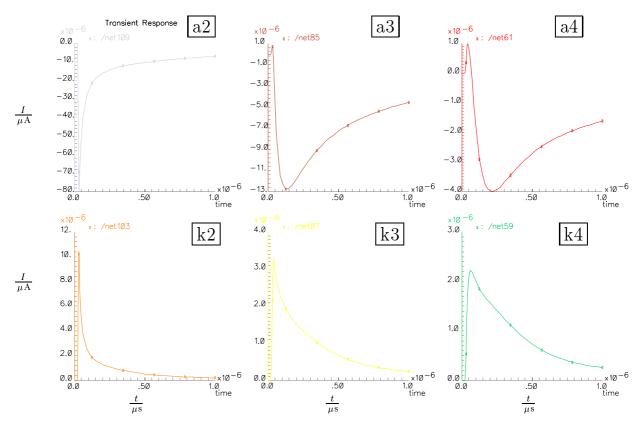

Das Ergebnis einer Simulation, bei der ein  $\delta$ -Impuls in das RC-Netzwerk eingespeist wurde zeigt Abbildung 12. Die Driftzeit der Primärcluster (voriges Kapitel) und die Verbreiterung der Signale auf dem Weg durch die Anodenstreifen bestimmen die nötige Integrationszeit des Ausleseverstärkers.

Abbildung 12: Simulation der Signalfortpflanzung im RC-Netzwerk: Antwort des in Abbildung 11 gezeigten Netzwerkes auf einen  $\delta$ -förmigen Stromimpuls, der zwischen den Netzwerkknoten a2 und k2 eingespeist wurde. Die Anoden- und Kathodenwiderstände entsprechen einer Gold-beschichteten MSGC. In den Plots a2 bis a4 sieht man die Verzögerung und Verbreiterung des Signals auf dem Anodenstreifen bei Verringerung der Amplitude (Skala der y-Achse ändert sich). Die unteren drei Plots zeigen, wie sich das Signal auf der Kathode ausbreitet.

## 3 Hochspannungstests mit Keramik-Adaptern

Die Anoden der MSGC werden über ein flexibles Folienkabel mit der Helix-Leiterplatte (Kap. 6.2) verbunden. Das Folienkabel hat MSGC-seitig ein Rastermaß (pitch) von  $270\,\mu\mathrm{m}$ . Der geringe Pitch der Helix-Eingangskanäle von  $41,4\,\mu\mathrm{m}$  kann mit einem Folienkabel nicht kontaktiert werden. Auch auf einer Leiterplatte sind Strukturen mit einem Pitch kleiner als  $100\,\mu\mathrm{m}$  nicht realisierbar.

Als Adapter zwischen Folienkabel und Chip fungiert daher ein Keramik-Plättchen. Der MSGC-Pitch wird auf dem Folienkabel schon auf  $200\,\mu\mathrm{m}$  reduziert, um den Adapter klein zu halten. Das verbessert die Ausbeute und verringert die Kosten bei der Herstellung.

Als Schutz vor Hochspannungsüberschlägen in der MSGC wurden Prototypen des Helix mit Schutzdioden und -widerständen ausgestattet. Tests haben gezeigt, daß diese Schutzstrukturen alleine nicht ausreichend sind [Bec96]. Die auf dem Chip integrierten Widerstände halten der Belastung eines HV-Überschlags nicht stand. Der Schutzwiderstand soll daher extern angebracht werden. Aufgrund der genannten Platzprobleme, die schon bei der einfachen elektrischen Verbindung enstehen, werden die Widerstände auf dem Keramik-Adapter integriert.

Erste Prototypen des Adapters wurden an der Universität-GH-Siegen in Dickfilmtechnik hergestellt. Später wurde wegen Schwierigkeiten bei Herstellung und Verarbeitung die Produktion der Keramik-Adapter in Dünnschichttechnologie an einen kommerziellen Hersteller vergeben. Meine Aufgabe war es, die Belastbarkeit der Dick- und Dünnfilmwiderstände zu messen, die Hochspannungsfestigkeit des Helix-Chips in Verbindung mit den Keramik-Adaptern zu überprüfen und aufgrund dieser Erkenntnisse eine geeignete Dimensionierung der Widerstände zu bestimmen.

## 3.1 Adapter in Dickfilmtechnik

Bei der Dickfilmtechnologie werden Leiterbahnstrukturen im Siebdruckverfahren auf Keramikplatten aus Al<sub>2</sub>O<sub>3</sub> aufgedruckt [Geb97]. Die Leiterbahnpasten bestehen üblicherweise aus einem Gemisch von Silber-Palladium- und Glaspartikeln, die in ein zähflüssiges Lösungsmittel eingebettet werden. Die aufgedruckten Leiterbahnen werden in einem Ofen bei einer Temperatur von 850°C eingebrannt. Dadurch verschmelzen die Partikel miteinander und bilden eine leitfähige Struktur aus. Die schmelzenden Glaspartikel sorgen für eine gute Haftung auf dem Keramikträgermaterial.

Danach kann die Schaltung weiter aufgebaut werden, z.B. durch Aufdrucken einer Isolationsebene und einer weiteren Leiterbahnebene, die mittels Durchkontaktierungsfenster mit der darunter liegenden Leiterbahnebene verbunden ist. Es können mehrere Leiterbahnebenen mit zwischenliegenden Isolationsschichten übereinander gedruckt werden. Die Isolationspasten bestehen meist nur aus Glas-Partikeln im pastenförmigen Lösungsmittel. Auch die benötigten Widerstände werden im Siebdruckverfahren aufgedruckt. Wichtig ist, daß jede der aufgedruckten Schichten für sich eingebrannt werden muß. Auf diese Weise können Schaltungen, wie bei der Leiterplattenherstellung, in mehreren Lagen realisiert werden. Wenn alle Schichten aufgedruckt und eingebrannt sind, werden die Widerstände mit Hilfe eines Lasers auf

Abbildung 13: Keramikadapter in Dickfilmtechnik mit Helix128S-2 (vorne rechts).

die gewünschten Werte getrimmt, was eine sehr hohe Genauigkeit ermöglicht. Mit der Dickfilmtechnologie sind Leiterbahnbreiten und Zwischenräume bis minimal  $100\,\mu\mathrm{m}$  entsprechend  $200\,\mu\mathrm{m}$  Rasterabstand möglich. Kleinere Strukturen können durch die Nachbearbeitung mit einem Laser erreicht werden.

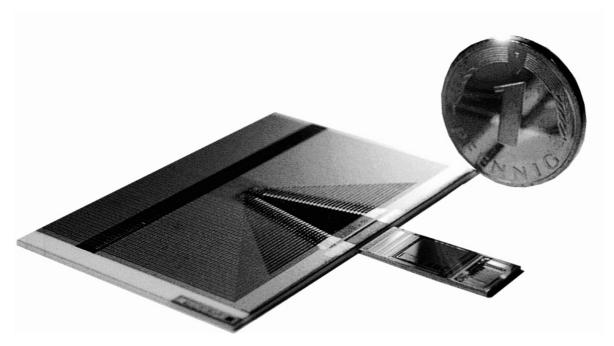

Die Prototypen der Universität-GH-Siegen besitzen einen Pitch von 270  $\mu$ m auf der MSGCund 41.4  $\mu$ m auf der Helix-Seite. Jeder der 128 Kanäle besitzt einen integrierten Widerstand. Die Widerstände des untersuchten Prototypen hatten Werte von 1,0 k $\Omega$  bis 1,4 k $\Omega$  bei einem konstanten Gradienten vom ersten bis zum letzten Kanal. Die Oberfläche der Leiterbahnen war für das Bonden nur eingeschränkt geeignet. Das lag zum einen an den Eigenschaften der Silber-Palladium-Legierung, zum anderen an Rückständen durch die Laser-Strukturierung und an Graten an den Leiterbahnkanten, die ebenfalls durch die Laser-Bearbeitung entstanden sind. Diese Grate hindern das Bondwerkzeug am flächigen Kontakt mit der Leiterbahn.

Abbildung 14: Belastung der Filmwiderstände durch Entladung eines Kondensators

Zunächst wurden die Keramik-Adapter alleine einem Belastungstest unterzogen:

• Die Maximale Dauerleistung der Widerstände ist 6,7W. Bei der Messung wurden Strom

und Spannung durch einen Kanal bis zur Zerstörung gemessen. Die Nachbarwiderstände wurden dabei nicht gleichzeitig belastet.

- Ab 3,0 kV treten Überschläge zwischen den Kanälen auf.

- Die kurzfristige Belastbarkeit durch Spannungsspitzen (Überschläge in der MSGC) wurden durch Entladung eines Kondensators über einen Schalter und den Keramik-Adapter getestet (Abb. 14). Als Schalter wurde ein hochspannungsfester Taster verwendet. In Verbindung mit einem Kabel von etwa 20 cm zwischen Taster und Prüfling, konnten damit Hochspannungspulse mit einer Anstiegszeit von etwa  $50\frac{V}{ns}$  erzeugt werden. Bei  $C=10\,\mathrm{nF}$  halten die Widerstände bis 1,05 kV. Bei einem realistischen  $C=100\,\mathrm{pF}$  wurden die Widerstände bei 3,5 kV noch nicht beschädigt. Die Hochspannung der MSGC liegt bei 1,0 kV oder weniger.

Die Dickfilmwiderstände sind also hinreichend robust.

## 3.2 Untersuchung von Schutzstrukturen an den Verstärkereingängen

Die Schutzwiderstände des Keramik-Adapter sollen gerade so groß sein, daß sie zusammen mit den Schutzdioden auf dem Chip einen ausreichenden Schutz gegen Hochspannungspulse gewährleisten. Zu große Widerstände erhöhen das Rauschen und die Signalverzögerung unnötig. Für diese Messungen wurden die Testchips "Helix-ESD" verwendet. Dieser Chip enthält acht ladungsempfindliche Vorverstärker mit unterschiedlichen Schutzstrukturen an den Eingängen.

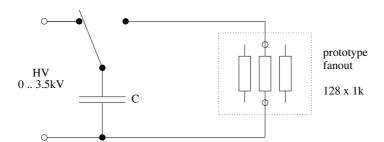

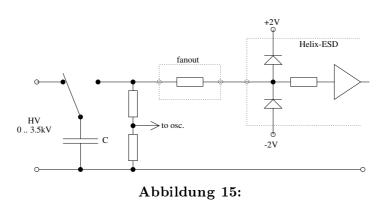

Zur Messung wurde ein Kondensator auf 1kV aufgeladen und über den Keramik-Adapter und die Schutzdioden des Helix-ESD entladen (Abb. 15). Der Keramik-Adapter wurde durch SMD-Widerstände ersetzt, um beliebige Werte testen zu können. Es wurde bereits erwähnt, daß die integrierten Schutzwiderstände den Hochspannungsentladungen nicht standhalten. Bei den Test wurden daher Kanäle ohne diese Widerstände verwendet<sup>2</sup>. Zum Schutz des Chips während der Entladungen waren Widerstände von  $450\,\Omega$  oder größer notwendig. Bei kleineren Werten wurde der jeweilige Kanal oder schlimmstenfalls der gesamte Chip zerstört. Aufgrund dieser Messungen wurden bei den folgenden Dünnfilmkeramik-Adaptern die Widerstände auf  $600\,\Omega$  festgelegt.

<sup>&</sup>lt;sup>2</sup>Bei zwei Kanälen des Helix-ESD ist es möglich, diese Widerstände mit einem Bonddraht zu überbrücken.

## 3.3 Adapter in Dünnfilmtechnik

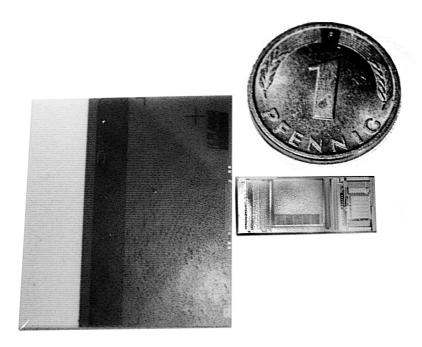

Abbildung 16: Keramikadapter in Dünnfilmtechnik mit Helix128S-2 (rechts).

Die Prototypen eines Keramik-Adapters in Dünnfilmtechnologie wurden von einer Firma<sup>3</sup> hergestellt, die sich auf die Produktion von Mikro-Sensoren spezialisiert hat.

Das Keramik-Substrat ("Rubalit 710") besteht zu 99,96% aus  $Al_2O_3$  [End97]. Die Widerstände (einer pro Kanal) werden aus NiCr hergestellt. Diese Legierung wird aus einem NiCr-Target "gesputtert". Man erreicht damit bei  $1\,\mu\mathrm{m}$  Schichtdicke einen Flächenwiderstand<sup>4</sup> von  $0,16\,\Omega$ . Die Leiterbahnen entstehen durch Strukturierung einer ebenfalls aufgesputterten Aluminiumbeschichtung. Ein fotostrukturierbarer Lötstopplack ("LSF60") dient schließlich als Schutz gegen Korrosion und mechanische Beschädigung.

Die genannten Materialien wurden mit dem Ziel einer einfachen technologischen Beherrschbarkeit und Kompatibilität zu Folgeprozessen (Bonden, Z-Bonden) gewählt. Die einzelnen Schichten (Widerstände, Leiterbahnen und Lötstopplack) werden dabei jeweils in den Schritten Beschichtung, Belichtung, Entwicklung und Ätzen hergestellt. Ungewöhnlich für diesen Prozeß waren die großen Abmessungen des Adapters (26 mm × 22 mm). Da ein Defekt ein ganzes Bauteil unbrauchbar machen kann, hängt die Ausbeute von der Gesamtfläche eines Bauteils ab. Um Fehler frühzeitig erkennen und eventuell korrigieren zu können, wurde jeder Bearbeitungsschritt unter dem Mikroskop optisch kontrolliert.

Da erst wenige Tage vor Abgabe dieser Arbeit zwei Musterexemplare der Keramik-Adapter in Dünnfilmtechnik zur Verfügung standen (Abb. 16), konnten nur noch vorläufige Messungen

<sup>&</sup>lt;sup>3</sup>HL-Planar Technik GmbH, Dortmund

$<sup>^4</sup>$ Der Widerstand einer Leiterbahn hängt vom Material, dem Querschnitt und der Länge der Bahn ab. Der Querschnitt Aist das Produkt aus der Breite b und der vorgegebenen Schichtdicke. Also ist  $R \sim \frac{l}{A} \sim \frac{l}{b}$ . Das bedeutet, daß der Flächenwiderstand  $R_{\square}$  eines quadratisches Teilstücks (l=b) einer Leiterbahn nicht von der Kantenlänge abhängt und daher in  $\frac{\Omega}{\square}$  angegeben werden kann.

durchgeführt werden. Bei den untersuchten Mustern handelt es sich um erste Exemplare, bei denen Bondpads zu klein gefertigt worden sind. Außerdem überdeckt ein Lötstopplack nicht nur Marker zur optischen Kontrolle der Ausrichtung bei der Bestückung, sondern grenzt auch zu nahe an die Anschlußflächen. Dadurch liegt die Bondfläche in einer Vertiefung, sodaß der Bondvorgang behindert wird. Diese Exemplare konnten aus diesen Gründen zur Bestückung der Helix-Leiterplatten nicht verwendet werden.

Die Messung der Widerstände ergab Werte von  $(601\pm1)\,\Omega$ ). Bei der Belastung durch einen Gleichstrom verfärbt sich ab 9,5 W der Lötstopplack über dem Widerstand. Bei höheren Belastungen beginnt der Lötstopplack zu schmelzen und der Widerstand liegt blank. Bei etwa 20 W beginnt der Widerstand zu glühen und brennt schließlich durch.

Bei der durchgeführten Gleichstrommessung kann der Widerstand über das Keramik-Substrat sehr gut Wärme an die Umgebung abführen. Unklar ist der Einfluß von Langzeiteffekten auf die Widerstände, denn bei hohen Stromdichten kann es zur Elektronen-Migration kommen, das heißt die leitende Schicht wird allmählich abgetragen. Das Verhalten bei wiederholten kurzen Hochspannungsimpulsen über lange Zeit entsprechend den Überschlägen in MSGCs bleibt daher noch zu untersuchen.

# 4 Differentieller Komparator

Die vorverstärkten Signale der MSGC sollen zur Erzeugung eines Triggersignals mit einer einstellbaren Referenzspannung verglichen werden. Diese Aufgabe übernimmt der im Rahmen dieser Arbeit entwickelte Komparator, der in der aktuellen Version des Auslesechips Helix128S-2 verwendet wird. Auf die Integration der Komparatoren in den Helix128S-2 wird später in Kapitel 6 eingegangen. Für den Einsatz im Triggerpfad 1.6 des Helix-Chips werden an die Komparatoren die folgenden Anforderungen gestellt:

- Das Signal eines minimal ionisierenden Teilchens (MIP, s.S. 14) soll mit ausreichender Effizienz erkannt werden. D.h.:

- Die Auflösung soll so gut sein wie möglich.

- Die Offsetvariation verschiedener Komparatoren soll kleiner sein als 10mV.

- entsprechend der Pulsform des Vorverstärkers muß der Komparator Anstiegsgeschwindigkeiten von wenigstens  $1\frac{mV}{ns}$  verarbeiten können.

- Offsetschwankungen des Vorverstärkers müssen kompensiert werden.

Weitere Randbedingungen sind möglichst geringer Flächenbedarf und die Vermeidung von Störungen, die in den Analogteil des Chips dringen könnten.

#### 4.1 Differenzverstärker

#### 4.1.1 Funktionsweise

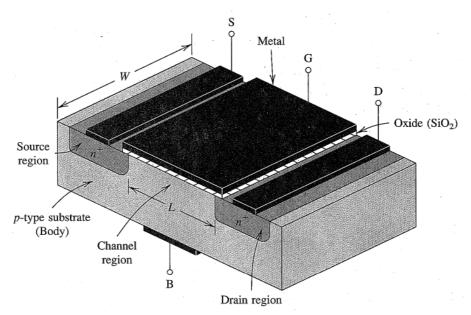

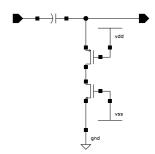

Die Schaltungen eines Mikrochips sind aus Widerständen, Kondensatoren und vor allem Transistoren aufgebaut. Als Transistoren werden Feldeffekttransistoren (FET) verwendet (Abb. 17, 18 und 19). Die Steuerelektrode des FET ist das Gate (G). Mit der Steuerspannung  $U_{\rm GS}$  läßt sich der Widerstand zwischen Drain (D) und Source (S) steuern. Der vierte Anschluß eines FET ist das Substrat (B, wie "bulk"). Wenn in Schaltbildern das Substrat eines Transistors nicht eingezeichnet ist, so ist es bei n-Kanal-FETs mit der negativen und bei p-Kanal-FETs mit der positiven Betriebsspannung verbunden.

Genaugenommen handelt es sich um Sperrschicht-CMOS-FETs (enhancement channel type metal oxyd silizium - field effect transistors). Diese Variante des Feldeffekttransistors ist selbstsperrend, das heißt bei  $U_{\rm GS}=0$  fließt kein Strom zwischen Drain und Source. Der Strom von Drain nach Source wird im folgenden  $I_{\rm D}$  genannt. Als Einführung in die Eigenschaften von Feldeffektransistoren und andere Grundlagen der Elektronik sei das Buch "Halbleiter-Schaltungstechnik" [TS93] empfohlen.

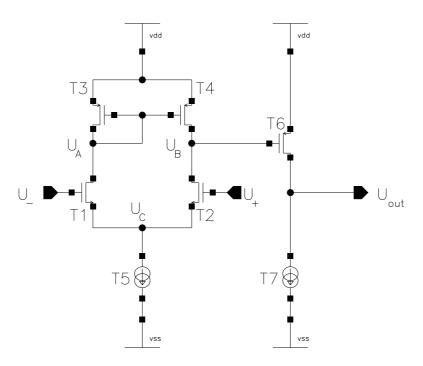

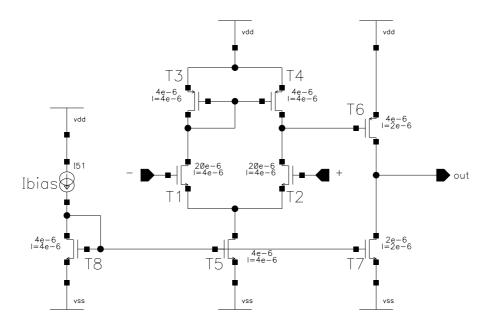

Abbildung 21 zeigt die Schaltung des Differenzverstärkers, der als Komparator verwendet werden soll. Die Versorgungsspannungen sind  $V_{\rm ss}=-2{\rm V}$  und  $V_{\rm dd}=+2{\rm V}$ . Transistor  ${\rm T}_5$  arbeitet als Konstantstromquelle. Dadurch bleibt die Summe der Ströme durch  ${\rm T}_1$  und  ${\rm T}_2$  konstant. Im Ruhezustand sind die beiden Eingangspannungen  $U_{\ominus}$  und  $U_{\oplus}$  gleich groß. Dann teilt sich aus Symmetriegründen der Konstantstrom auf die beiden Zweige auf:

$$I_{\mathrm{D}_{1}} = I_{\mathrm{D}_{2}} = I_{\mathrm{D}_{3}} = I_{\mathrm{D}_{4}} = \frac{1}{2}I_{\mathrm{D}_{5}}$$

${\bf Abbildung\ 17:\ Struktur\ eines\ n\text{-}Kanal\text{-}Sperrschicht\text{-}Feldeffekttransistors\ [SS91]}$

Abbildung 18: n-Kanal MOSFET

Abbildung 19: p-Kanal MOSFET

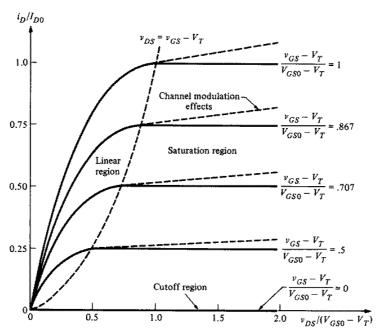

**Abbildung 20:** Ausgangskennlinienfeld eines n-Kanal-Sperrschicht-Feldeffekttransistors [AH87]

Abbildung 21: Zweistufiger Differenzverstärker

An Transistor  $T_3$  sind Drain und Gate miteinander verbunden. Ein solcher "selbsteuernder" Transistor verhält sich im Bereich der Sättigung wegen  $R_{\rm DS} = \frac{U_{\rm DS}}{I_{\rm D}}$  und  $U_{\rm GS} \sim I_{\rm D}$  wie ein ohmscher Widerstand.

Die Spannungen  $U_{\rm A}=V_{\rm dd}-U_{\rm DS_3}=V_{\rm dd}-U_{\rm DS_4}=U_{\rm B}$  bleiben konstant, solange der Strom durch jeden der beiden Zweige konstant bleibt. Daran ändert sich auch nichts, wenn sich beide Eingangsspannungen um den gleichen Wert verändern (Gleichtaktaussteuerung). Wird dagegen z.B.  $U_{\oplus}>U_{\ominus}$ , dann ändert sich die Stromaufteilung im Differenzverstärker.  $I_{\rm D_2}$  nimmt zu und  $I_{\rm D_1}$  nimmt ab, wobei die Summe nach wie vor  $I_{\rm D_5}$  bleibt. Also ist

$$\Delta I_{\rm D_1} = -\Delta I_{\rm D_2}$$

Damit sinkt  $I_{\rm D_3} \sim U_{\rm A} = U_{\rm GS_3} = U_{\rm GS_4}$ . Für Transistor T<sub>4</sub> gilt  $R_{\rm DS_4} \sim \frac{U_{\rm DS_3}}{I_{\rm D_4}}$ . Wenn  $U_{\rm GS_4}$  sinkt, vergrößert sich  $R_{\rm DS_4}$  und  $U_{\rm B} = V_{\rm dd} - U_{\rm DS_4}$  sinkt.

Der Differenzstufe folgt ein einfacher Inverter.  $T_7$  ist eine weitere Konstantstromquelle. Sinkt  $U_B$ , verringert sich der Widerstand des p-Kanal-FET  $T_6$ , was zur Erhöhung der Ausgangsspannung  $U_{\text{out}}$  führt.

#### 4.1.2 Schaltungsentwurf

Nachdem der Schaltplan festgelegt ist, besteht das Hauptproblem darin, eine gute Dimensionierung der Bauteile zu finden. Beim Design eines CMOS-Transistors hat man zwei Freiheitsgrade: Länge und Weite (Abb. 17).

4.1 Differenzverstärker 25

Sie geben dem Transistor seine wesentlichen Eigenschaften [RG86]:

$$i_{\rm D} \sim \frac{W}{L} \cdot U_{\rm GS}$$

und damit  $g_m = \frac{\partial i_{\rm D}}{\partial U_{\rm GS}} \sim \frac{W}{L}$

Folgende Kriterien sind für das Design relevant:

- Der Differenzverstärker soll eine möglichst große Verstärkung erreichen.

- Die differentielle Stufe soll möglichst symmetrisch sein, also  $W_1=W_2, W_3=W_4$  und  $L_1=L_2, L_3=L_4$

- Gleiche Längen für alle Transistoren sorgen dafür, daß korrelierte Fehler in dieser Dimension die Balance nicht stören. Also:  $L_1 = L_2 = L_3 = L_4$ .

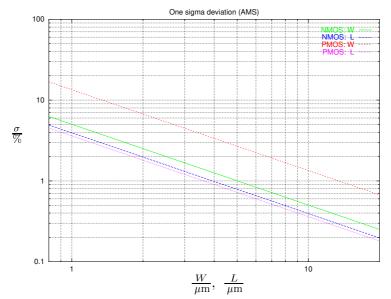

- Um unkorrelierte Fehler (s. Abb. unten) kleinzuhalten, sollten  $W_i$  und  $L_i$  möglichst groß gewählt werden.

**Abbildung 22:** Schwankung der Prozessparamter W und L [WM94]. Die Kurven stehen (von oben nach unten) für die Weite eines p-MOS-, Weite eines n-MOS-, Länge eines n-MOS und Länge eines p-MOS-Transistors.

- Allerdings machen große Dimensionen den Transistor langsamer, bzw. der Transistor benötigt mehr Strom, da größere Kapazitäten geladen werden müssen.,

- Die Transistoren sollen in Sättigung betrieben werden.

- Für die zweite Stufe sind noch weitere Zusammenhänge zu berücksichtigen:

- T<sub>5</sub> und T<sub>7</sub> spiegeln den Strom durch T<sub>8</sub> entsprechend der Verhältnisse ihrer  $(\frac{W}{L})$ . Das gleiche gilt für  $T_3$ ,  $T_4$  und  $T_6$ , die das gleiche Gatepotential besitzen:

$$I_6 = I_4 \frac{\left(\frac{W}{L}\right)_6}{\left(\frac{W}{L}\right)_4}, \qquad I_7 = I_5 \frac{\left(\frac{W}{L}\right)_7}{\left(\frac{W}{L}\right)_5}$$

- Für ausgeglichene Bedingungen soll  $I_6 = I_7$  sein, also:

$$I_4 \frac{\left(\frac{W}{L}\right)_6}{\left(\frac{W}{L}\right)_4} = I_5 \frac{\left(\frac{W}{L}\right)_7}{\left(\frac{W}{L}\right)_5}$$

- Weil sich der Strom durch  $T_5$  auf die beiden Zweige aufteilt, ist  $I_5=2I_4$ . Also:

$$\frac{\left(\frac{W}{L}\right)_6}{\left(\frac{W}{L}\right)_4} = 2\frac{\left(\frac{W}{L}\right)_7}{\left(\frac{W}{L}\right)_5}$$

• Durch T<sub>7</sub> muß genug Strom fließen können, um die Kapazitäten der nachgeschalteten Bauelemente in der geforderten Anstiegszeit laden zu können:

$$I_7 = C \frac{\Delta U}{\Delta T} = 0, 1 \text{pF} \cdot \frac{4 \text{V}}{10 \text{ns}} = 40 \mu \text{A}$$

Dabei setzt sich C zusammen aus den Gatekapazitäten der vier angesteuerten Transistoren des nachfolgenden Gatters und der Leitungskapazität<sup>5</sup>  $C_{\text{line}}$ , die der parasitären Simulation entnommen wurde:  $C = \sum W_i L_i C_{g_{\text{ox}}} + C_{\text{line}} = 39,9 \, \mu\text{m} \cdot 0,8 \, \mu\text{m} \cdot 2,2 \frac{\text{fF}}{\mu\text{m}^2} + 20,8 \, \text{fF} = 90 \, \text{fF} \approx 0,1 \, \text{pF}$

Die aufgezählten Kriterien müssen nun in die Dimensionierung der Längen und Weiten der Transistoren umgesetzt werden. Denkbare Dimensionierungen wurden daher durch eine Schaltungssimulation<sup>6</sup> überprüft und durch iterative Anpassung der Parameter verbessert.

Es kristallisierten sich drei grundverschiedene Arten der Dimensionierung heraus:

- Transistoren mit minimaler Länge  $(0, 8 \,\mu\text{m})$  und einer Weite von einigen  $\mu\text{m}$ . Sie liefern eine sehr hohe Empfindlichkeit und Geschwindigkeit bei minimalem Strombedarf. Diese Möglichkeit scheidet aber leider wegen der zu erwartenden Produktionstoleranzen aus.

- Transistoren mit einigen  $\mu$ m Länge und einer Weite in der Größenordnung von  $100 \,\mu$ m. Hier liegt man mit Rauschen und Toleranzen auf der sicheren Seite. Um die benötigte Geschwindigkeit zu erreichen, ist aber die Stromaufnahme zu hoch.

- Transistoren mit Weite und Länge von einigen  $\mu$ m. Eine solche Kombination wird im folgenden behandelt.

#### 4.1.3 Großsignalmodell

Im Abschnitt 4.1.2 wurden bereits Schaltungssimulationen angesprochen. Jeder Simulation liegt ein Modell zugrunde, mit dem das Verhalten der Bauteile beschrieben wird. Mit dem Großsignalmodell können Transistoren aufgrund ihrer Geometrie und der Prozessparameter

$<sup>^5</sup>$ Parasitäre Kapazitäten können erst nach dem Entwurf eines Layouts berechnet werden und müssen daher zunächst abgeschätzt werden.

<sup>&</sup>lt;sup>6</sup> Zur Schaltungssimulation wurde die Software SpectreS verwendet. SpectreS ähnelt in der Funktionalität dem bekannten Spice, ist aber Teil der Software Cadence, die im ASIC-Labor zum Entwurf, Layout und Simulation von ASICs verwendet wird.

**Abbildung 23:** Der fertige Schaltplan des 2stufigen Komparators. Die Zahlen an den Transistoren geben Weite und Länge an, z.B.  $T_1$ :  $W = 20 \,\mu\text{m}$ ,  $L = 4 \,\mu\text{m}$ .

beschrieben werden. Abbildung 20 zeigt qualitativ das Ausgangskennlinienfeld eines Feldeffekttransistors. Für verschiedene Arbeitsbereiche des Transistors können unterschiedliche Näherungen zur Berechnung von  $I_{\rm D}(W,L,U_{\rm GS},U_{\rm DS},\dots)$  verwendet werden. Mit dem Großsignalmodell kann das zeitliche Verhalten einer Schaltung z.B. mit einem bestimmten Eingangssignal simuliert werden. Eine andere Möglichkeit ist es, für jeden Transistor die Verstärkungsfaktoren, Ruheströme und Spannungen und Kapazitäten zwischen den einzelnen Anschlüssen für den jeweiligen Arbeitspunkt zu berechnen. Diese Größen werden für Berechnungen mit dem Kleinsignalmodell (nächster Abschnitt) benötigt. Tabelle 1 enthält die für diesen Zweck berechneten Werte.

#### 4.1.4 Kleinsignalmodell

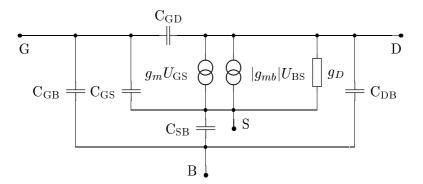

Das Kleinsignalmodell ist eine Näherung erster Ordnung und beschreibt die Änderungen um den Arbeitspunkt der Schaltung. Berücksichtigt man alle Eigenschaften eines Feldeffektransistors, erhält man das Ersatzschaltbild Abbildung 24. Die Stromquelle in der Mitte liefert einen Strom, der mit dem Verstärkungsfaktor  $g_m$  von der Steuerspannung  $U_{\rm GS}$  abhängt. Das Potential des Substrats beeinflußt genauso wie das Gatepotential das elektrische Feld zwischen Source und Drain und damit den Kanal der Ladungsträger. Eine zweite Stromquelle hängt daher von der Spannung zwischen Bulk und Source ab. Außerdem besitzt der Kanal des Transistors einen Widerstand  $R_{\rm D}$ . Es ist rechentechnisch günstiger, mit dem Leitwert  $g_{\rm D}=R_{\rm D}^{-1}$  zu arbeiten. Schließlich sind die parasitären Kapazitäten zwischen Gate, Source, Drain und Bulk zu berücksichtigen.

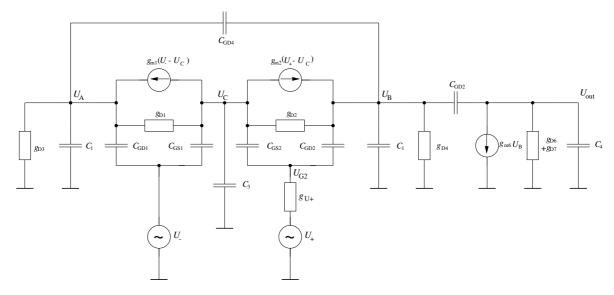

Um das Kleinsignalmodell des Differenzverstärkers zu erhalten, wird jeder Transistor der Schaltung durch sein Kleinsignalmodell ersetzt (Abb. 25). In der Mitte liegen die Stromquellen, Leitfähigkeiten und Gatekapazitäten der beiden Eingangstransistoren  $T_1$  und  $T_2$ . Am

|                | $\frac{W}{\mu \text{m}}$ | $\frac{L}{\mu m}$ | $\frac{g_{\rm m}}{\mu {\rm A/V}}$ | $\frac{g_{\mathrm{D}}}{\mu\mathrm{A/V}}$ | $\frac{g_{\mathrm{mB}}}{\mu \mathrm{A/V}}$ | $\frac{I_{\mathrm{DS}}}{\mu \mathrm{A}}$ |

|----------------|--------------------------|-------------------|-----------------------------------|------------------------------------------|--------------------------------------------|------------------------------------------|

| $T_1$          | 20                       | 4                 | 76.8                              | 0.253                                    | 19.4                                       | 16.2                                     |

| $T_2$          | 4                        | 4                 | 75.0                              | 0.164                                    | 18.9                                       | 15.3                                     |

| $T_3$          | 4                        | 4                 | 32.0                              | 0.519                                    | 5.95                                       | -32.4                                    |

| $T_4$          | 4                        | 4                 | 23.8                              | 9.54                                     | 4.61                                       | -30.6                                    |

| $T_5$          | 4                        | 4                 | 24.0                              | 92.7                                     | 6.82                                       | 63.0                                     |

| $T_6$          | 4                        | 2                 | 22.1                              | 0.114                                    | 5.06                                       | -4.93                                    |

| $\mathrm{T}_7$ | 2                        | 2                 | 1.13                              | 78.6                                     | 0.253                                      | 4.93                                     |

| $\mathrm{T}_8$ | 4                        | 4                 | 87.9                              | 0.601                                    | 21.5                                       | 100                                      |

|       | $\frac{U_{\mathrm{DS}}}{\mathrm{V}}$ | $\frac{U_{\mathrm{D,sat}}}{\mathrm{V}}$ | $\frac{U_{\mathrm{GS}}}{\mathrm{V}}$ | $\frac{U_{\mathrm{th}}}{\mathrm{V}}$ | $\frac{C_{\mathrm{GD}}}{\mathrm{fF}}$ | $\frac{C_{\mathrm{GS}}}{\mathrm{fF}}$ | $\frac{C_{\mathrm{BD}}}{\mathrm{fF}}$ | $\frac{C_{\mathrm{BS}}}{\mathrm{fF}}$ | $\frac{C_{\mathrm{GB}}}{\mathrm{fF}}$ |

|-------|--------------------------------------|-----------------------------------------|--------------------------------------|--------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| $T_1$ | 0.998                                | 0.325                                   | 1.43                                 | 1.00                                 | 3.0                                   | 55                                    | 0.17                                  | 0.22                                  | 0.60                                  |

| $T_2$ | 2.25                                 | 0.315                                   | 1.417                                | 1.00                                 | 3.0                                   | 55                                    | 0.14                                  | 0.22                                  | 0.60                                  |

| $T_3$ | -2.41                                | -1.402                                  | -2.41                                | -0.728                               | 1.1                                   | 21                                    | 0.25                                  | 0.48                                  | 0.62                                  |

| $T_4$ | -1.16                                | -1.4                                    | -2.41                                | -0.729                               | 12                                    | 18                                    | 0.32                                  | 0.48                                  | 0.62                                  |

| $T_5$ | 0.583                                | 1.298                                   | 2.74                                 | 0.833                                | 13                                    | 13                                    | 10                                    | 12                                    | 0.60                                  |

| $T_6$ | -3.93                                | -0.362                                  | -1.16                                | -0.712                               | 1.1                                   | 11                                    | 0.21                                  | 0.49                                  | 0.32                                  |

| $T_7$ | 0.062                                | 1.115                                   | 2.74                                 | 0.827                                | 2.1                                   | 2.1                                   | 66                                    | 68                                    | 0.30                                  |

| $T_8$ | 2.74                                 | 1.301                                   | 2.74                                 | 0.830                                | 0.99                                  | 17                                    | 6.9                                   | 12                                    | 0.60                                  |

Tabelle 1: Ergebnisse der Großsignalsimulation im Arbeitspunkt des Differenzverstärkers mit den Transistordimensionen W und L. Berechnet wurden der Verstärkungsfaktor  $g_{\rm m}$ , die Leitfähigkeit  $g_{\rm D}$  des Feldeffektkanals, der Verstärkungsfaktor  $g_{\rm mB}$  der Bulk-Source-Spannung, der Drainstrom  $I_{\rm DS}$ , die Spannungen  $U_{\rm DS}$  und  $U_{\rm GS}$  zwischen Gate und Source bzw. Drain, die Grenzspannung für den Sättigungsbereich  $U_{\rm D,sat}$ , die Schwellenspannung  $U_{\rm th}$  und die parasitären Kapazitäten.

Abbildung 24: Das vollständige Kleinsignalmodell eines Feldeffektransistors

Abbildung 25: Kleinsignalmodell der Differenzstufe

Gate von  $T_2$  liegt das Eingangssignal  $U_{\oplus}$  an. Der Ausgangswiderstand eines davorliegenden Verstärkers wird durch die Leitfähigkeit  $g_{U_{\oplus}}$  berücksichtigt. An  $T_1$  liegt die Referenzspannung  $V_{\text{ref}}$  an. Hier kann der Ausgangswiderstand vernachlässigt werden. Durch  $C_1$ ,  $C_2$  und  $C_3$  werden soweit möglich parasitäre Kapazitäten zusammengefaßt:

$$C_{1} = C_{\mathrm{GS}_{3}} + C_{\mathrm{GS}_{3}} + C_{\mathrm{GS}_{3}} + C_{\mathrm{A}}$$

$C_{2} = C_{\mathrm{GS}_{6}} + C_{\mathrm{B}}$

$C_{3} = C_{\mathrm{GD}_{7}} + C_{\mathrm{Out}}$

$C_{\mathrm{A}},~C_{\mathrm{B}},~C_{\mathrm{Out}}$  sind die parasitären Leitungskapazitäten der jeweiligen Netzwerkknoten.

Nach der Knotenregel für Ströme lassen sich aus dem Ersatzschaltbild fünf Gleichungen ableiten:

<sup>&</sup>lt;sup>7</sup>Die parasitären Leitungskapazitäten stehen erst nach Entwurf eines Layouts fest.

Dieses Gleichungssystem kann analytisch gelöst werden. Die exakte Lösung ist jedoch genauso lang wie unübersichtlich. Durch Einsetzen der Werte aus der Großsignalsimulation erhält man sinnvolle Aussagen über das Verhalten des Differenzverstärkers.

Für niederfrequente Eingangssignale ist  $\omega \approx 0$ . Damit fallen alle Terme weg, die parasitäre Kapazitäten enthalten.

$$\begin{array}{lcl} U_{\rm B} & = & -\frac{1}{2} \frac{g_{m_1}}{g_{d_1} + g_{d_3}} & (U_{\oplus} - U_{\ominus}) \\ & = & -180 & (U_{\oplus} - U_{\ominus}) \end{array}$$

$$\begin{array}{lcl} U_{\rm out} & = & -\frac{g_{m_6}}{g_{d_6} + g_{d_7}} & U_{\rm B} \\ & = & 6840 & (U_{\oplus} - U_{\ominus}) \end{array}$$

## 4.2 AC-Kopplung

Die Ausgänge des Helix-Vorverstärkers sind mit einem Offset behaftet, der von Kanal zu Kanal variiert. Diese Variation liegt in der Größenordnung des Nutzsignals. Da die Referenzspannung der Komparatoren für alle Kanäle gemeinsam sein soll, muß diese Offsetvariation beseitigt werden. Dies kann u.a. durch eine AC-Kopplung erfolgen. Dafür gibt es zwei gebräuchliche Möglichkeiten:

• Eine kapazitive Kopplung ist für Gleichstromanteile undurchlässig. Mit einem Schalter gegen Masse wird der Arbeitspunkt auf der rechten Seite festgelegt. Der Schalter wird periodisch zu einem Zeitpunkt geschlossen, wenn das Signal nicht ausgewertet wird. Ist der folgende Eingang hochohmig (MOSFET-Gate) muß der Schalter nur sehr selten betätigt werden, da bei geöffnetem Schalter kein Gleichstrom fließen kann.

• Ein CR-Glied (Hochpaß) filtert tiefe Frequenzen aus dem Signal heraus. Die Zeitkonstante  $\tau=RC$  muß hinreichend groß sein um das durchgehende Signal nicht zu beeinträchtigen. Es soll nur der Gleichspannungsanteil ausgeschlossen werden.

Die Realisierung der benötigten Bauelemente in einem integrierten Schaltkreis geschieht wie folgt:

- Kondensatoren implementiert man durch Überlappung leitfähiger Lagen mit geringem Abstand. Im verwendeten Prozeß bieten sich hierfür zwei Lagen aus poly-kristallinem Silizum an. Die spezifische Kapazität von Überlappungen dieser beiden Lagen ist  $C_{\rm POX}=1,77\frac{\rm fF}{\mu{\rm m}^2}$ . Damit können Kondensatoren in der Größenordnung von 100 fF bis 10 pF gebaut werden. Kleinere Kapazitäten werden vergleichbar mit parasitären Effekten und größere Werte haben einen zu üppigen Platzbedarf.

- Ein Schalter (transmission gate) wird durch zwei Transistoren gebildet. Die paarweise Verwendung jeweils eines pund n-Kanal-Transistors soll die Ladungsinjektion kompensieren. Nachteil der Schaltung ist eine zusätzliche differentielle Steuerleitung. Beim Schalten selbst sind natürlich auch Störungen zu erwarten. Außerdem fließen durch die gesperrten Transistoren immer auch Leckströme, sodaß die Schaltung letztendlich dem nachstehenden CR-Glied nahekommt.

- Ohmsche Widerstände werden durch lange Leiterbahnen in einer möglichst hochohmigen Lage gebildet. Eine der beiden Lagen aus poly-kristallinem Silizium des verwendeten Prozesses (Poly-2) weist mit  $R_{\text{poly2}} = 27\frac{\Omega}{\Box}$  den größten Flächenwiderstand auf. Die benötigten Widerstände liegen aber in der Größenordnung von 1 M $\Omega$ . Ein Poly-2-Widerstand hätte dann bei minimaler Breite von 1,6  $\mu$ m eine Länge von  $l = \frac{R}{R_{\text{poly2}}} = 37\,\text{mm}$ . Dies ist bei 128 Kanälen völlig ausgeschlossen.

- Eine andere Möglichkeit einen Widerstand zu realisieren ist es, den Leckstrom gesperrter Transistoren auszunutzen. Von dieser Anordnung darf man kein lineares Verhalten erwarten. Ist die Zeitkonstante jedoch viel größer als die Zeitskala des Nutzsignals, spielt dies keine Rolle. Nach Abwägung der genannten Vor- und Nachteile verschiedener Möglichkeiten fiel die Wahl für den Einsatz im Helix128V2 auf die Implementierung der Widerstände durch Transistoren.

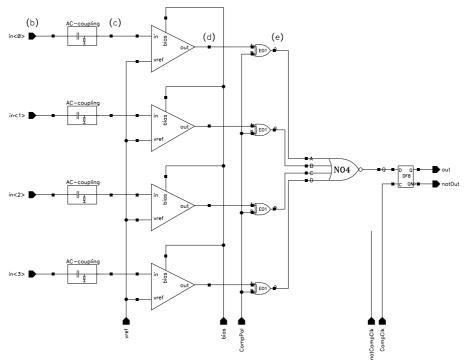

## 4.3 4fach-Oder und D-Flip-Flop

Nachdem das Eingangssignal durch den Komparator mit der Referenzspannung verglichen wurde, steht ein digitales Signal zur Verfügung. Dieses Signal ändert seinen Pegel (bis auf eine Verzögerung) zeitgleich mit dem Über- oder Unterschreiten der Referenzspannung. Die Schaltung soll aber lediglich anzeigen, ob zum Zeitpunkt der steigenden Flanke der Komparator-Clock (CompClk) die Eingangsspannung größer oder kleiner ist als die Referenz. Das Ausgangssignal soll sich dabei nur einmal pro Taktzyklus zu einem definierten Zeitpunkt ändern können.

Dieses "Testen und Halten" eines digitalen Signals erreicht man durch den Einsatz eines D-Flip-Flops. Es bot sich an, dafür die Standardzelle "E08" von AMS zu verwenden. Standardzellen haben den Vorteil, daß ihr Layout schon existiert und getestet ist.

Das Konzept des "First-Level-Triggers" sieht vor, daß jeweils vier Streifen einer MSGC mit sich selbst und den vier Streifen der darüberliegenden MSGC oder-verknüpft werden. Die Kanäle einer MSGC werden dabei gleich auf dem Helix-Chip oder-verknüpft, was 96 Leitungen und Bond-Pads einspart. Diese Verknüpfung geschieht wiederum durch eine AMS-Standardzelle (N04). Genaugenommen handelt es sich dabei um ein Nicht-Oder. Dies ist bei der nachfolgenden Elektronik zu beachten, denn die Veroderung von jeweils zwei Kanalgruppen (à vier Kanälen) übereinanderliegender MSGCs soll durch die Parallelschaltung der Triggerausgänge erfolgen. Dazu werden die Triggerausgänge als Treibertransistoren mit offenem Drain-Anschluß ausgeführt.

Führt man erst das Nicht-Oder durch und schließt danach das Flip-Flop an, spart man drei von 4 Flip-Flops.

**Abbildung 26:** Eine Vierergruppe Komparatoren mit AC-Kopplung, 4fach-Oder und Flip-Flop

Das Nicht-Oder selbst funktioniert nur, solange positiv-aktive<sup>8</sup> Signale verwendet werden. Für negative Logik (wie bei der MSGC mit Anodenauslese<sup>9</sup>) wird das Oder zum Und! Dem könnte man mit der Verwendung eines Und Gatters anstelle des Oders begegnen. Zielsetzung ist aber ein Chip, der universell für beide Signalpolaritäten einsetzbar ist. Eine einfache Lösung ist ein zusätzliches Exklusiv-Oder (E01). Das Ausgangssignal wird mit dem Steuerpegel  $V_{\rm pol}$  exklusiv verodert. Mit anderen Worten: Ist  $V_{\rm pol}=0$ , wird das Signal nicht verändert. Ist  $V_{\rm pol}=1$ , wird es invertiert.

Die genannten Komponenten ergeben nun die vollstände Schaltung einer Vierergruppe von

$<sup>^8</sup>$ Positiv-aktive Logik bedeutet, daß eine logische "1" der positiven Betriebspannung (+2V) entspricht und eine logische "0" der negativen (-2V). Bei negativ-aktiver Logik verhält es sich genau umgekehrt.

<sup>&</sup>lt;sup>9</sup>Im Falle der Anodenauslese werden Elektronen, die in die Anode eintreten, vom Verstärker als ein Impuls negativer Spannung registriert

4.4 Layout 33

Komparatoren (Abb. 26). Das Signal CompClk soll, um Übersprechen zu vermeiden, wie alle Clocks differentiell auf Platine und Chip geführt werden. Die negierte "notCompClk" wird nicht zur Ansteuerung von Eingängen verwendet, sondern wird parallel zur CompClk-Leitung verlegt, um Störungen zu kompensieren. Eine identische kapazitive Belastung der notCompClk, entsprechend der Gatekapazitäten die an CompClk liegen, kann durch entsprechende Ersatzkondensatoren erreicht werden. Hierauf wurde verzichtet, da die parasitären Kapazitäten der Leitungen selbst größer sind, als die Belastung durch die angesteuerten Eingänge.

### 4.4 Layout

Das Layout muß noch mehr als der Schaltplan in Hinblick auf den verwendeten Produktionsprozess erstellt werden. Der Helix-Chip wird in einem  $0,8\,\mu\text{m}$ -CMOS-Prozeß von AMS $^{10}$  gefertigt , der für analoges Design geeignet ist. In diesem Prozeß stehen für Verbindungen zwei Lagen Metall und zwei Lagen poly-kristallines Silizium ("Poly-1" und "Poly-2") zur Verfügung. Seinen Namen bezieht der Prozeß von der minimalen Breite der Poly-1-Lage, die als Gate der Feldeffekttransistoren eingesetzt wird und damit deren minimale Länge auf  $0,8\,\mu\text{m}$  festlegt. Die minimalen Strukturen in anderen Lagen sind größer als  $0,8\,\mu\text{m}$  und müssen den "Design Rules" des Prozesses entnommen werden.

Die wichtigste Vorgabe für das Layout ist die Kanalbreite des Helix-Chips von  $41,4\,\mu\text{m}$ . Diesen Platz teilen sich die Komparatoren mit Abschirmstrukturen und den durchgereichten Analogleitungen vom Vorverstärker zur Pipeline. So bleibt eine nutzbare Kanalbreite von  $33\,\mu\text{m}$  übrig. Die Transistoren  $T_1$  und  $T_2$  bestehen aus jeweils zwei Teiltransistoren. Eine symmetrische Anordnung der Teile kompensiert räumliche Gradienten in den Prozeßparametern. Die Teilung selbst reduziert den statistischen Fehler der Gesamttransistoren. Von der wünschenswerten vollsymmetrischen Anordnung wie sie in vielen Fachbüchern vorgeschlagen wird [AH87], wurde wegen Platzmangel etwas abgewichen (Abb. 27).

Um zu einer guten Flächenausnutzung zu kommen, bot es sich an, vier Kanäle mit AC-Kopplung, Differenzstufe, Exklusiv-Oder und gemeinsamen Nicht-Oder und D-Flip-Flop (Schaltplan s. Abb. 26) auch im Layout zu einem kompakten Block zusammenzufassen (Abb. 28): Die analogen Teile AC-Kopplung und Differenzstufe sind für jeden Kanal getrennt von einem Schutzring eingeschlossen. Dieser Ring kontaktiert das Substrat niederohmig mit der negativen Betriebsspannung. So sollen Störungen in beiden Richtungen unterdrückt werden. Die sechs Standardzellen liegen aneinandergereiht und sind von einem eigenen Schutzring umgeben. Die digitalen Gatter weisen steile Signalflanken auf und verursachen damit potentiell Störungen. Die Trennung von analogen und digitalen Schaltungsteilen durch Schutzringe und durch getrennt Spannungsversorgungen soll dies entschärfen. Sämtliche für alle Komparatoren gemeinsame Leitungen (Spanungsversorgung, CompClock, Compbias und CompPol) verlaufen senkrecht zu den vier Kanälen über den Block. So lassen sich später auf dem Helix-Chip 32 Blöcke à vier Kanäle zu einer Komparatorenspalte mit 128 Eingangskanälen aneinanderreihen.

$<sup>^{10}</sup>$ Austria Mikro Systeme International AG

$<sup>^{11}</sup>$ Diese Kanalbreite wird durch den Silizium-Vertex-Detektor (SVD) bestimmt, der vom Max-Planck-Institut für Kernphysik in Heidelberg entwickelt wird. Für den Betrieb am SVD werden die HELIX-Chips direkt an den Silizium-Detektor gebondet, wodurch der Kanalabstand von  $41,4\,\mu\mathrm{m}$  erhalten bleibt.