Dissertation submitted to the Combined Faculties for the Natural Sciences and for Mathematics of the Ruperto-Carola Univertsity of Heidelberg, Germany for the degree of Doctor of Natural Sciences

> presented by Dipl. phys. Johannes Fieres born in Fulda, Germany

Oral examination: November, 29, 2006

A METHOD FOR IMAGE CLASSIFICATION USING LOW-PRECISION ANALOG COMPUTING ARRAYS

Referees: Prof. Dr. Karlheinz Meier Prof. Dr. Bernd Jähne

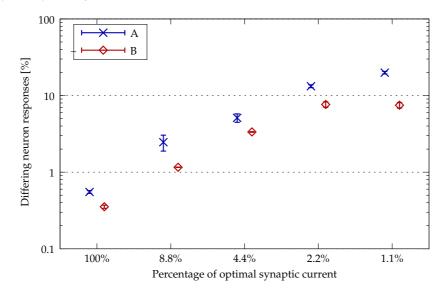

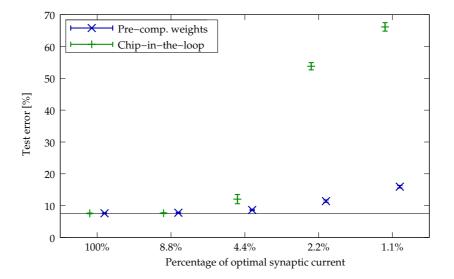

Eine Methode zur Bildklassifikation mit analogen Recheneinheiten beschränkter Genauigkeit

#### Zusammenfassung

Das Rechnen mit analogen integrierten Schaltkreisen kann gegenüber der weit verbreiteten Digitaltechnik einige Vorteile bieten, z.B.: geringerer Fläche- und Stromverbrauch und die Möglichkeit der massiven Parallelisierung. Dabei muss allerdings aufgrund unvermeidlicher Produktionsschwankungen und analogen Rauschens auf die Präzision digitaler Rechner verzichtet werden. Künstliche neuronale Netzwerke sind hinsichtlich einer Realisierung in paralleler, analoger Elektronik gut geeignet. Erstens zeigen sie immanente Parallelität und zweitens können sie sich durch Training an eventuelle Hardwarefehler anpassen. Diese Dissertation untersucht die Implementierbarkeit eines neuronalen Faltungsnetzwerkes zur Bilderkennung auf einem massiv parallelen Niedrigleistungs-Hardwaresystem. Das betrachtete, gemischt analog-digitale, Hardwaremodell realisiert einfache Schwellwertneuronen. Geeignete gradientenfreie Trainingsalgorithmen, die Elemente der Selbstorganisation und des überwachten Lernens verbinden, werden entwickelt und an zwei Testproblemen (handschriftliche Ziffern (MNIST) und Verkehrszeichen) erprobt. In Softwaresimulationen wird das Verhalten der Methode unter verschiedenen Arten von Rechenfehlern untersucht. Durch die Einbeziehung der Hardware in die Trainingsschleife können selbst schwere Rechenfehler, ohne dass diese quantifiziert werden müssen, implizit ausgeglichen werden. Nicht zuletzt werden die entwickelten Netzwerke und Trainingstechniken auf einem existierenden Prototyp-Chip überprüft.

A Method for Image Classification Using Low-Precision Analog Computing Arrays

#### Abstract

Computing with analog micro electronics can offer several advantages over standard digital technology, most notably: Low space and power consumption and massive parallelization. On the other hand, analog computation lacks the exactness of digital calculations due to inevitable device variations introduced during the chip production, but also due to electric noise in the analog signals. Artificial neural networks are well suited for parallel analog implementations, first, because of their inherent parallelity and second, because they can adapt to device imperfections by training. This thesis evaluates the feasibility of implementing a convolutional neural network for image classification on a massively parallel low-power hardware system. A particular, mixed analogdigital, hardware model is considered, featuring simple threshold neurons. Appropriate, gradient-free, training algorithms, combining self-organization and supervised learning are developed and tested with two benchmark problems (MNIST hand-written digits and traffic signs). Software simulations evaluate the methods under various defined computation faults. A model-free closed-loop technique is shown to compensate for rather serious computation errors without the need for explicit error quantification. Last but not least, the developed networks and the training techniques are verified on a real prototype chip.

# Contents

| In | Introduction |                                                              |    |

|----|--------------|--------------------------------------------------------------|----|

| 1  | Bac          | ground                                                       | 7  |

|    | 1.1          | Biological Inspiration                                       |    |

|    |              | 1.1.1 The Nervous System                                     |    |

|    |              | 1.1.2 Rate-Based Neuron Model                                |    |

|    |              | 1.1.3 Activity-Driven Learning Mechanisms                    |    |

|    |              | 1.1.4 Visual Processing in the Brain                         |    |

|    |              | 1.1.5 Biological Implications for Artificial Systems         |    |

|    | 1.2          | Convolutional Neural Networks                                |    |

|    |              | 1.2.1 Overview                                               |    |

|    |              | 1.2.2 Invariant Recognition: From Local to Global Invariance |    |

|    |              | 1.2.3 Neural Implementation of Convolutional Filters         |    |

|    |              | 1.2.4 Hierarchical Sets of Convolution Filters               |    |

|    |              | 1.2.5 Boosting Invariance by Blurring and Sub-sampling .     | 18 |

|    | 1.3          | Training Methods                                             | 20 |

|    |              | 1.3.1 The Curse of Dimensionality                            |    |

|    |              | 1.3.2 Supervised Approaches                                  | 22 |

|    |              | 1.3.3 Un-Supervised Approaches                               |    |

|    |              | 1.3.4 Hybrid Approaches                                      |    |

|    | 1.4          | Analog VLSI Implementations                                  |    |

|    |              | 1.4.1 Motivation                                             |    |

|    |              | 1.4.2 Massively Parallel Computing Arrays                    | 27 |

|    |              | 1.4.3 Recent Array-Based Neuro Chips                         | 28 |

| 2  | Wor          | king Environment                                             | 31 |

|    | 2.1          | Software                                                     |    |

|    |              | 2.1.1 The HElement C++ Library                               |    |

|    |              | 2.1.2 User Interfaces                                        |    |

|    | 2.2          | Hardware                                                     |    |

|    |              | 2.2.1 The HAGEN Chip                                         | 48 |

|    |              | 2.2.2 Distributed Operation of Multiple Chips                |    |

| 3  | A N          | eural Network for Object Recognition                         | 53 |

| -  | 3.1          | Neuron Model                                                 |    |

|    | 3.2          | Topology                                                     |    |

|    | 3.3          | Training                                                     |    |

|    |              | 3.3.1 Hidden Layers: Self-Organization by Clustering         |    |

|              |      | 3.3.2 Output Layer: Supervised Perceptron Learning 56                                       | 8 |  |  |

|--------------|------|---------------------------------------------------------------------------------------------|---|--|--|

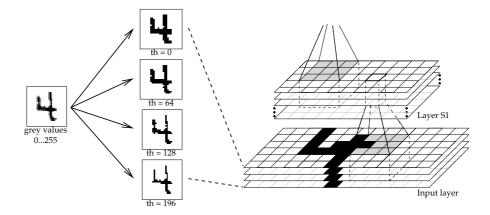

|              | 3.4  | Image Preprocessing 5                                                                       | 9 |  |  |

|              | 3.5  | Meta Parameters 5                                                                           | 9 |  |  |

|              |      | 1. 1.1.1.1.1.1.1.                                                                           |   |  |  |

| 4            |      | ults With Ideal Neurons 6                                                                   |   |  |  |

|              | 4.1  | Two Benchmark Problems   66                                                                 |   |  |  |

|              |      | 4.1.1 Hand-Written Digits                                                                   |   |  |  |

|              | 4.0  | 4.1.2 Traffic Signs                                                                         |   |  |  |

|              | 4.2  | Properties of the Training Method                                                           |   |  |  |

|              |      | 4.2.1 Self-Organization Produces Linear Separability 75                                     |   |  |  |

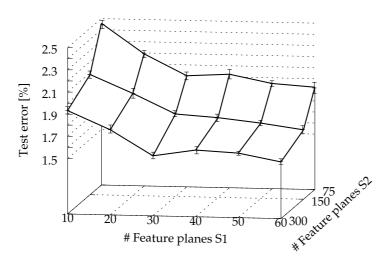

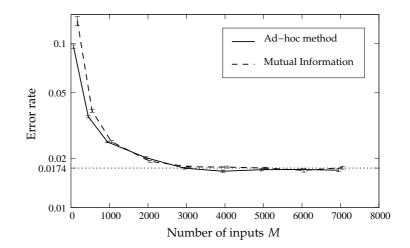

|              |      | 4.2.2 Network Size: The Bigger the Better                                                   |   |  |  |

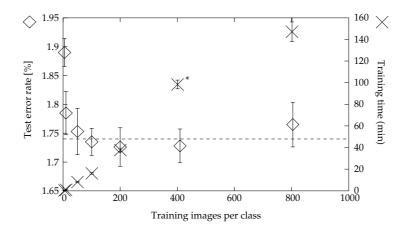

|              |      | 4.2.3 Size of the Training Data Set                                                         |   |  |  |

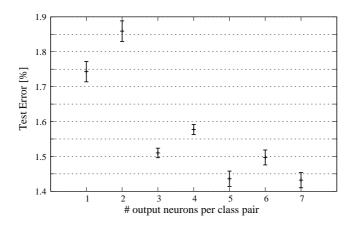

|              | 4.2  | 4.2.4       Scalability       7         Starting Points for Performance Improvement       7 |   |  |  |

|              | 4.3  | 0 1                                                                                         |   |  |  |

|              |      | 0 1                                                                                         |   |  |  |

|              |      | 1 0 0                                                                                       |   |  |  |

|              |      | 4.3.3 Using Larger Networks                                                                 |   |  |  |

|              |      | 4.3.4 Suggestions for Further Optimization                                                  | 9 |  |  |

| 5            | Roh  | ustness Against Computation Faults 8                                                        | 1 |  |  |

| U            | 5.1  | Error Compensation With Chip-in-the-Loop                                                    | - |  |  |

|              | 0.1  | Training                                                                                    | 1 |  |  |

|              |      | 5.1.1 Hidden Layers                                                                         |   |  |  |

|              |      | 5.1.2 Output Layer                                                                          |   |  |  |

|              | 5.2  | Results                                                                                     |   |  |  |

|              | 5.3  | Discussion                                                                                  |   |  |  |

|              | 5.4  | Additional Result: Computing Without Algebra 88                                             | 8 |  |  |

|              |      |                                                                                             | _ |  |  |

| 6            |      | dware Implementation 9                                                                      |   |  |  |

|              | 6.1  | General Approach                                                                            |   |  |  |

|              | 6.2  | Implementation Details                                                                      |   |  |  |

|              |      | 6.2.1 Adjusting the Neuron Model                                                            |   |  |  |

|              |      | 6.2.2 Weight and Threshold Scaling                                                          |   |  |  |

|              |      | 6.2.3 Calibration of Fixed Offsets                                                          |   |  |  |

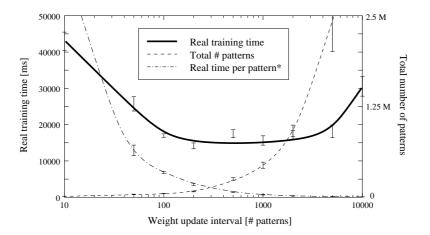

|              | ( )  | 6.2.4 Optimizing Training Speed by Cumulative Weight Update 9                               |   |  |  |

|              | 6.3  | Limitations of the Prototype System                                                         |   |  |  |

|              |      | 6.3.1 Size Limitations of the Chip                                                          |   |  |  |

|              | 6.4  | 6.3.2 Data Handling and Transfer                                                            |   |  |  |

|              | 6.4  | Actual Array Layout                                                                         |   |  |  |

|              | 6.5  | Results                                                                                     |   |  |  |

|              |      | 6.5.1 Optimal Hardware Operation                                                            |   |  |  |

|              |      | 6.5.2 Artificially Degraded Hardware                                                        | 3 |  |  |

| Sı           | ımma | ary and Conclusions 11                                                                      | 9 |  |  |

|              |      |                                                                                             |   |  |  |

| $\mathbf{A}$ | ppen | dix 12                                                                                      | 3 |  |  |

|              |      |                                                                                             | _ |  |  |

| Bibliography |      |                                                                                             | 7 |  |  |

| In           | dex  | 13                                                                                          | 3 |  |  |

Acknowledgments

137

## Introduction

Most of today's data processing tasks are efficiently and economically solved by digital computing machines based on the principles described by John von Neumann in 1945. In fact, the von Neumann architecture has proven to be so universal that, today, digital computers are found in virtually every sector of private and professional life.

The enormous success of digital technology has pushed the pursue of alternative computing approaches away from the public view, although some of them have the potential to offer advantages in various terms. Examples are computing with analog electric signals, or new emerging technologies like DNA computing or quantum computing. Two of the following limitations of digital computers were foreseen already by von Neumann himself<sup>1</sup>:

- **Fault-Intolerance** *"The desired automatic functioning must, of course, assume that it [i.e., the computer] functions faultlessly. ... Any error may vitiate the entire output of the device".* Everybody knows this truth from their recent hard drive crash. But also, for example, during the chip production, manufacturing faults constitute a serious issue: With constantly growing chip areas and circuit densities the probability of defects increases, boosting production costs.

- **Explicit Programming** "The instructions ... must be given to the device in absolutely exhaustive detail. ... [requiring] some code to express the logical and algebraic definition of the problem under consideration". A problem the solution of which cannot be put down in exact instructions cannot be solved by a computer. Modern so-called machine learning techniques can partly account for this problem. However, for many of these methods, von Neumann computers are actually not the optimal substrate. E.g., the parallel execution in artificial neural networks or the multi-valued logic of fuzzy systems can only be simulated with digital processors.

- **Sequential Computing** Algorithms implementable on von Neumann machines are inherently sequential processes. Attempts of simulating truly parallel systems (e.g., hydro-dynamic processes or realistic brain models) on such machines require massive equipment (super computers, cluster computers) and highly sophisticated programming.

- **Power Consumption** The trend to ever higher device densities and clock fequencies goes along with a considerable amount of power dissipation.

<sup>&</sup>lt;sup>1</sup>Quotes taken from his 1945 publications [42]

Besides paying the high electricity bill, cooling down the systems requires more and more effort. Today, for the private user this problem becomes apparent mainly by a higher number of air fans in the PC, but for the maintainer of a super computing center, cooling can in fact constitute a major item of expenses.

Computing with analog electric circuits—in contrast to digital—constitutes one of the alternative techniques mentioned at the beginning. Digital computers operate on abstract symbols represented within a complex electronic machinery. In analog computing circuits, basic laws of physics are exploited for performing calculations. Examples are the Kirchhoff rules for currents or the electrical properties of solid matter boundaries. This difference makes analog micro electronics usually occupy way less silicon area and consume factors less power compared to digital devices performing an equivalent task.

Space and power efficiency enable the design of massively parallel systems where a large arrays of equivalent computing elements are integrated on one micro chip. Such devices are quite different from conventional computers and using them requires to leave common patterns of sequential algorithmics behind for the search of new, truly parallel computing techniques.

When performing computations with analog elements, one of the major properties of digital technology is to be sacrificed: preciseness. Quantities coded by analog signals are inherently limited in precision. An upper limit of accuracy is constituted by noise present in the system, e.g., by thermal fluctuations or undesired electro-dynamical side effects. Another source of uncertainty are random device variations inevitably occurring during the manufacturing process. Although some of the variations can be compensated for by sophisticated circuitry and calibration procedures, the software running on analog devices must be tolerant against imperfect calculations.

Artificial neural networks are a promising application for a massively parallel analog implementation: First, they consist of a large number of identical, parallelly working, computing units which makes the employment of a parallel device a natural approach. Second, artificial neural networks are adaptively trainable for a given task, and can thus be supposed to be able to cope with substrate imperfections and precision limitations. Although the computing paradigm is very different from conventional algorithms, the concept has already proven to be successfully applicable to many problems.

So-called *convolutional* neural networks are a special type of artificial neural networks which are applied for recognizing objects in images. Inspired by biological research on the mammalian visual cortex, such networks implement a hierarchical set of feature extraction stages, allowing to learn object representations invariant of many modes of appearance, e.g., position, scale, deformation, or illumination. Convolutional networks require very large network sizes and are thus considered to benefit especially from a massively parallel implementation.

The by far most popular training method for neural networks, backpropagation, works excellent for networks of small and medium sizes. For very large network scales it becomes more and more impractical due to its high computational complexity. It is necessary to development training meth-

### INTRODUCTION

ods which scale well together with the network size. Self-organization and local learning are promising approaches.

This thesis presents a convolutional neural network application for object recognition and evaluates its feasibility of being implemented in analog hardware. A prototype realization of a massively parallel analog neural network architecture was available for experiments. Topics covered in this thesis include the development of a training method adequate for the network model featured by this particular hardware system, computer simulations of the network behavior under various computation faults, and the investigation of the network when running on the prototype hardware system.

INTRODUCTION

## Organization

The thesis is organized in the following chapters.

**1 Background** The fields relevant for this thesis are shortly reviewed. Preceded by a section about biological foundations of neural networks, the concept of object recognition with convolutional networks is introduced. Previously reported training methods are covered. The chapter is closed by a review of analog hardware implementations of neural networks. p. 7

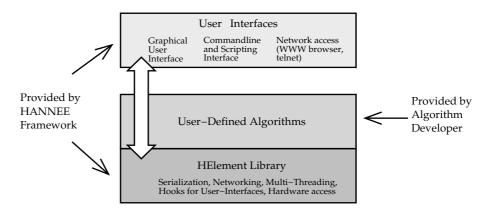

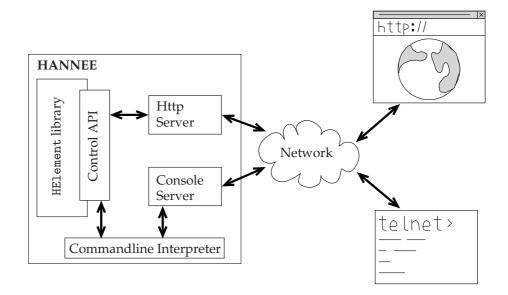

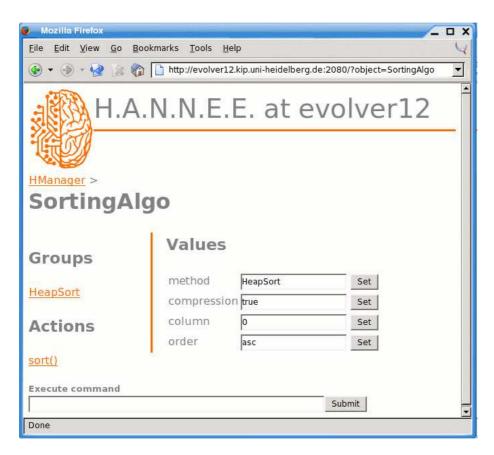

**2 Working Environment** The hardware and software setup used to conduct the experiments are described. Special emphasis is given to the software tools developed as part of this thesis. p. 31

**3 A Neural Network for Object Recognition** This chapter presents the main contribution of this thesis. A convolutional neural network, suited for implementation on the present hardware system is described. Adequate training methods, based on both local self-organization and supervised learning, are developed. p. 53

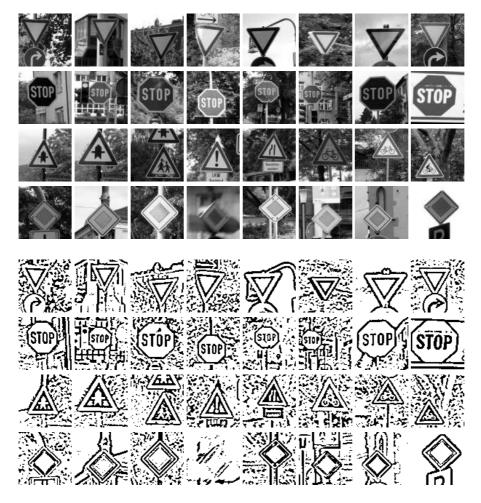

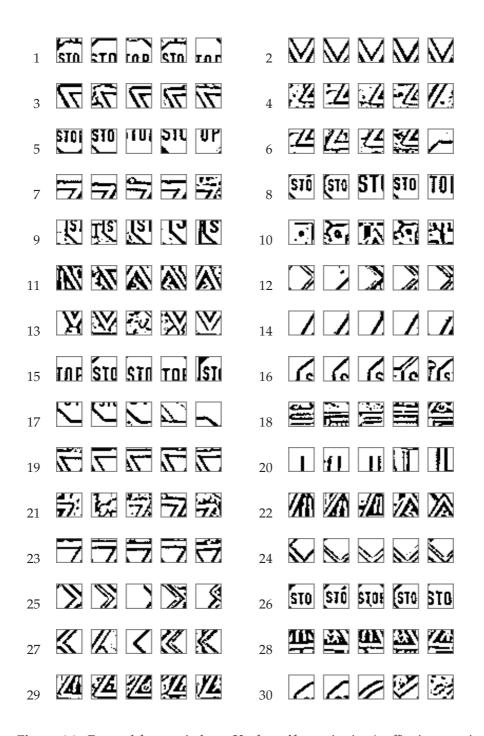

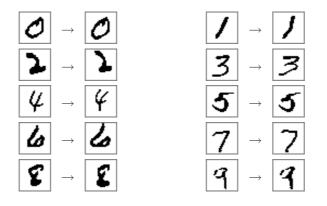

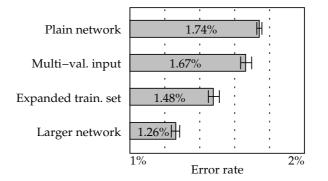

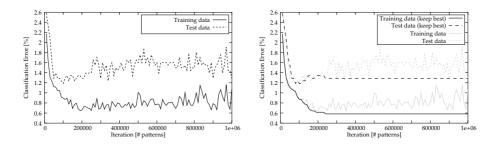

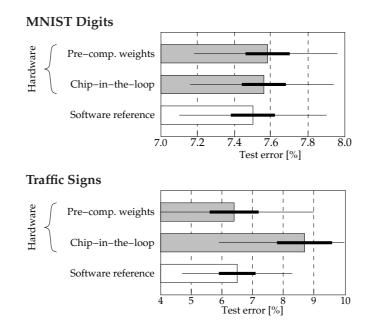

**4 Results With Ideal Neurons** The methods described in chapter 3 are tested in a computer simulation on two problems: The recognition of handwritten digits and the recognition of traffic signs on photographs. The properties of the system are investigated and suggestions for further performance improvement are presented. p. 63

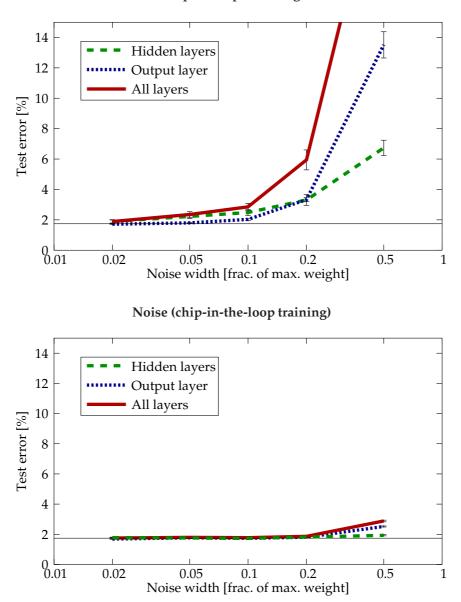

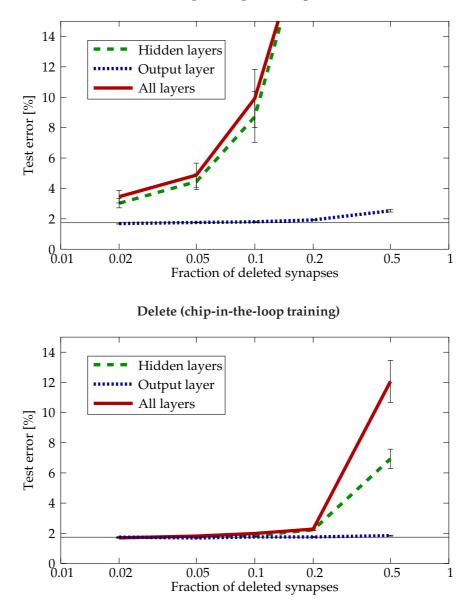

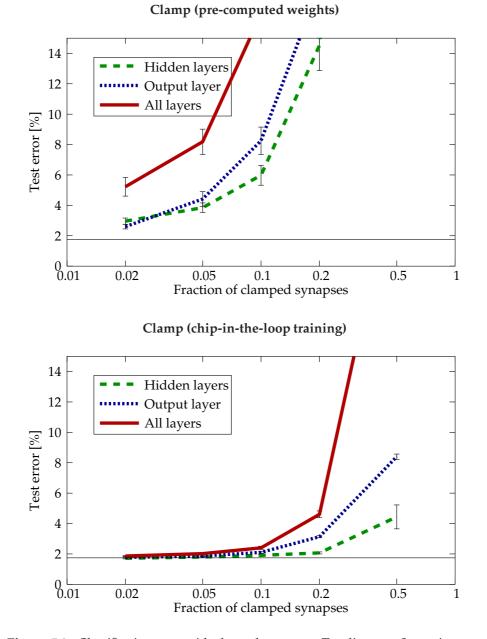

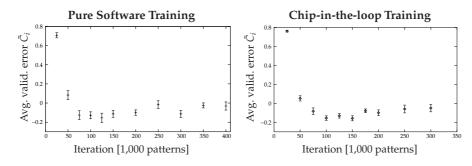

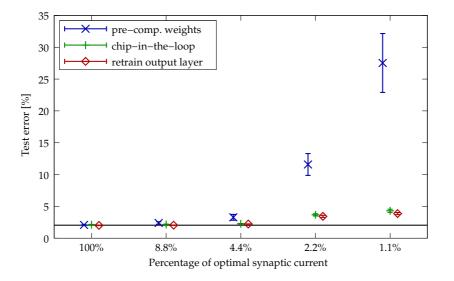

**5** Robustness Against Computation Faults An application implemented in analog hardware should be robust against computation inaccuracies. The robustness of the developed convolutional network is evaluated. Two chip-in-the-loop training strategies are suggested which take possible errors into account already during training. Simulation results with and without applying the chip-in-the-loop techniques are presented. p. 81

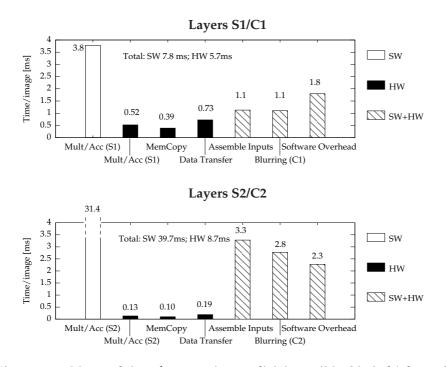

**6** Hardware Implementation The methods developed in chapter 3 and 5 are tested on the neuro-chip prototype HAGEN and compared with software simulations. Particular implementation details required by the used hardware are described. The size limitation of the prototype chip imposes restrictions on the implementable networks. Pruning strategies are applied for fitting the networks onto the chip. p. 91

ORGANIZATION

## **Chapter 1**

## Background

## 1.1 Biological Inspiration

### 1.1.1 The Nervous System

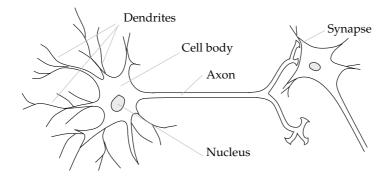

Biological organisms use their perception of the environment to generate behavior, which in turn acts upon the environment. This process requires some sort of information processing taking place within the organism's body. In animals and humans, this task is for a large part accomplished by a special type of cells, the *nervous cells* or *neurons*. These cells are known to be able to generate electric signals in response to external stimuli. Usually, the cell body possesses long appendices, the dendrites and the axon, which are able to propagate the signals over a certain distance (up to in the order of meters) from and to other cells (see Figure 1.1). This way, large and heavily connected networks of neurons are formed. In the human brain, each of the approcimately 5 Billion cells connects on average to about 10,000 other cells. These neural networks are are believed to provide the basis for purposeful behavior and intelligence.

Let us characterize the nature of the neural electrical signals in more detail: A nervous cell in living tissue resides floating in an electrolytic solution. The

Figure 1.1: A nervous cell

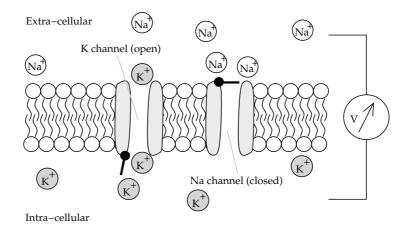

**Figure 1.2:** A cell's membrane consists of a double lipid layer. Diffusion of ions through membrane channels results in an electric potential between the inner and the outer space of the cell.

inner and outer part of the cell are separated by the cell's membrane, a double lipide layer, see Fig. 1.2. Mechanisms which are not covered here maintain a concentration difference of various charged particles between the inside and the outside. Only the most important ions,  $K^+$  (Potassium) and  $Na^+$  (Sodium), are considered in the figure. Ion channels, complex molecules penetrating the membrane, permit or deny certain types of ions to pass and follow their concentration gradient. By this controlled diffusion process, charge is carried across the membrane, resulting in an electric potential which in turn leads to an ion flow in the opposite direction, along the electric field. These two processes settle at a dynamic equilibrium state corresponding to a membrane potential of typically about  $U_{\rm in} - U_{\rm out} = -70$ mV.

Most ion channels can change between an open and closed state, influenced by external parameters (e.g., the current membrane voltage), or by internal mechanisms (e.g., implicit time dependence). This is the basis for an important feature of nervous cells: The actual membrane potential can vary within a relatively wide range, between -90mV and +40mV, at every point in time defined by the current permeability of the various channel types.

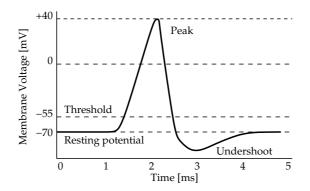

The particular dynamics of the different sorts of ion channels provide the mechanisms for the phenomenon of *action potentials*: As soon as the membrane potential exceeds a given threshold (usually around -55mV) a transient voltage break-out is triggered, as shown in Fig. 1.3. The temporal evolution of the voltage spike is stereotypical: It is exactly the same for every action potential. An action potential causes the voltage in adjacent regions of the membrane to grow above the threshold, too. This way, once triggered, action potentials propagate along the cell's membrane, thus carrying information to remote areas. Because all action potentials are identical, no information is carried in the form of an action potential, but only in the instance of time when it was triggered.

As a mechanism of passing information between cells in neural networks, action potentials are able to influence the membrane potentials of other neurons. This happens primarily at structures called *synapses* (see Fig. 1.1). There are two main sorts of synapses: On arrival of an action potential, excitatory

synapses de-polarize (i.e., increase the voltage of) the membrane of the target (or *post-synaptic*) cell, while inhibitory synapses polarize the same. Simply speaking, the post-synaptic cell integrates over all incoming voltage changes received over a period of time, and, if the firing threshold is exceeded, generates an action potential itself. This behavior is described by the *Integrate-and-Fire* neuron model [].

### 1.1.2 Rate-Based Neuron Model

In order to describe communication in larger networks of neurons, a simple rate-based model is often used which has proven to be adequate for describing many basic phenomena. In this model, the train of spikes produced by a given neuron is represented by a time-dependent continuous value being equal to the current firing rate (e.g., measured in spikes per second). The firing rate is computed by counting the number of spikes occurring within a moving time window. The size of this window is chosen large compared to the mean time between spikes, but small compared to the time scale of the investigated phenomena. Let a spike train be approximated by a sequence of delta peaks  $S(t) = \sum_i \delta(t - t_i)$ , where  $t_i$  is the time of the *i*th spike. The firing rate *r* is then defined by:

$$r(t) = \int_{t'=-\infty}^{\infty} k(t'-t)S(t')dt',$$

(1.1)

where k(t) is a bounded kernel function representing the moving window. In the most simple case, k is chosen as a function being equal to 1 in a given interval [-a, a], and 0 otherwise.

A cell usually receives input spike trains from a large number (typically in the order of  $10^4$ ) of other cells. If the input rates stay constant over time, the output rate *O* will saturate at a steady state:

$$O = F\left(\sum w_i I_i\right) \qquad \text{(steady state)},\tag{1.2}$$

where  $w_i$  is the efficacy of the *i*th input synapse and  $I_i$  is the *i*th input spike rate arriving at the *i*th synapse. The efficacy  $w_i$  of a synapse is also called its *strength* or its *weight*. The activation function *F* is not explicitly defined here. It allows

**Figure 1.3:** Action potentials are stereotypical fluctuations of the membrane voltage, constituting the basic signals for inter-neuron communication.

to model non-linear dependence on the input. For a thorough derivation of equation (1.2), read for example chapter 7 of the textbook [6].

## 1.1.3 Activity-Driven Learning Mechanisms

The nervous system of an organism is under constant development throughout its entire lifespan. Activity-dependent synaptic plasticity is believed to constitute the basic mechanism for learning [6, 12]; synaptic plasticity means that the weight of a given synapse is subject to modification. Many widely accepted models of plasticity are based on a principle formulated by Donald Hebb in 1949: He stated that if a neuron repeatedly contributes to the firing of another neuron, then the synapses between both neurons are strengthened.

The processes of synaptic plasticity are usually much slower than the duration of one spike. If we further assume that the pre-synaptic firing rates change slowly enough, we can well use the steady-state formula (1.2). In addition, we will replace the activation function *F* by the identity function. This corresponds to looking at a linearized version of (1.2), which is a reasonable simplification as long as the considered changes in  $w_i$  are small. Using vector notation where  $\mathbf{w} = [w_1, w_2, ...]^T$  and  $\mathbf{I} = [I_1, I_2, ...]^T$ , the output firing rate reads:

$$O = \mathbf{w}^{T}(t)\mathbf{I} \qquad \text{(linearized)}. \tag{1.3}$$

The weight vector is written as a function of time in order to emphasize our interest in synaptic changes.

The learning rule of Hebb, stated above, might be now expressed as

$$\epsilon \frac{\mathrm{d}\mathbf{w}(t)}{\mathrm{d}t} = \mathrm{IO},\tag{1.4}$$

where the constant  $\epsilon$  determines the speed of learning. This formula implies that simultaneous activity of the pre-synaptic and the post-synaptic cell causes an increase of the connecting synaptic weight. Usually, a cell receives many different input stimuli (patterns) during the learning process. So, the effective weight change may be written as the average change over many patters. Let  $\langle \cdot \rangle$  denote the average over many patterns **I**:

$$\epsilon \Delta \mathbf{w} = \langle \mathbf{I} O \rangle, \tag{1.5}$$

and replacing  $O = \mathbf{w}^T \mathbf{I}$ ,

$$\epsilon \Delta \mathbf{w} = \langle \mathbf{I} \mathbf{w}^T \mathbf{I} \rangle = \langle \mathbf{I} \mathbf{I}^T \mathbf{w} \rangle = \langle \mathbf{I} \mathbf{I}^T \rangle \mathbf{w}.$$

(1.6)

From the last line in (1.6), one important property of Hebbian-style learning can be derived. The matrix  $\langle \mathbf{II}^T \rangle$  represents nothing less than the statistical correlations among the inputs. So, where does the weight vector **w** saturate? One theoretical solution is to require  $\Delta \mathbf{w} = 0$ , which means that  $\langle \mathbf{II}^T \rangle$  has zero rank and **w** is pointing into a direction where the inputs have no correlation. However, this solution can be shown to be unstable against small weight fluctuations [34], and in practice, with large and diverse input pattern sets,  $\langle \mathbf{II}^T \rangle$ has usually full rank. The remaining solution are diverging weights, where the modulus of **w** keeps growing, and the direction of **w** will approach the direction of the largest eigenvector of  $\langle \mathbf{II}^T \rangle$ . To see this, suppose the initial weight

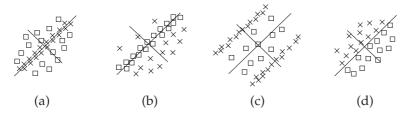

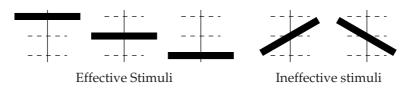

**Figure 1.4:** Receptive field geometries, as found by Hubel and Wiesel 1962, of four typical "simple cells".  $\times$  - areas giving excitatory responses;  $\Box$  - areas giving inhibitory responses. (After [18])

vector be de-composed into the Eigen-components of  $\langle \mathbf{II}^T \rangle$ . Then, by means of (1.6), the component with the largest eigenvalue will grow faster than all the other components, and, in the limit  $t \to \infty$ , dominate. This way, a simple rate-based neuron, together with Hebbian-style learning, is capable of performing a principal component analysis of the input data (see also [44]).

The above discussion only accounts for excitatory synapses and synaptic potentiation (weight increase). Various models following the spirit of equation 1.4 have been proposed to include inhibitory synapses and synaptic depression (weight decrease in response to low input/output correlation). The interested reader is referred to textbooks [6, 12]. In this thesis, inhibition and depression are incorporated into (1.4) by allowing all quantities (inputs, outputs, weights) to assume negative values, thereby abandoning a strictly biological model.

## 1.1.4 Visual Processing in the Brain

The visual systems of human beings and higher animals exhibit a remarkable ability to recognize seen objects. Recognition is accomplished robustly and with high speed, tolerant of many variances in, for example, positional shift, view angle, or illumination conditions, and unaffected by deviations from a learned prototype object or partial occlusion. What mechanisms are these outstanding capabilities based on? In fact, the visual cortex of mammals belongs to the best-known regions of the brain today. In addition to investigating small pieces of dissected living neural tissue, or studying whole brains post-mortem, modern techniques allow to observe neural activity in behaving organisms. Starting with the Nobel-Prize winning work of Hubel and Wiesel with living cats in 1962 [18], elaborate models of early visual processing have been established.

Hubel and Wiesel recorded the activities of cells in a cat's primary visual cortex (anatomical area V1) while presenting stimuli to the respective cell's receptive field. The receptive field of a neuron is the area on the retina which, by stimulation, can influence the activity of this neuron. Hubel and Wiesel classified the cells they observed into several groups. One class, which they called "simple cells", has receptive fields arranged into well-defined excitatory and inhibitory regions (cf., Figure 1.4). Obviously, the stimuli which make these neurons fire strongly are dark/bright straight lines or edges before a bright/dark background. A slight change in the optimal position or orien-

**Figure 1.5:** Behavior of a typical "complex" cell: A dark bar of a certain orientation (here: horizontal) evokes activity independently if the exact position. Tilting the stimulus away from its optimal orientation renders it ineffective. (After [18])

**Figure 1.6:** *Simple neural model explaining the emergence of invariant recognition: Many cells with simple receptive fields make excitatory connections to a more complex cell. In this example, the cell to the right will respond to an oblique bar, invariant to local shift.*

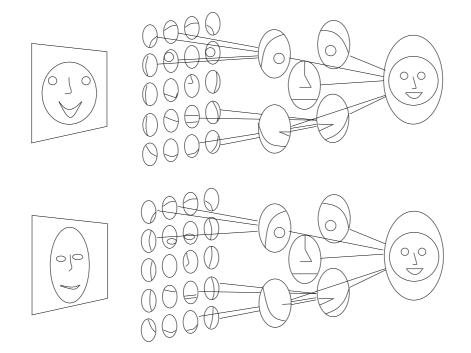

tation of the stimuli results in a significant decrease in firing activity. Another class of cells responds to specific line orientations, but independent of the exact position (Figure 1.5). These kind of neurons were termed "complex cells". Later, more cell types with increasing complexity were discovered in higher visual areas by the same authors and by other scientists (e.g., [19, 62]). Examples range from neurons responding to line combinations (corners, angles) to neurons responding selectively to shapes as complex as faces. One observation is that neurons responding to more complex shapes usually show a higher degree of invariance to shift, scale, orientation, or illumination of the presented shape.

One possible explanation for how this hierarchical set of feature detectors emerges in the brain is that complex cells receive excitatoty input connections from a range of simpler cells detecting similar features, as shown in Figure 1.6. Although this simple model is not able to explain all mechanisms of visual perception, it is widely accepted as playing an important role for early visual processing [48].

## 1.1.5 Biological Implications for Artificial Systems

When designing artificial neural vision systems, nature can provide several guidelines about the approach to choose. Usage of hierarchical feature detectors has been discussed in the previous section as one example. Another hint regards the required amount of computation resources [45]: From measure-

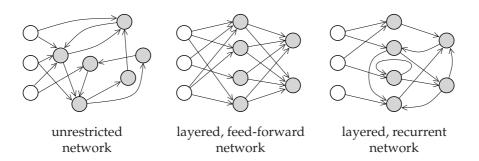

**Figure 1.7:** Artificial neural networks are directed graphs of processing units. Input nodes are drawn in white. Depending on the connection topology, different classes of networks can be distinguished.

ments, the delay between stimulus onset and recognition during the perception process in the brain is known. Dividing this time span by the time necessary for one neuron to transmit a spike to another restricts the number of possible neural relays having occurred during the recognition process to not more than eight. Anatomical studies of the visual areas and their inter-connections show that this is indeed the approximate number of neurons involved in a path from the primary visual cortex to the recognition stage. As a conclusion, basic object recognition cannot rely on lateral or feed-back connections, since this would not be consistent with the measured latency. For an artificial system, a purely feed-forward solution with approximately eight processing stages should be sufficient.

Interestingly, the mentioned time limit does not allow for neurons in the brain to saturate at a defined firing rate. In order to match the measurements, information must be passed on the basis of the first spike. During the first moments of recognition, the neural information seems to be entirely determined by whether a neuron is active or silent, "on" or "off". This implies that in fact a simple threshold neuron model, as employed in this thesis, can be expected to be sufficient to mimic at least some of the recognition capabilities present in the brain.

## 1.2 Convolutional Neural Networks

In order to read this thesis, basic knowledge about the general concepts of artificial neural networks is assumed. A few facts are shortly reviewed: . Basically, neural networks are directed graphs where the nodes (neurons) are processing units and the edges transport information between them. In the networks used in this thesis, the information is numerical data. A neuron computes a weighted sum of the afferent signals, and provides a scalar function of this sum as its output (cf., equation (1.2)). The scalar function is usually chosen as a bounded sigmoid or a step function, in which case one speaks of threshold neurons. The behavior of such a network is defined largely by the weights of the individual connections.

Networks can be divided into several classes, depending on the connection topology (examples in Figure 1.7). Different update schemes of the neuron out-

puts are possible, i.e., synchronous or asynchonous update, time-continuous or clocked operation. Further detail are found in a number of excellent text books on this topic [17, 3, 49].

#### 1.2.1 Overview

We have learned in section 1.1.4 that hierarchical feature detectors are believed to play an important role in the brain's visual system. In the following, it will be discussed how the principle of hierarchical structures are taken advantage of in artificial vision systems. In particular, the focus will be on so-called convolutional neural networks, a special type of artificial neural networks with a specific connection topology. Such networks have been successfully employed for industrial image analysis applications (character recognition [32], face identification [29, 67]), but are also used as models in computational neuroscience [34, 38, 48].

Convolutional neural networks belong to the class of layered, feed-forward networks.<sup>1</sup> The first layer usually detects simple features, e.g., oriented line segments. By successive feature extraction through the layer hierarchy, more and more complex shapes, and finally entire objects can be recognized in higher layers. In contrast to many standard feed-forward networks, adjacent layers are not fully connected. Rather, a particular local connectivity scheme implements topology-preserving feature maps which are the basis for the hierarchical image analysis.

Among the many authors who have contributed to the promotion of convolutional networks for image processing applications, the two probably most original are Kunihiko Fukushima and Yann LeCun. Fukushima invented a convolutional neural network for shift-invariant object recognition in 1980, which he named the "Neocognitron". It could be trained by both self-organization and supervision. The supervised training yielded better results but involved time-consuming manual training (cf., section 1.3.4). In 1989, Yann LeCun introduced a system for hand-written digit recognition based on a convolutional neural network trained by back-propagation which was utilized commercially for post office zip-code recognition. Parts of the computations were accelerated by a custom-made hardware device (see also section 1.4).

Although LeCun's work appeared years after the "Neocognitron", LeCun never cited Fukushima (neither did Fukushima cite LeCun in his later work). Therefore it is likely that the two authors, even though their methods have strong overlap, worked completely independent.

### **1.2.2** Invariant Recognition: From Local to Global Invariance

An ideal vision system is able to identify and classify objects invariant of positional shift, view angle, or illumination conditions, and unaffected by deviations from a learned prototype object. However, experience shows that such functionality is not easily programmed into artificial systems. The reason is that, in pixel space, different views of the same object are usually not close to each other (cf., Figure 1.11). Defining the common characteristics of the various

<sup>&</sup>lt;sup>1</sup>Although feed-back or lateral connections were sporadically proposed in more theoretical work, most real-life applications do without recurrent connections.

**Figure 1.8:** Hierarchical feature detectors facilitate invariant object recognition. Small invariances in each hierarchy level result in a large invariance of the whole system.

possible views of, say, a face *in terms of pixel values* would require prohibitively many rules of the form: "If pixel A is brighter than pixel B and pixel C is approximately as bright as pixel D, and ... then the shown object is a face".

One approach of tackling this combinatorial explosion is to use hierarchical structures [65, 48], where complex features are inferred from the presence or absence of many simpler features (see Figure 1.8). The intuitive idea is that the visual representation of a natural object is composed of a number of smaller shapes which, each taken by themselves, appear more invariant under transformations than the entire object as a whole. In each level of the hierarchy, decisions are based on abstract concepts found in the previous level rather than on raw pixel values. A face, for example, usually consists of two eyes, a nose and a mouth, appearing in a defined relative arrangement. Once it is known that a mouth is present somewhere in the lower part of the picture, the raw pixel values with could have produced this information are not longer of importance.

When using the hierachical approach, only a relatively small amount of invariance must be computed in each hierarchy level. If local feature detectors show invariance against small shifts, this will result in larger shift tolerances in higher layers, and eventually in higher-order invariances like tolerance against scale or deformation (section 1.2.5 and [11]).

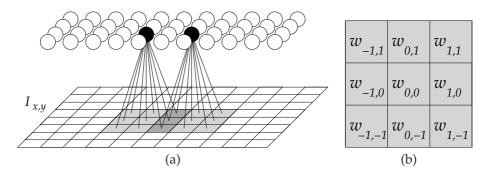

**Figure 1.9: (a)** A convolutional feature-plane: A grid of neurons with identical weights, receives connections from shifted, partly overlapping, input regions. Only the connections of two sample neurons are drawn. **(b)** The synaptic weights define the convolution kernel.

## 1.2.3 Neural Implementation of Convolutional Filters

Convolution operations are widely used in the field of computational image processing for extracting local information, e.g., edge positions, from digital images. In this context, convolutions are also referred to as *linear filters* or *local neighborhood operations* ([23] for an introduction). Convolutional neural networks use hierarchical sets of convolutions to detect not only edges, but all sorts of abstract shape information, generally called *features*, in a given input image (hence the name).

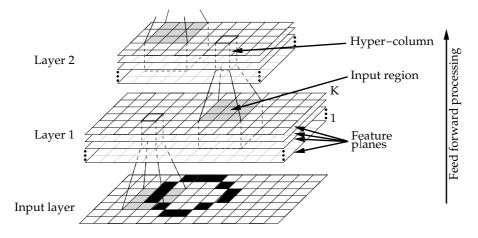

In convolutional neural networks, convolutions are implemented by particularly interconnected ensembles of neurons. Figure 1.9a shows the essential neural structure: a so-called *feature-plane*. All neurons in the plane are equal with respect to their synaptic weights but they receive their input from shifted, partly overlapping, local regions in the previous network layer. The input region is often chosen as a square with an odd-numbered side length  $S \equiv 2s + 1$ ,  $s \in \mathbb{N}^+$ . For example, the input region in Figure 1.9b has S = 3, or equivalently, s = 1. Let us, for a moment, refer to the synaptic weights by double indices according to their spatial arrangement, as shown in Figure 1.9b. Then, in accordance with equation (1.2), the output of a neuron at position x, ywrites

$$O_{xy} = F\left(\sum_{i=-s}^{s} \sum_{j=-s}^{s} w_{ij} \cdot I_{i+x,j+y}\right),$$

(1.7)

where  $I_{x,y}$  is the two-dimensional field of input nodes. The term in parentheses is equivalent to a two-dimensional discrete convolution applied to the function I, using the convolution kernel w (cf. [23]). Thus, a feature plane computes a convolution with the input data, and additionally scales the output by the (generally non-linear) scalar function F.

The fact that all neurons in a feature plane are equal in terms of their weights is a form of the general concept of *weight sharing*, cf., section 1.3.1. Weight sharing drastically reduces the free parameters in a neural network: Although a feature plane has a lot of computable input connections, the actual number of weights to be adjusted during training is only a small fraction thereof.

**Figure 1.10:** In a convolutional network, each layer consists of a set of feature planes. Each feature plane detects a different feature. A given neuron generally receives input connections from all feature planes in the previous layer.

## 1.2.4 Hierarchical Sets of Convolution Filters

Figure 1.10 shows how the convolutional feature planes are used in a complete convolutional neural network. A network layer consists of many equal-size feature planes, each detecting a different feature. An exception is the input layer, which has only a single plane representing the pixels of the image to be processed. The neurons in one layer at the same grid position, but belonging to different planes, are referred to as a *hyper column* throughout this thesis<sup>2</sup>. Neurons usually receive connections from all (or, at least most [30]) planes in the previous layer. The neural activities in a given hyper column form a feature vector, where each component indicates whether the corresponding feature is present in the image at that position. Obviously, the first network layer is transforming the raw image pixels into a topology-preserving feature map. The next layer transforms this feature map into another feature map with a higher degree of abstractness, and so on. Accordingly, the shape features detectable in a given layer are generally composed of features detected in the previous layer. Traversing up the layer hierarchy, more and more complicated shapes can be recognized.

A neuron, depending on its threshold (generally: depending on *F* in equation 1.7), is usually not only selective to a single point in the input space, but responds to a range of input vectors within an extended volume. This property is also referred to as *generalization*. A neuron in the first network layer will therefore not only fire for one exact pixel combination being present in its input region, but also for image patches whitch look similar. The same holds for neurons in higher layers, where the input consists of abstract features. This neural generalization provides the foundation for the hierarchical principle of invariant recognition discussed in section 1.2.2.

<sup>&</sup>lt;sup>2</sup>naming after [10]

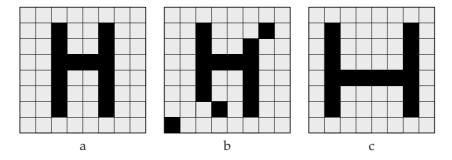

**Figure 1.11:** *Images* a *and* b *have most pixels in common, so they are close to each other in pixel space. On the other hand, the pixel distance between* a *and* c *is very large, although, on an abstract level, the shapes look similar as well.*

## 1.2.5 Boosting Invariance by Blurring and Sub-sampling

The invariance computable by one single neuron is restricted to certain modes of variations. Consider, for example, a neuron connected to each pixel of an 8 x 8 image, tuned to respond maximally to the shape "H" shown in Figure 1.11*a*. Presenting this neuron the image in Figure 1.11*b* will result in a similarly strong response, because most pixels are equal in both pictures. In contrast, image *c* will yield a very weak neural response, although, in terms of abstract shape features, the shown object has also much in common with image *a*. We may conclude that a convolutional network as described in the previous section might well cope with noisy images or slight illumination changes, but not at all with shift, scaling, or rotations of the whole shape or parts of it. This investigation gives rise to the introduction of special blurring layers (equivalently called subsampling layers), which in fact generate the real abstraction power of convolutional neural networks.

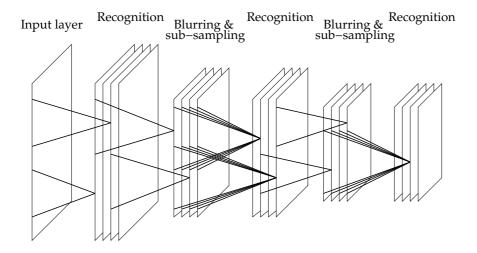

A blurring layer is very similar to a recognition layer, except for three differences: First, a blurring layer has the same number of feature planes as the preceding layer, and only corresponding planes are connected (e.g., neurons in the third feature plane in the blurring layer receive only inputs from the third feature plane in the preceding layer). Second, the convolution kernels implement blurring filters. In the most simple form, all weights are equal positive numbers. Third: The spatial resolution of the feature planes decreases in the blurring layer. This is usually accomplished by sub-sampling the feature plane grid, i.e., by discarding some rows and columns of neurons.

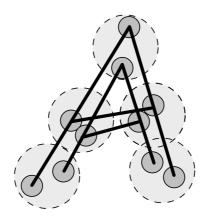

In a typical convolutional neural network, recognition layers and blurring layers are arranged in alternating order. When a feature is detected at one position in the recognition layer, an extended neighborhood around this position will be active in the following blurring layer. This in turn results in shift-invariance in the subsequent recognition layer. Putting it in other words: As soon as a feature is detected, its exact position does not matter any longer. While traversing up the layer hierarchy, concrete positional information will be gradually transformed into abstract, position-invariant information. Figure 1.13 illustrates how local blurring is used detect deformed instances of the same shape.

A link to the biological paradigm should be emphasized here. A blurring

**Figure 1.12:** A complete convolutional neural network consists of recognition layers and blurring layers in alternating order. The presence of blurring layers is essential for invariant recognition. Neurons in the blurring layers only receive inputs from the corresponding feature plane in the preceding layer.

**Figure 1.13:** Local blurring can create global invariance. Solid circles represent local features detected by S-neurons. Due to blurring, deviations within dashed circles are tolerated. At the blurred level, the original and the deformed version of the letter "A" can be recognized by the same neuron.

layer acting on top of a recognition layer exhibits some analogy to the relationship between simple and complex cells observed in the visual cortex (cf., Figure 1.6). According to the terms *simple* and *complex*, recognition layers are often referred to as "S"-layers, blurring layers as "C"-layers in the literature [10, 41].

## 1.3 Training Methods

The previous section was concerned with the topology and functional principles of convolutional neural networks. However, before being applicable to a given problem, a neural network must be *trained*. in the context of neural networks, *training* usually refers to the adjustment of the synaptic weights with the goal to reach a desired network behavior. Often, training methods are based on a cost function

$$\mathcal{C}(\mathcal{I}, \{w_i\}) \tag{1.8}$$

which depends on a set of training input patterns  $\mathcal{I}$  and the weights  $\{w_i\}$ . It measures the discrepancy between the actual network behavior and the ideal, desired network response. The training algorithm tries to find the set of weights such that  $\mathcal{C}$  is minimal ( $\mathcal{I}$  is usually constant for a given problem).

In this section, we will only discuss training methods that have been previously applied in the special field of convolutional neural networks. Comprehensive reviews of training algorithms for neural networks in general can be found in text books, e.g., [17].

Before turning to concrete training methods in sections 1.3.2 *et seqq.*, some general considerations about the dimensionality of the problem are of interest.

## **1.3.1** The Curse of Dimensionality

A typical convolutional neural network possesses a huge number (in the order of 10<sup>6</sup>) of synaptic connections. Training a network like this corresponds to finding the global minimum of a function of 10<sup>6</sup> variables, where the function is supposed to be highly non-linear. According to Bellman's notion of the "curse of dimensionality", such a high-dimensional search space is virtually not coverable within reasonable time and resources, considering the exponential growth of the hyper-volume with the number of space dimensions [2]. Training is also impractical from another point of view: Any machine-learning system suffers from the effect of overfitting if the number of free parameters is in the order of, or exceeds, the number of training samples (e.g., [3]). An overfitted system does not generalize, i.e. it may work well on the training set but it will fail when confronted with input patterns not seen during training. For many visual recognition tasks it is difficult to get hold of a sufficiently large number of training samples for proper generalization.

Thus, methods are required for large networks to restrict the search space in advance. Three important strategies, applicable to convolutional networks, shall be mentioned:

**1) Weight Sharing** This strategy comes for free in a convolutional neural network. The convolutional nature of a feature plane requires that all its neurons

have equal weight vectors, in other words: they share the same weights. So, even though there are a lot of computable connections present, the number of actual free parameters is significantly reduced. For each feature plane, only one representative weight vector is necessary. Besides simplifying the training, the shared weights also turn out to enable fast evaluation in the analog hardware environment evaluated in this thesis (cf., section 6.1).

**2) Divide and Conquer** Even after taking into account the reduction of parameters by weight sharing, a convolutional network can easily possess a few thousand independent weight values. Although nowadays all these parameters can be trained at once by brute computing force (taking hours or even weeks for one training run, [32, 60]), many approaches, including the one described in this thesis, make use of divide and conquer techniques. The network is split into multiple sub-networks which can be trained independently. Assuming that the complexity of training depends exponentially on the number of free parameters, but only linearly on the number of sub-networks to be trained, the divide and conquer approach will greatly simplify computations. However, the challenge remains to find appropriate partitions, such that both the sub-networks are trainable in isolation, and the overall network will be still be close to optimal in the end.

One common partition policy is to divide the network vertically, i.e., to train the network layers independently, one after another. As a consequence, the global network task (e.g., the correct classification of images) cannot directly guide the training, since the global error can only be assessed in the topmost network layer. Therefore, intermediate layers are either trained for solving pre-defined sub-problems [11], or unsupervised methods are employed [10, 67, 41]. Another possibility is to divide the network horizontally. Examples are *ensembles of experts* [17] or partitioning a many-class problem into many 2-class problems [22]. As an extreme example of divide and conquer, one can train each single neuron in a network separately [11] which, however, shifts a large part of the training intelligence from machine learning to the skill of the human operator.

**3)** Self-Organization The term self-organization refers to phenomena where simple, locally determined processes produce a complex global order. Applied to neural networks, this means that a neuron, or a neighborhood of near-by neurons, change their weight values depending on local parameters as for example their own current activation. An example for a local weight update rule is Hebbian-type reinforcement learning (equation (1.5)). In terms of the principle of splitting the global problem into many local problems, self-organization is similar to the divide and conquer approach outlined above—with the crucial difference that no cost-function (1.8) is explicitely given. Rather, the network converges to a state implicitly defined by the used local learning scheme. Of course, for many problems it is difficult—if not impossible—to define local update rules which result in the desired global network behavior. However, some data processing tasks can be very well accomplished by self-organization techniques. This is done also in this thesis (section 3.3).

## **1.3.2** Supervised Approaches

Supervised training methods subsume all strategies which rely on some sort of external teacher who has sufficient *a priori* knowledge of the problem to be solved.

**Manual Weight Adjustment** The most basic, albeit very laborious, supervised "training" method is to set each and every weight value by hand. This method requires detailed knowledge about both the problem and about the strategy by which the network will solve it. With convolutional neural networks, the solution strategy is known: Detect simple shape features in the first layer and more complex features in subsequent layers. So, given a hierarchical set of features, the corresponding network weights can be constructed analytically. The actual work consists in defining the features detectable in each layer. This task requires a high degree of skill and intuition of the human supervisor. Usually, a lot of trial-and-error adjustments are involved, since for many problems it is not obvious which features are optimally suited for the detection of the object(s) in question. Nevertheless, some authors were able to achieve sound results with this method [11, 41].

**Interactive Feature Learning** This method adds some level of automation to the plain manual setting of weights discussed above. The supervisor is still responsible for defining the features detected in each layer, but it is no longer necessary to think of raw pixel representations and to specify individual network connections. Instead, the supervisor marks examples of the features in the training images (e.g., using a mouse pointer on a graphical display), and some sort of automatic learning identifies the optimal synaptic weights. In one of Fukushima's approaches, the supervisor explicitly appoints a single neuron for each example, which is to alter its weights [11], i.e., the supervisor assigns features to neurons beforehand. In other techniques, a winner-take-all learning scheme automatically finds a suitable feature-to-neuron mapping, and additionally may insert new feature planes as deemed necessary [64, 67]. Training normally proceeds bottom-up, i.e., complex features are learned after the training for simple features is complete.

**Global Training With Back-Propagation** Back-propagation [51] is one of the most prominent automatic supervised methods applied in the scope of neural networks in general. It belongs to the family of gradient-based optimization methods. A set of training input patterns  $\mathcal{I}$  for which the correct network response is known in advance must be given as a prerequisite. Then, the cost function is defined as a distance measure between the desired ( $O_d$ ) and actual network output ( $O_a$ ):

$$C(\mathcal{I}, \{w_i\}) = \sum_{j \in \mathcal{I}} |O_d(j) - O_a(j, \{w_i\})|^2.$$

(1.9)

In each iteration, the weights of the network  $w_i$  are updated by following the negative gradient of the cost function:

$$w_i \leftarrow w_i - \epsilon \frac{\partial \mathcal{C}}{\partial w_i}$$

, for each *i*. (1.10)

**Figure 1.14:** Competitive learning. *n* neurons are connected to the same inputs (n = 3 in this drawing). For each training pattern, only the neuron with the strongest response is reinforced. Sometimes this winner-take-all policy is implemented by lateral inhibitory connections (drawn shaded).

By application of the chain formula, the gradient (1.10) can be evaluated not only for synapses belonging to output neurons but also for neurons in hidden network layers, provided the transfer function *F* in (1.2) is differentiable. This technique was termed "error back-propagation" by its inventor D. Rumelhart in 1986 [51]. In fact, back-propagation was the first algorithm to provide a universal formula to train a multi-layer neural network by global supervised training. For convolutional neural networks, this means that only the mapping from full-scale images to object labels must be given by the supervisor. All the details of the features detected in the hidden layers are learned automatically by the algorithm.

Examples of successful application of back-propagation in the field of convolutional neural networks include hand-writing recognition by LeCun and successors [30, 60] and face recognition by another research group [29].

Although back-propagation is extremely popular and yields successful solutions for many problems, it suffers from the following shortcomings: First, like any gradient-based method, it is prone to get stuck in local minima of the cost function. Second, back-propagation can get computationally very expensive for large networks. Training times as long as many hours or even days for just one training run are often reported. Third, as mentioned above, the neural transfer function (F in (1.2)) and its derivative must be exactly specified. These preconditions can be easily realized in software simulations, but they can constitute an issue in hardware implementations.

## 1.3.3 Un-Supervised Approaches

Un-supervised learning refers to training approaches which do not rely on *a priori* knowledge about the task to be solved. Only the implicit structure contained in the training data is used. Un-supervised methods are often used for dimensionality reduction or for the automatic identification of pattern classes implicitly defined by clusters. In the field of neural networks, un-supervised is also called self-organization and is often based on Hebbian-style reinforcement.

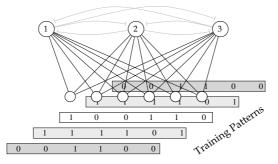

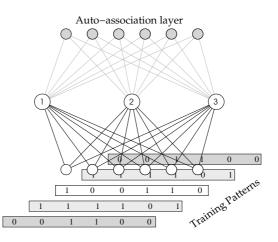

**Figure 1.15:** *Learning by auto-encoding: A 3-layer network is trained such that the temporary auto-association layer (shaded) reproduces the input for all training patterns. After training, the hidden neurons (1-3) represent the most significant components of the input data.*

**Competitive Learning** The term "competitive learning" was introduced by Rumelhart et al. in 1985 [50], denoting a learning scheme where only the most active neuron of an ensemble has its weight altered in each learning step. The other neurons do not change their weights in this step. If topological information is to be learned, neurons in the neighborhood of the winner neuron can be updated as well, as, for example, done in Kohonen's self-organizing maps.

The update rule itself is Hebbian-style reinforcement learning (cf. equation (1.4)), followed by some sort of weight normalization. All neurons in the ensemble receive the same inputs (see Figure 1.14). Ideally, for different training inputs, a different neuron is the one with the strongest activation, so, during training, every neuron in the ensemble gets the chance to be reinforced. After a neuron was reinforced, the next time a similar training pattern is presented, the same neuron will again be the one with the strongest activation. Gradually, the network will partition the input space into several classes, where each neuron responds to patterns from its corresponding class (see also Figure 3.2, p. 56). The success of this method can vary depending on the initial weight values and the order in which the training patterns are presented. Competitive learning is one example of vector quantization and it is very similar to the *K-means* clustering method.

In his early work, Fukushima used a kind of competitive learning in his "Neocognitron" in order to identify suitable feature sets detected by the feature planes [10]. The training proceeded sequentially layer after layer. Fukushima focused on supervised methods later because better results could be obtained. Competitive learning is a key technique for the training procedure described in this thesis (see section 3.3).

Auto-Encoding / Principal Components Like competitive learning, autoencoding is a method for dimensionality reduction. The aim is to transform the *N*-dimensional input data into *M*-dimensional feature vectors (M < N) while preserving as much of the information as possible. In Figure 1.15, the 7-neuron input layer is to be reduced to a 3-dimensional feature vector defined by the activity of the neurons labeled "1", "2", and "3". During training, a temporary *N*-dimensional association layer (shaded) is introduced, and the resulting feed-forward multi-layer network is trained to reproduce the input as close as possible. For this purpose, back-propagation is used in [41], but other training methods are possible. After the training, the association layer is removed. This training strategy ensures that a maximum of the information is preserved in the middle layer. It can be shown that for a linear transfer function *F* (cf., equation (1.2)) the activities of the *N* neurons in the middle layer correspond to the first *N* principal components of the training data [3]. In [41], auto-encoding is used to identify the features for the hidden network layers.

**Reinforcement Without Competition** Some authors use self-organization by reinforcement where, in contrast to competitive learning, the reinforcement is not limited to the most active neuron in an ensemble. The decision whether a neuron is reinforced by the current input or not depends on whether its activation exceeds a given threshold, either a global or a dynamically adjusted one. Such a technique is useful if it is not known in advance how many distinct features are needed in each layer (adaptive network size), or if multiple objects should be detectable simultaneously in the same field of view. Examples are the Cresceptron [67], the multiple-object recognizing network of McQuoid [38], or the association network by Teichert [64].

## 1.3.4 Hybrid Approaches

Hybrid approaches, mixing supervised and un-supervised methods, are often utilized. One approach is to train the lower convolutional network layers by self-organization, and to train a classifier layer on top by a supervised method. The classifier can be either another neural network layer [41] or other non-neural machine learning systems [32, 29]).

An interesting hybrid approach is described by Weng et al. [67], where the supervisor marks high-level objects in example images and assigns them class labels. For each new class label, a new feature plane is added in the top-most network layer while a self-organization process based on the marked input field alters the structure of the network below. Thereby, the number of feature planes in each layer can grow adaptively when new features are detected. Training is based on bottom-up analysis rather than on back-propagating errors. Similar approaches are described in [38, 64]

In this thesis, the hidden layers are trained by self-organization without any explicit class information, and only the output layer is trained by a supervised optimization method.

## 1.4 Analog VLSI<sup>2</sup> Implementations

## 1.4.1 Motivation

The majority of today's computing machines rely on digital general-purpose processors, mostly based on the von Neumann architecture [42]. In contrast, analog electronic circuits are not widely applied for complex computing tasks<sup>3</sup> although they have the potential to offer advantages in various terms (cf., [33, 26, 66]):

- **Space efficiency.** In analog computing circuits, basic laws of physics are exploited for performing calculations. Examples are the Kirchhoff rules for currents or the electrical properties of solid matter boundaries (see [66] and section 6). In contrast, digital solutions operate on abstract symbols represented within a complex electronic machinery. This difference makes analog VLSI implementations usually occupy way less silicon area compared to equivalent digital devices.

- **Power efficiency.** For the same reason, many analog solutions consume less power than a digital implementation performing the equivalent computation. This holds especially for so-called *sub-threshold* designs where currents are low and are determined by Bolzmann statistics.

- **Massive parallelization.** Space and power efficiency enable the design of massively parallel implementations where a large number of equivalent computing elements are integrated on one micro chip.

However, when designing analog computers, the following drawbacks relating to the analog nature must be taken into account:

- **Limited computing precision.** Quantities coded by analog signals are inherently limited in precision. An upper limit of accuracy is constituted by noise present in the system, e.g., by thermal fluctuations or electrodynamical side effects, e.g., crosstalk. Other sources of uncertainty are random device variations which are characteristic for the manufacturing process.

- **Limited application scope.** Not all types of applications are equally well suited for an analog implementation. First, precision requirements must match the capabilities offered by the used analog system. Second, in applications relying on algebraic computations, parallel processing can only be exploited if the problem is partitionable into independent, simple, computing steps.

Feed-forward neural networks seem to be a promising application for analog computing devices. The high degree of regularity and the natural fine-grained partition into independent computing units makes a parallel implementation straight-forward. This is true even more in the special case of convolutional networks (see next section).

<sup>&</sup>lt;sup>2</sup>Very Large-Scale Integration

<sup>&</sup>lt;sup>3</sup>involving more than a single multiplication or addition

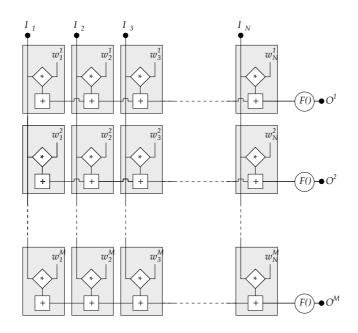

**Figure 1.16:** 2D parallel computing array. Each of the M rows constitutes a neuron with N inputs. The input signals  $I_1...I_N$  are shared by all neurons. Shaded boxes represent the atomic multiply-and-accumulate elements, the synapses. The weights are stored in the synapses. The non-linear scaling function F() is computed once per neuron.

Whether limited computing precision is an issue remains to be assessed in each individual case. Techniques of limiting the precision problem exist on the hardware level, e.g., using analog computing but digital signal transmission [16, 4, 54], or incorporating calibration routines ([22] and section 6.2.3). It is a main contribution of this thesis to tackle the issue of precision on the training level. Methods are developed which yield reliable networks independent of hardware inaccuracies (chapter 5).

# 1.4.2 Massively Parallel Computing Arrays

As pointed out in the previous section, massively parallel computing is one of the applications where analog VLSI technology can promise efficient alternatives to digital processors. Neural networks are particularly well suited for parallel implementations, since (at least for layered neural networks) each neuron can be computed independently. Moreover, even the computation within a single neuron can be further parallelized. Recall that a neuron computes the dot-product with a given weight vector and scales the result (equation 1.2 repeated):

$$O = F\left(\sum_{i=1}^{N} w_i \cdot I_i - t\right).$$

(1.11)

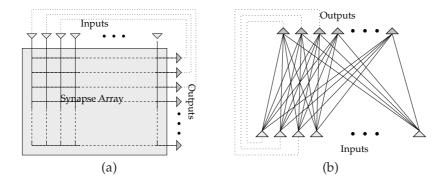

The *N* multiplications  $w_i \cdot I_i$  can be performed independently and can thus be processed by parallel computing elements. Depending on the number of inputs *N*, this can imply a significant performance gain compared to sequential processing. Kramer states in [26] that the most dense arrangement of such multiplication units is a 2-dimensional array, as shown in Figure 1.16. The multiplication units (synapses) are laid out in a grid, where the shared inputs are along one dimension ( $I_1...I_N$ ), and the outputs are along the other dimension ( $O^1...O^M$ ). Each synapse holds a locally stored (but re-configurable) weight and thus implements a *single-instruction multiple-data* element.

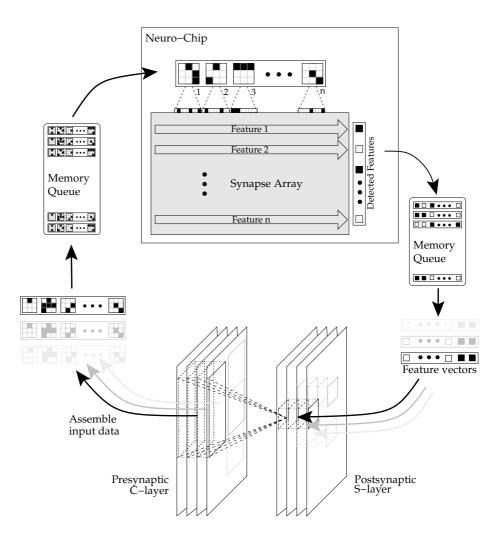

If reconfiguring of weights is to be avoided during the evaluation phase, one row must be reserved for each neuron in the network. Convolutional neural networks usually possess a huge absolute number of computable neurons, but due to *weight sharing* (p. 20), large groups of neurons have identical weights. If a distinct computing row is reserved only for every *unique* neuron in the network, the required array size is thus limited to practical dimensions. This makes convolutional networks especially well suited for parallel array implementations. Indeed, all serious applications of array-based analog VLSI known to the author are located in the field of image processing and involve computing convolutions [5, 26, 31, 37].

# 1.4.3 Recent Array-Based Neuro Chips

A plethora of analog neural network implementations have been developed by various research groups. Rather exhaustive overviews are given in [1] or [33]. Here, we will review some of the most-cited array-based VLSI solutions of the recent years. Some of them are reviewed also in the book [68] and the paper [25]. All these chips have configurable weights, but they do not include learning circuitry, so training is done either completely in software or in a closed software/hardware loop. Except for the ETANN chip, which is purely analog, the described chips combine analog computing with digital data transmission. This *mixed-signal* approach enables convenient interfacing by standard digital hardware and confines the noisy analog calculations into closed units.

**ETANN (1989)** The first commercially available analog chip was the Intel i80170NX, or ETANN (Electrically Trainable Analog Neural Network), containing 64 neurons and 10280 weights (there are 128 inputs plus 32 bias weights per neuron). Multiple configurations including multilayer networks using internal feedback can be realized. The array can be split into two 64x64 banks. The programming of the weight values is very slow compared to the other chips drescribed below. The ETANN chip was used in various commercial devices, including a music synthesizer.

**NET32K (1990)** The NET32K chip [16], developed by AT&T, implements 256 neurons with 8,192 synapses. The chip uses only 1-bit resolution for weights and data, but several synapses can be used in conjunction to realize effectively up to 4-bit weights and/or data. The chip was used for example on a commercial extension board for use with standard workstations [5]. The board, containing 2 NET32K chips and digital support logic was used to accelerate convolutions for image processing tasks. An interesting development by the same

research group was a similar architecture by Satyanarayana et al. (1992) which allowed for more flexible connection topologies by equipping each synapse with an own neuron body circuit.

**ANNA (1992)** Another development by AT&T is the ANNA chip (Analog Neural Network Arithmetic) which implements 4,096 synapses which can be configured as 8 neurons with 256 inputs each [4]. Other configurations with 64 or 128 inputs per neurons are possible as well. The activation function is piecewise linear, roughly approximating a sigmoid. The digital interface allows 6 bit resolution for the weights and 3 bit for the input/output data lines. The ANNA chip was used for the evaluation of convolutional networks for hand-written character recognition [52].

**MoneyPen (1999)** One example of a VLSI neural network development which matured into a commercial product is the chip presented by Masa et al. [37]. The application-specific chip has a fixed connection topology with three different-sized synapse arrays corresponding to three convolutional network layers. Image data is directly fed in from an optical sensor. The system is marketed as a mobile character recognition system for check reading ("MoneyPen") through a company in Switzerland (www.csem.ch/fs/microelectronics.htm).

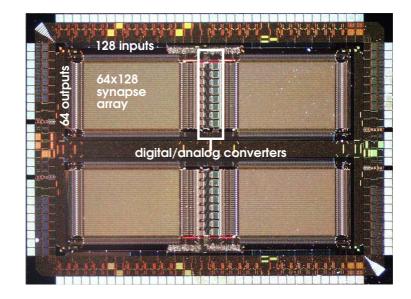

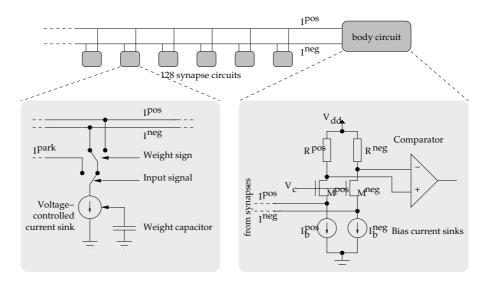

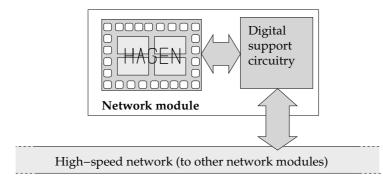

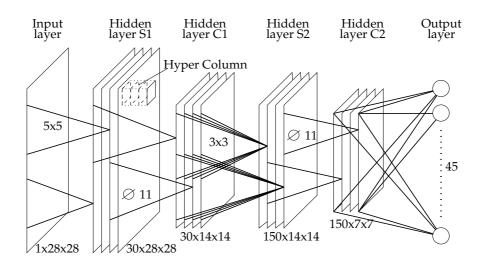

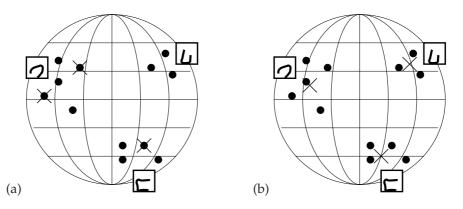

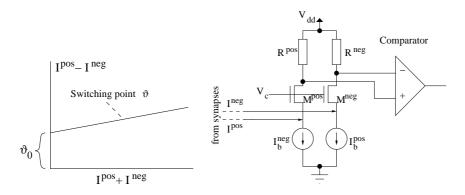

**HAGEN (2003)** The HAGEN chip, developed by J. Schemmel in Heidelberg (HAGEN = Heidelberg AnaloG Evolvable Network) [54], implements 256 neurons with 128 inputs each. The neurons are arranged in 4 synapse arrays of 64 neurons. Input/output lines have 1 bit precision, weights can be written with 10 bit precision (+ 1 sign bit). Of all reviewed chips, HAGEN is manufactured using the most modern technology and outperforms its predecessors in terms of operating speed, weight configuration speed, and power efficiency. This chip is described in more detail in section 2.2.1. It is used for the hardware experiments in chapter 6. Previous studies for utilizing this chip for image recognition are described in [43].

30

# **Chapter 2**

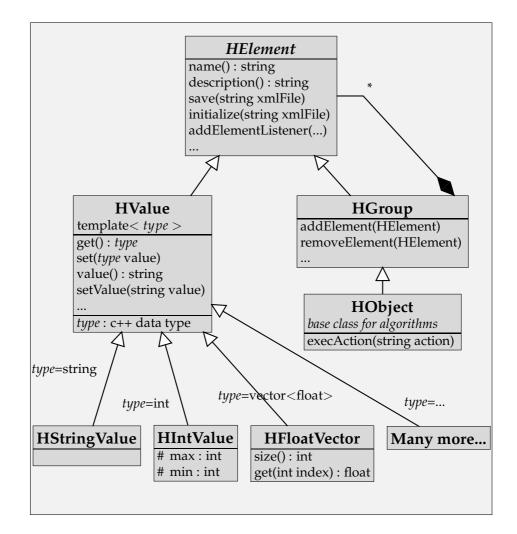

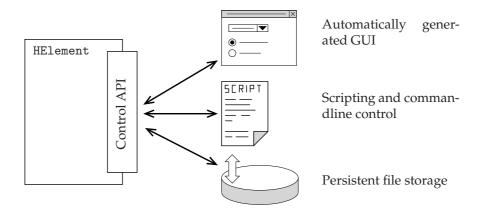

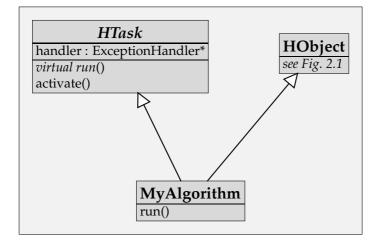

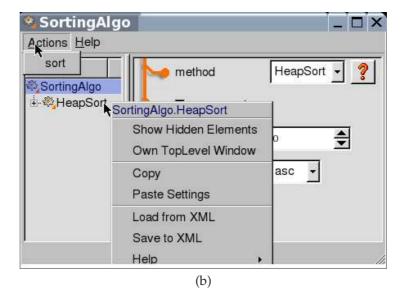

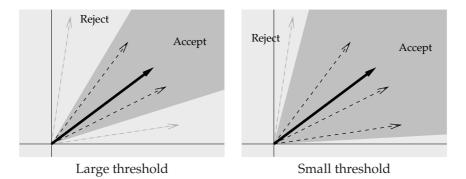

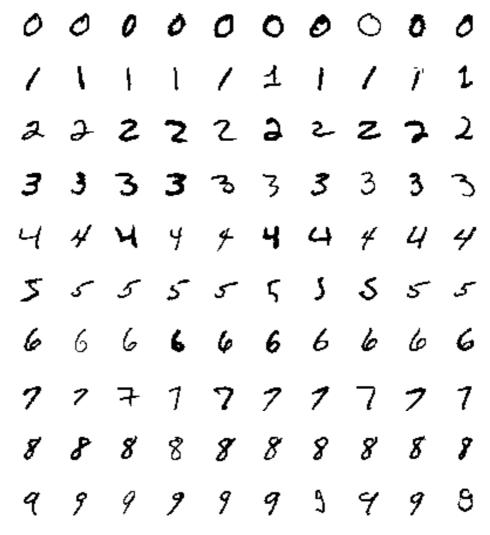

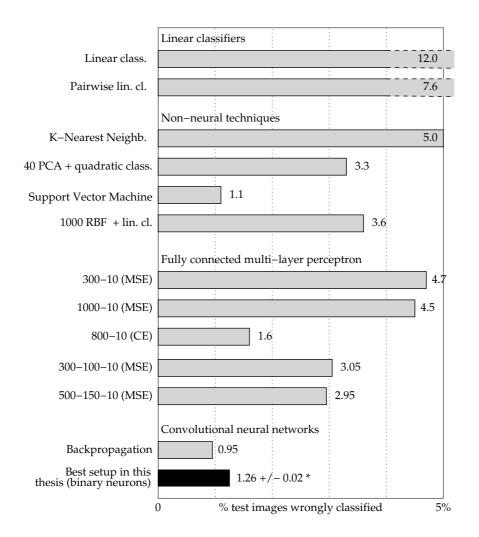

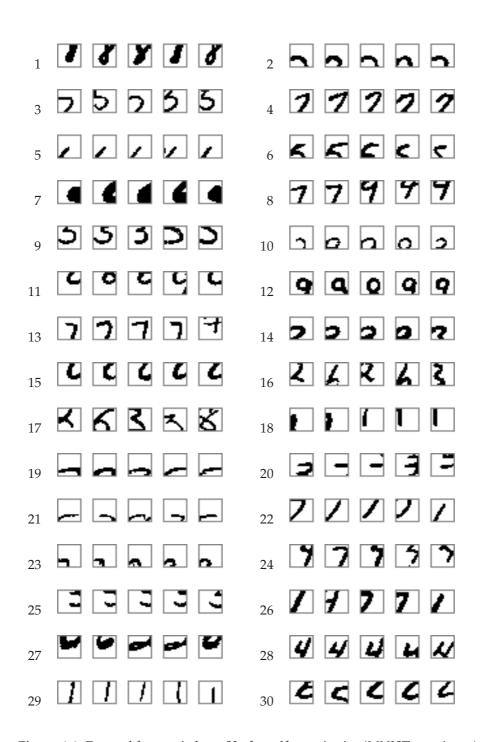

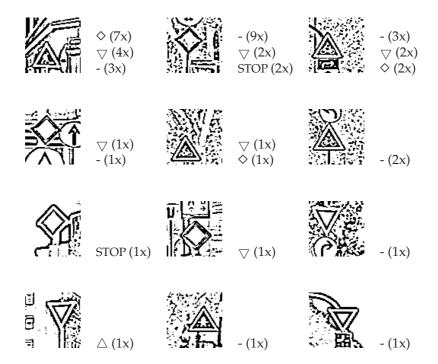

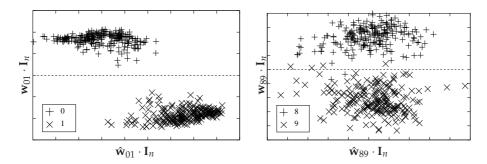

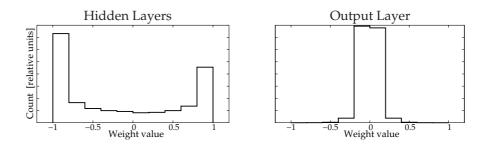

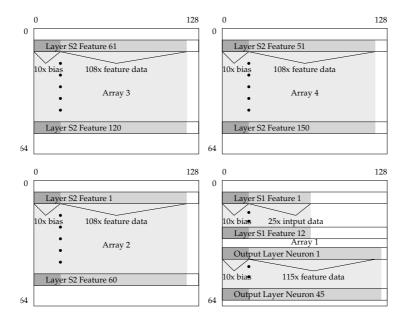

# **Working Environment**