# Dissertation

submitted to the

Combined Faculties for the Natural Sciences and for Mathematics of the Ruperto-Carola University of Heidelberg, Germany

for the degree of

Doctor of Natural Sciences

Presented by

Dipl.-Inf. Jochen Knopf

born in Mannheim, Germany

Oral examination: November 9<sup>th</sup>, 2011

Development, Characterization and Operation of the DCDB, the Front-End Readout Chip for the Pixel Vertex Detector of the Future BELLE-II Experiment

Referees: Prof. Dr. Peter Fischer

Prof. Dr. Johanna Stachel

#### **Zusammenfassung:**

#### Entwicklung, Charakterisierung und Betrieb des DCDB, dem Auslesechip des Pixel Vertex Detektors (PXD) im geplanten BELLE-II Experiment

Der BELLE-II Detektor ist eine Weiterentwicklung des BELLE Detektors am Forschungszentrum KEK im japanischen Tsukuba. Mit Letzerem konnte in der Vergangenheit die Existenz CP-verletzender Zerfälle erfolgreich nachgewiesen werden. Der ebenfalls weiterentwickelte Teilchenbeschleuniger SuperKEKB erzeugt eine Luminosität von  $8 \times 10^{35} \, cm^{-2} \, s^{-1}$ . Die damit einhergehenden Sekundärereignisse führen zu einer erheblichen Auslastung des Detektors, insbesondere des innersten Pixel Vertex Detektors (PXD). Um die geforderten physikalischen Leistungsmerkmale in diesem Umfeld erfüllen zu können, müssen höchste Anforderungen an die jeweilige Ausleseelektronik gestellt werden.

Das PXD Pixel Detektor System basiert auf der sogenannten DEPFET Technologie. DEPFET Transistoren vereinen die Teilchendetektion und die Verstärkung des resultierenden Signals in einem Element. Der DCDB Chip wurde entwickelt, um die Signale dieser Transistoren den Bedingungen im BELLE-II Detektor entsprechend zu messen und zu digitalisieren. Die vorliegende Ausarbeitung beschreibt die Fähigkeiten dieses Chips sowie dessen Implementierungsprozess. Mit Hilfe eines eigens entwickelten Testaufbaus wurde der DCDB umfassend charakterisiert. Die entsprechenden Ergebnisse werden hier dargelegt. Die Einsetzbarkeit dieses Chips in einem teilchenphysikalischen Messinstrument wird anhand eines DEPFET Detektor Prototyp Systems eindrucksvoll unter Beweis gestellt. Die Höhepunkte sind die Messung eines Zerfallsspektrums von Cd-109 sowie die erfolgreiche Durchführung eines Teilchenstrahlexperiments am CERN.

#### **Abstract:**

#### Development, Characterization and Operation of the DCDB, the Front-End Readout Chip for the Pixel Vertex Detector of the Future BELLE-II Experiment

The BELLE-II detector is the upgrade of its predecessor named BELLE at KEK research centre in Tsukuba, Japan, which was successfully used in the past to find evidence for CP violating decays. The upgraded SuperKEKB accelerator is specified to produce a luminosity of  $8 \times 10^{35} cm^{-2} s^{-1}$ . Consequently, the BELLE-II detector and particularly the innermost pixel vertex detector (PXD) suffers from enormous occupancy due to background events. Coping with this harsh environment while providing the required physics performance results in tough specifications for the front-end readout electronics.

The PXD pixel detector system is based on the DEPFET technology. DEPFET transistors combine particle detection and signal amplification within one device. The DCDB chip is developed to sample and digitize signals from these transistors while complying with the specifications of BELLE-II. The presented work illustrates the chip's features and describes its implementation process. The device is comprehensively characterized using an individually developed test environment. The obtained results are presented. The DCDB's ability to serve as a readout device for particle physics applications is demonstrated by its successful operation within a DEPFET detector prototype system. Highlights are a decay spectrum measurement using Cd-109 and the successful operation in a beam test experiment at CERN.

# Table of Contents

| CHAPT | er 1 Introduction                                                                                   | 1  |

|-------|-----------------------------------------------------------------------------------------------------|----|

| 1.1   | Motivation                                                                                          | 2  |

| 1.2   | The Challenge of SuperKEKB and BELLE-II                                                             | 3  |

| 1.3   | BELLE-II Experiment Overview                                                                        |    |

|       | 1.3.1 The SuperKEKB B-Factory                                                                       |    |

|       | 1.3.2 The Study Subjects                                                                            |    |

| 1.4   | 1.3.3 The BELLE-II Detector System                                                                  |    |

| 1.4   | rocus of the Presented Work                                                                         | /  |

| СНАРТ | ER 2 The PXD Vertex Detector for BELLE-II                                                           | 9  |

| 2.1   | The DEPFET Pixel Detector                                                                           | 10 |

|       | 2.1.1 The DEPFET Principle                                                                          |    |

|       | 2.1.2 The History of DEPFET Detectors                                                               |    |

| 2.2   | 2.1.3 Reading DEPFET Pixel Matrices                                                                 |    |

| 2.2   | 2.2.1 Impact Parameter Resolution                                                                   |    |

|       | 2.2.2 Occupancy                                                                                     |    |

|       | 2.2.3 Layer Radii                                                                                   |    |

|       | <ul><li>2.2.4 Frame Readout Time.</li><li>2.2.5 Modules and Dimensions.</li></ul>                   |    |

|       | 2.2.6 Pixel Geometries                                                                              |    |

|       | 2.2.7 Detector Thinning                                                                             |    |

|       | <ul><li>2.2.8 Front-End Readout System</li><li>2.2.9 Bump Bond Interconnection Technology</li></ul> |    |

|       | 2.2.10 Higher Level Readout System                                                                  |    |

| 2.3   | The SwitcherB Steering ASIC                                                                         | 25 |

|       | 2.3.1 Overview                                                                                      |    |

|       | 2.3.2 Channel Boosting 2.3.3 Overlapping Gates                                                      |    |

|       | 2.3.4 Operation Mode Details                                                                        |    |

| 2.4   | DCDB - The Drain Current Digitizer for BELLE-II                                                     | 31 |

| 2.5   | DHP - The Data Handling Processor                                                                   | 33 |

| CHAPT | ER3 The Analog Domain of the DCDB                                                                   | 37 |

| 3.1   | Overview                                                                                            | 38 |

| 3.2   | The Analog-To-Digital Conversion Principle                                                          | 38 |

| 3.3   | The Cyclic ADC Realization                                                                          | 40 |

| 3.4   | Details of the Building Blocks                                                                      | 41 |

|       | 3.4.1 The Current Receiver                                                                                     | 41 |

|-------|----------------------------------------------------------------------------------------------------------------|----|

|       | 3.4.2 The Current Memory Cell                                                                                  |    |

|       | 3.4.3 The Comparator                                                                                           |    |

|       | 3.4.4 Pre-Sampling cell                                                                                        |    |

|       | 3.4.5 Calibration Circuit                                                                                      |    |

|       | 3.4.6 Offset Current Compensation                                                                              |    |

| 3.5   | Configuration Summary                                                                                          | 48 |

| СНАРТ | TER 4 The Digital Domain of the DCDB                                                                           | 51 |

| 4.1   | General Considerations                                                                                         |    |

|       | 4.1.1 Digital Tasks                                                                                            |    |

|       | 4.1.2 From Full Custom to Synthesized Digital Logic                                                            |    |

|       | 4.1.3 Revision History                                                                                         |    |

| 4.2   | Logic Development                                                                                              |    |

|       | 4.2.1 Data Format Conversion                                                                                   |    |

|       | 4.2.2 Output Serialization                                                                                     |    |

|       | 4.2.3 Input Value Distribution for the Dynamic Offset Compensation                                             |    |

|       | 4.2.4 ADC Control Sequence Generation                                                                          |    |

|       | <ul><li>4.2.5 Clocking and Resetting Scheme</li><li>4.2.6 JTAG Configuration and Debugging Interface</li></ul> |    |

|       | 4.2.7 Digital Test Signal Injection                                                                            |    |

| 4.3   | Verification                                                                                                   |    |

|       | 4.3.1 Digital-Only Functional Verification                                                                     |    |

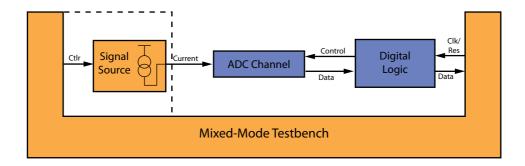

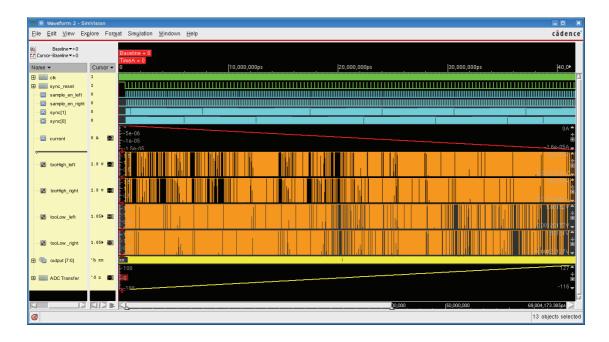

|       | 4.3.2 Mixed-Mode Simulation                                                                                    |    |

|       | 4.3.3 Concluding Remark                                                                                        | 64 |

| 4.4   | Standard Cell Library Development                                                                              | 64 |

|       | 4.4.1 Radiation Hard Standard Cell Library: First Approach                                                     | 66 |

|       | 4.4.2 Standard Cell Library: Second Approach                                                                   |    |

|       | 4.4.3 The Standard Cell Library for the DCDB                                                                   | 69 |

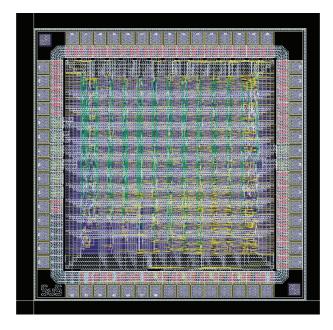

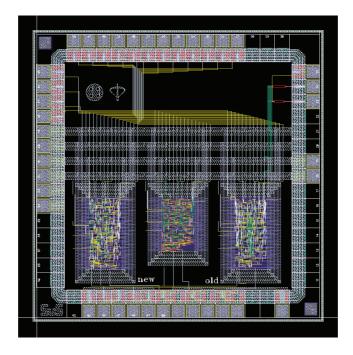

| 4.5   | Physical Implementation                                                                                        | 70 |

|       | 4.5.1 Constraining the Design                                                                                  | 71 |

|       | 4.5.2 Encounter: Standard vs. MMMC Flow                                                                        | 72 |

|       | 4.5.3 Synthesis                                                                                                | 73 |

|       | 4.5.4 Floorplanning and Placement                                                                              |    |

|       | 4.5.5 Power Planning                                                                                           |    |

|       | 4.5.6 Clock Tree Synthesis                                                                                     |    |

|       | 4.5.7 Signal Routing                                                                                           |    |

|       | 4.5.8 Timing Analysis                                                                                          |    |

|       | 4.5.10 Tape-Out and Design Transfer to the Virtuoso ADE                                                        |    |

| СНАРТ | TER 5 The DCDB Test Environment                                                                                | 85 |

| 5 1   | The Hardware Components                                                                                        | 94 |

| 3.1   |                                                                                                                |    |

|       | <ul><li>5.1.1 Electrically Interfacing the DCDB</li><li>5.1.2 The DCDB Test Board</li></ul>                    |    |

|       | 5.1.3 General Purpose FPGA Board                                                                               |    |

|       | 5.1.4 The DCDB Test Environment Hardware Setup                                                                 |    |

| 5.2   |                                                                                                                |    |

| 3.4   |                                                                                                                |    |

|       | 5.2.1 Complexity Distribution: Software vs. Hardware                                                           |    |

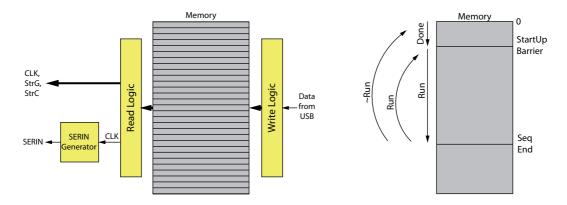

|       | 2.2.2 III COIICEPIAAI DII ACTAIC                                                                               |    |

|       | 5.2.3 DCDB Communication and Data Processing Issues                                                                                    | 92  |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|-----|

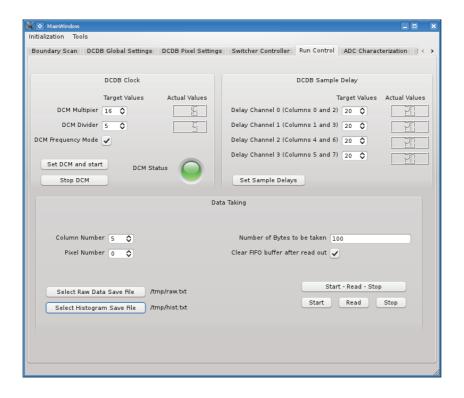

| 5.3   | The DCDB Test Software                                                                                                                 | 93  |

|       |                                                                                                                                        |     |

| CHAPT | TER 6 The DCDB-based Detector Prototype                                                                                                | 95  |

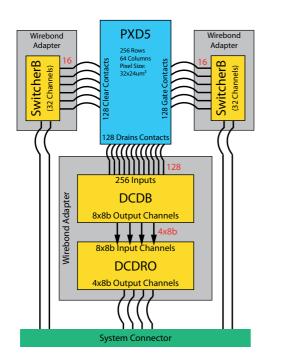

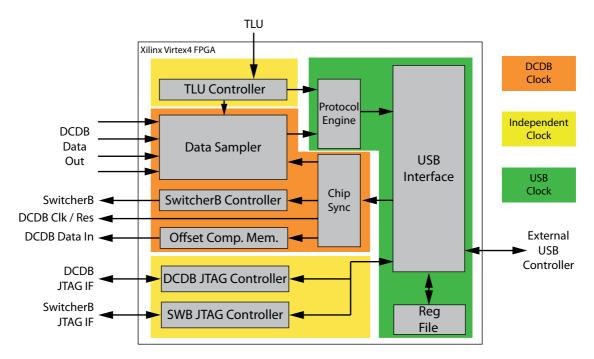

| 6.1   | The Hardware Platform                                                                                                                  | 96  |

|       | 6.1.1 DEPFET Detector and Switcher Chip Selection                                                                                      |     |

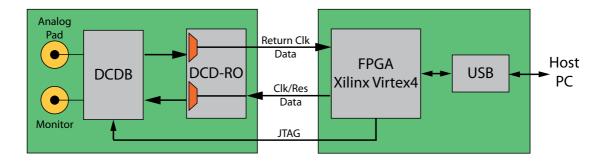

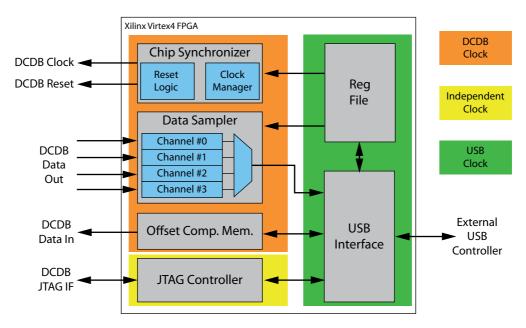

|       | 6.1.2 FPGA-based Controlling and Readout System                                                                                        |     |

|       | 6.1.3 The Hybrid Board                                                                                                                 |     |

| 6.2   | 6.1.4 Powering Scheme                                                                                                                  |     |

| 6.2   |                                                                                                                                        |     |

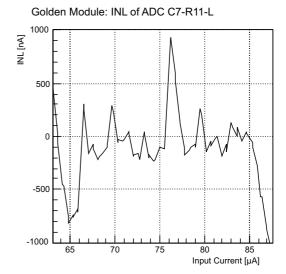

|       | 6.2.1 Overview                                                                                                                         |     |

|       | 6.2.3 Trailing Frames                                                                                                                  |     |

|       | 6.2.4 SwitcherB Controller                                                                                                             |     |

| 6.3   | The Data Acquisition Software                                                                                                          | 102 |

| СНАРТ | ter 7 DCDB Characterization                                                                                                            | 103 |

|       |                                                                                                                                        |     |

| 7.1   | Digital Functionality Checks                                                                                                           |     |

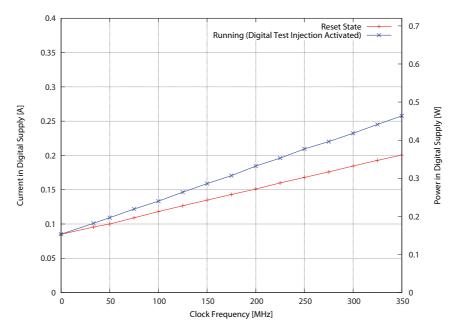

|       | 7.1.1 Power Consumption of the Digital Block                                                                                           |     |

|       | <ul><li>7.1.2 Clock Insertion Delay</li><li>7.1.3 Digital Test Signal Injection</li></ul>                                              |     |

|       | 7.1.4 Maximum Operation Speed                                                                                                          |     |

| 7.2   | Detailed Analog Channel Measurements                                                                                                   |     |

|       | 7.2.1 The Current Memory Cell                                                                                                          |     |

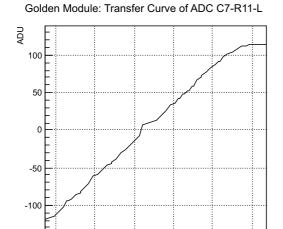

|       | 7.2.2 The Analog-to-Digital Converter                                                                                                  |     |

|       | 7.2.3 The Analog-to-Digital Converter: Stability Measurements                                                                          |     |

|       | 7.2.4 The Analog-to-Digital Converter: Dynamic Behaviour                                                                               |     |

|       | <ul><li>7.2.5 The Transimpedance Amplifier: DC Measurements</li><li>7.2.6 The Transimpedance Amplifier: Dynamic Measurements</li></ul> |     |

|       | 7.2.7 Overall Channel Performance                                                                                                      |     |

|       | 7.2.8 Power Consumption of the Analog Channels                                                                                         |     |

| 7.3   | Multi-Channel Measurements                                                                                                             | 129 |

|       | 7.3.1 Bad ADCs                                                                                                                         |     |

|       | 7.3.2 Offset Analysis                                                                                                                  |     |

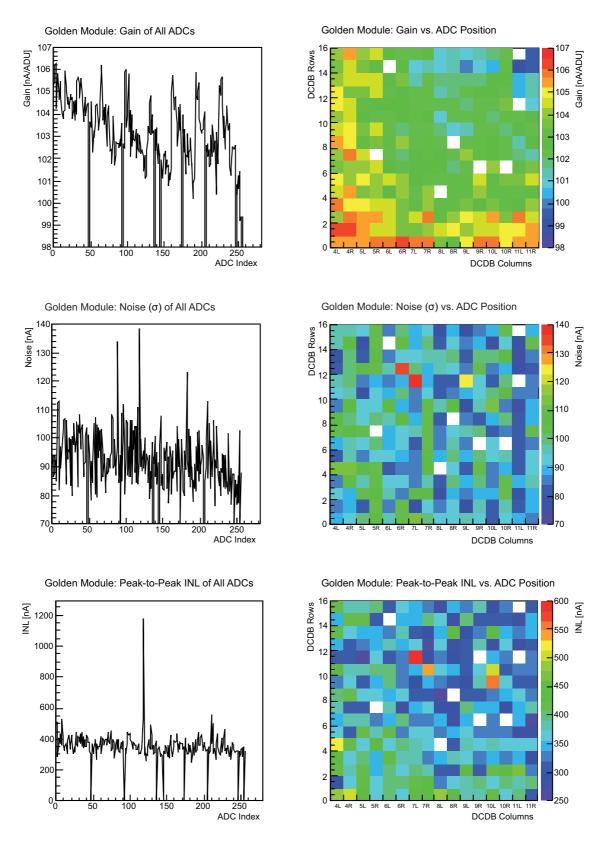

|       | 7.3.3 Gain Analysis                                                                                                                    |     |

|       | 7.3.4 Noise Analysis                                                                                                                   |     |

| 7.4   | 7.3.5 Integral Non-Linearity Analysis                                                                                                  |     |

| 7.4   | Conclusions                                                                                                                            | 134 |

| СНАРТ | TER 8 The Detector Prototype Operation                                                                                                 | 137 |

| 8.1   | System Simulation                                                                                                                      | 138 |

|       | 8.1.1 Motivation                                                                                                                       |     |

|       | 8.1.2 Simulation Setup                                                                                                                 |     |

|       | 8.1.3 Simulation Result                                                                                                                |     |

|       | 8.1.4 Concluding Remarks                                                                                                               |     |

| 8.2   | Reducing Pedestal Fluctuations                                                                                                         |     |

|       | 8.2.1 Theoretical Benefit                                                                                                              | 141 |

|       | 8.2.2 Optimization Algorithm         |     |

|-------|--------------------------------------|-----|

| 8.3   | Detector Operations                  | 144 |

|       | 8.3.1 First Imaging Measurement      | 144 |

|       | 8.3.2 Radioactive Source Measurement |     |

|       | 8.3.3 Clear Efficiency Studies       |     |

|       | 8.3.4 Beam Test Period at CERN       |     |

| CHAPT | TER 9 Conclusion & Outlook           | 149 |

| 9.1   | Conclusion                           | 150 |

| 9.2   | Summary of Own Contributions         | 151 |

| 9.3   | Outlook                              | 152 |

| Bibli | iography                             | 153 |

| Ackr  | nowledgements                        | 159 |

# Throduction

#### Abstract:

This introduction defines the presented work's relevance in the scientific world of experimental particle physics.

After a coarse description of particle physics experiments searching for evidence of symmetry violating processes in nature, the future BELLE-II experiment is brought into focus. In particular, the DEPFET vertex pixel detector sub-system of BELLE-II is of outstanding importance: within the DEPFET collaboration, this thesis emerged from the development of major parts of the readout electronic devices for this detector.

#### 1.1 Motivation

In modern physics, studying symmetries in physical transformations has lead to a deep understanding of natural phenomena. Searching, finding and understanding the preservation or violation of symmetries turned out to be a very powerful tool in discovering the secrets of nature. Some symmetries are quite obvious, others are very hard to find. Physicists have been making huge efforts for both, their theoretical description and their experimental verification, historically, often with surprising results.

The following three fundamental symmetries, as well as the combination of those, have been of very strong interest:

- Charge conjunction C: transformation of a particle into its antiparticle

- Parity P: transformation of the location  $r \rightarrow -r$

- Time reversal T: transformation of the time  $t \rightarrow -t$

Very general considerations about the principles of symmetries lead to the fact that there is no consistent theory which allows the violation of the combined symmetry  $C \cdot P \cdot T$  in any transformation. However, there are transformations that violate a single one or a combination of two of those. A very important example is the combined symmetry of charge conjunction and parity  $C \cdot P$ . For a long time, physicists assumed that any system would be invariant under the  $C \cdot P$  symmetry. But in 1964, James Cornin, Val Fitch et.al. found a violation of this symmetry in a kaon decay experiment [1]. This discovery not only lead to the Nobel Prize of Physics in 1980, but also to an enormous excitation in the physics community. At that time, none of the present theories could explain this observation. The first theoretical description of  $C \cdot P$  violating transformations was proposed in 1972 by Makoto Kobayashi and Toshihide Maskawa [2]. Their model extended the quantum field theory, so that finally the experiment of Cornin and Fitch could be explained.

Five years later, in 1977, S. W. Herb et. al. [3] found evidence for the existence of the b-quark and therefore B-mesons. The Kobayashi-Maskawa model predicted that neutral B-mesons would have the same  $C \cdot P$  properties as kaons, but with a significantly higher cross section. This fact gave the chance for an experimental verification of this theory and therefore, in the following years B-factories and appropriate detector systems were developed. The most important ones were the BABAR experiment at SLAC at Stanford, USA, and the BELLE experiment at KEK at Tsukuba, Japan. The independent measurements of the two collaborations confirmed the model with impressive agreement [4]. Nowadays, the Kobayashi-Maskawa model and hence the  $C \cdot P$  violation is well established in the Standard Model.

However, there must be more to discover! It was back in 1964 when Andrei Sakharov claimed that a  $C \cdot P$  violation must be the reason for the inequality of matter and antimatter in the universe [5]. The effect of  $C \cdot P$  violation described by the Kobayashi-Maskawa model, however, is not strong enough [6]. There must be other, yet undiscovered sources of  $C \cdot P$  violations in nature. Obviously, the state-of-the-art high energy physics experiments are either not precise enough, or simply do not reach the necessary energy level. Current developments of future particle accelerators and detectors are aiming to cope with both insufficiencies. The Large Hadron Collider at CERN with its experiments ATLAS and CMS try to push the energy frontier up to a

centre-of-mass energy of  $14 \, TeV$ . Others, like the LHCb (also LHC, CERN) for example, are designed for enhancing the precision of the measurements and thereby focusing on rare events. The precision measurement experiment SuperB at INFN in Italy is currently being planned.

Another representative of the latter group will be the BELLE-II experiment at the planned SuperKEKB accelerator at KEK in Japan. The BELLE-II experiment is currently under development and is going to be an upgrade of the predecessor experiment named BELLE. The new high precision detector system is intended to reveal unknown deviations from the Standard Model in strongly suppressed processes.

The development of the BELLE-II experiment started in December 2008 by forming the BELLE-II collaboration. As one of its members, the DEPFET collaboration is going to provide the inner layer vertex sub-detector (PXD) system. The presented dissertation emerged from the design and the development of the front-end readout electronics for this sub-detector system.

# 1.2 The Challenge of SuperKEKB and BELLE-II

The success of BELLE was not only the excellent experimental verification of the  $C \cdot P$  violation that is predicted by the Kobayashi-Maskawa model. Beyond that, it also indicated, that there would be more to find. Indeed, results exist that are - conservatively speaking - hard to explain with the present understanding of nature. Numerous examples are given in [7]. They may hint to deviations from the Standard Model. In order to prove this it is necessary to have a closer look. Technically, this means to produce the physically interesting and mostly very rare events with a significantly higher rate than before, because in some cases actual measurement errors are still limited by experimental statistics. Increasing the relevant data set may eventually allow for well-grounded statements of New Physics. If so, mankind would have proceeded to identify yet unknown structures beyond those currently explained by the Standard Model. The key is to increase the overall number of produced and captured interactions enormously. This goal is addressed by BELLE-II and SuperKEKB.

From the accelerator's point of view, this requirement translates into an increase of luminosity. Since the luminosity is proportional to the beam current and inversely proportional to the beam's cross section, there are mainly two ways to go. The first one is to increase the number of particles in the beam. The second one is to narrow the beam by applying better focusing. Both options have been discussed by the SuperKEKB accelerator designers. Currently, a compromise with focus on the latter one, the so called *nano-beam* option, is the favourite [9].

For the detector system, however, the increased luminosity of the accelerator is fairly challenging, since there is not only an increase in those events that are intended to be studied. There is also a significant increase in second order events, the so called *background*. Particles produced by background events hit the detector just like those produced by the main events do, with considerable effect on the various sub-detectors. Depending on the type of sub-detector, they are causing at least higher occupancy and therefore a higher load on the readout devices, or, in worst case, even higher dead time and performance degradation.

Four main sources for background effects have been identified in the previous KEKB/BELLE setup [8]: beam gas scattering, Touschek scattering, synchrotron radiation and radiative Bhabha scattering. A lot of simulation effort has been put in already in order to find out how to extrapolate from these individual background contribution towards a realistic estimation of the background levels for BELLE-II and there are still some unanswered questions about it. Nevertheless, a conservative pre-estimation results in an increase of background hits in the detector by a factor of 20, while the rate of main events will increase by a factor of 50 [9]. Due to this harsh environment, the primary requirement for the BELLE-II detector system will be to at least maintain the performance of BELLE while coping the higher background.

# 1.3 BELLE-II Experiment Overview

#### 1.3.1 The SuperKEKB B-Factory

Like the predecessor KEKB, the SuperKEKB is an asymmetric positron-electron collider. Electrons and positrons are accelerated in two separate rings and there is a single crossing point, the so called *Interaction Region (IR)*, where the two beams collide.

As already mentioned in section 1.1, the main purpose of the SuperKEKB is to produce B-mesons. First of all, using an electron-positron collider is a quite reasonable choice, since the acceleration of those particles to a certain energy level can be done with very high accuracy. This is necessary in order to exactly find the  $\Upsilon(4S)$  resonance in the centre-of-mass energy  $(10.58\,GeV)$ , at which the B-meson pair production (mass:  $m_{B^\pm} = 5279.15 \pm 0.31 MeV/c^2$   $m_{B^0} = 5279.53 \pm 0.33 MeV/c^2$  [13]) is very likely. Secondly, using asymmetrically accelerated particles for the collisions is very useful, because in that case the centre-of-mass is moving relatively to the detector (Lorentz boost). Therefore, the various decays in the B-meson decay chain are locally separated. The decay products are detected at different space points which simplifies the event reconstruction.

The current design of the SuperKEKB plans that electrons are accelerated in the high energy ring (HER) to 7GeV/c and positrons are accelerated in the low energy ring (LER) to 4GeV/c. The crossing angle of the two beams is 92mrad and the target luminosity at the point of interaction is calculated to be  $8\times10^{35}cm^{-2}s^{-1}$ , which is an improvement by a factor of almost 38 compared to KEKB. A full set of machine parameters can be found in [9].

# 1.3.2 The Study Subjects

Once the B-meson are created via the  $\Upsilon(4S)$  resonance, they decay into lighter particles after a very short period of time. Measuring these decay vertices, in terms of quantity and position for example, is the key to determine their inherent  $C \cdot P$  violation parameters.

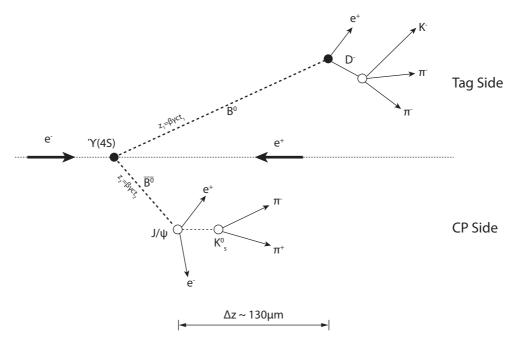

A very prominent example for such a decay is illustrated in figure 1-1. Here, a pair of neutral B-mesons  $(B^0\overline{B^0})$  is created, where the one decays into a D and a charged lepton (tag side), while the other decays basically into a  $J/\Psi$  (CP side). A speciality of this

**Figure 1-1** Exemplary decay mode of neutral B-mesons to be studied with the BELLE-II detector [10].

decay mode is that both mesons,  $B^0$  and  $\overline{B^0}$ , can go both ways and the only chance to clarify the situation is by determining the charge of the lepton on the tag side [11]. The  $C \cdot P$  violation parameters in this case are obtained from the time difference  $\Delta t = t_1 - t_2$  of these decays, which is typically in the order of a picosecond. As explained above, the measuring process is simplified by using the trick of an asymmetric collider. For the given machine parameters, the created particles are boosted by a factor of  $\beta \gamma = 0.283$ , which translates into a spatial separation of about  $85 \mu m$  per picosecond. Thus, the time difference is actually measured via the spatial separation of the vertices, which are reconstructed using the signals introduced by further decay products in the surrounding detector.

#### 1.3.3 The BELLE-II Detector System

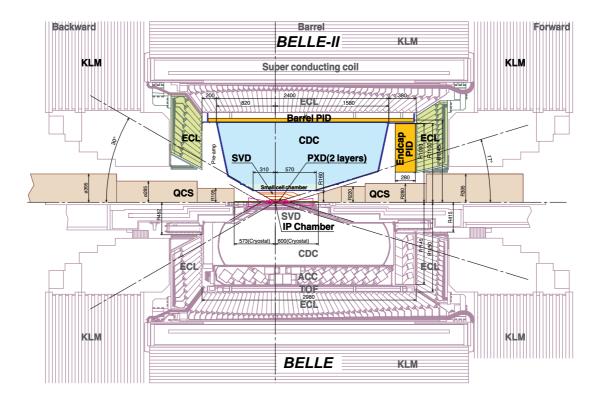

The BELLE-II detector system is located around the Interaction Region. It is built up using different types of sub-detectors, arranged in the typical barrel fashion. A superconducting solenoid with an inner radius of 1.7m is providing a magnetic field of 1.5T in order to allow for particle identification. A corresponding schematic drawing is presented in figure 1-2.

The innermost detector sub-system is a vertex detector. It provides an excellent spatial resolution and therefore allows for the reconstruction of B-meson decay vertices. Moreover, high precision vertex reconstruction has been proven to be a powerful tool to identify and reject background events [12]. The vertex detector is built up using six layers of solid state detectors. The four outer layers are double-sided silicon strip detectors (SVD), while the two inner ones are pixel detectors based on the DEPFET principle (PXD). A lot more details about the PXD in particular can be found throughout

this work, since it emerged from the development of the readout electronics for this detector.

The vertex detector is surrounded by the central drift chamber (CDC). It is not only used for the reconstruction of charged tracks and precise momenta measurements, but also as a trigger source. Additionally, it can be used as particle identification device for low momentum tracks that loose all their energy within the chamber's gas volume.

Outside of the central drift chamber, a particle identification system is located (PID). Its main capability is the separation of kaons and pions at a nominal energy of 4GeV/c [14]. To this end, it uses quartz radiators that allow for the emittance of photons by crossing particles due to the Cherenkov effect. Particle information is then derived from time and location of the photon detection. In addition, a particle identification system based on the ring-imaging Cherenkov detector principle is placed into the forward end cap.

The PID is enclosed by an array of electromagnetic calorimeter elements for precise energy measurements. They are mounted in a barrel shape around the beam pipe. This barrel is closed by more of those elements in both end caps. The calorimeter elements themselves are built up using a tower structure of CsI scintillator crystals. Each of them will be tilted individually in order to project directly to the interaction region.

The outermost detector sub-systems is a  $K_L$  and muon detector, located outside of the superconducting solenoid. This detector is built up using a sandwich structure. There are arrays of massive iron plates as stopping material with glass-electrode resistive plate chambers in-between.

**Figure 1-2** Schematic of the BELLE-II detector system (upper half) in comparison to its predecessor BELLE (lower half) [9].

#### 1.4 Focus of the Presented Work

The main focus of this work is placed on the electronic devices of the front-end readout chain for the pixel vertex detector (PXD) of BELLE-II.

Chapter 2 begins with a presentation of the DEPFET transistor, the actual detection device of the PXD. Afterwards, the technical specification parameters of the detector and its readout devices are derived from the physics aspects in the BELLE-II experiment. The front-end readout ASICs<sup>1</sup> of the detector system are introduced. One of these, the *Drain Current Digitizer for BELLE-II* (DCDB), is the major subject of the presented work. It is used to convert the analog electrical signals of the detector into digital data.

The DCDB is developed in a team effort by Dr. Ivan Peric and Jochen Knopf (the author) at the Chair of Circuit Design, Heidelberg University. The chip's analog domain, developed by Dr. Ivan Peric, is described in chapter 3. Its digital domain is the contribution of Jochen Knopf and is comprehensively explained in chapter 4.

Beyond the participation in the development of the DCDB, its testing, characterization and operation are further major contributions of the author and are therefore outlined in this work. The chapters 5 and 6 describe the development of a chip testing setup and a DCDB-based DEPFET prototype system respectively. Using these environments, the DCDB is characterized and the results are presented in chapter 7. Finally, chapter 8 presents evidence for the DCDB's successful operation together with a DEPFET detector. The highlights are results from a radioactive source measurement as well as the system's operation in a beam test at CERN.

Since the DCDB is a crucial element in the readout chain of the PXD detector for BELLE-II, its proper functionality and the achievement of major quality parameters are of outstanding importance for the entire project. In that context, this work aims for both, providing the chip itself and proving its adequateness for the target job. Thus, it is of great relevance for both, the DEPFET and the BELLE-II collaborations.

-

<sup>1.</sup> Application-Specific Integrated Circuit

# The PXD Vertex Detector for BELLE-II

#### Abstract:

The second chapter of this thesis focuses on the inner layer vertex detector setup for BELLE-II. Starting with an explanation of the DEPFET transistor principle, the assembly of the detector's half ladder building block is presented. Major specifications for both, detector and readout electronics, are derived from physics aspects of the BELLE-II experiment. Finally, the readout ASICs used are introduced. These are the SwitcherB, the DCDB and the DHP, which were developed exclusively for this project.

#### 2.1 The DEPFET Pixel Detector

#### 2.1.1 The DEPFET Principle

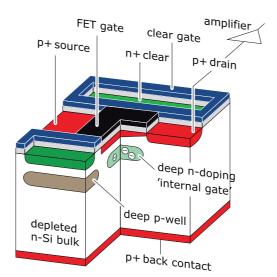

The DEPFET<sup>1</sup> principle describes the combination of radiation detection and signal amplification in a single transistor. A MOSFET transistor (JFET is also possible) is integrated onto a n-doped silicon detector substrate. Figure 2-1 provides an example schematic drawing of such a device. The substrate is fully depleted by means of sideward depletion, a technique that is well known from silicon drift chambers. While the substrate is kept at a constant potential, negative voltages (relative to the substrate potential) are applied to the top and the bottom of the substrate using p<sup>+</sup> contacts, in order to deplete it from both sides. Once the voltages are low enough, the substrate is fully depleted while still having a tiny horizontal layer of "high" bulk potential where the two depletion volumes meet. By relatively varying these voltages, the depth of the bulk potential layer inside the substrate can be influenced. For the DEPFET operation, it is shifted right below the top surface of the detector substrate, that is where the transistor is located. Additionally, at the same depth as the bulk potential layer, a n<sup>+</sup>-doped region is implanted into the substrate just underneath the gate of the transistor. Since this n<sup>+</sup>-doped region is depleted as well, only the atomic cores are left and therefore form the potential minimum for electrons inside the substrate.

Once such a device is hit by a particle with sufficient energy, electron-hole pairs are created. Due to the electric field inside the substrate caused by the depletion voltages, the

Figure 2-1 Schematic drawing of a DEPFET transistor [9]. The transistor structure is integrated onto the detector substrate. A deep n<sup>+</sup>-doped region underneath the FET gate is acting as the potential minimum for electrons. Signal electrons get trapped there and modulate the transistor current. There are clear contacts and clear gates on both sides of the transistor structure. Deep p-doped regions underneath the clear contacts prevent signal electrons from getting attracted by the clear contact rather than the internal gate.

<sup>1.</sup> DEpleted P-channel Field Effect Transistor

free electrons and the holes drift apart and hence cannot recombine. While the holes drift towards the depletion voltage contacts, where they can recombine, the free electrons accumulate at the potential minimum underneath the transistor gate. Once there is a p-channel established between the source and the drain contact of the transistor by applying an appropriate voltage to its gate, the p-channel is modulated also by the electric field of the electrons residing in the potential minimum. In other words, the potential minimum is acting as an "internal gate". That means first of all, electrons created by incidental particles are measurable due to their influence on the p-channel of the transistor and therefore on the current flowing through it. Secondly, because of the transistor effect, the signal is amplified simultaneously. Thirdly, the signal electrons are measured indirectly, so the measurement is neither destructive, nor is there any charge transfer necessary. Fourthly, the fully depleted substrate leads to a very low input capacitance, so the measurement can be performed with very low noise, even at room temperature.

Having a non-destructive measurement scheme, however, requires for some kind of mechanism to take signal electrons away from the internal gate once the measurement is finished. Therefore, another n-contact, the *clear* contact, is introduced to the substrate right next to the transistor. By applying a sufficiently high positive voltage to that contact, a punch-through is established, which removes the electrons from the internal gate. The only drawback of this solution is that special care is necessary in order to prevent signal electrons from drifting to the clear contact rather than to the internal gate, since this would cause signal loss. The approved way to cope with this issue is to shield the n-doped region of the clear contact by a deep p-doped region underneath. Additionally, another gate structure is introduced, the so-called *clear gate*, which is located just above the gap between clear contact and internal gate. By means of the cleargate, the electric fields inside the substrate can be influenced and therefore, the optimal working conditions can be adjusted.

#### 2.1.2 The History of DEPFET Detectors

It was back in the late 1980s, when the two scientists J. Kemmer (Technische Universität München) and G. Lutz (Max-Planck-Institut für Physik und Astrophysik, München) were engaged in studying the innovative potential of silicon drift chambers. With the microelectronic technology present at that time, they found a way to combine the detection of radiation and the amplification of the induced electronic signal not only on the same chip, but also within a single transistor. Their idea was published in 1988 [15], the birth of the DEPFET detectors. The success of an experimental proof of principle was reported in 1990 [16].

During the following years, the idea was improved continuously. In co-operation with the Universities of Bonn and Dortmund, suitable electronics for steering DEPFET transistor prototypes as well as measuring their signal were developed. In 1997, the success of single pixel measurements [17] justified the development and production of larger arrays of DEPFET transistors. Finally, three years later, P. Fischer published a paper on the first successful operation of a  $32 \times 32$  pixel imaging matrix based on DEPFET transistors using 60keV gamma rays and an IR laser [18].

Since that time, the DEPFET technology was ready for real use. Prototype systems for a variety of applications were developed in order to show the performance of the new

detector type. Not only biomedical devices [19], but also prototypes for X-ray astronomy missions like XEUS, BepiColombo and others were presented. Beside that, however, in 2003, the three partner institutes, MPI, University of Bonn and University of Mannheim formed the DEPFET collaboration. The goal was to develop DEPFET-based systems for high energy physics experiments. The first one in a series of high energy physics prototypes (working title: PXD4) was designed in 2003 for the TESLA experiment at DESY, Germany [20]. In 2006, the DEPFET collaboration decided to aim for a vertex detector system for the planned International Linear Collider (ILC) [21]. A new prototype detector device (working title: PXD5) was developed, customised for the ILC requirements.

Since 2005 the DEPFET collaboration has been triggering the interest of other groups working the field of high energy physics. Some of them, in particular groups from Prague, Karlsruhe, Valencia, Göttingen, Munich, Krakow and Giessen, joined the collaboration and became inherent parts of it. Nowadays, the collaboration is focused on the development of a vertex detector system for the future BELLE-II experiment at KEK, Japan. A new prototype (working title: PXD6) suitable for the BELLE-II requirements is currently being developed. The presented work is a part of this new prototype system and therefore continuing the history of DEPFET detectors.

In parallel to the work of the DEPFET collaboration, the DEPFET detector technology is still being used for X-ray experiments. The latest one is the so-called XFEL project, which is going to be a free electron laser experiment at DESY, Germany, started in the year 2008 [22].

#### 2.1.3 Reading DEPFET Pixel Matrices

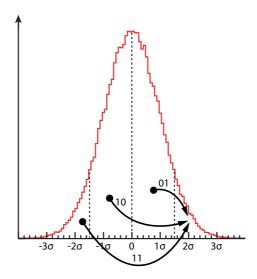

The straightforward way to realize a particle detector device based on DEPFET transistors is to arrange a number of transistors in a matrix structure, regarding each transistor as a pixel of an imaging frame. In order to capture a frame, each pixel of the matrix needs to be read. Reading in this context means the determination of the amount of signal electrons in the transistor's internal gate. As described in section 2.1.1, the signal electrons residing in the internal gate modulate the current from source to drain. This fact, however, causes the requirement for two separate measurements. Beside the measurement of the potentially modulated current, the offset current needs to be determined as well. That is the current flowing through the transistor while the transistor is switched on, but the internal gate is empty (known as pedestal current). Hence, the difference of both measurements is regarded as the signal.

#### Reading a Single Pixel

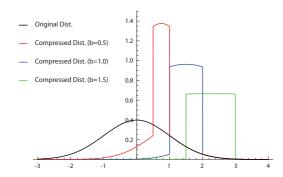

The need for two measurements for signal determination leads to two main strategies of reading DEPFET pixels. The first one is the so-called *double correlated sampling*. That means, whenever a pixel is addressed, two separate measurements are performed. The first measurement samples the pedestal current together with a possible modulation due to signal electrons. The second measurement is performed directly after the signal is erased by clearing. Afterwards, the difference of the two measurements is calculated in order to determine the signal.

The second strategy is called *single sampling*. Compared to the double correlated sampling, the second measurement is skipped here. The signal is calculated using a stored pedestal value. Thus, the pedestal current needs to be determined and stored before, during a dedicated pedestal measurement. The single sampling is almost twice as fast as double correlated sampling, since only half of the measurements are performed. The time consumption of the clearing can be neglected compared to that of the sampling. However, the quality of the signal determination is directly dependent on the quality of the stored pedestal value. Variations among pixels need to be considered as well as variations in time due to temperature, radiation and other effects.

#### Combining Multiple Pixels to a Matrix Structure

Beside the strategy for reading single pixels, the number of readout channels is the next parameter to be optimised. In principle, there are two extremes. On the one hand, only a single readout device can be sufficient. In that case, all the pixels of the matrix need to be multiplexed to the single readout device subsequently, which is obviously very time consuming. On the other hand, every pixel of the matrix could have its own readout device. In this way, the reading of the entire matrix was accelerated enormously. However, depending on the size of the matrix, a huge amount of not only readout devices but also interconnections would be necessary, which is hardly feasible for most realistic matrices.

The approved way is a compromise between the two extremes. To this end, the fact is used, that signal electrons residing in the internal gate of a DEPFET transistor are not able to set up a conducting channel between source and drain, but only to modulate a signal onto an existing channel that is switched on via the transistor's external gate. Groups of DEPFET transistors, typically arranged in a column of the matrix, share a single readout device by simply connecting all of them in parallel to the readout device's input. By external steering signals, it must be ensured that at any time only a single pixel of the group is switched on, while all others are switched off<sup>1</sup>. The detector matrix is then built using several of these grouped columns in parallel. Pixels in the same row can then share the same pair of gate and clear steering signals, so that they are switched on/ off and erased at the same time. This results in a number of readout devices that is equal to the amount of pixels in one dimension of the matrix.

Using this readout mode leads to the fact that pixels in the same row of the matrix are read out in parallel, while pixels in the same column are read out sequentially. This row-wise readout mode is known as *rolling shutter*.

#### Source Follower vs. Drain Readout

The way of connecting the grouped DEPFET transistors in parallel to a single readout device is not just a technical detail, but again an important design decision. In principle, there are two possibilities, the so called *source follower readout* or the *drain readout*. On the level of the DEPFET transistors, there is only a single difference between these two, namely whether the readout device is connected to a common source node (source

<sup>1.</sup> In principle it is also possible to have more than one pixel of the group being switched on. This method is called *ganged pixel readout*, but it is not considered here.

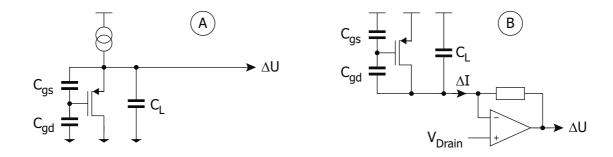

**Figure 2-2** Generic and simplified schematic of a DEPFET transistor in source follower (A) and drain readout (B) mode [23].

follower) or a common drain node (drain readout). From the electrical point of view, these methods are completely different.

In the source follower configuration, as shown in figure 2-2 (A), a current source is forcing current through the DEPFET transistor, during which the voltage at the transistor's source node is measured. A variable conductivity of the DEPFET transistor induced by charge residing on its internal gate results in variable potential at this node.

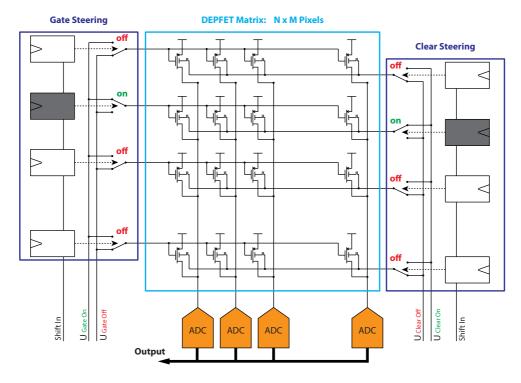

Figure 2-3 DEPFET pixel matrix readout arrangement (drain readout configuration). Pixels in the same column share a common readout drain line, while pixels in the same row are steered using the same gate and clear signals.

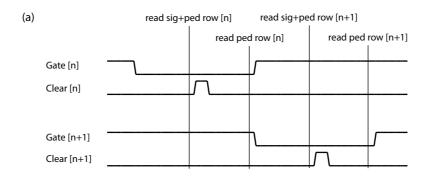

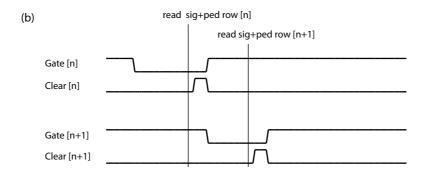

Figure 2-4 Example steering sequence for a DEPFET matrix. Gate and clear signals for two consecutive rows are shown. Note: DEPFET pixels are basically PMOS transistors, therefore, the gate signals are low-active. (a) Steering sequence in double correlated sampling mode. (b) Steering sequence in single sampling mode.

However, the signal rise time can be severely degraded by the line capacitance  $C_L$  of the common source node. It can be described by the following equation [23]:

$$t_r = \frac{C_L \left(1 + \frac{C_{gs}}{C_{gd}}\right) + C_{gs}}{g_m} \cdot 2.2$$

This settling time can easily reach several microseconds, so that the source follower configuration is not suitable for high speed applications.

In the drain readout configuration, the situation is completely different. The DEPFET transistor is operating as current source, and the signal is a change in its current. A simple amplifier can be connected to the common drain line, keeping its potential constant. Therefore, there is no need to charge and discharge the line capacitance  $C_L$ , so that it does not affect the speed anymore. The drawback of this configuration is, however, that fluctuations in the device thresholds and voltage drops on the source traces are amplified by the DEPFET transistor. As an effect for large matrix arrangements, fairly large current fluctuations among the pixels can appear.

An example DEPFET matrix readout arrangement using the drain readout configuration is illustrated in figure 2-3. Figure 2-4 shows the corresponding steering signal waveforms for single and double correlated sampling.

# 2.2 The PXD Detector System for BELLE-II

#### 2.2.1 Impact Parameter Resolution

The major goal of the barrel-shaped inner layer pixel vertex detector of BELLE-II (PXD) is to enhance the tracking accuracy of the surrounding SVD detector by improving the impact parameter resolution. That is the measure of how good a decay position close to the interaction region can be reconstructed [58]. The target resolution is driven by physics aspects which demand a precision of about  $20\mu m$  [9]. The equation for the impact parameter resolution  $\sigma$  in the case of a two layers detector, located at radii  $r_1$  and  $r_2$ , with an intrinsic spatial resolution  $\sigma$  of  $\sigma$ 0 is made up of a geometric term and a multiple scattering term [25] [26]:

$$\sigma = \sqrt{\sigma_{geo}^2 + \sigma_{MS}^2}$$

$$\sigma_{geo} = \sqrt{\frac{r_2^2 + r_1^2}{(r_2 - r_1)^2}} \cdot \sigma_0$$

$$\sigma_{MS} = r_1 \cdot \frac{13.6 MeV}{\beta c p (\sin \theta)^k} \cdot z \cdot \sqrt{\frac{x}{X_0}} \cdot \left[ 1 + 0.038 \ln \left( \frac{x}{X_0} \right) \right]$$

For the latter, p is the momentum of the incident particle,  $\theta$  is its track polar angle and z the charge. x is the thickness of the detector material and  $X_0$  its radiation length. k = 3/2 for the resolution in  $r \times \Phi$  and k = 5/2 for the z-projection.

The geometric term depends only on the distances of the detector layers to the interaction point and their spatial resolution. Beside the direct influence of  $\sigma_0$ , the resolution is optimal for a minimized radius of the inner layer and a simultaneously maximized radius of the outer layer, which acts as lever arm. Considering the multiple scattering part of the equation, the detectors contribution to its minimization is again a close distance of the inner layer and a reduction of the detector's material. These are the major boundary conditions. Beyond that, extensive performance simulations yield to a set of design parameters which constrain the PXD detector development. The consequences of these simulations are discussed in the following.

# 2.2.2 Occupancy

The general issue that has to be handled in the context of parameter optimization is the detector's occupancy due to hits that are caused background events. The expected rate of background events is of course depending on the luminosity of the SuperKEKB accelerator. But this is certainly not a subject for optimizations here, so the luminosity

<sup>1.</sup> A simplifying assumption here is that the intrinsic spatial resolution is equal for both detector layers. This is not the case for the BELLE-II's PXD detector.

and thus the level of background events is considered given. The corresponding hits in the detector are of no interest for physical studies and only degrade the effective efficiency of reconstructing real events. So primarily, the basic question here is how much occupancy in a frame is allowed by the track reconstruction mechanisms in order for the PXD to improve the impact parameter resolution. The answer is given by Monte-Carlo simulations [33] (assuming baseline design parameters for the involved elements): about 1% per frame is fairly acceptable, for higher occupancies than 2.3% the PXD is not helping anymore. This result has to be respected by any optimization.

#### 2.2.3 Layer Radii

The lower boundary for the radius of the detector's innermost layer is given by the existence of a beam pipe at the interaction region. Referring to its latest design [27], the beam pipe has an outer radius of 12mm. So by keeping a little safety distance, mounting the detector down to about 13mm radius is mechanically feasible. Simulations are made in order to find out how much the radius could be further increased while not unacceptably degrading the effective resolution, since the occupancy scales roughly with  $1/r^2$  [9]. The result is that an increase to 14mm is only hardly degrading the effective resolution [28]. Although this is still a tough distance, it is decided to fix the radius of the BELLE-II's innermost pixel detector layer at that value. The position of the second layer is less critical and is mainly driven by mechanical and mounting constraints. Its radius is set to 22mm.

#### 2.2.4 Frame Readout Time

With the known radii of the detector layers, in particular that of the innermost one which is most affected by background hits, it is the job of the readout system to make sure that the occupancy per frame is kept within the defined limits. This is because the occupancy scales with the time required to read a frame.

Another general requirement for the readout time is derived from system aspects. The bunch circle time at the SuperKEKB accelerator is  $10.06 \mu s$ . From the data analysis's point of view it is desirable to read the frames synchronously to that.

With respect to what is assumed to be feasible for the readout system, a frame readout time of  $20.12\mu s$  is set as the baseline of the PXD detector. Simulations showed that the resulting expected occupancy due to background hits is about 0.4% [29] and thus fairly within the limits.

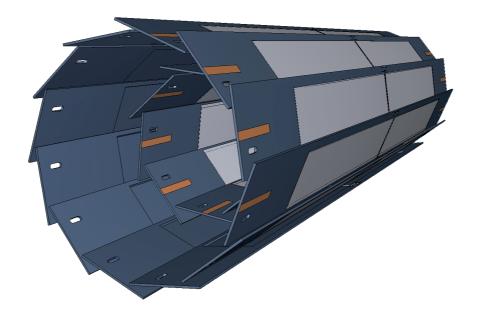

#### 2.2.5 Modules and Dimensions

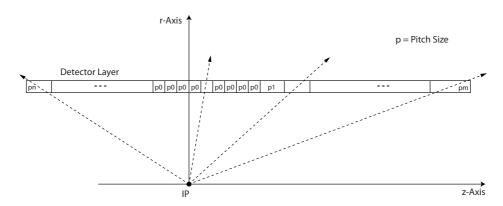

The cylindric shape of an ideal barrel detector is approximated by a polyangular arrangement of planar modules, the so-called *ladders*, as illustrated in figure 2-5. Eight ladders form the inner layer, while twelve of them are used for the outer one. The ladders are mounted onto solid support structures that are placed at both ends of the barrel. These

<sup>1.</sup> Since SVD data is used together with that from the PXD, the second layer's data is not primarily used as lever arm for the track reconstruction.

Figure 2-5 Drawing of the DEPFET vertex detector arrangement around the beam pipe at the interaction region [9]. A cylindric shape is approximated using flat ladder modules. The innermost layer comprises eight ladders at a radius of 14mm. The second layer is made of twelve elements resulting in a 22mm radius.

**Figure 2-6** Picture of a DEPFET vertex detector assembly model. It shows a dummy beam pipe with the DEPFET vertex detector's mechanical support structures and ladder demonstrators mounted onto it. A can is used as a size reference [31].

support structures themselves are fixed to the beam pipe. A model of that assembly is presented in figure 2-6. The ladders are composed of two *half-ladder* modules, the major building block of the PXD detector, by gluing their top edges together. This is a self-supporting all-silicon module that serves as a substrate for the sensitive pixel area,

**Figure 2-7** Illustration of the variable pixel pitch strategy [32].

chip housing as well as the interconnection platform at the same time. The width of the sensitive area is geometrically given by the polyangular arrangement and the aim of 100% coverage in  $r \times \Phi$  plane. It is defined as 12.5mm for both layers. Its length along the beam pipe is primarily derived from the polar angular acceptance range of the SVD detector:  $17^{\circ} < \theta < 150^{\circ}$  [9]. By additionally taking the layout and the geometric issues into account, the lengths are set to 44.8mm for the inner layer and 61.44mm for the outer one. The overall sizes of the half ladders are  $15.4mm \times 67.975mm$  and  $15.4mm \times 84.975mm$  respectively. The ladder designs are not fixed yet, so the numbers given here are the latest but may still be subject to slight changes.

#### 2.2.6 Pixel Geometries

Having the radii and the sensitive area dimensions of the two innermost detector layers fixed, the pixel geometries are the next parameters to consider. Here, the constraints are of course given by the physics aspects, but also the achievable performance of the readout electronics comes into play. First of all, the detector's intrinsic spatial resolution is approximated by  $\sigma_0 \approx P/(S/N)$ , where P is the pixel pitch and S/N is the signal to noise ratio [30]. The former is obviously a property of the detector layout, while the latter is a quality parameter of the readout electronics. From that, a first order estimation of the pixel geometry is derived: by assuming an achievable signal to noise ration of 10 to 20, a rectangular shape with a pitch of about  $50\mu m$  is reasonable.

Using this number as starting point, detailed simulation studies have been performed in order to further optimise the pixel geometries. The most promising strategy is to use variable pixel pitches in the z-axis that are adjusted to the incidence angle of the particles as illustrated in figure 2-7. This idea is beneficial in two ways. First, increasing the pixel size towards the ends of a ladder reduces the overall number of pixels and thus relaxes the readout time per pixel for a given frame readout time. Second, the charge induced by hits at the ends is not spread over too many pixels, which is in principle advantageous for the track reconstruction accuracy. Simulations show that there is indeed an improvement, but not such that an excessive use would justify extra complications in track reconstruction algorithms [32].

In addition to the physics-driven considerations, more boundary conditions come from the readout electronics development, such as the available number of input and output channels of the various devices. Taking all this into account, leads to a segmentation of

Figure 2-8 Processing steps for thinned wafers with both sides being structured [36].

the sensitive areas into pixels with the following sizes  $^1$ [34]. The sensitive area of the half-ladder modules for the innermost layer is divided into two regions with pixels of different pitch in the z-axis. The 256 rows  $^2$  nearest to the interaction point (IP) are separated by  $55\mu m$ , the remaining area contains 512 rows of  $60\mu m$  pitch. So there are 768 rows in total. Along the short side of the sensitive area the pitch of  $50\mu m$  is kept, resulting in 250 columns. The same numbers of rows and columns hold for the modules of the outer layer, too. For the columns this is straightforward, since the modules are of the same width. With regard to the rows, an unequal number would result in different readout speeds per pixel for the two layers, which is not desirable for numerous reasons. So consequently, the pixel pitch along the z-axis must be adopted. Here there are currently two alternatives, either keeping the two regions approach using  $256 \times 70\mu m$  and  $512 \times 85\mu m$  or dismissing it by using  $80\mu m$  pitch uniformly. A final decision about these options and values has not been made yet.

#### 2.2.7 Detector Thinning

The optimization studies discussed so far focused only on the geometrical aspects of the detector design's influence on the effective impact parameter resolution. But as mentioned in section 2.2.1, the thickness of the detector material must be considered as well due to multiple scattering effects.

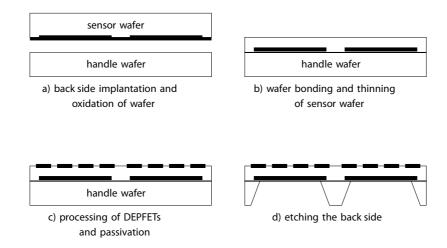

In order to tackle this issue, the technologists at the MPI Semiconductor Laboratory (Munich) have been acquiring know-how in wafer thinning [35]. Indeed, wafer thinning is a common technique in the semiconductor industry. In fact, for silicon detectors based on the DEPFET principle it is mandatory to structure both sides of a wafer, this however,

<sup>1.</sup> The given numbers are the latest, but they may still be changed.

<sup>2.</sup> A line of pixels along the short side of the sensitive area forms a row, a line along the long side (z-axis) forms a column respectively. The terminology of "row" and "column" is used in accordance to the meaning as defined in section 2.1.3. That means the readout procedure is defined such that the pixels are addressed consecutively along the z-axis. This scheme comes very naturally from area and material constraints of the used electronic devices and their required interconnections.

makes the processing extraordinary challenging. To this end, a special procedure has been developed. The relevant steps are illustrated in figure 2-8.

The main idea is to build the silicon device from two wafers rather than just a single one. In the first step both wafers, the so-called *sensor wafer* and the *handle wafer*, are oxidized and the back side structure of the final sensor device is realized on the back side of the sensor wafer. After that the two wafers are merged by means of direct wafer bonding. The unstructured top side of the sensor wafer can then be thinned down to the target thickness using conventional equipment. The third step is to build the DEPFET structures on the new polished top side of the sensor wafer and to deposit passivation material at the back side of the handling wafer. Finally, the openings in that back side passivation define the areas where the bulk of the handling wafer is removed by deep anisotropic wet etching. The etch process is stopped by the oxid layer in-between the two original wafers and thus uncovers the back side structure of the sensor wafer. A proof of principle showed that silicon membranes of only  $50\mu m$  thickness can be produced this way.

By using this technique, the PXD detector modules can be thinned and thus the effects of multiple scattering are reduced, in particular the degradation of the achievable impact parameter resolution. In fact, the silicon bulk underneath the active area is thinned, while the remaining parts of the all-silicon modules keep their original thickness in order to provide sufficient mechanical stability. However, the thickness of the detector is also affecting the intrinsic spatial resolution of the detector itself. The thinner the detector, the smaller is the diffusion volume and the less energy is deposited by incident particles. Both reduces the effective resolution. It has been discovered by simulations that for the defined pixel sizes there is an optimum at  $75 \mu m$  [37][38]. Together with a thickness of the unthinned silicon parts of  $420 \mu m$  and including the contributions of the relevant ASICs, the total average thickness is equivalent to  $< 0.2\% X_0$  [9].

#### 2.2.8 Front-End Readout System

In the previous sections several assumptions and definitions concerning the achievable performance of the front-end readout system are made. They can be summarised as follows. On the half-ladder scale it is assumed possible to read a detector frame of  $768 \times 250$  pixels within a time period of  $20.12 \mu s$  and a signal to noise ratio of 10 to 20. These performance assumptions turned into specifications!

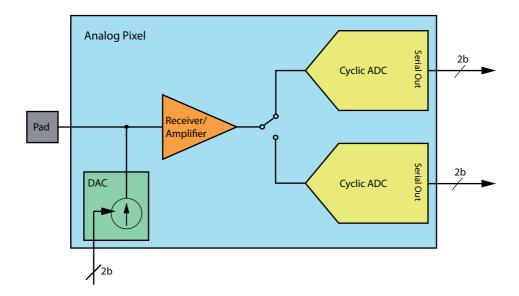

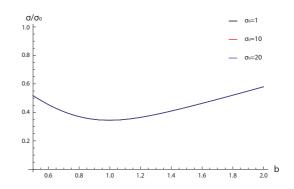

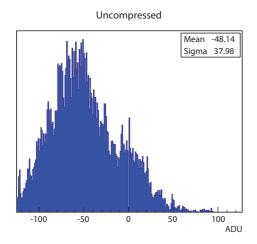

#### Resolution, Dynamic Range and Noise Performance

The energy deposited in the detector by a minimum ionizing particle (MIP) for the defined geometries can be calculated using the Bethe-Bloch formula. It turns out that the energy is sufficient to generate 6000 electron-hole pairs in the silicon bulk of the detector. By expecting a DEPFET transistor gain of  $500pA/e^{-}$  [9], the target signal-to-noise ratio of 20 demands for an input referred noise of the readout device of 150nA. Moreover, it requires for a signal resolution of at least five bit.

The considerations about the readout device's dynamic input range is driven by mainly two facts. First of all, due to the Landau fluctuations of incident particles the input range must be extended.  $8\mu A$  is considered sufficient. In addition to that the readout device needs to cope with fluctuations on the pedestal currents of the various DEPFET

transistors, which is about  $12\mu A$  for an unirradiated prototype device [58]. In order to realize this extended dynamic range while keeping the effective signal resolution, the number of bits for the analog-to-digital conversion has to be increased accordingly. An eight bit representation is reasonable.

#### Single Pixel Readout Period

In the context of the DEPFET readout procedure as introduced in section 2.1.3, there is no doubt that the realizable performance is limited by the drain current measuring device rather than by that for steering the gate and clear lines. The number of required readout channels is depending on the actual organisation of rows and columns in the steering and drain lines. But in any case it is at least equal to the number of columns (250), so a fairly large amount of parallelly working channels is required. Consequently, the chip area is a limiting factor as well, which restricts the possible implementation alternatives. But nevertheless there is a good chance to meet these tough requirements, as already shown by a previous multi-channel microchip designs [42]. Derived from that experience, for the required accuracy a single pixel readout period of 100ns seems feasible with the existing concept.

#### Matrix Organisation

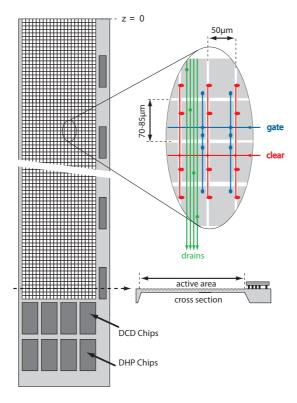

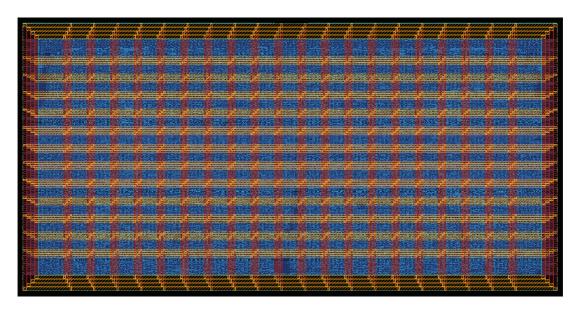

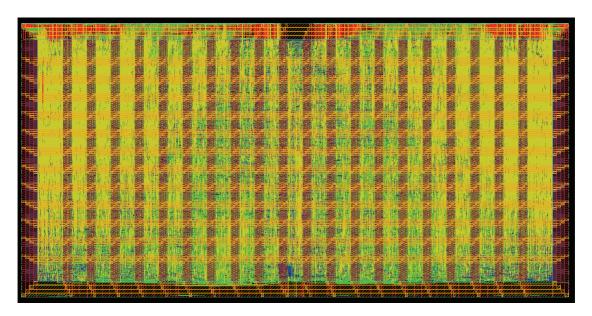

In order to achieve the required frame period of roughly  $20\mu s$  while a single readout channel is able to read a pixel every 100ns, the pixels of a half-ladder must be organised in up to 200 groups. The various groups are addressed for readout one after the other. All pixels within a group must be read in parallel. Taking the physical pixel arrangement into account  $(768 \times 250 \text{ pixels})$ , this structure can be mapped to the matrix in the following way. A group of pixels comprises four entire rows. This results in 192 groups of 1000 pixels each. Expressed in electronic terms, this structure translates into 192 gate and clear lines as well as 1000 readout channels per half-ladder module, which is illustrated in figure 2-9. Consequently, the effectively required readout period for a single pixel is sightly extended to roughly 104ns.

#### The Readout ASICs

The ASICs required for reading the matrix are placed directly onto the all-silicon half-ladder surrounding the sensitive pixel area as shown on figure 2-9. The steering of the matrix is controlled by the *SwitcherB* ASICs. According to the applied readout scheme it is able to sequentially switch on/off and clear the matrix's quad-rows. The SwitcherB provides 32 output channels and can be daisy-chained. Using six of these along the half-ladder module allows for steering the entire matrix. For several reasons a multi-chip solution is preferred over a single chip design. Foremost, the tough area constraints for the balcony along the sensitive area in z-axis restricts the available routing space. More detailed information about the SwitcherB is presented in section 2.3.

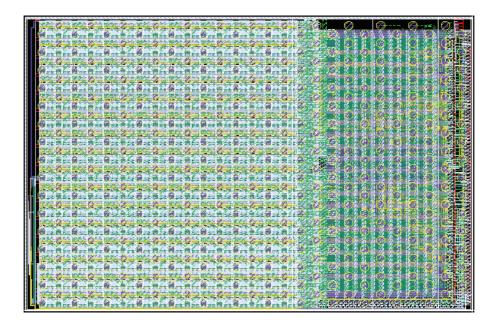

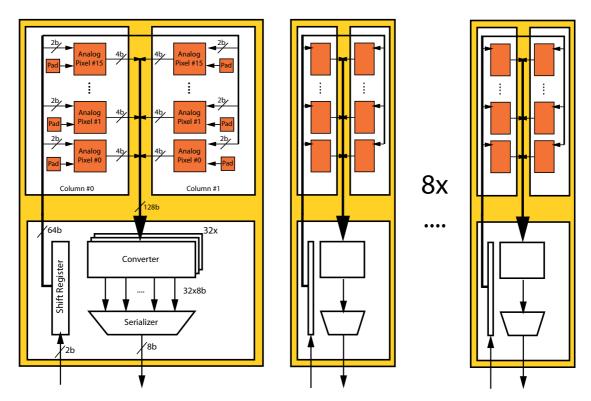

The drain lines of the matrix are routed to the outer end of the half-ladder where the readout ASICs are located. As indicated in figure 2-9, two different sets of readout ASICs are used here, the *DCDB* and the *DHP*. The DCDB (Drain Current Digitizer for BELLE-II) provides 256 analog-to-digital conversion channels<sup>1</sup> on a single chip. Four of them are required to connect all the drain lines. More detailed information about the

Figure 2-9 Schematic drawing of a half-ladder module. It shows the sensitive pixel area and the balconies for the SwitcherB steering chips and the DCDB / DHP readout ASICs. A zoomed section of the sensitive area provides some detailed information about the pixel interconnection. The pixel dimensions refer to the second layer half-ladder modules [9].

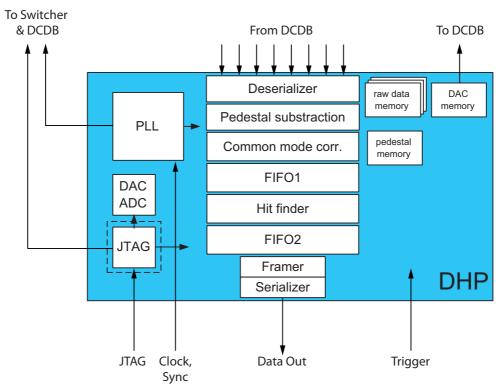

DCDB is presented throughout this work starting with section 2.4. In order to cope with the huge amount of data produced by the DCDB, the DHP (Data Handling Processor) is used for early data analysis and reduction. It is discussed very briefly in section 2.5.

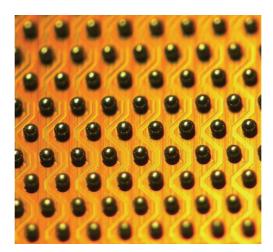

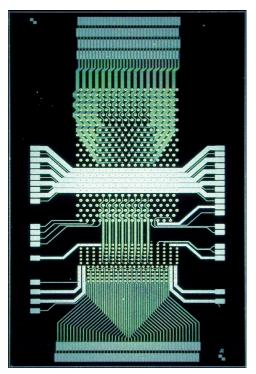

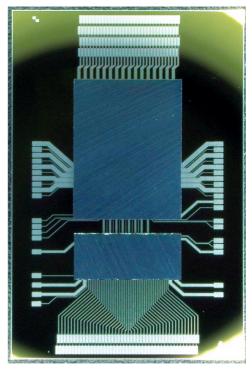

#### 2.2.9 Bump Bond Interconnection Technology

As the amount of detector material has to be minimized in order to reduce multiple scattering effects, the insensitive area of the half ladder module is kept as small as possible. As a consequence, space restrictions for placing and interconnecting the readout chips arise very naturally. Electrically connecting the chip's signals and power lines by means of *wire bonding*, a very basic and well-established technique, is therefore impossible. A much more dense method to do all the required interconnections is called *flip-chip bonding*, where the chip is flipped and placed face-to-face onto the carrier. So the latter is used for interconnecting all the chips on a half-ladder module.

There exist several ways of doing flip-chip bonding, distinguished by procedural differences. An important restriction to the choice of the flip-chip bonding method for

<sup>1.</sup> The number of channels is derived from chip layout constraints and thus does not match exactly an integer fraction of the drain count.

**Figure 2-10** Picture of the DCDB solder bumps:  $100\mu m$  diameter,  $200\mu m$  horizontal pitch,  $180\mu m$  vertical pitch [36].

the PXD project is due to the fact that the carrier, which is the half-ladder module in this case, has a very fragile structure. Thus, the use of any compressing forces is prohibited. A suitable solution is to use solder bumping. Here, the chip pads are assembled with solder balls. The electrical interconnection is established by simply placing the chip onto the carrier, heating it up and making the solder melt. Another big advantage of solder bumping over other existing technologies is the easy rework procedure as the solder can simply be remelted in case of any chip failure. This is of particular importance as there are 14 chips in total residing on a single half-ladder module, each with a limited production yield. In order to achieve an acceptable overall production yield on half-ladder level, an easy rework procedure is indispensable.

The DCDB and the DHP chip are assembled with solder balls on wafer level during production. However, for the SwitcherB such an option is not available, so the solder balls must be assembled afterwards. An additional complication arises from the fact that the SwitcherB's pads are made of aluminium, which is not wettable by solder. To this end, gold studs must be placed on the SwitcherB's pads prior to the assembly of the solder balls. Gold studs provide good mechanical and electrical connectivity to the aluminium pads on the one hand and are wettable by solder on the other hand. The gold studs are placed using a modified wire bond process. The solder balls are assembled by means of a solder jetting technology. More detailed information about chip assembly for the BELLE-II PXD detector is available in [36].

#### 2.2.10 Higher Level Readout System

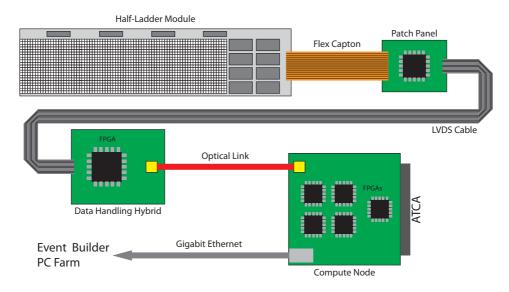

The data that is produced by the two chips DCDB and DHP must be transferred to the higher level readout system for further processing. Unfortunately, there is only very little room available around the inner layer detector, which has a large impact on its connection scheme. The baseline design in shown in figure 2-11.

A FLEX capton cable of about 20cm connects the half-ladder module to a patch panel. Besides power filtering and impedance matching, the patch panel is mainly acting as repeater within the electrical connection of the half-ladder module to the so-called *Data*

**Figure 2-11** Architecture of the PXD readout system [9].

Handling Hybrid (DHH), a FPGA-based readout board. There is one DHH per half-ladder module, responsible for its interconnection to the outside world. First of all, it provides the clock signal as derived from the BELLE-II environment. Secondly, it acts as slow control master for all the ASICs. And thirdly, the data coming from the DHPs via electrical connections is multiplexed onto a single optical link. Via this optical link, the data is further transferred to the so-called *Compute Nodes* (CN). These CNs are FPGA-based devices and compatible to the ATCA<sup>1</sup> standard. There is one CN per DHH, resulting in the total number of 40 CNs for the entire PXD detector system. However, all the CNs are interconnected using a system level network, thus each CN is potentially able to access the data of every DHH. Together with tracking information coming from the SVD, data processing algorithms running on the CNs define regions of interest within the PXD data. These regions of interest are then further analysed and provided to the BELLE-II event builder farm, where they are combined with associated data from the rest of the BELLE-II sub-detectors.

# 2.3 The SwitcherB Steering ASIC

#### 2.3.1 Overview

The SwitcherB ASIC [39] is a steering chip for DEPFET pixel matrices that is particularly designed for the application in the BELLE-II inner layer vertex detector system. It is the latest version in a series of DEPFET steering ASICs and is now in a close-to-final state.

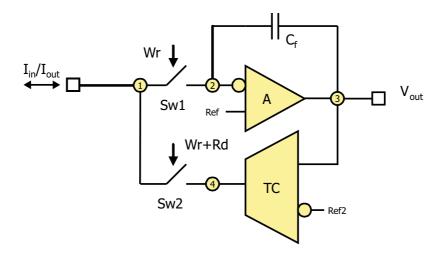

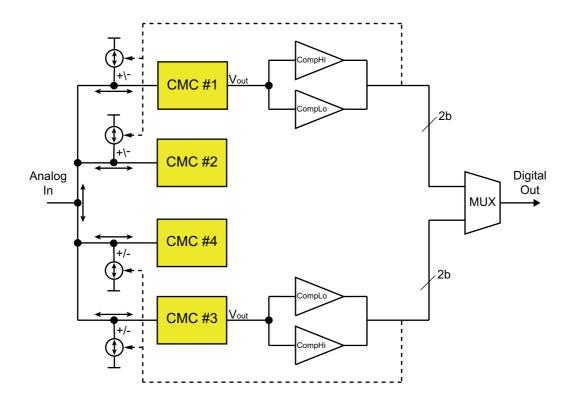

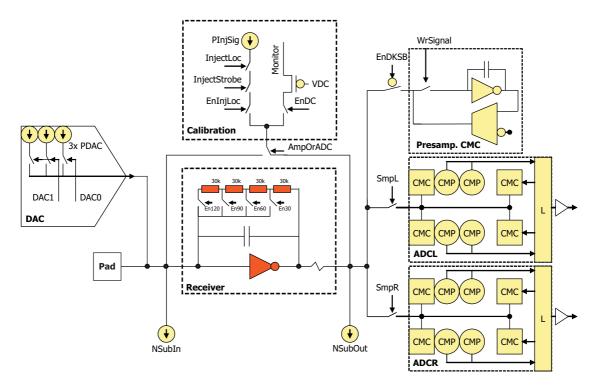

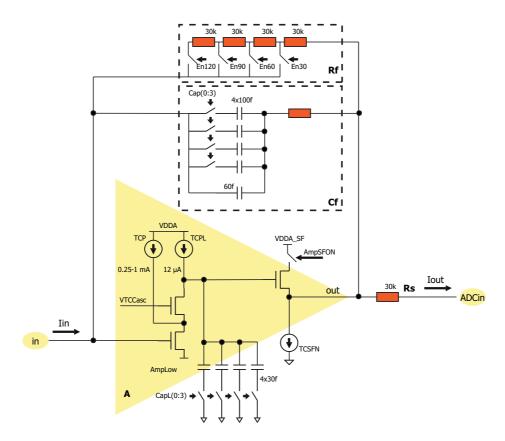

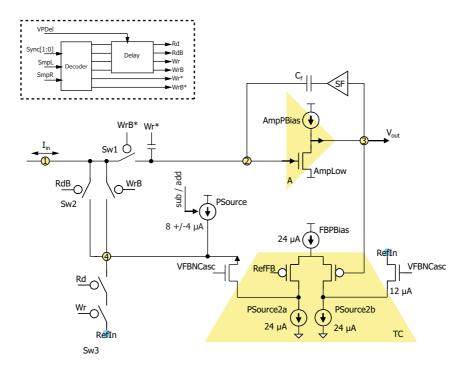

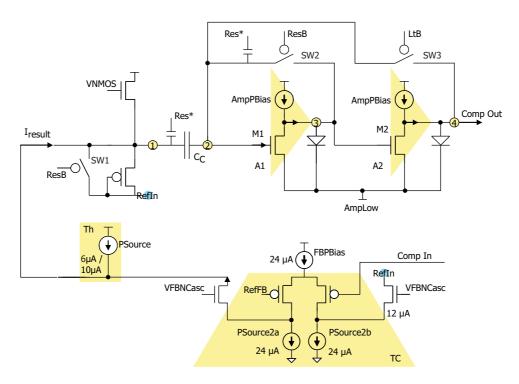

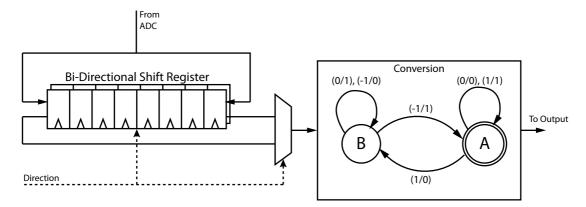

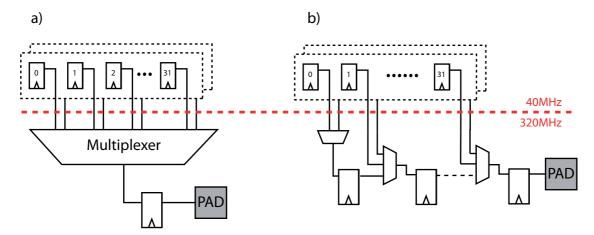

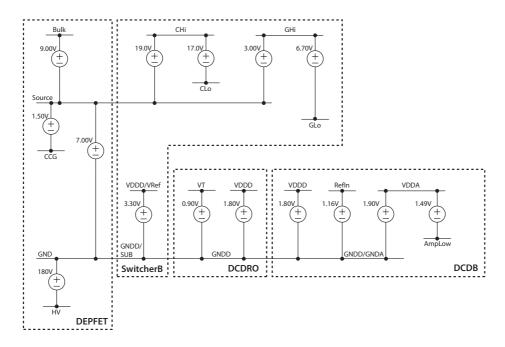

The SwitcherB provides the total number of 32 output channels, each consisting of a gate line and a clear line driver. All gate output drivers share the two common supply inputs

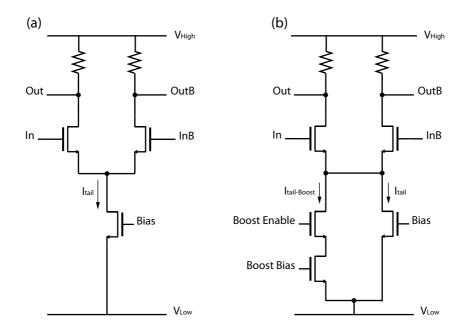

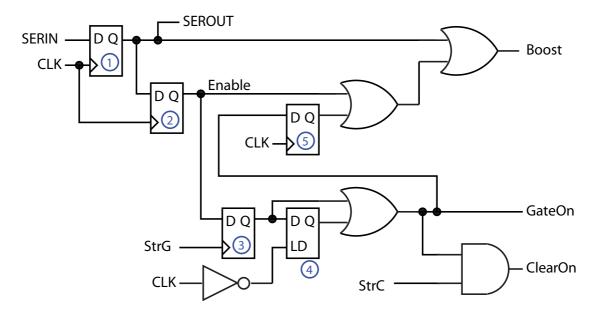

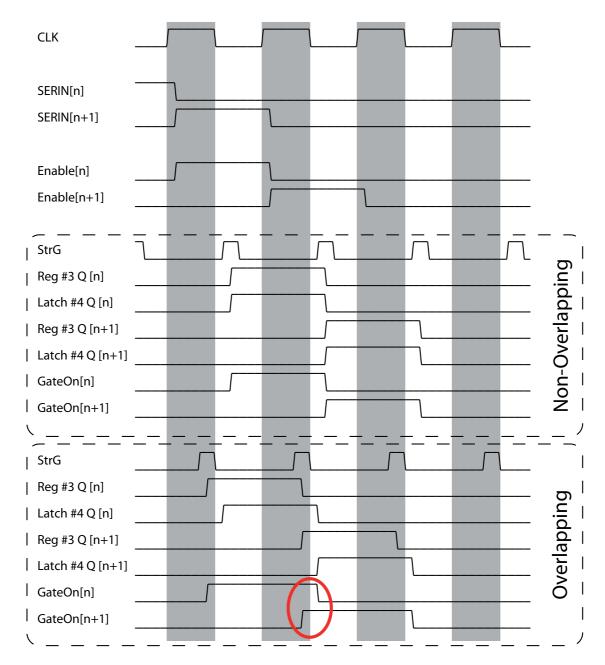

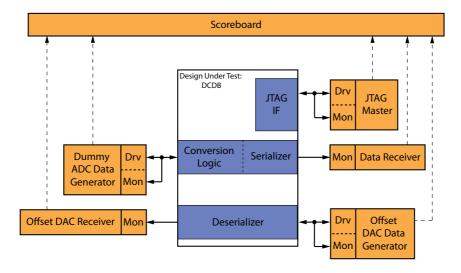

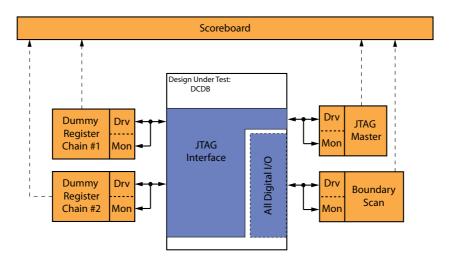

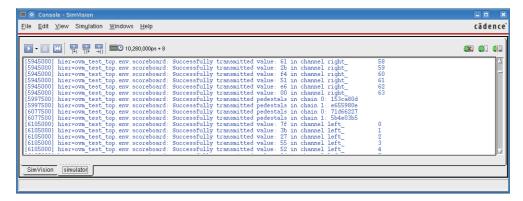

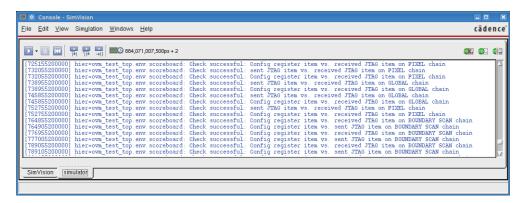

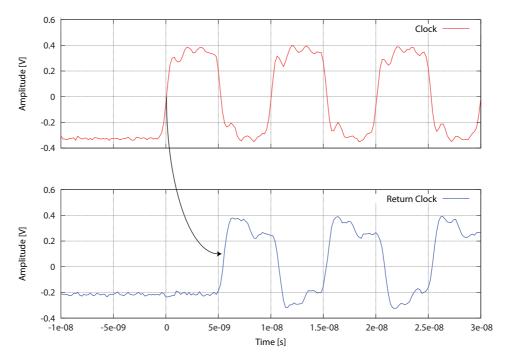

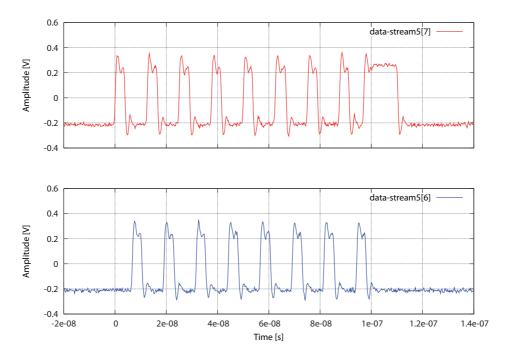

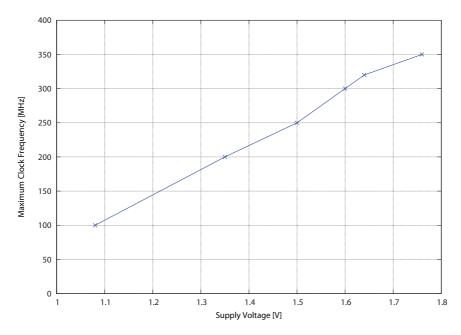

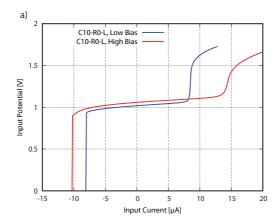

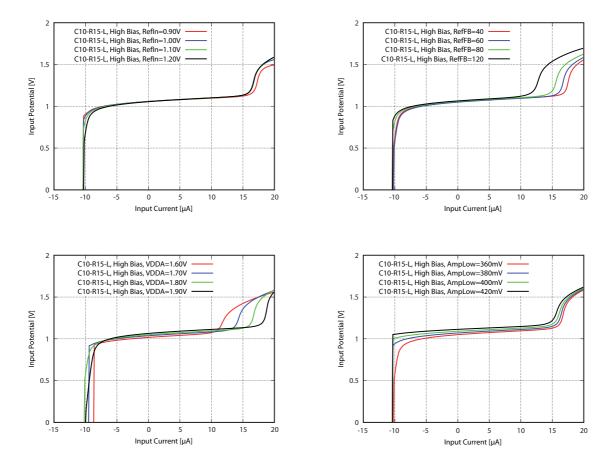

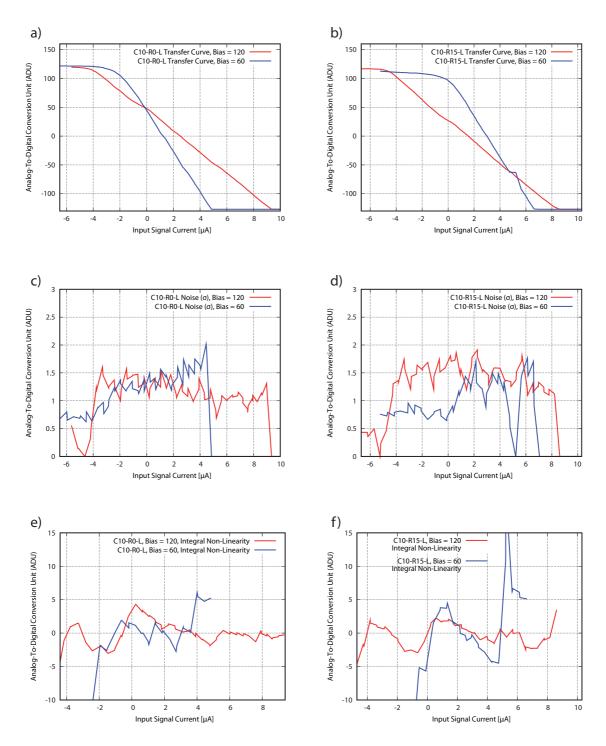

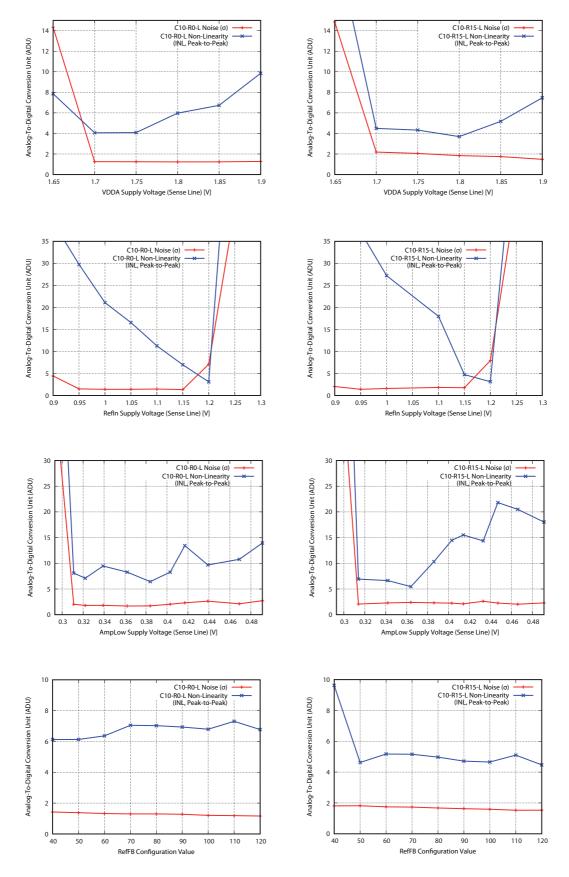

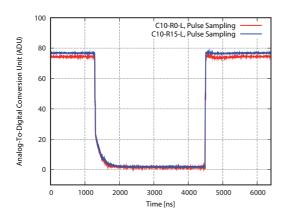

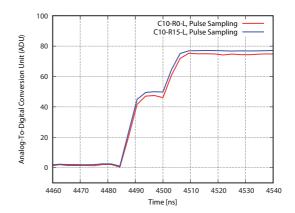

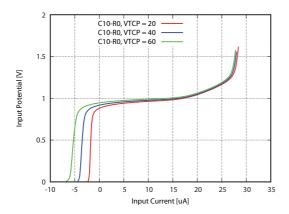

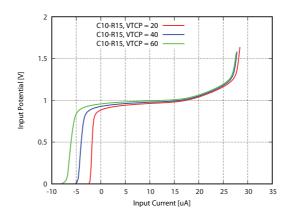

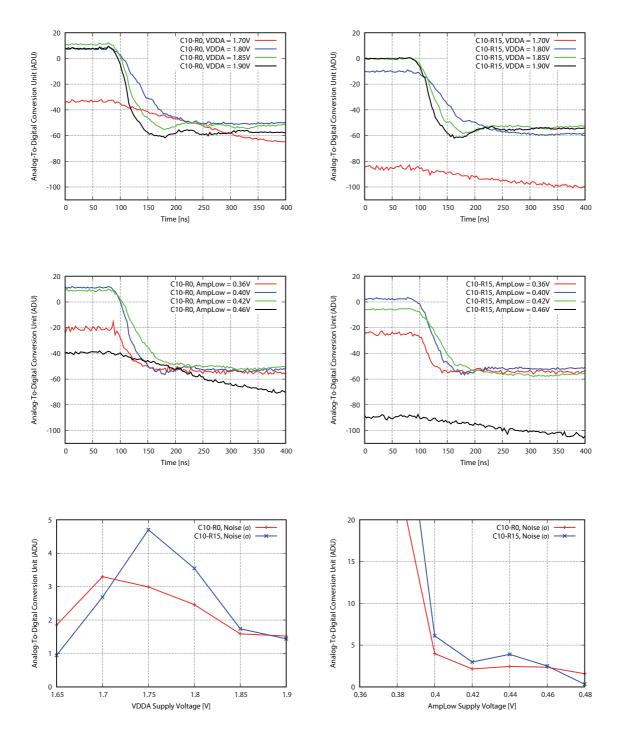

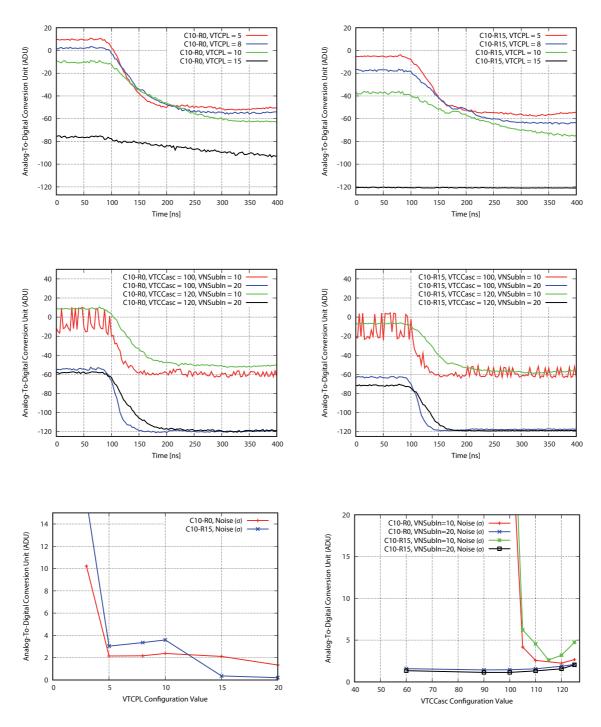

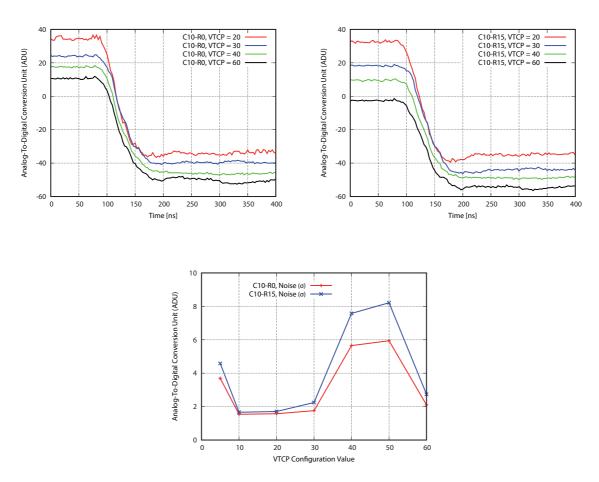

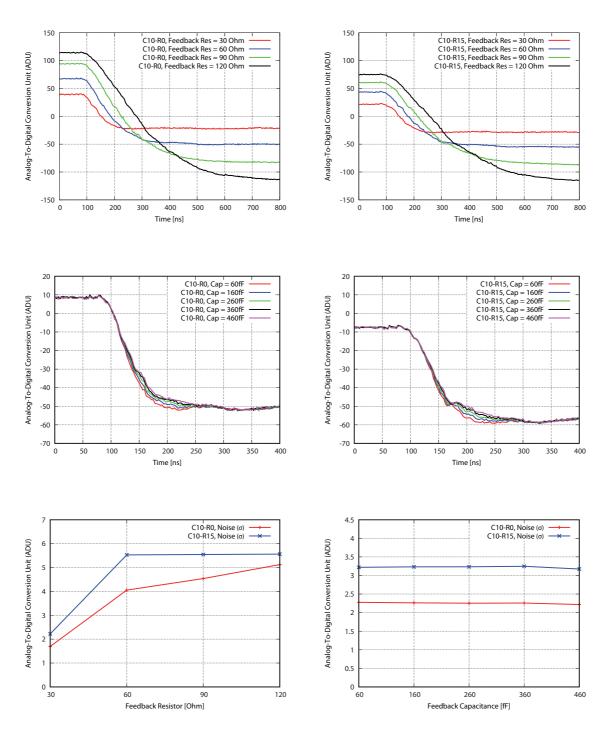

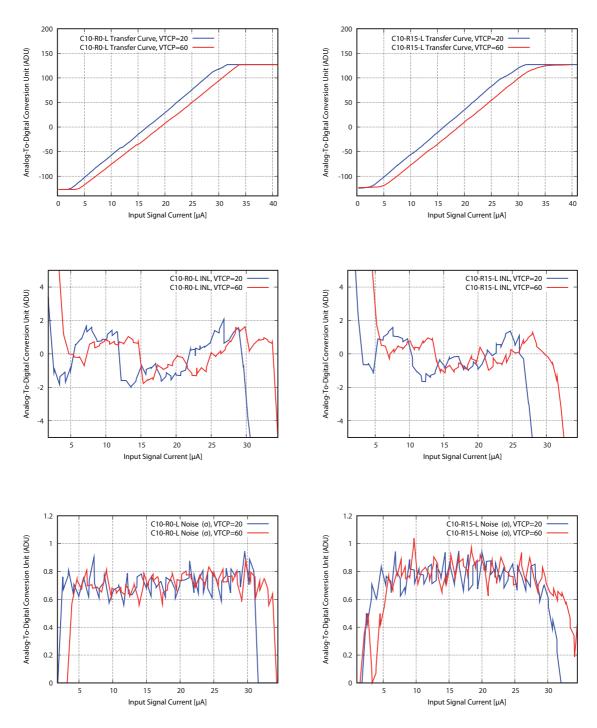

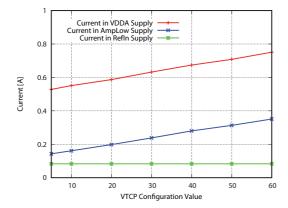

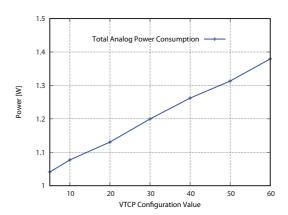

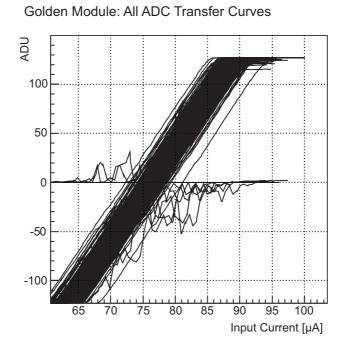

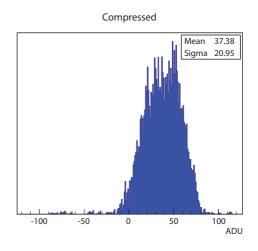

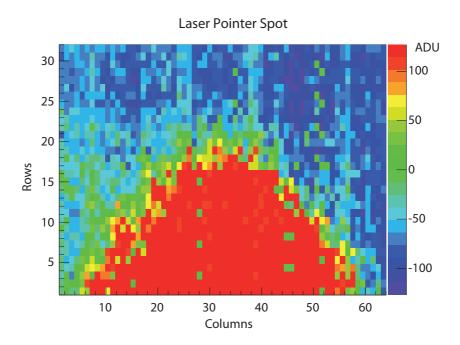

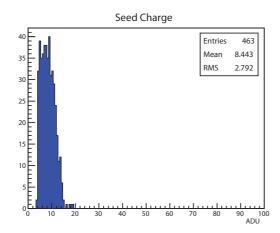

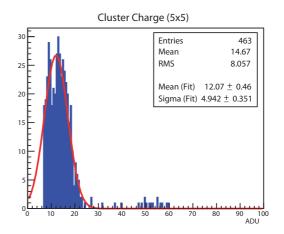

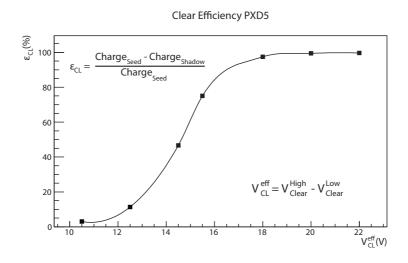

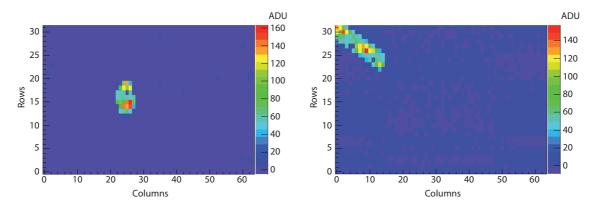

<sup>1.</sup> Advanced Telecommunication Computing Architecture