## Geänderte

## INAUGURAL-DISSERTATION

zur

Erlangung der Doktorwürde

der

Naturwissenschaftlich-Mathematischen Gesamtfakultät

der

$Ruprecht-Karls-Universit \"{a}t$

Heidelberg

vorgelegt von

M. E. Wenxue Gao

aus Liaoning, China

Tag der mündlichen Prüfung:  $22 \text{ M\"{a}rz } 2012$

## Thema

Active Buffer Development in CBM Experiment

Gutachter: Prof. Dr. Reinhard Männer

Prof. Dr. Ulrich Brüning

## **Abstract**

The DAQ (data acquisition) system of the CBM experiment in GSI is featured by the large data rate of about 1 TB/s and the high event rate of about 100 kHz. Such challenge is being a trend in high-energy physics experiments. The Active Buffer concept is applied to establish the proprietary buffering system for the CBM DAQ, which also provides active support in the event building. The project requires a modular framework and the work in this dissertation includes the development, testing and verification of FPGA modules for efficient data transfer, buffering and reconfiguration, as well as software for automatic transformation of HDL codes.

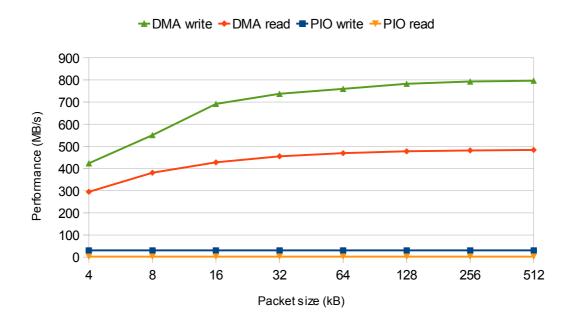

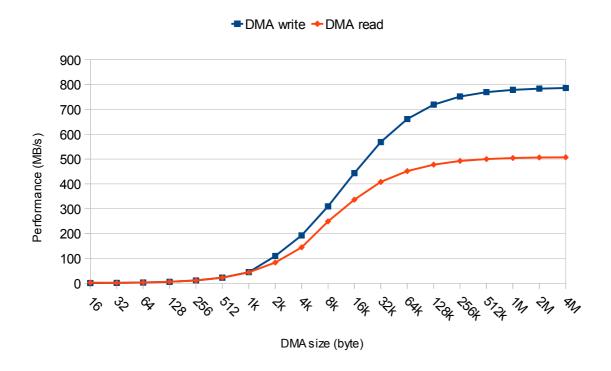

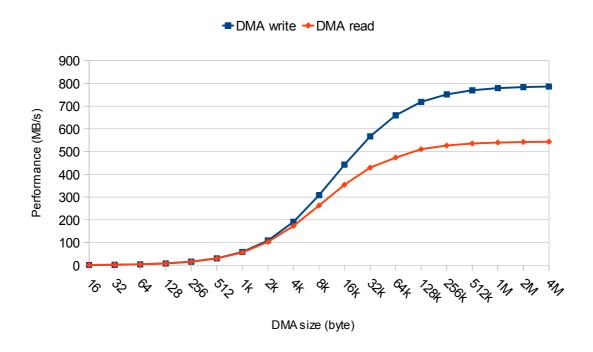

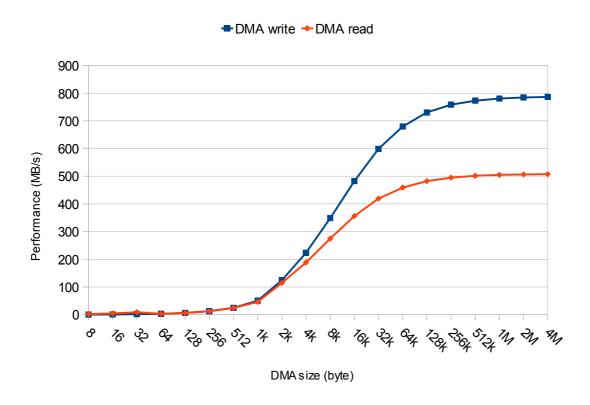

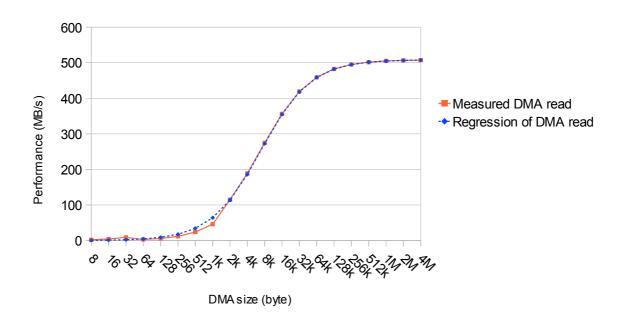

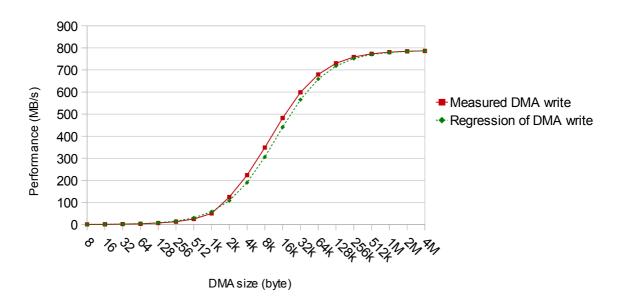

The central control device of the Active Buffer is a high-end FPGA. The storage kernel is a DDR2 SDRAM module of 512 MB. With a FIFO wrapper implemented with a small amount of FPGA resource, the local buffer on the Active Buffer board has both large-size memory space and standard FIFO access ports. To perform reliable and efficient data transfer from the read-out system to the computing nodes, a double-channel scatter-gather DMA engine over PCI Express is developed, which has 543 MB/s DMA read performance and 790 MB/s DMA write performance. Based on the same DMA functionalities, epoch marker indexing is tested in the Active Buffer system.

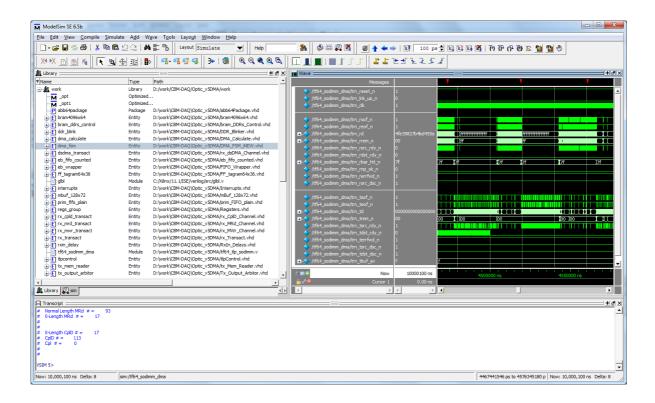

In terms of the large-scale FPGA design for the Active Buffer, verification plays an important role. For a secure function set on the transaction layer of PCI Express, HDL designs for the Active Buffer are verified by a rich combination of simulation environments. Upon this verification, the logic can be improved quickly and reliably. This is a sound foundation for the future Active Buffer development.

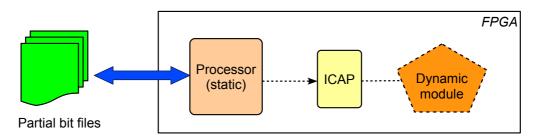

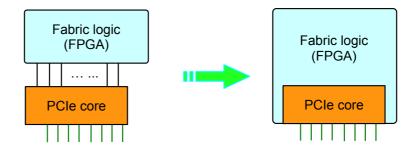

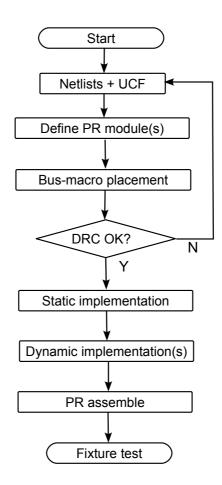

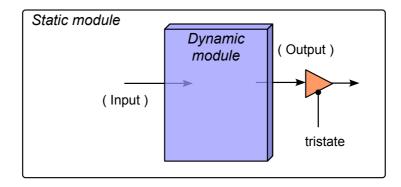

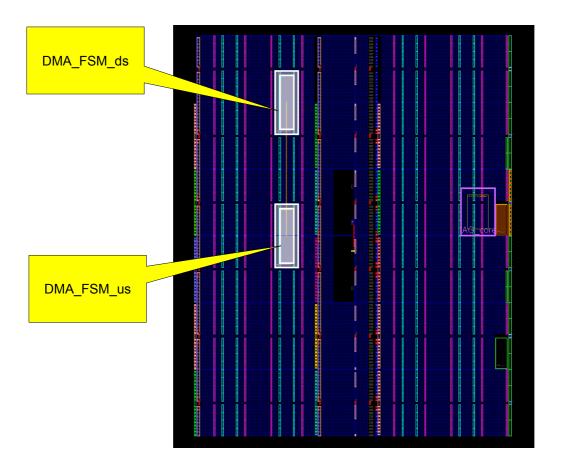

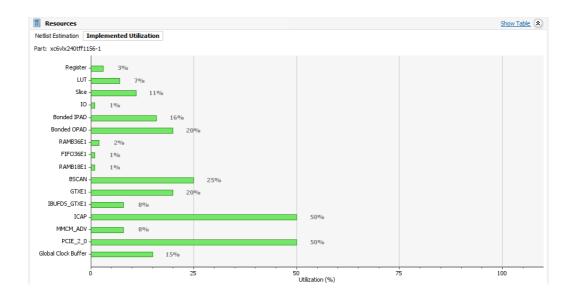

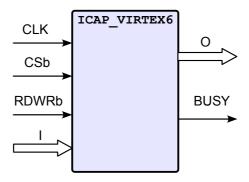

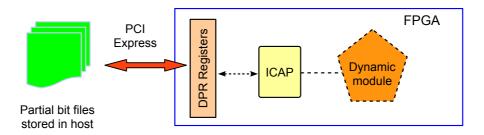

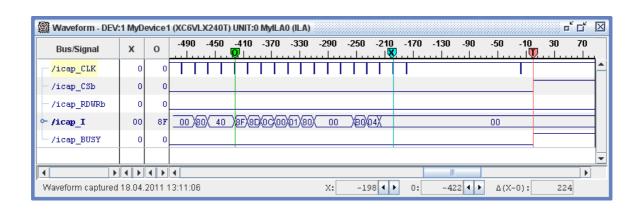

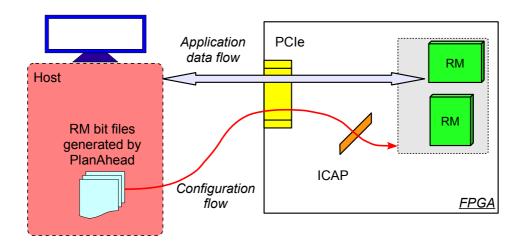

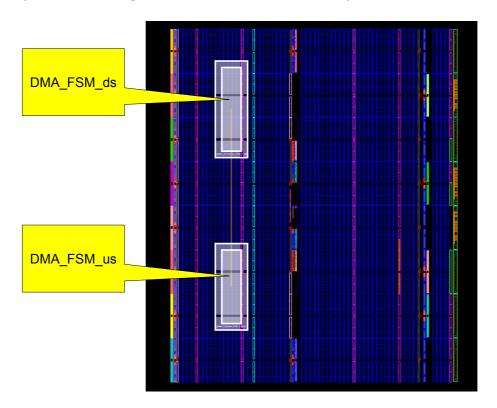

Against the link training issue in the PCI Express reboot and the license limitation of the Virtex4 PCI Express core, as well as for a modularized firmware architecture to the upper-level software applications, DPR (dynamic partial reconfiguration) technology is implemented on Virtex4, Virtex5 and Virtex6 FPGAs. Concurrent PlanAhead software with the partial reconfiguration license proves a competitive framework to do DPR. Attractive features are introduced by DPR experiments into the Active Buffer system. The fast reconfiguration is successfully done via ICAP over PCI Express operations, which leads to a general computing acceleration plug-in card scenario.

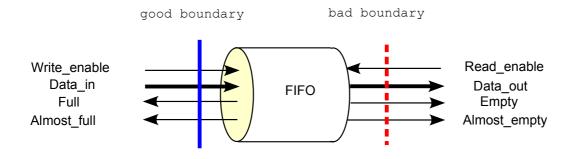

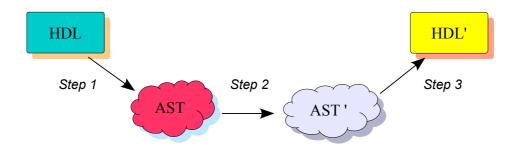

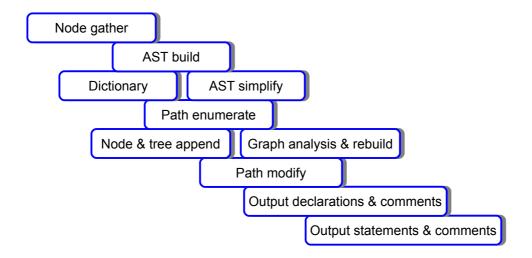

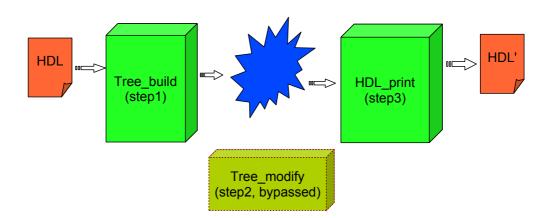

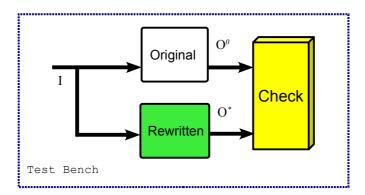

During the DPR experiments in high-frequency clock domains, the boundary logic between the static and the dynamic modules needs to be rewritten, which took more time and effort than expected. Therefore the HDL code reuse is studied to save the error-prone HDL rewrite work and to try out a new HDL development pattern. The HDL code reuse tool, *Logro*, transforms original HDL design into target HDL design with specified pipeline reorganization so that the DPR boundary logic is automatically and correctly decoupled. Encouraging results of *Logro* V1.0 are presented.

**Keywords**: CBM, DAQ, Active Buffer, FPGA, DDR SDRAM, PCI Express, DMA, verification, DPR, PlanAhead, ICAP, HDL reuse

## Zusammenfassung

Die Anforderungen an das Datenerfassungssystem (DAQ) des CBM Experiments an der GSI sind mit einer Datenrate von 1TB/s und einer Ereignisrate von 100 kHz sehr hoch und stellen auch im Vergleich zu anderen Experimenten in der Hochenergiephysik eine Herausforderung dar. Bei der Datennahme wird daher ein aktiver Zwischenspeicher ("active buffer") eingesetzt, der durch eine Vorsortierung der Datenfragmente und eine intelligente Übertragung in den Hostrechner den Aufbau der Datenstrukturen zur Ereignisverarbeitung unterstützt. Das Projekt erfordert ein modulares Framework und die Arbeit umfasst die Entwicklung, Verifikation und Test von FPGA Modulen zum effizienten Datentransfer, zur Zwischenspeicherung und zur Rekonfiguration, sowie von Software zur automatischen Transformation von HDL Beschreibungen.

Die zentralen Bauteile dieses Zwischenspeichers sind ein leistungsfähiges FPGA zur Datenflusssteuerung und ein DDR2 SDRAM Modul mit einer Kapazität von 512MB. Durch eine spezielle Ansteuerungsmethode kann das Speichermodul zusammen mit den FPGA-internen Speicherelementen als leistungsfähiges, großes FIFO betrieben werden. Den Datantransfer vom Zwischenspeicher zum PC übernimmt eine spezielle DMA Einheit, die an den PCIe-Kern im FPGA angeschlossen ist. Die zwei DMA Kanäle arbeiten mit Scatter-Gather Unterstützung und erreichen beim Transfer zum PC 543 MB/s und in der Gegenrichtung 790MB/s. Die für die Vorsortierung wichtige Übertragung der Zeitstempel ("epoch marker") erfolgt ebenfalls mit einem DMA Kanal.

Die Verifikation ist eine wichtige Stufe bei der Entwicklung einer umfangreichen FPGA Anwendungen wie des aktiven Zwischenspeichers. Daher wurden die HDL Module der Funktionen für das PCI Express "transaction layer" mit einer Reihe unterschiedlicher Simulationsumgebungen verifiziert. Auf dieser Grundlage können Verbesserungen an der Funktionalität schnell und zuverlässig umgesetzt werden, womit eine konsistente Weiterentwicklung gewährleistet ist.

Aufgrund der typischen PC-Architektur muss die PCIe-Einheit im FPGA bereits während des Startvorgangs funktionsfähig sein, wohingegen die eigentliche aktive Zwischenspeicherfunktion erst zusammen mit der entsprechenden Anwendungssoftware verfügbar sein muss. Strikte Modularisierung zusammen mit dynamischer, partieller Rekonfigurierung ("DPR") ermöglichen Veränderungen in der Zwischenspeicherfunktion zur Laufzeit. Ein weiter Grund für die Nutzung der DPR sind die Lizenzbedingungen der PCIe-Core-Implementierung mit Virtex4-FPGAs. DPR kann bei den FPGA Familien Virtex-4, -5 und -6 im Rahmen der "PlanAhead" Software von Xilinx benutzt werden. DPR wird im Projekt im Sinne eines allgemeinen Coprozessors eingesetzt, indem die FPGA Konfiguration über die PCIe und die interne Konfigurationsschnittstelle ("ICAP") im FPGA nachgeladen wird.

Um DPR bei hohen Taktgeschwindigkeiten einsetzen zu können, muss die Verbindungslogik zwischen den statischen und dynamischen Modulen speziellen Anforderungen genügen. Da die manuelle Anpassung existierenden Module an diese Anforderungen aufwändig und fehleranfällig ist, wurde das Programm "Logro" entwickelt, das HDL Beschreibungen mittels einer speziellen Pipeline-Neustrukturierung automatisch so transformiert, dass die DPR Anforderungen erfüllt werden. Mit Logro V1.0 wurden dabei gute Ergebnisse erzielt, die hier vorgestellt werden.

**Keywords**: CBM, DAQ, Active Buffer, FPGA, DDR SDRAM, PCI Express, DMA, Verifikation, DPR, PlanAhead, ICAP, HDL Reuse

# Acknowledgement

During the last six years of stay in Mannheim for the CBM experiment, I have received enormous help from all people around me. I owe great thanks to them.

Prof. Dr. Reinhard Männer and Dr. Andreas Kugel have given and are giving me precious supervision and support into the project, building up the sound fundamental to research. Prof. Dr. Reinhard Männer and Prof. Dr. Ulrich Brüning contributed excellent advices and suggestions in improving the dissertation structure. PD. Dr. Joachim Gläß led me into the project with great patience. Andreas Wurz has thousands of wonderful ideas, contributes robust designs and invokes my mind open to solutions. When I have questions, they are always there. Christian Steinle, Markus Gipp, Dr. Guillermo Marcus, Jakob Haufe, Yuning Yang, Thomas Gerlach, Nicolai Schroer, Raul Fajardo, Michael Stapelberg and Philipp Schäfer helped me a lot in discussion and technical debugging as well as test programs. Indispensable PCI driver support is from Dr. Guillermo Marcus. People in the department of Prof. Dr. Ulrich Brüning (CAG Group) are active in cooperation and have provided efficient modules for the Active Buffer FPGA. Thanks go to Frank Lemke, Sven Schenk and Prof. Dr. Ulrich Brüning.

All colleagues in Lehrstuhl Informatik V are so kind and in such a warm atmosphere. Andrea Seeger, Dina Geppert and Christiane Glasbrenner are always ready to help. Towards the literal completion of the dissertation, Lei Zheng made proof-reading for most chapters with expert opinions.

Thanks go to people in GSI, Darmstadt and to people in KIP, Heidelberg University. Without them, almost half of the dissertation would be nowhere. They are Dr. Sergey Linev, Dr. Jörn Adamczewski-Musch, Dr. Hans-Georg Essel and Dr. Walter F.J. Müller in GSI and Dr. Norbert Abel, Sebastian Manz and Prof. Dr. Udo Kebschull in KIP.

My family supports me with heart and love. There stand my mother Yumei Xiao, my father Jimei Gao, my sister Wenying, my wife Bin Xu and my sweet daughter Yina.

I wish my best to all people happy and healthy, mentioned and unmentioned. Thank you all the way.

## **Acronyms**

ABB Active buffer board

ASIC Application specific integrated circuit

CBM Compressed baryonic matter

CPLD Complex programmable logic device

CRC Cyclic redundant code

DABC Data acquisition backbone core

DCB Data combiner board

DMA Direct memory access

DPR Dynamic partial reconfiguration

DW Double-word (32-bit data)

ECRC End-to-end CRC

FAIR Facility for Anti-proton and Ion Research

FEE Front-end electronics

FPGA Field programmable gate array

GT Giga-transfer

GTP Gigabit transceiver pair

ICAP Internal configuration access port

LCRC Link-by-link CRC

MGT Multiple-giga transceiver

MPRACE Multi-purpose reconfigurable accelerator/computing engine

ROC Read-out controller

SFP Small-factor plug

# **Contents**

| Abstract                                          | i   |

|---------------------------------------------------|-----|

| Zusammenfassung                                   | iii |

| Acknowledgement                                   | V   |

| Acronyms                                          | vii |

| Contents                                          | ix  |

|                                                   |     |

| Chapter 1 Introduction                            | 1   |

| 1.1 High-energy physics (HEP) background          | 1   |

| 1.2 CBM DAQ characteristics and the Active Buffer | 4   |

| 1.3 Fast data path                                | 7   |

| 1.4 Dynamic partial reconfiguration               | 8   |

| 1.5 Logic design reuse                            | 9   |

| 1.6 Organization of the dissertation              | 10  |

| Chapter 2 The Active Buffer system                | 11  |

| 2.1 Introduction                                  | 11  |

| 2.1.1 Active Buffer                               | 13  |

| 2.1.2 Traffic classes                             | 15  |

| 2.1.3 Hardware-aided indexing                     | 16  |

| 2.2 Buffer kernel                                 | 17  |

| 2.2.1 Requirement                             | 19 |

|-----------------------------------------------|----|

| 2.2.2 Logic building                          | 19 |

| 2.2.3 Test and verification                   | 23 |

| 2.2.4 Implementation in FPGA                  | 28 |

| 2.2.5 Stand-alone IC scenario                 | 28 |

| 2.2.6 Notes to the transformed FIFO           | 29 |

| 2.3 Future Active Buffer upgrade              | 30 |

| 2.4 Summary                                   | 30 |

|                                               |    |

| Chapter 3 ABB – Interfacing networks to hosts | 31 |

| 3.1 Introduction                              | 31 |

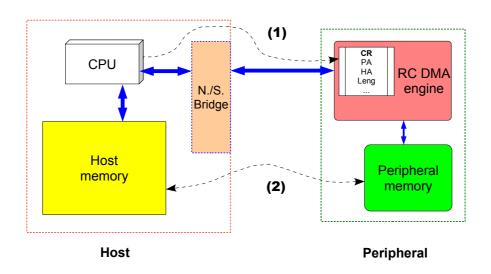

| 3.1.1 Register-controlled (RC) DMA            | 32 |

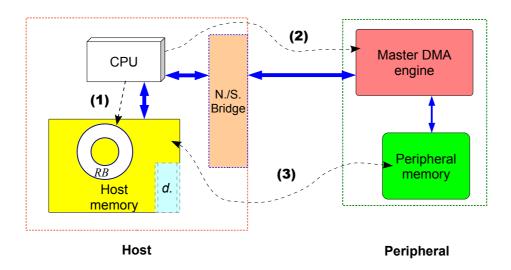

| 3.1.2 Master DMA                              | 33 |

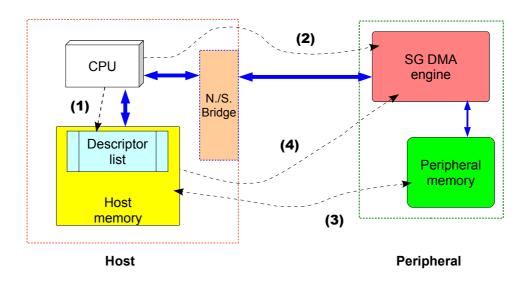

| 3.1.3 Scatter-gather (SG) DMA                 | 35 |

| 3.1.4 Selected solution                       | 37 |

| 3.2 PCI Express                               | 38 |

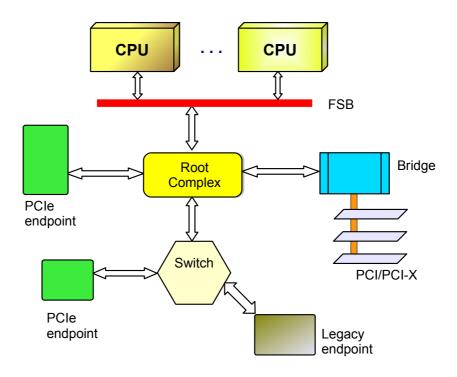

| 3.2.1 Root complex and endpoint               | 40 |

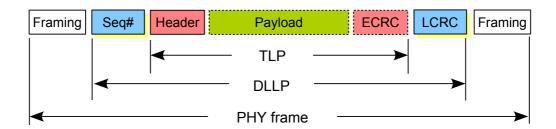

| 3.2.2 Transaction layer packet (TLP)          | 41 |

| 3.2.3 PCI Express evolution                   | 43 |

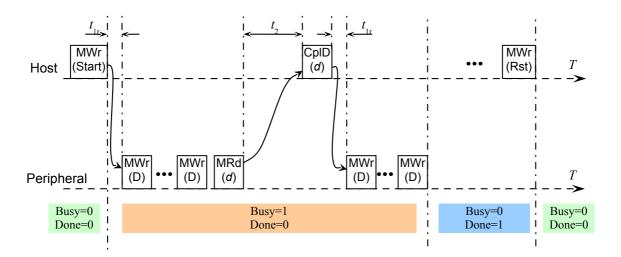

| 3.3 DMA transaction-layer behaviour           | 43 |

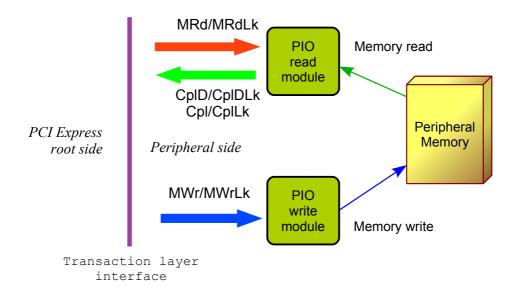

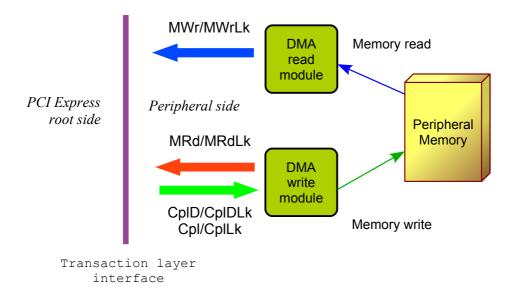

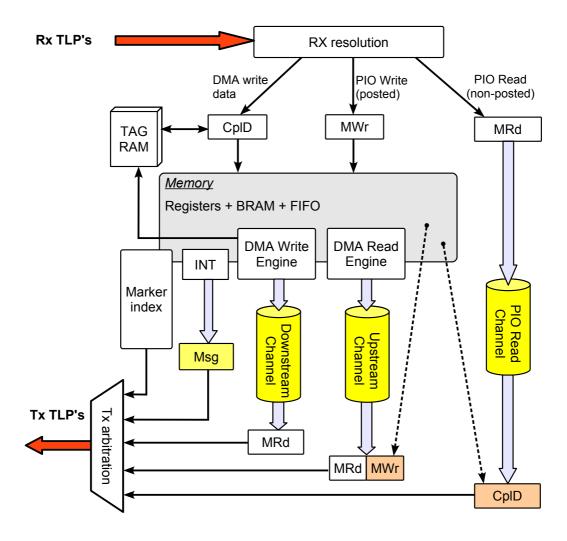

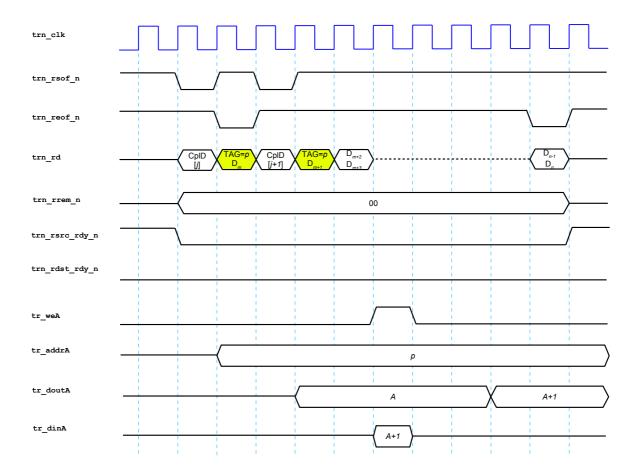

| 3.4 DMA engine development                    | 45 |

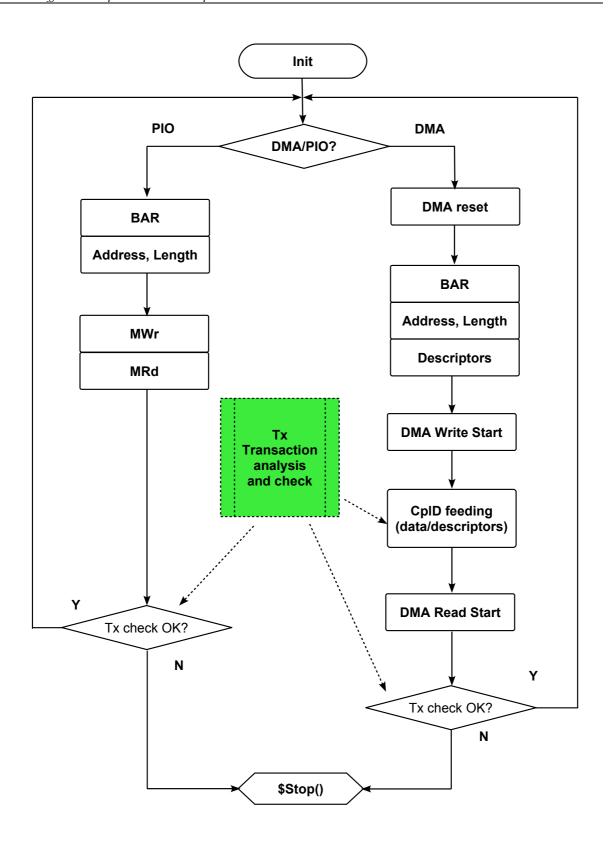

| 3.4.1 DMA procedure                           | 47 |

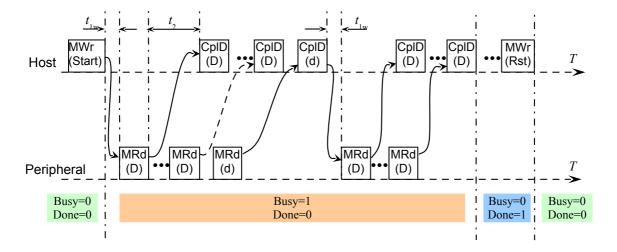

| 3.4.2 DMA packet division                     | 49 |

| 3.4.3 TAG management for DMA write            | 51 |

| 3.4.4 Channel buffers and Tx arbitration      | 52 |

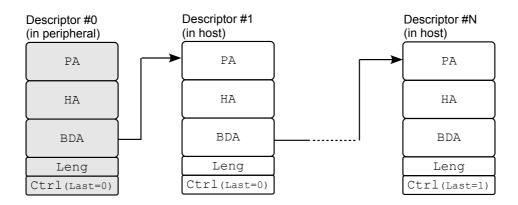

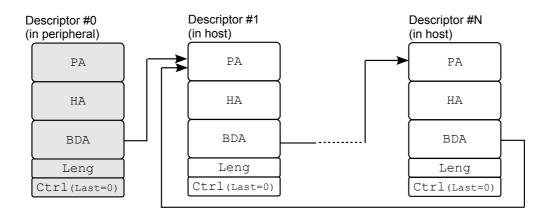

| 3.4.5 DMA descriptor and DMA commands         | 54 |

| 3.4.6 DMA status                              | 55 |

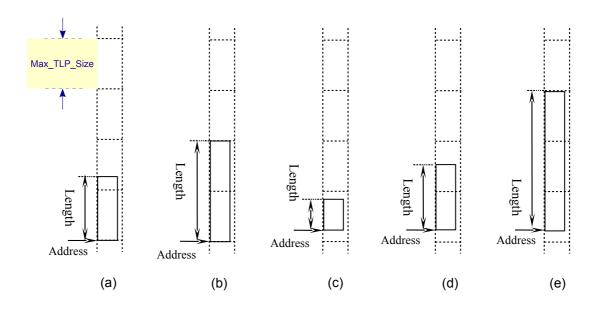

| 3.4.7 Transaction layer interface: 32-bit vs. 64-bit | 56 |

|------------------------------------------------------|----|

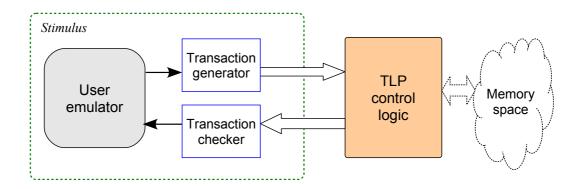

| 3.5 Transaction-layer verification                   | 57 |

| 3.6 Transition-level verification                    | 68 |

| 3.7 DMA engine variations                            | 71 |

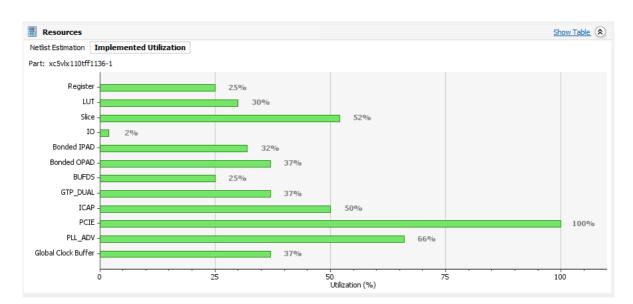

| 3.7.1 ABB1 – Virtex4 FX20/FX60                       | 72 |

| 3.7.2 MPRACE2                                        | 73 |

| 3.7.3 ABB2 – AVNET Virtex5 PCIE development board    | 74 |

| 3.7.4 Viroquant application – ML605                  | 74 |

| 3.8 PCI driver                                       | 75 |

| 3.9 Summary                                          | 75 |

|                                                      |    |

| Chapter 4 DMA performance tests                      | 77 |

| 4.1 Introduction                                     | 77 |

| 4.2 Virtex4 performance test                         | 79 |

| 4.3 Virtex5 DMA performance test and analysis        | 79 |

| 4.4 Virtex6 DMA performance test                     | 85 |

| 4.5 Summary                                          | 88 |

|                                                      |    |

| Chapter 5 Dynamic partial reconfiguration            | 89 |

| 5.1 Motivation                                       | 89 |

| 5.2 Overview                                         | 93 |

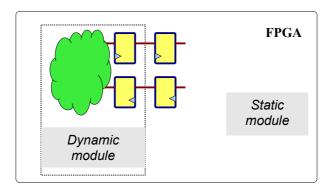

| 5.2.1 Partition                                      | 94 |

| 5.2.2 Boundary processing                            | 94 |

| 5.2.3 Dynamic module                                 | 95 |

| 5.2.4 Reconfiguration methods                        | 95 |

| 5.3 Implementation – Virtex4 FX60                    | 95 |

| 5.3.1 The problem                                    | 96 |

| 5.3.2        | The solution                       | 97  |

|--------------|------------------------------------|-----|

| 5.3.3        | Implementation                     | 98  |

| 5.3.4        | Test analysis                      | 101 |

| 5.3.5        | Conclusion to the Virtex4 DPR      | 102 |

| 5.4 Imp      | lementation – Virtex6 LX240T       | 103 |

| 5.4.1        | Boundary decoupling and partitions | 103 |

| 5.4.2        | Bit file format of Xilinx FPGAs    | 105 |

| 5.4.3        | ICAP primitive                     | 106 |

| 5.4.4        | Conclusion and scenario            | 108 |

| 5.5 Imp      | lementation – Virtex5 LX110T       | 109 |

| 5.6 Lim      | itation of DPR                     | 111 |

| 5.7 Sum      | ımary                              | 112 |

|              | OL code reuse tool                 |     |

| 6.1 DPR      | R review and HDL reuse             | 113 |

| 6.2 Feas     | sibility                           | 117 |

| 6.2.1        | Underlying rules                   | 118 |

| 6.2.2        | Path management                    | 120 |

| 6.3 Mak      | ring of Logro (LOGic RObot)        | 121 |

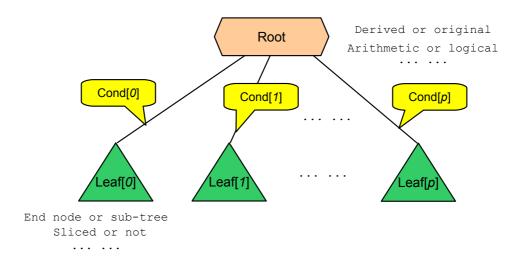

| 6.3.1        | Data structure                     | 122 |

| 6.3.2        | Running steps                      | 123 |

| 6.4 Tes      | t and verification                 | 129 |

| 6.5 Sug      | gestion to DPR vendors             | 130 |

| 6.6 Арр      | plication perspective              | 131 |

| 6.7 Cor      | nclusion                           | 133 |

| Chapter 7 Su | mmary and outlook                  | 135 |

|              |                                    |     |

| 7.1 The Active Buffer                                           | 135 |

|-----------------------------------------------------------------|-----|

| 7.2 DMA over PCI Express                                        | 135 |

| 7.3 DPR                                                         | 136 |

| 7.4 HDL reuse                                                   | 137 |

|                                                                 |     |

| Appendices                                                      |     |

| A.1 ABB1 FPGA implementation report                             | 139 |

| A.2 MPRACE2 Bridge FPGA implementation report                   | 141 |

| A.3 DDR FIFO self-test (AVNET board) FPGA implementation report | 143 |

| A.4 ABB2 (AVNET board) FPGA implementation report               | 145 |

| A.5 ML605 FPGA implementation report                            | 147 |

| A.6 Epoch marker (EM) indexing                                  | 149 |

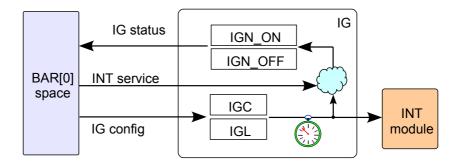

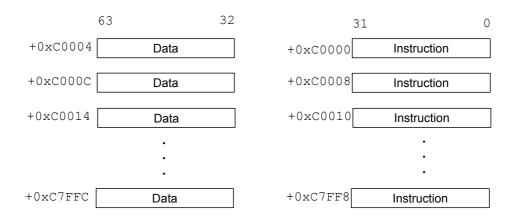

| A.7 Interrupt Generator (IG)                                    | 157 |

| A.8 Data Generator (DG)                                         | 159 |

|                                                                 |     |

| Bibliography                                                    | 163 |

|                                                                 |     |

| List of arrata                                                  | 160 |

## **Chapter 1 Introduction**

### 1.1 High-energy physics (HEP) background

Physicists have been trying to widen their vision for thousands of years, spatially in two extreme directions, the microscopic and the macroscopic. Concerning the extreme microscopic physics research today, the deeper humans want to see into the matter, the larger effort is made to reach that scope. Observations on the particle level are different than those in the human world. In the subatomic scale, this is generally accepted and evidenced by higher and higher reaction energy found in today's accelerators, for example, LHC (Large Hadron Collider), SLC (Stanford Linear Collider), FAIR (Facility for Anti-proton and Ion Research), and so on. Frontier scientists get the knowledge they want out of these giant machines, dozens of kilometres in size and several TeV in the reaction energy level. [1]

Concerning the extremely macroscopic physics, there are huge telescopes situated on the earth surface and floating in the space, for example, the Hubble Space Telescope and the being-built Giant Magellan Telescope. [2] [3] They observe the huge-size images of the universe and record the evolution of galaxies. Such macroscopic observations differ from the experiments in the HEP accelerators in that they do not affect the observed objects. However, the accelerator experiments are trying to reveal the secret of the initial universe, or the internal state of the extremely dense neutron stars. The microscopic and macroscopic physics are asymmetrical and different in approaches, although they have influence upon each other.

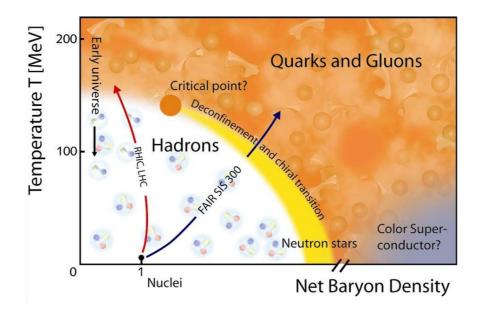

Besides the energy level an accelerator can reach, the target region in the phase diagram is also an critical factor during experiments are constructed. Different equipments serve different scientific purposes. LHC is mainly designed for researching the Higgs particles. [4] [5] FAIR in Darmstadt, Germany targets on anti-proton and ion research. [6] Due to the cost consideration, an accelerator normally feeds multiple experiments, categorized by regions in the phase diagram that an experiment focuses, as in figure 1-1. For instance, the CBM (Compressed Baryonic Matter) experiment in FAIR project is focused on high temperature and high baryon density; the PANDA (anti-Proton ANnihilation at DArmstadt) experiment is intended to study weak and strong forces, exotic states of matter and the structure of hadrons. Of course there is much space untouched in the phase diagram, which provides us with attractive possibilities. [7] [8] [9]

Not only the spatial size of particles under research goes extremely tiny, but also become their lives tremendously shorter. For example, lifetime of Sigma particles is from 1.48 x  $10^{-10}$  s ( $\Sigma$ ) to 1.8 x  $10^{-23}$

s  $(\Sigma^*)$ . [10] Such ephemerality has strong influence on the detector design as well as on the hit data processing.

Source: http://www.gsi.de/forschung/fair experiments/CBM/lintro.html

Figure 1-1 QCD Phase diagram for FAIR

In the particle physics experiments today, matter reactions are not really seen with human eyes, as the physics around one hundred years ago, but are *seen* through the sophisticated instruments. And thus, the observer of the under-size world has to compensate the effect from himself, according to the law of uncertainty. Thanks to the material, electronics and information technologies, people are able to build sharper *eye*s to detect the hyper microscopic events. And at the back-end, DAQ (**D**ata **AcQ**uisition) system serves as the storage, archive, and event selection part.

CBM experiment is a part of the FAIR system, located in GSI, Darmstadt, Germany. It is proposed to explore the QCD (**Q**uantum **C**hromo **D**ynamics) phase of high temperature and high baryon density. Researches such as simulating the initial stage of the big-bang and studying the centre status of neutron stars may benefit from its results. CBM experiment is featured by huge amount of data flow density of about 1 TB/s into the DAQ system. This characteristic leads to a self-triggered architecture for the DAQ, which will deliver possibly more events and higher data flow to the back-end processing modules. [11]

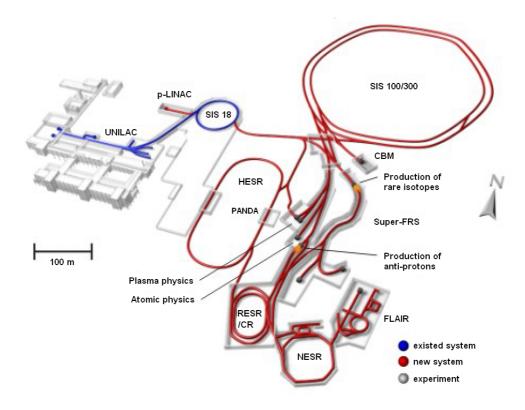

The accelerator of FAIR in development is SIS100/300, as figure 1-2 shows. It is expanded from the existing equipment, SIS 18, and is planned to feed several different experiments, such as CBM, PANDA, etc. The double-ring facility of about 1100 meters in diameter is supposed to generate intense high-energy ion beams, out of which secondary beams can be produced. CBM and PANDA both use self-triggered approach and the trigger selection is formally done in the compute nodes. [12][13] Comparatively, most experiments at LHC in CERN are implemented in level-trigger fashion, for example, the ALICE (A Large Ion Collider Experiment) and the ATLAS (A Toroidal LHC

### ApparatuS) experiment at CERN. [14] [15]

Source: http://www.gsi.de/portrait/fair/beschleuniger.html

Figure 1-2 CBM in FAIR

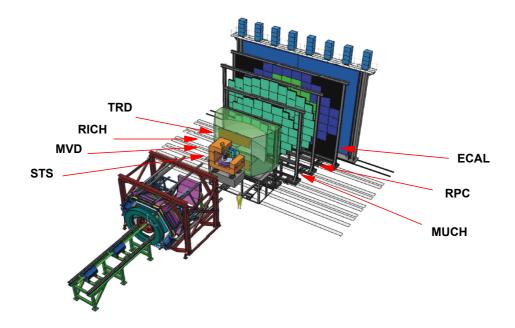

As shown in figure 1-3, CBM experiment is supposed to consist of the following major detectors, [11]

- Silicon tracking system (STS) and micro-vertex detector (MVD)

- Ring imaging Cherenkov detector (RICH)

- Transition radiation detectors (TRD)

- Muon detection system (MUCH)

- Resistive plate chambers (RPC)

- Electromagnetic calorimeter (ECAL)

Dependent on the sizes, distances to the beam source and physics purposes, the data rates and distributions vary a lot from detector to detector. For example, the STS has much higher data rate than the RPC. Within a single detector, the hit densities also vary according to radius and angle. This is simulated and experimented and has impact upon the DAQ strategy.

Source: CBM Experiment Technical Status Report, January 2006

Figure 1-3 CBM detectors

Data coming from the detectors are processed by machines in order to reproduce the physic events. Event building, either with software or with hardware, is the central task for the DAQ. Machines do most of the work, of course final decision is in man's hand. Information technologies support physicists with faster and more accurate recognition and identification of new physics. The DAQ portion is being naturally enlarged in the HEP field.

For example, the track finding research for CBM STS takes advantage of 3D Hough transform algorithm and tries to fit the algorithms into FPGA devices. [16]

Before the final CBM set-up, many small beam tests are carried out for different modules of the DAQ system. For example in December 2010, a 2.1 GeV beam test was done in COSY, FZ Jülich to test the updated development progress and to find out hidden bugs as early as possible. Similar beam tests have also been made in CERN.

### 1.2 CBM DAQ characteristics and the Active Buffer

The nature of CBM experiment is the huge data rate of about 1 TB/s due to the high reaction rate of about 10 MHz. If the average bandwidth of each cable, either copper or fibre, is 10 Gbps, the number of links should be about 1000. For the technology standard in 2011, Xilinx Virtex5 and Virtex6 LXT FPGA series can drive 5 Gbps link with its GTP. [17] [18] Therefore the 1000-link estimation is modest.

To process such a data density in the DAQ system, the technologies today and even in the next few years have to compromise between trigger speed and the event granularity. CBM experiment wants a fine observation of the very rare physics events and it does not want to sacrifice the precision.

Therefore CBM is trying a weak-triggered fashion in DAQ, in which the level triggers are not explicit. This brings challenge for DAQ. On the other hand, as a benefit of the triggering pattern, the DAQ latency is not critical to the CBM experiment.

Simulations of the experiment reactions at detectors are deliberated. They help to evaluate the detector geometry and the material utilization as well as the data flow distribution. The detector design and the DAQ data flow distribution are much dependent upon the results of these simulations.

Most of our design is based upon the simulations for STS events. Such simulations are helpful because they take advantages of the newest physics progress and are proven in previous experiments. <sup>[20]</sup> According to the STS simulation, we set the throughput for every buffer sub-system as 5 Gbps, which can be fit into 2 fibres.

However, simulations cannot tell us everything about the physics output, otherwise we would not have to build huge accelerators and detectors. As we are to find new physics, we should preserve enough redundant space in our design, to cover as many exciting corners as we can. For example in the DAQ system, the event rate should not be under estimated.

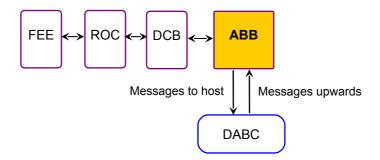

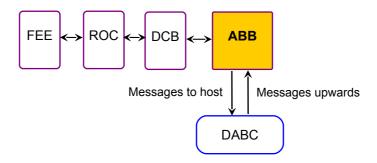

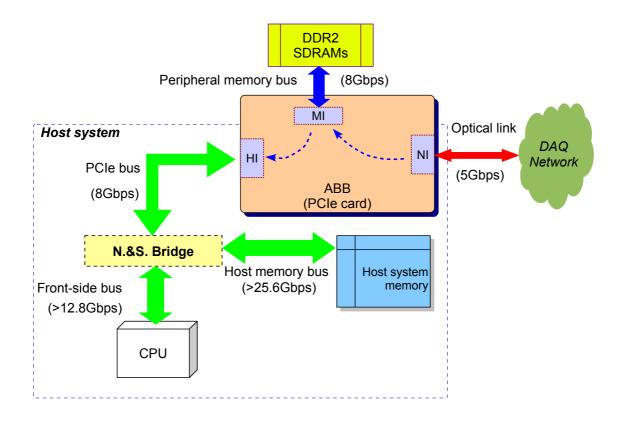

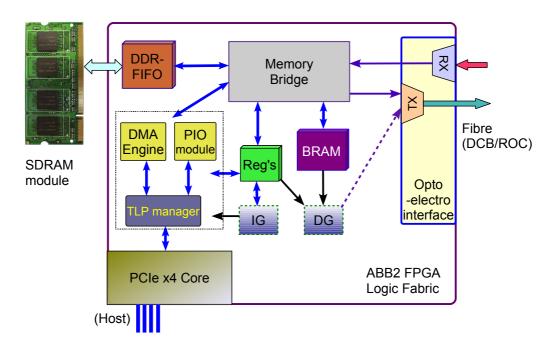

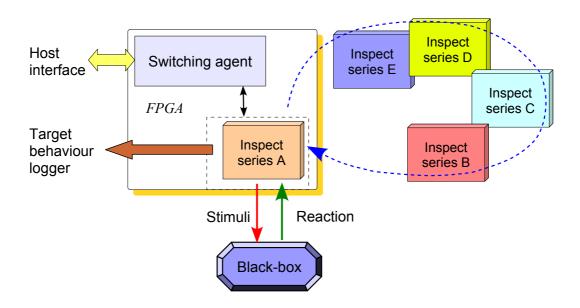

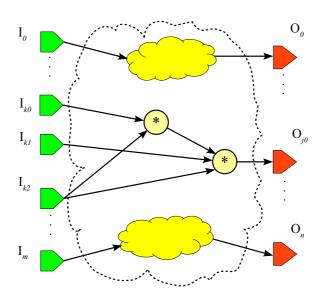

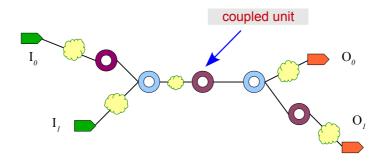

Figure 1-4 shows the DAQ chain for CBM. The DAQ system receives detector hit data from the FEE (Front-End Electronics) and the data travel through the ROC (Read-Out Controller), DCB (Data Combiner Board), ABB (Active Buffer Board) and reach the software framework DABC (Data Acquisition Backbone Core). ROC reads out the hit data from FEE or configures FEE. DCB organizes the data from ROC and manages the synchronization and possesses radiation-hard capability, which the ABB does not have.

Figure 1-4 CBM DAQ chain

The Active Buffer is the buffer element in CBM experiment for DAQ. Namely, it is not only for passive buffering of incoming hit packets, but also manages to carry out part of the first-level event selection (FLES) for the experiment. It is the last stage in the hardware portion.

Its first major function is to buffer the incoming hit packets over 2.5Gbps or 5Gbps optical links. Logically, the Active Buffer stands between the DCB and the back-end host computer. It carries out also event building, as the second major function. Taken as a black-box, it manages miscellaneous

classes of outgoing and incoming packets, whether data packets or control messages. Control messages can be CTL (control) messages or DLM (**D**eterministic **L**atency **M**essage). CTL messages are for the DAQ control purposes to the previous stages and DLM are for measuring and gathering necessary latency information for the DAQ system. The Active Buffer behaves similar to a dual-port memory, so we are trying to make a dual-port memory emulation logic on our Active Buffer board upon the commercial SDRAM memory modules.

From the FEE to the storage, there are many options to build the data path. Storage is mostly attached to a computer. High-speed data paths must be built between these hosts and the FEE. Considering the radiation-hardness and the distance between the front-end and the back-end, the data are firstly read out by the ROC. On account of fibre cost, data are to be aggregated and relayed in the middle by the DCB. And then the aggregated data stream goes into ABB. After ABB, software suite will do online-analysis, monitoring and supervising. Afterwards, the minimum amount of data are stored into the archive net. The ABB is the juncture point between hardware and software, and we develop a high-performance DMA (Direct Memory Access) engine over PCI Express Gen1.

In the future FAIR geography, the IT centre building locates about 350m away from the CBM building. <sup>[19]</sup> The cable cost between these two spots is a factor in data path development. Compared with copper wires, fibre transmission is better in spatial budget, noise tolerance, power consumption, etc. Therefore, optical fibre is the top choice in building the distant data route. Optical fibres and connectors match the requirement of high-speed data transport. Multiple-Gbps fibres with reliable transmission distance of multiple kilometres are purchasable and mature products.

To meet the requirement of the high rate of hit data, the Active Buffer system of CBM experiment takes the challenge of large, fast and intelligent memory design. A directly handy solution is to use the popular and favourable SDRAM modules as the memory kernel, which go easily to Gigabytes in size with benign price, meanwhile running at 2.5~5 GB/s bandwidth. However, due to the single address bus structure, such memory module cannot be written and read concurrently. The concurrent write and read is a fundamental requirement of the Active Buffer design. In this sense, a simplified vision of CBM DAQ buffer system can be modelled as a FIFO. Of course, the ultimate model is much more complex and intelligent.

For the first version, we work out a FIFO-style memory controller (wrapper) around the DDR-2 SDRAM module, which enables the concurrent FIFO standard accessing, without sacrificing the port bandwidth. In this way, 512 MB FIFO with concurrent speed of over 2 GB/s for both write and read is possible. This FIFO wrapper can be scaled to larger sizes, e.g. 1GB, 2GB and so forth. Such development is going on, targeting a really active and intelligent buffer system for the CBM DAQ. Compared with the IC market, FIFO device size is always lower than people expect. For example, the largest IDT FIFO is only 18 Mb for the year 2011. [21]

Dual-channel memory technology in current PC platform is a similar attempt to improve the throughput of the memory modules, where a pair of identical (DDR mode) SDRAM modules is used to double the memory throughput. Dual-channel memory gets support from the chip-sets and relieves the system bottleneck. [22]

### 1.3 Fast data path

The Active Buffer is implemented to transfer the high rate of data flow to the host memory space. At the most beginning of the prototype beam tests, Gigabit Ethernet and InfiniBand were used to deliver the data to the back-end due to their robustness and availability of software frameworks. As the development advances, DCB and ABB join in. A prominent advantage of optical communication in CBM experiment is the quietness and noise tolerance. [23] [24] Ethernet is a general network, but we do not need many features of it, such as retransmission, WAN (Wide Area Network) address resolution, etc.

Interconnect technologies such as PCI Express, HyperTransport, InfiniBand are proving technical perspectives in DAQ system. Almost every corner in the information technology is well driven by the Moore's Law. These data-path-dominated technologies involve also a lot in the integrity of the data content to provide a reliable link.

Among the high-speed interconnect technologies, PCI Express is a good choice for the ABB. PCI Express, usually abbreviated as PCIe or PCI-E, is a computer expansion card standard that is intended to replace legacy PCI, PCI-X and AGP (Accelerated Graphics Port). Its key difference apart from those older standards is the point-to-point serial link on the PHY layer. This makes it very easy to expand the bandwidth by multiplying link number. In this thesis, we use 4 PCI Express Gen1 lanes, which delivers 2.5 GT/s per lane. Another advantage of PCI Express is that it is software-compatible with older PCI drivers. This feature accelerates its occupation in the market. [25]

PCI Express devices build the bridge from the hit data links to the host nodes. They transfer data between the two high-speed buses, the optical and the PCI Express. So the protocol translation and flow control is implemented on such devices.

Another competitive candidate can be HyperTransport, which has also scalable performance and has no demand on license fee. [26] [27]

If every data over these data paths are moved by the host CPU (Central Processing Unit), the host resource will be exhausted in PIO (Programmable Input-Output) operations. Although PIO mode requires least firmware support, its performance is quite low. Typical PIO write performance in our Linux system is measured about 30 MB/s and PIO read performance only about 3 MB/s. For sake of higher performance over fast data paths and lower host CPU load, DMA mode is generally adopted in the data path card. For example in our tests, the DMA engine over 4-lane PCI Express Gen1 delivers over 700 MB/s for DMA write and over 500 MB/s for DMA read. A difference between these two modes of data moving is the size-dependency. Generally larger DMA size has higher performance but the PIO performance almost does not change according the transfer size.

In terms of the integrated circuit (IC), customized computing favours programmable devices. Data-path-dominated research and development often benefit from FPGA (Field Programmable Gate Array) technologies. High-end programmable logic devices are FPGAs, which provide fast development for complex logic projects. Internal structure of the FPGA is being improved for better timing performance and lower power consumption. High-speed differential serial transceivers are paid great effort in development. 10 Gbps transceiver modules are announced by Xilinx and by Altera. [28] [29] The Active Buffer is implemented in Xilinx FPGA, initially in Virtex4 FX40 for the

first version, later on Virtex5 LX110T for the second version.

As a natural extension of the embedded system research, integrating processors into programmable devices has accumulated valuable experience. Xilinx has previously PowerPC into VirtexII Pro series and Virtex 4 FX series. Later on till recently, MicroBlaze takes over the fashion for Xilinx FPGA. [30] Altera has NiOS II processors in their high-end FPGAs. [32] The corresponding software development suites are provided for these embedded processors. For example on the ROC board, the embedded processor (PowerPC) of the FPGA (Virtex4 FX20) is used to manage the read-out behaviour and Ethernet access port.

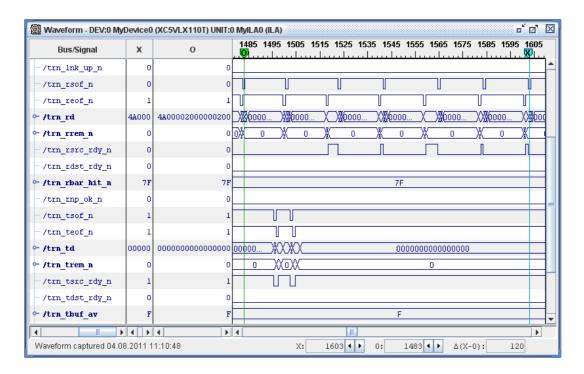

As debugging approach, Xilinx has ChipScope and Altera has SignalTap II. Such structures give the developer a very good approach to check the internal timing. [33] [34] In the Active Buffer development, the ChipScope facility shows many cases that were not covered by the simulation, and therefore, helps to improve the verification.

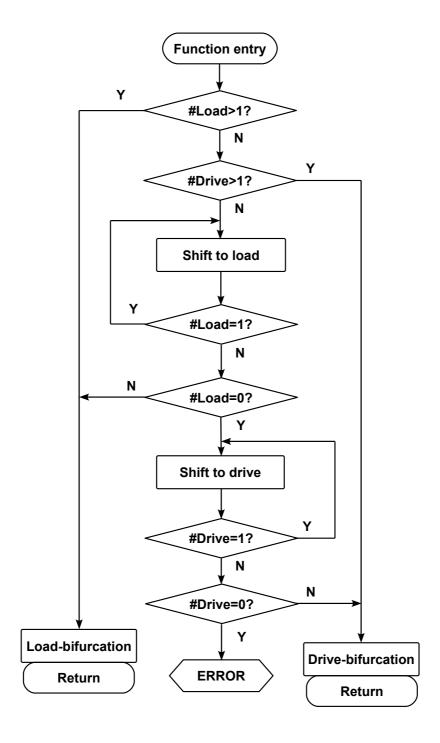

### 1.4 Dynamic partial reconfiguration

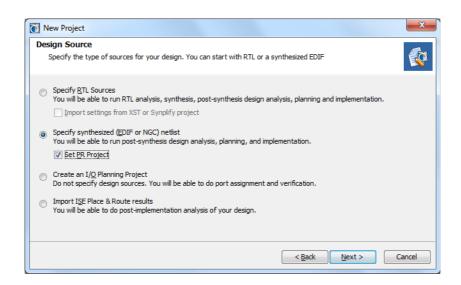

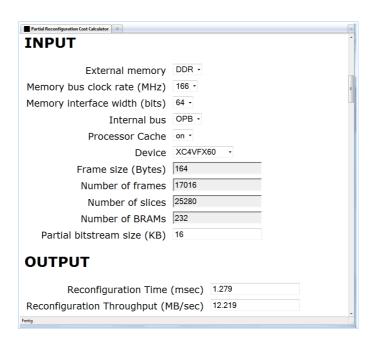

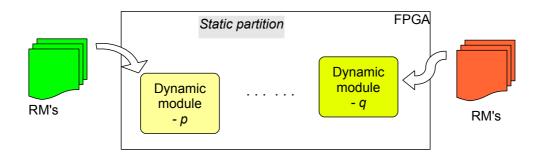

The DMA development was done in the Heidelberg University and the soft PCI Express core for Virtex4 FPGA was licensed to research in universities. Therefore GSI cannot use the design, although the logic implementation in the FPGA is transparent to GSI. A solution for such situation came from the dynamic partial reconfiguration (DPR), which encapsulates the protected module (PCI Express core) and provides the final user with dynamic non-licensed modules. With the progress in Xilinx FPGA, PCI Express core has been upgraded to hard-macro in Virtex5 and Virtex6, so that the license problem is no longer there for GSI. However, the DPR technology is still benefiting the high-end FPGA projects.

Given a type of FPGA, the resource is a limited parameter, which has influence not only on price, but also on the board size and power consumption. In chapter 6 we will see that our project is confronted with this universal problem.

DPR is an attempt to mimic the hardware system to a software system. Due to the nature of hardware (gate-based model, wire latency, power-dependence, etc.), the hardware system cannot be so flexible as a software one, in which individual module is renewed just by recompile and reload. Software is supported by the operating system. Hardware cannot have such supporting system to play flexibility on it. However, with recent progress in Xilinx DPR software suite such as PlanAhead, the implementation of DPR becomes much easier.

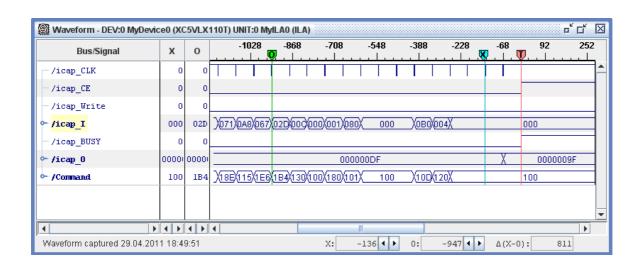

ICAP (Internal Configuration Access Port) is available in Xilinx FPGA families, which makes it possible to load a partial bit file to a reconfigurable module on-line via high-speed general paths, such as HyperTransport, PCI Express and so on. [35]

DPR application has to cope with the boundary clearance between modules. Former DPR projects with Xilinx FPGA used bus-macros to isolate the boundaries and nowadays the bus-macros are no longer needed, while the boundary decoupling is strongly recommended. [36]

In DPR we adapted logic design for bus-macros or for boundary decoupling, both expecting HDL reuse. Without boundary processing, the timing convergence goes mostly to fail across partitions.

If an FPGA application contains time-mutexed modules, DPR can generally save the resource and further make place for more logic functions in one device.

In most recent years, Altera also starts to support dynamic reconfiguration and partial reconfiguration in their FPGAs. This is a good sign for the DPR field, since two FPGA giants are sharing a vivid world in information technology. [37]

### 1.5 Logic design reuse

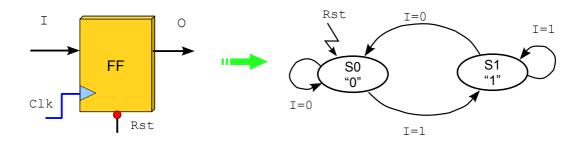

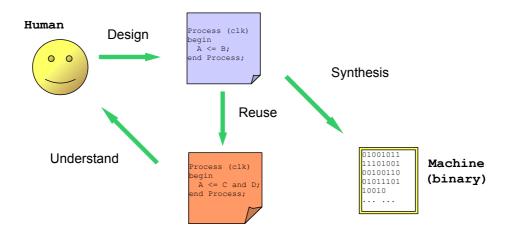

In the Active Buffer logic development, both VHDL and Verilog HDL are used. And in the DPR experiments, the VHDL codes had to be rewritten for the boundary processing. Although the rewrite was so straightforward and seemed to be simple enough, it took much time to get the rewritten design working as the original one. To improve the efficiency of similar rewrite practice, HDL-level code reused is studied in this thesis.

Code reuse in HDL design is wanted especially when pipelines are to be inserted into original design to compensate the application of synchronous bus-macros/boundary units between the modules in DPR experiments. Also, such reuse is evidenced by the fact that most of HDL design are somehow overlapped in functions, but hard to be reused by each other.

The two conventional mainstream HDL are VHDL and Verilog HDL. VHDL was advocated by the U.S. Department of Defence for digital circuit documentation in 1980s. It is a strongly typed HDL. It helps the synthesizer to check the syntax with ease. The user is well regulated to prevent typing errors, although it is not case-sensitive. [38] Accellera is responsible for making the VHDL standards and the most recent VHDL revision (IEEE Standard 1076-2008) was released in 2009. [39]

Verilog HDL was originally invented as a simulation language in around 1983/1984 by Phil Moorby in the company Gateway Design Automation (which was in 1990 purchased by Cadence Inc.). Cadence has now the right of Verilog HDL as well as Verilog-XL. Verilog HDL reference more features from C and it gives the user more flexibility. The up-to-date Verilog HDL standard is Verilog 2005 (IEEE Standard 1364-2005). [40]

Although these two major HDL's came from different area, their purposes are quite similar. However, VHDL covers broader range of digital design and Verilog HDL works better in simulation.

There is also HDL brothers such as ActiveHDL, JHDL. [41] [42] SystemC, SystemVerilog, etc. came into being with the anticipation of enhanced aspects, e.g. ease of verification, good usability for software developers. [43] [44]

Design tools convince the scientists with reliability and fast development cycle in the EDA (Electronics **D**esign Automation) field. Design suites of Cadence, Synopsis, Xilinx, Altera, Mentor Graphics, etc. update themselves more than once a year. Design, verification as well as project management are better handled. [45] [46] [47] [48] [28] [29] [49]

All the effort is to make the digital hardware design easier to average engineers. Out of commercial reasons as well as the development tradition of a group, some designs are in VHDL, some in Verilog, and some in SystemC or SystemVerilog for verification. Actually an engineer which uses one design language does not have to endeavour much effort to exploit the advantage of another one. The EDA

world does not need so many languages because they just establish unnecessary barriers among engineers or groups and bring confusion to beginners. However, no one single language is so perfect that it can eliminate all others, just similar to the software world.

As the mainstream HDLs today, neither VHDL nor Verilog HDL concerns the "dynamic" reuse of the source code, as we experienced in the DPR projects. HDL codes are created, debugged, verified, but reuse of the previous codes sometimes even takes the same long time as to redesign it all over again from scratch.

The HDL code reuse study in this thesis is to prove the feasibility of code reuse and to suggest the DPR tools to integrate part of such functions into their frameworks. A DPR user should focus on the partitioning of the function modules and their cooperation, instead of the pipeline shifting or elaborating.

Reusability, reliability and readability are top favourable properties of a design code in electronics. Code reuse, or HDL code reuse, has been considered and studied for a long time in EDA world. Plenty of IP (Intellectual Property) cores are available from electronic companies and from the open-source community. These cores, or macros, are made with great verification effort and minimized bugs before being released. Not all IP cores save financial cost, but they do save time for development. Suppose to redesign an Ethernet MAC controller, even a skilled engineer cannot complete it within one week, but the existing IP core may work in just a work day. However, most of the progress is limited in the "static" reuse scope, where the original design is literally kept in the new design as a block. The reusability is achieved by the pre-paid development time to make the IP cores reusable. [50] The reuse technology is actually reuse requirements rather than reuse tools. Reusing an arbitrary (syntax-correct) HDL design has not been explored. Such study is not directly related to the Active Buffer development, but it has general meaning for the logic designs in the future.

### 1.6 Organization of the dissertation

This dissertation is to design a buffer system for the CBM DAQ, which not only stores the events, but also makes the necessary acceleration for event building. The questions expected to be answered per chapter include,

Chapter 2, how to build the buffer with enough large size and sufficient bandwidth?

Chapter 3, what kind of data path should be applied to the interface between the network and the host and how to build it?

Chapter 4, how about the performance of the designed buffer system?

The focus is on the Active Buffer design and some related issues aroused from its development. Thereby another two questions might appeal to the reader,

Chapter 5, how can a firmware module have the dynamic loading flexibility as a software module?

Chapter 6, how to accelerate the logic development in terms of HDL reuse?

## **Chapter 2** The Active Buffer system

#### 2.1 Introduction

As mentioned in chapter 1, the DAQ system of CBM experiment is characterized with the weak-triggered pattern due to its huge amount of data flow, especially for data-intense detectors such as TRD, STS. The trigger decision is distributed to a wide range of units along the DAQ chain, in order to lose as few events as possible.

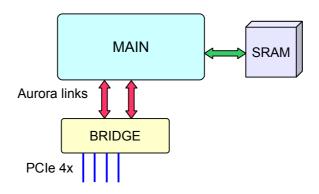

Concerning the large data rate into CBM DAQ system, we need a DAQ chain to get the data off the FEE and move them to applications, the DABC. This chain is divided into three parts, ROC, DCB and ABB, which are all equipped with FPGAs because integrating them all into one device is not practical, as shown in figure 2-1.

Figure 2-1 DAQ chain diagram (duplication of figure 1-4)

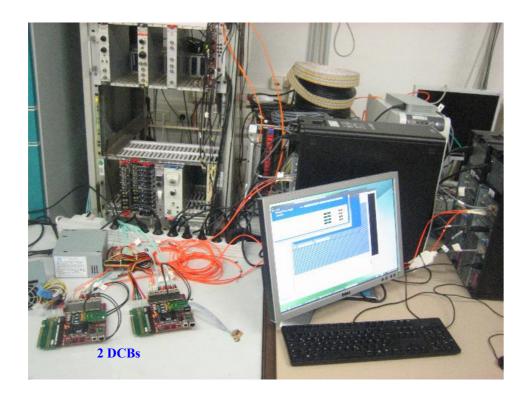

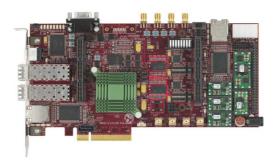

Figure 2-2 is a photo with the major DAQ chain elements, taken from CBM COSY beam test in December 2010 in FZ Jülich. In the set-up, we use 2 DCBs connected to 2 ABBs (plugged in the PCs), and 8 ROCs all connected to DCBs.

DAQ system and FLES (First-Level Event Selection) system together get the data off the detectors, process the events, and store them in the back-end storage media, in format which is eligible to the physicists. FLES is logically placed after the DAQ section. It makes initial event building and selecting the epoch boundary out of the DAQ data stream.

Figure 2-2 DAQ chain set-up in COSY beam test December 2010, FZ Jülich.

ROCs in the cave (not in this photo), and ABBs in the computer's PCI Express slots are all connected via the orange fibres to the 2 DCBs on the desk.

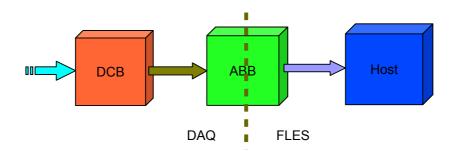

Between the DAQ and FLES is the interface component, the Active Buffer board (ABB), as shown in figure 2-4. Before ABB, the DCB manages the data combining, link balancing, as well as the network protocols. The data stream arriving at ABB is much smoother and more balanced, so that the links can be well utilized. In this sense, ABB is not only a buffering system, but also an event-building assistance system. The content of the data stream is moderately analysed for the sake of the FLES/DABC convenience. FLES is made up of computer farms and the work in it is organized in the software packages. [51] [52] [53] [54]

Large buffer with event building assistance is a scenario in the ABB development. The buffer pattern can be RAM or FIFO. The event building is ideally epoch rearrangement in the DAQ system, which is namely "active". However, in the starting phase of the project, the event building function is very rudimentary, and most event building is done by the software and hardware provides the indices to help the software sorting the data packets.

The size estimation for the Active Buffer can be only roughly done with the epoch duration and event building requirement. The epoch length is about 10 µs and the input data rate via the two SPFs is 500 MB/s (5 GT/s). If an event building takes about 1000 epochs, the data amount should be larger than

$500 \times 10 \times 1000 = 5 MB.$

We should reserve certain leeway for the software application as well as for the future event building development, so a buffer structure of over 16 MB should be the minimum requirement on the Active Buffer size.

In the initial phase, we used to implement a 128KB built-in FIFO in Virtex5 FPGA as the Active Buffer prototype. In the software test, this size turned out to be too small. Concerning the limit of FPGA BRAM resource, built-in FIFO should also not be the final solution.

#### 2.1.1 Active Buffer

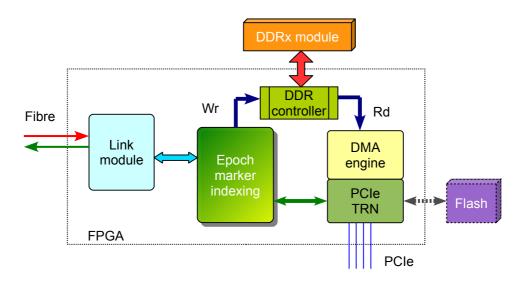

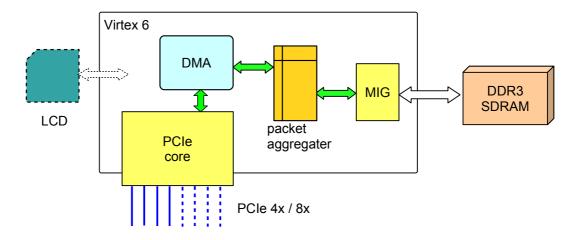

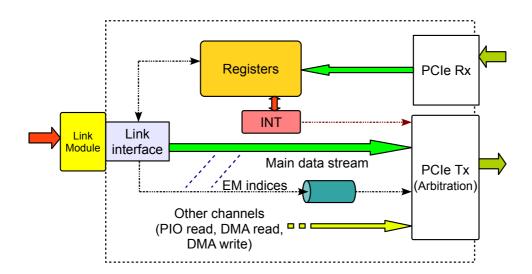

The Active-Buffer kernel is illustrated in figure 2-3, which uses DMA engine over PCI Express as the data path.

As shown in figure 2-3, the epoch marker indexing module is designed as the event building assistance module. Some basic settings for the event building are considered to be stored into the Flash on the board, but it is not a must (as denoted with the dashed line).

Figure 2-3 FPGA modularization for event building

One option to implement the ABB function in figure 2-1 is with software nodes. Another option can be a system without PC. The data stream is buffered, filtered, and transferred to the storage. Such architecture (without PC) is available for a more succinct system and takes smaller space. However, the processing nodes will nevertheless be installed. And that is why we take the advantage of the standard data path specification, PCI Express. Other standard candidates can be HyperTransport, InfiniBand, or Gigabit Ethernet.

Located in such a position, the ABB function must include high-speed links from the DAQ and high-performance paths to the FLES. A reasonable choice for this combination consists of fibres and PCI

Express lanes. And to be suitable for this function, the central device on ABB should be high-end FPGA, which can be configured to transfer high-speed customized data packets.

As figure 2-4 shows, the ABB sits between DAQ and FLES and its functional partitioning in terms of hardware and software is blurry.

Figure 2-4 ABB between DAQ and FLES

Event building is the major purpose for the Active Buffer. Hit data coming from multiple ROCs are merged (combined) somehow by the DCB, before they land on the ABB. If hit data are reordered or filtered in the host memory, the time cost of the host CPU will be higher than the system, in which the event building is done in hardware. On the other side, the ABB board has enough resource to carry such tasks out. What the host needs to do is to set some rules during the initialization phase and then the FPGA on ABB can accordingly execute the reordering and filtering before transferring the events to the host memory (via DMA). These rules are, from the present vision, some parameter registers that contain control information about the event building policy. These registers of rule primitives should be set in a way of simplification and uniqueness (no ambiguity). They can be static, being defined at the most beginning of an operation. Or they can be dynamic, and the FPGA gathers the event building strategy during beam.

The hit packets from different sources (chips, channels, etc.) are combined through the DCB links and arrive at ABB. The Active Buffer (event buffer) can be 9× bits (e.g. 72-bit) wide with additional framing information, but the software accesses it only in 8× mode (e.g. 64-bit). The framing information is missing to software. If these packets are written into the host memory without preprocessing by the ABB card, special effort is expected for the software to distinguish events/epochs out of its DMA buffer. So it is better for ABB to dispatch the hit packets before making upstream DMA.

The event building involves analysis over the incoming hit packets. Information in the packets such as time stamp, channel number and chip number are the candidate tags to be analyzed. The hit packets will be first dispatched to the peripheral memory and afterward, transferred to the host memory. The dispatching is what the event building module will do. And the original DMA engine is categorized as transport module (data moving).

For current configuration, the fibre link runs at 2.5 GT/s, and the PCI Express Gen1 4-lane provides 8 Gbps (10 GT/s) peak bandwidth per direction. We use Virtex5 LX110T as the FPGA device, which

has 16 tiles of GTPs, for SFP interfaces and for PCI Express serial interfaces. Each ABB has two SFPs. So the Buffer should transfer at least 4 Gbps per direction.

Another reason to choose PCI Express is the availability of the stable open-source PCI driver under Linux in our research group. This driver and the companioned library have been integrated into the DABC suite and works reliably in the real DAQ experiments.

The data density varies much from detector to detector. Our DAQ system (including FLES) is mainly targeted on the STS, which has the largest data flow rate among the CBM detectors.

#### 2.1.2 Traffic classes

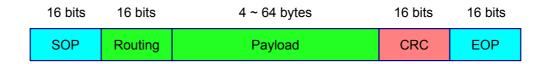

Hit, control and synchronization data packets travel through the DAQ system. The data packet format is shown in figure 2-5. [55]

Figure 2-5 Packet format in CBM DAQ system

Further, they are categorized into three traffic classes. [56]

#### 2.1.2.1 CTL protocol

The CTL traffic class is responsible for the coordination between the front-end and the back-end. It does not involves high data rate, but helps to provide the reliable transportation of control and monitor messages. This class is specially implemented to avoid communication crash due to message loss. CTL is in low frequency and needs no buffer for it. Decoding and executing is enough.

One of the important CTL packets downstream is the epoch marker, which defines the epoch boundary.

CTL message tests have been well proceeded because they are the management for almost all DAQ activities. Application-level tests for CTL message latencies result in 0.138 ms for write-read and 0.053 ms for read.

#### 2.1.2.2 Sync mechanism (DLM)

DLM (**D**eterministic Latency **M**essage) is a lower-level message class. It is sent periodically to reach the parts that need synchronization. DLM messages have been very fundamentally tested and they are supposed to be further accomplished in terms of the protocol. DLM occupies only a very small portion of the overall bandwidth.

#### 2.1.2.3 DAQ class

DAQ data is the major part of detector data flow and takes over 90% of the total bandwidth. DAQ class needs a large buffer system. When 2 ROCs are connected, DMA performance in transferring DAQ packets is about 300 MB/s on ABB2 in beam test measurements.

A hit packet consists of a precise time-stamp and the hit coordinate information.

#### 2.1.3 Hardware-aided indexing

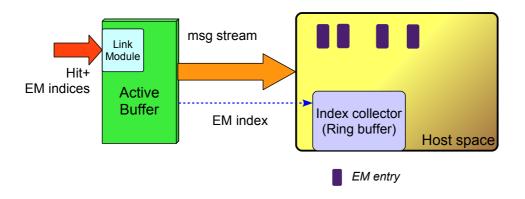

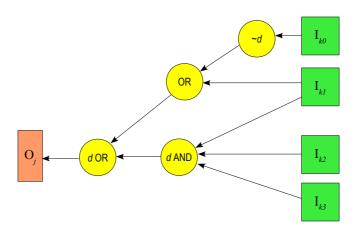

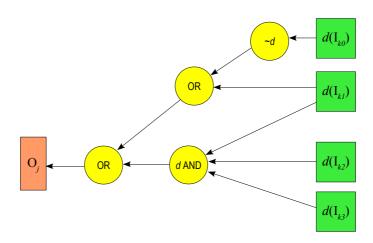

Other than a pure buffering function, the ABB carries out also the FLES assistance tasks in event building. For current version, epoch markers are indexed and stored in a ring-like buffer in the host memory space, which helps the applications by the event reorganization.

The epoch marker (EM) in CBM DAQ system plays an important role for event building and hit reorganization. With current configuration of ABB, the upper-level software has to search these epoch markers through the whole data in the memory space, because the ABB only moves the incoming hit data packets into the host memory space according to the DMA descriptors and does not have the knowledge inside the data stream.

The need for a new epoch marker handling mechanism arises from the software applications. Epoch marker indexing or selection in the firmware will simplify the software procedures and therefore improve the system capability by relieving the host CPU load.

For future ABB development, such specific message handling will take place for similar boundary identifying of different hit packets. So the implementation of EM handling is a good practice for the future DAQ operation.

As figure 2-6 shows, a ring-buffer is used for collecting the EM indices and it is a part of the host memory space. The Active Buffer logic distils the EMs out of the main data stream and sends them to the ring-buffer in the host in proper timing.

Figure 2-6 Epoch marker handling concept

EM handling is discussed in *Appendix A.6*.

Similar requirement comes out of the SYNC messages, which helps to define the time slices. The SYNC indexing will benefit from the EM indexing design. In the next version of the Active Buffer design, multiple marker indexing shall be supported.

#### 2.2 Buffer kernel

FIFO (First-In-First-Out) is generally used for data buffering. If the data production (writing) and data processing (reading) are not of the same rate, the buffer should be built towards a better overall performance. If the two clocks, write and read, are not of the same rate, the buffer is usually used to separate the clock domains.

Ideally, the buffer works the best if the FIFO has infinite depth. However, on practical circuits, the resource is never unlimited. Therefore, we can only try to make a buffer as deep as we can to approximate that ideal condition.

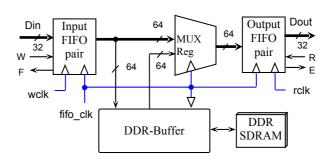

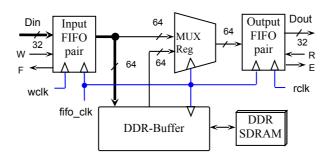

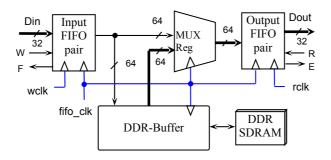

For a simplified FIFO control, the write rate and read rate should be approximately equal, or the read speed is a little bit faster. In this way, the FIFO is not expected to have a deliberated flow control. Effective buffer utilization reserves not too much space vacant.

Larger FIFO has advantage over smaller one in a buffer system without flow control. The larger (deeper) the FIFO is, the lower overflow risk we have in application. However, FIFO product size is limited by the IC technology, which stomps below hundred million bits by 2011. And such large-size FIFO usually costs several dozens of dollars. Compared with SDRAM, pure FIFO chip density has less competence. In programmable devices, such as FPGA, the possible FIFO is yet smaller because of the resource limitation and expensiveness.

Most FIFO applications in DAQ research field are combined with programmable devices. So we have the solution like

Such a solution increases the FIFO depth easily over hundred million entries.

Of course the FPGA is not only used for building FIFO. Most resource is available to other functions.

Due to the irregularity of the arrival and departure, the buffer occupancy is fluctuating. This fluctuation causes the buffer full for some specific time. And when the buffer is full, there are usually two ways to process,

- (1) set flow control upstream; or

- (2) abandon the overwriting data.

The first solution demands extra logic to control the data flow speed so as to make the system structure complex and the behaviour difficult to predict; and the second solution leads to data loss. Different applications use different buffer management and there is no universal solution.

Flow control can not be essentially eliminated with our solution, but it can be immensely reduced. For

a buffering system with quasi regular flow rate, the flow-control logic is able to be spared.

For a buffer system with flow control, the buffer depth has influence upon how frequently the flow control actions. Certainly fewer flow control actions offer higher performance in terms of throughput. A larger FIFO can lower down the flow control probability than a smaller one.

With variable aspect-ratio FIFOs, half-bus access is supported. However, in our project, only full-bus access is supported, because otherwise the memory kernel (SDRAM) controller would be much more complicated.

Four points to note again in building such a FIFO wrapper are,

- A) data into and out of the SDRAM are aligned to row boundary, to have a better and simplified management over the SDRAM module. Only when the data amount in the small input FIFO block reaches a row size of the DDR SDRAM, the data transfer into the DDR-Buffer is carried out. And on the opposite side, only after the output FIFO is able to accommodate a row-size data, the data are directed from the SDRAM to the output FIFO again. The benefit lies in minimized row-open and row-close operation for the SDRAM. Hence, the hazard of logic error is diminished.

- B) internal data run in double-width data bus, i.e. 64-bit bus, which suffices the possibly full data rate, even if the SDRAM overhead such as auto refresh and row recharge has to be taken into account. This helps to keep the external full-empty state the same as a conventional FIFO, which means, full state is only expressed when all the memory units (small FIFOs and SDRAM module) are occupied; empty state is only expressed when all the memory units are vacant. This is also valid for almost-full and almost-empty flags.

- C) PAD delays are variable and calibratable, so that the design has general meaning to the variety of boards. On the Xilinx FPGA board, IDELAY is used with variable delay value. Auto-calibration logic acts in the initialization and finds the optimized delay parameters for the IO pins.

- D) SDRAM module clock frequency is some percent higher than the external FIFO clock frequency, in order to compensate the SDRAM operation overhead such as refresh. Taking burst length = 4, page size = 128 as example,

- Page activate needs 2 cycles of DDR clock

- Page precharge needs 6 cycles (without auto-precharge)

- 14 cycles of auto-refresh are inserted every 1024 cycles

Hence, the minimum clock upgrade ratio is approximately

$$1 + (2+6)/128 + 14/1024 = 1.08$$

In our test, we use 150 MHz clock for the SDRAM module compared to 125 MHz of the external clock, where the ratio is

$$150/125 = 1.20 > 1.08$$

Such increase upon clock rate is done by the frequency synthesis module in FPGA.

#### 2.2.1 Requirement

The FIFO specification should be well complied, which means, on the write and read ports the timing diagram is the same as the standard FIFO,

- Write enable comes together with the input data.

- The output data goes out at exactly the next cycle of read enable (provided the FIFO not empty).

- The Full flag prevents further writes into the FIFO and the Almost-Full flag tells a possible overwrite hazard.

- The Empty flag is asserted when there is no more data in the entire buffer system and the Almost-Empty flag tells a possible under-read hazard.

- The FIFO should support asynchronous write and read, which means, the write clock and the read clock rates can be different.

However, the DDR (II) SDRAM module has certain overhead during operation, e.g. page-open and -close, refresh, which makes the real-time receiving and sending of data impossible. A sub-buffer layer is needed between the user logic and the SDRAM modules. Therefore, setting smaller standard (asynchronous) FIFO modules at the input and output ports is a reasonable solution, so that all the requirements above are naturally fulfilled. The smaller FIFO here is called proxy FIFO.

Random data flow arbitration between the smaller port FIFOs and the SDRAM module is complex and prone to faults because of the page initialization actions entangled with write or read control of small FIFOs. Therefore, we have the solution of page-aligned internal data transfer, in which every transfer involves one and only one page initialization of the SDRAM module. Such regular operation helps to simplify the arbitration logic and to reduce the debug effort. And as a result, those smaller standard FIFOs at the interface ports should be deeper than one page size of the SDRAM module. In our system, 512-word FIFOs are chosen on the safe side, corresponding to a 128-word page size of the SDRAM module.

#### 2.2.2 Logic building

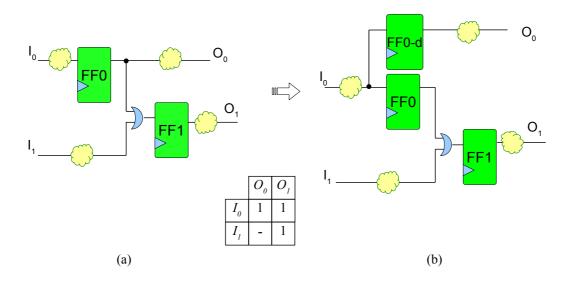

Following discussion is with a data bus width of 32 bits, double clock edges. And in practice the data bus can of course be wider.

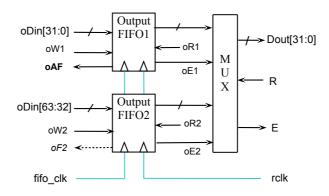

The internal asynchronous FIFO blocks in FPGA are together used for this design. Of course the internal FIFOs are quite small in size and we use altogether 4 of them to make the conversion, 2 for input port and 2 for output port. They are used in pairs because of the double clock edge transfer.

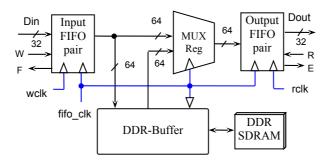

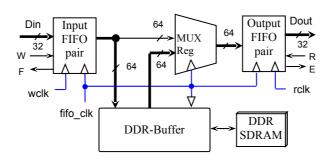

The diagram is depicted in figure 2-7. One pair of these 4 small FIFO blocks is connected to the input port, and the other pair to the output port. Between them is a DDR buffer control module, which takes over the processing upon the external DDR SDRAM module. This DDR buffer receives the input written data and decides whether to transfer them into the SDRAM or to the small output FIFO. If the saved data in SDRAM are to be transferred to the output port of the large FIFO, they are arbitrated by

a MUX before the small FIFO block of the output port.

To simplify the refresh operation of the DDR SDRAM, the internal transfer takes 512 entries as the block size unit. In this way, every read or write access to the DDR SDRAM is well aligned to the page boundary, to achieve simplified and robust control logic.

As can be seen in figure 2-7, the internal data bus is 64 bits wide. This helps reducing the possibility of flow congestion and to achieve sufficient time for processing the input data, which can be full rate. The data flows alternate among the channels in the data path of the large FIFO. The DDR buffer module consists of two major parts, a FIFO-to-DDR interface and a DDR-to-FIFO interface. With these two interfaces, the DDR SDRAM is "transformed" into FIFO.

Figure 2-7 DDR-FIFO block diagram

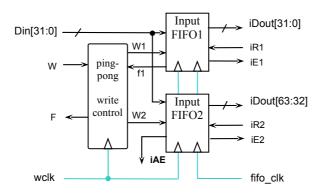

Figure 2-8 shows the input FIFO details. It is built upon a pair of primitive FIFOs from the FPGA vendor.

Figure 2-8 Input FIFO

The "ping-pong" write-control in figure 2-8 illustrates the alternate writing into the 2 input-FIFOs, i.e. the rising-edge 32-bit data is put into input-FIFO2, and the falling-edge data into input-FIFO1. A waterline, iAE, is set to control the transfer from the input FIFO pair into the DDR-Buffer, instead of directly into the output FIFO pair. iAE flag is asserted when  $N \le 128$ , where N denotes the entry

number in the FIFO.

Similarly, output FIFOs are built at the output port of the hybrid FIFO, as shown in figure 2-9. This pair of small FIFO blocks is multiplexed for the final FIFO output. Another waterline signal, oAF, is used for flow arbitration. When this signal is asserted,  $N \ge 384$ , the successive data will be put into DDR-Buffer instead of into the small output FIFO pair.

Figure 2-9 Output FIFO

In figure 2-9, the output MUX is not synchronized because of the empty flag timing requirement. These two waterline signals, iAE and oAF, help to keep the buffer performance while the SDRAM is well page-aligned.

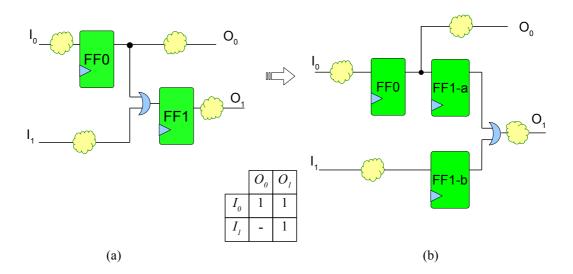

Next, we discuss the data flow between these two channels. Figures 2-10 through 2-13 are the different situations for this large FIFO and explain how the data flow, where the bold lines denote the current data flow paths for each situation. In the brackets attached to each figure, the full-empty states of the input, output, as well as of the total FIFOs are listed.

Figure 2-10 Data flow - loose

(DDR-Buffer: empty= 1; Input-FIFO: empty= 0; Output-FIFO: oAF= 0)

Figure 2-11 Data flow – congested output

(DDR-Buffer: empty= 0/1; Input-FIFO: empty= 0; Output-FIFO: oAF= 1)

Figure 2-12 Data flow – weak input

(DDR-Buffer: empty= 0; Input-FIFO: iAE= 1/0; Output-FIFO: oAF= 0)

Figure 2-13 Data flow - dense

(DDR-Buffer: empty= **0**; Input-FIFO: iAE= **0**; Output-FIFO: oAF= **0**)

The flags coherence is especially handled because there are more than one data buffer stages and the mutual effect is made complex by the SDRAM overhead operations. All buffering stages must be well monitored to ensure the entire FIFO reports correct flags. The Empty state should be asserted only when there is no more data in the whole data module. And the same must be guaranteed for Almost-Empty as well as for Full and Almost-Full flags.

Data count logic is additionally designed, which provides information about the data amount to the upper-level application. For such a large-size FIFO, the data count has to be deliberated separately. As the standard FIFOs, the data count can be synchronized to the write clock or to the read clock. We have only implemented the data count that is synchronized to the read clock. The write-clock synchronized data count is not implemented, because the write port does not have to know the information of how many data inside. At the write port, the almost-full signal is sufficient to assert the flow control. The size of the FIFO we use is a little bit larger than 512MB, so the width of the data count with respect to the 64-bit bus should be greater than 26 bits. Therefore we use 27 bits for the FIFO data count.

#### 2.2.3 Test and verification

#### 2.2.3.1 Simulation

All behaviour of this transformed FIFO follows the approved FIFO specification, because the proxy (input and output) modules are real FIFOs. FWFT (First-Word-Fall-Through) mode is not supported in this version because of the cascaded FIFOs along the data path and the block-buffering property of the input FIFO. The EMPTY-falling logic has a bigger latency than the standard FIFO because the first data into the FIFO has to be transferred from one FIFO (input-FIFO) to another (output-FIFO). EMPTY is deasserted when data is available in the output-FIFO.

To make a strict verification over the wrapper logic, we build the simulation environment including the wrapper logic and the DDR SDRAM simulation module. Micron Co. provides the simulation module for their DDR chip in Verilog HDL. And our simulation is behavioural, to test the functionality of the logic.

- (1) Independent write and read clock rates variable within a defined range. The frequencies of the write clock and the read clock can change randomly. This is the requirement for an asynchronous FIFO and also helps to create the different ratios of read and write.

- (2) Random write and read rates variable. The write and read densities are varied over time, to get the Full and Empty function tested. Both Full and Empty signals are expected toggling. For the write and read rates, we use double-scale randomization, which means the involved signal varies both in small time-scale and in large time-scale. If the rate is randomized only with one time-scale, the toggling of empty or almost-full will be hard to observe, because they are averaged in a larger scale. Multiple-time-scale randomization prevents data flow smoothing in large time scale.

- (3) Practically, the Empty state is easy to get because it happens at the most beginning initial state and sometimes during lower data rate. However, the Full signal goes up after a quite long simulation time, if we use the whole size of the SDRAM. The full-size simulation also takes longer time because

of the multiplied memory consumption. So we use the partial size of the SDRAM, by setting it to 1/8 of the whole size and the Full signal toggles much more frequently. This is equivalent to shrink the SDRAM address size, e.g. from 15 bits to 12 bits. The smaller size should be limited over a column size (8KB) and the bank boundary should also be straddled, so that the points where errors are likely to take place are covered. In this way, we can make sure the logic works for the true-size memory module and the prototype simulation can prove the real functionality. Such address down-scaling makes the simulation faster and the verification process is accelerated.

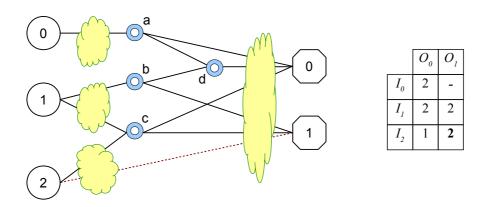

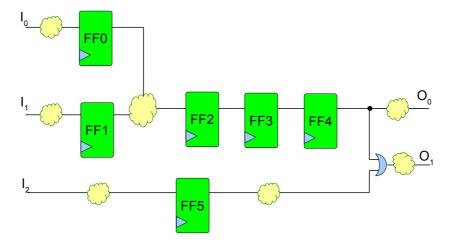

### 2.2.3.2 Self-test

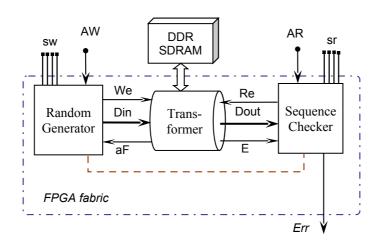

Figure 2-14 shows a self-test scheme for the design. A pseudo-random (Linear Feed-back Shift Register, LFSR) generator feeds data into the FIFO logic with pseudo random write enable, and the output data are checked by the checker. The read enable is also calculated from a pseudo-random generator. The generator and checker use the same sequence of the data stream. When the checking fails, an error signal is asserted. The error signal is verified in an error-injection test that generates deliberated failure for all sorts of errors and it is asserted as expected.

In bench test, two buttons, AW (Accelerate Write) and AR (Accelerate Read), are used to accelerate the write or read. Write enable and read enable are both combinations of the pseudo-random sequence and the manual button state. Without pressing these buttons, the read and write both run at a lower speed, e.g. 1/16 speed. And the acceleration buttons can drive write or read to a configured speed, in order to force the buffer full or empty or critical. The configured speed is set by some switches (SW for write, ST for read) on the test board. For instance, discrete speed grades, 1/8, 1/4, 1/2, full speed and combination speeds such as 3/8, 5/8, 3/4 or 7/8, are available. These buttons make the test closer to a random environment. Of course, the generator logic takes care of that the FIFO is not overwritten. When it is full, the write must stop and the random registers stops counting up.

Without these buttons, the data flow inside the FPGA is more regular and some subtle bugs might be hidden even if a (pseudo-)random sequence of write and read is used, because the logic can never be able to generate true random events.

Figure 2-14 DDR FIFO Self-test diagram

After a thorough test over 4 hours, with automatic and manual modes mixed, the error signal is never asserted. That means the large FIFO has succeeded in emulating all functional behaviours of a standard FIFO. The resource consumption of this self-test can be found in *Appendix A.3*.

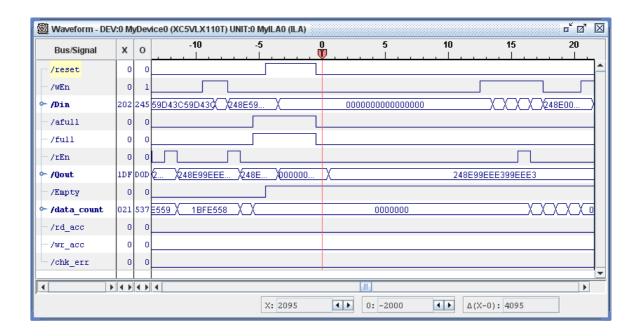

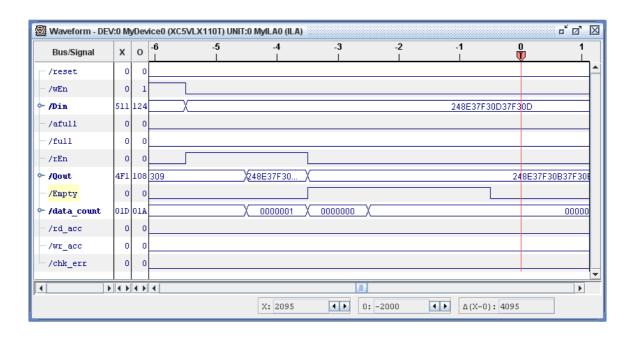

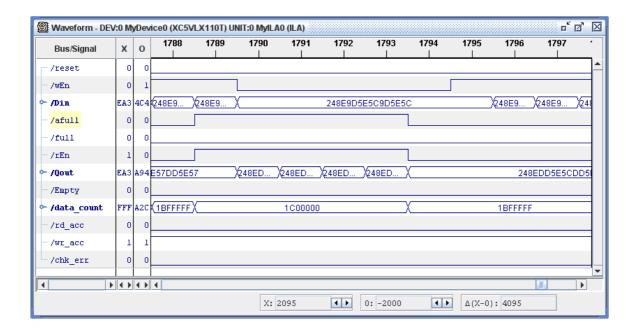

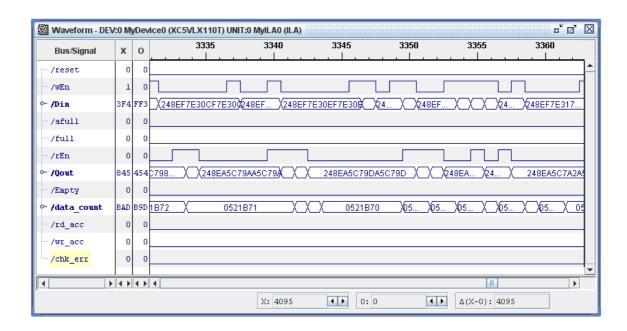

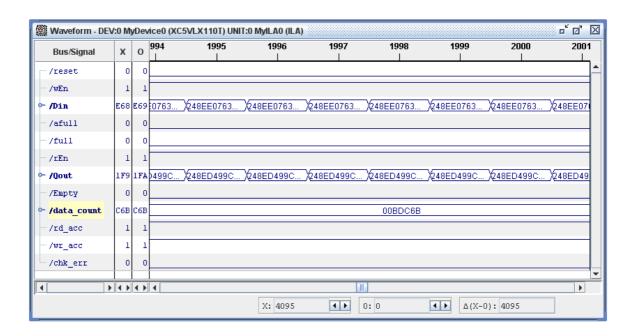

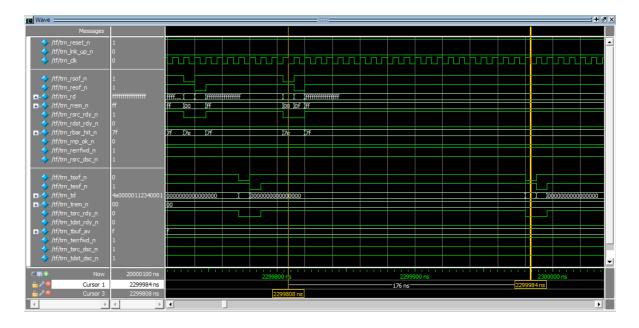

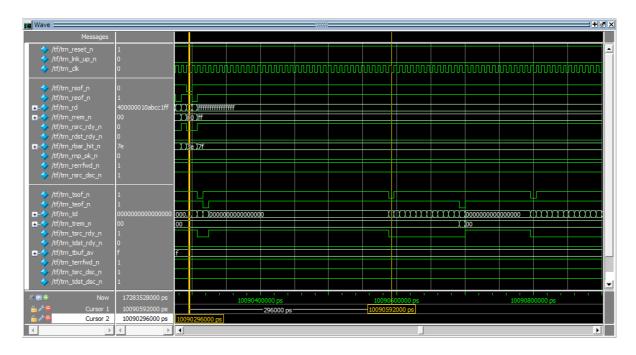

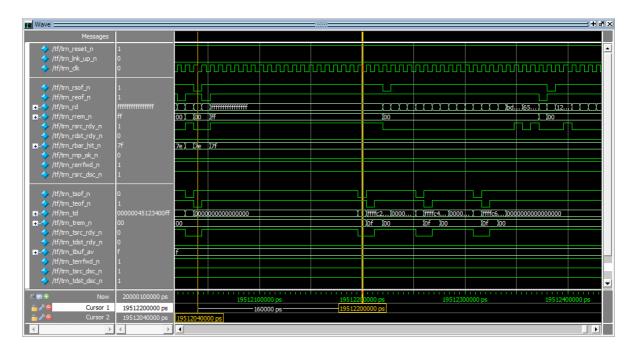

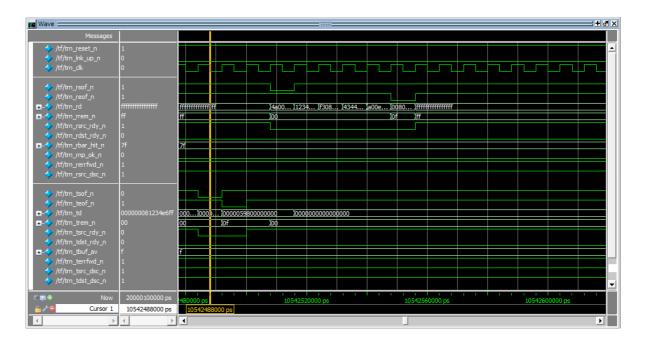

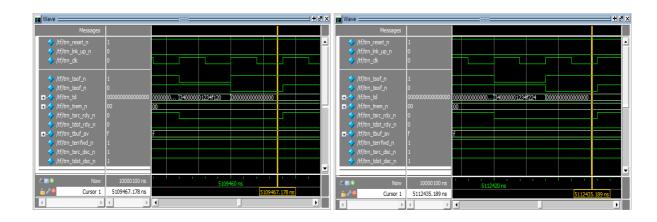

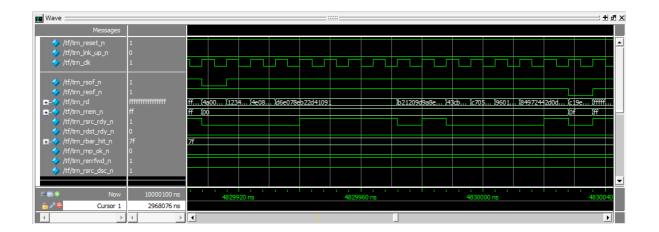

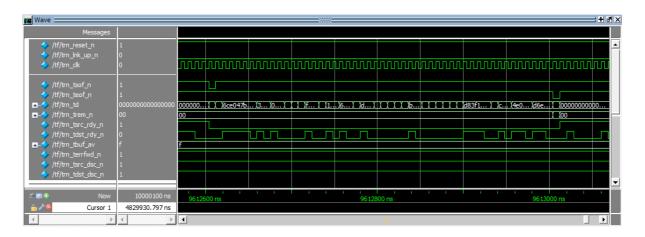

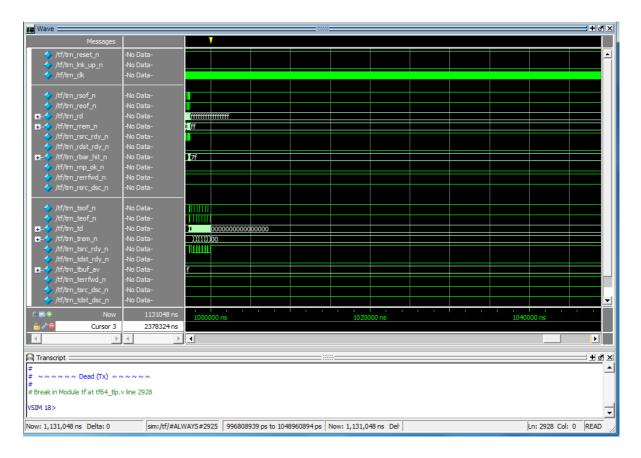

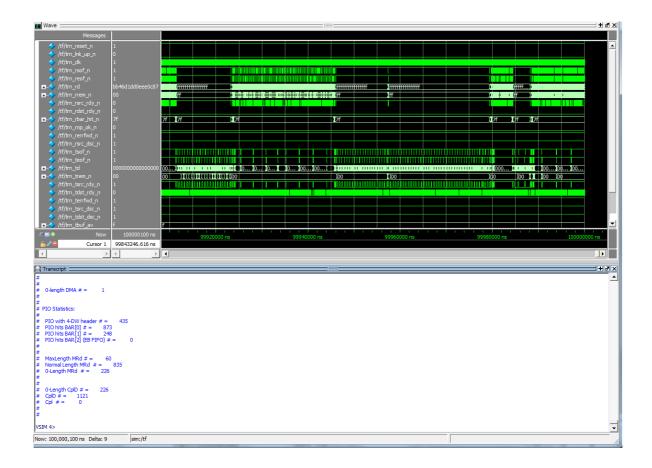

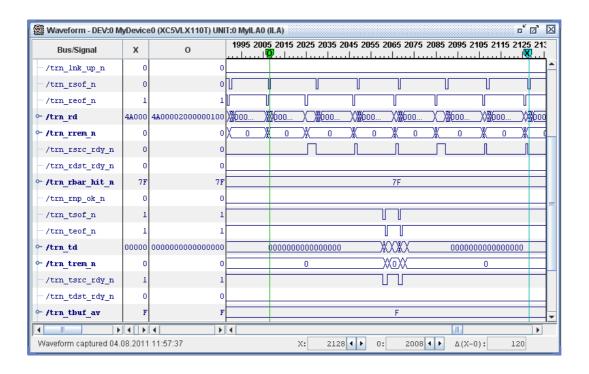

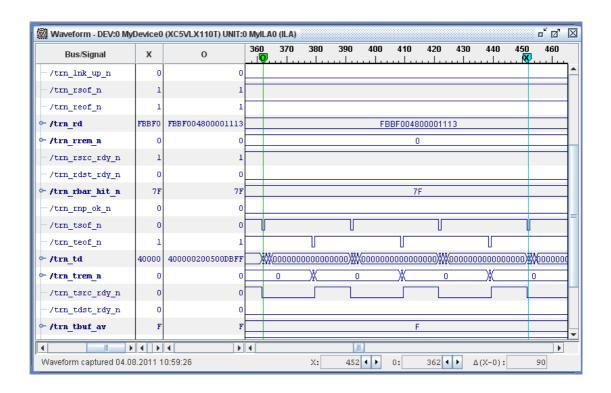

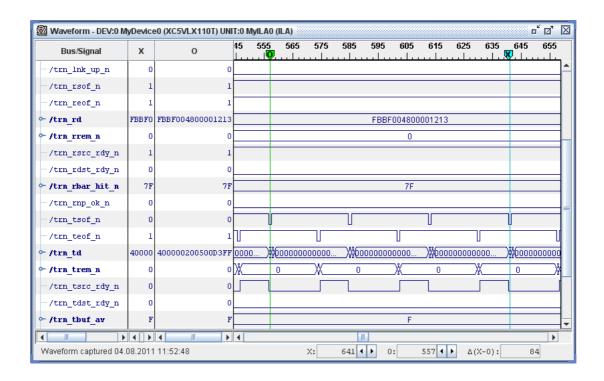

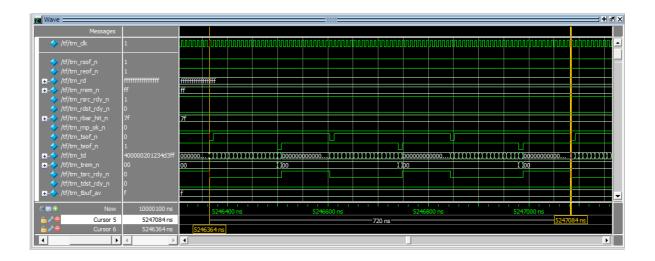

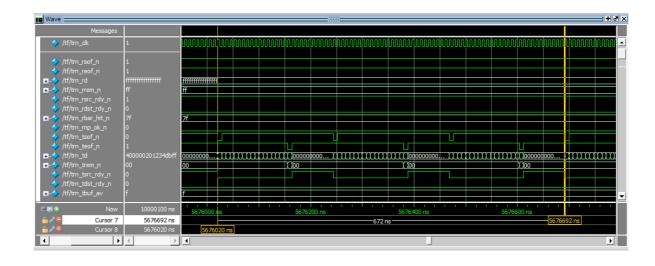

Timing diagrams of DDR FIFO from the ChipScope viewer prove that this FIFO behaves correctly as the standard FIFO, both in small occupancy and in large occupancy. These diagrams are shown with EMPTY, FULL, ALMOST\_FULL, as well as the generated data count signals. The experiments are made with the help of AW and AR buttons. The write and read control signals are generated with pseudo-random logic. The data integrity is proven by the deasserted chk\_err signal. From the reset timing diagram in figure 2-15 we can see this SDRAM FIFO has longer latency from write to empty low. The proxy BRAM FIFO is 1024 words altogether and hence, the SDRAM kernel is used if the data count is greater than 0x100, as in figure 2-16, figure 2-17 and figure 2-18.

Figure 2-15 Reset

Figure 2-16 Empty logic

Figure 2-17 Almost-full logic

Figure 2-18 Low rate flow

Figure 2-19 High rate flow

#### 2.2.4 Implementation in FPGA

Timing constraint can be met to over 175 MHz for Virtex4 FPGA with -10 speed grade for this design. The numbers of flip-flops and (4-input) look-up-tables are both under 1000 and the number of 18Kb RAM blocks is 4. For the adjusting of data bus of the SDRAM module, 20 IDELAYCTRLs are used.

We use two parallel 32MB, 16-bit DDR SDRAMs with CAS latency of 3 as the kernel memory. It is driven by a DDR clock of 175MHz. Our global clock for the FIFO wrapper runs at 150 MHz.

With a long and sustained test, mixed with manual accelerations, the FIFO behaves well in terms of performance and in stability. So, the peak bandwidth goes up to

150 MHz

$$\times$$

2  $\times$  32 bit = 9.6 Gbps

in the test system. However, in the DMA logic, the transaction layer clock rate is 125 MHz, where the performance is

$$125 \text{ MHz} \times 2 \times 32 \text{ bit} = 8.0 \text{ Gbps}$$

This performance estimation suffices the 4 Gbps requirement.

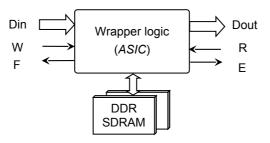

#### 2.2.5 Stand-alone IC scenario

The design in FPGA can be transported to build a stand-alone ASIC chip that transforms DDR SDRAM into a large-size FIFO, as figure 2-20 shows. The transformer logic consists of the (small-size) input and output FIFOs, MUX and the DDR buffer. The clock signals are omitted in figure 2-20.

Here we have

SDRAM modules + Wrapper ASIC => large-size FIFO.

Figure 2-20 Stand-alone IC

And the data buses can be varied in width, dependent upon the applied number of the DDR SDRAM chips. Of course the operation frequency is mainly limited by the timing of the DDR SDRAM chips. As we have seen, the resource is not a big problem, but the pin out.

The extra built-in FIFOs cost is proportional to the buffer bus width, if their depths are fixed to e.g. 512 words. So this part is the major resource consumer, but it is not proportional to the buffer depth.

The data counts can be implemented as in our project and they are proportional to the address width of the SDRAM modules, about the level of  $O(\log N)$ , where N is the volume of the entire buffer.

By the FPGA resource estimation from the stand-alone test implementation report (*Appendix A.3*), such an ASIC (64-bit data bus) can be achieved within 10 million gates.

Such structure might be useful to build up more powerful computing systems, which are in great need of buffer resource. For instance, the DAQ systems in high-energy physics often have to work a lot for triggering strategies in saving buffer resource, where SDRAM FIFO is supposed to be a nice solution to simplify the design complexity. It can also be combined into chipset (northbridge) in the commercial PC main-board to provide a specific channel of data flow. With more and more network video-audio applications today, such buffer architecture shall provide preferably higher performance and neater structure for network instruments.

#### 2.2.6 Notes to the transformed FIFO

Advantages of such FIFO include good scalability and economic. The cost is acceptable and the clock rate is satisfactory. More importantly, the depth is much larger, usually dozens of times larger, even hundreds of times larger than the marketable devices.

This approach can be easily expanded to DDR2 or DDR3 SDRAM and other sorts of memory chips, such as SRAM, or ZBT, even Flash memories.

On the opposite direction of integrating, we provide large-size FIFO solution in separate fashion. Stand-alone transforming ASIC chip is feasible and the functionality has been verified by FPGA implementation.

For data integrity reason, the FIFO bus width today is popular with multiple of 9, instead of 8. However in our example, constrained by the DDR SDRAM chip we take, the bus can only be 16, 32 or 64, or so on.

Later in this chapter we can see that the event buffer prefers additional bit parallel to the data bus. However, this FIFO is difficult to expand its bus width, because we use the SDRAM module without parity check. If framing or other marking signals are to be accompanied, work-around has to be found.

To have 9-multiplied bus width, 1-bit wide internal RAM module can be used parallel with the main SDRAM module and these 2 modules should have the same depth (address range) so that their address pins can be merged and treated as one address bus. However, this solution usually takes too much resource in the wrapper IC. For example, a 1GB FIFO with bus width 64 bits should be additionally attached with

$10^{30} / 8$  bits = 128 Mbits

memory. It is a big cost.

Therefore, a more plausible solution is to use available 9-folded SDRAM module as the FIFO kernel. COTS can be purchased like 2GB SODIMM MT18HTF25672PKZ-667 of Micron Co, which is x72 module. [57]