## DISSERTATION

$\quad submitted \\$

to the

Combined Faculties for the Natural Sciences and for Mathematics of the  $\,$

Ruperto-Carola University of Heidelberg, Germany for the degree of Doctor of Natural Sciences

Put forward by

Master of Science Jens-Thomas Krüger

Born in Hilden

Oral examination:

# Green Wave: A Semi-Custom Hardware Architecture for Reverse Time Migration

Advisor: Prof. Dr. Ulrich Brüning

## Abstract

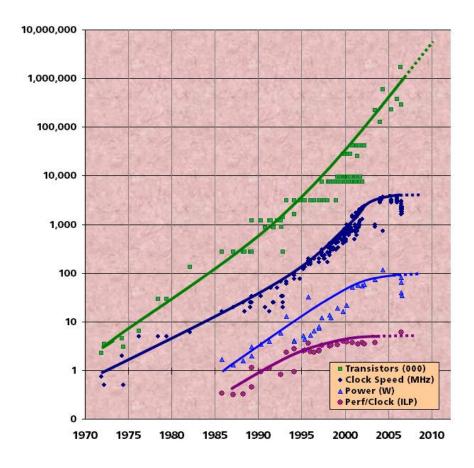

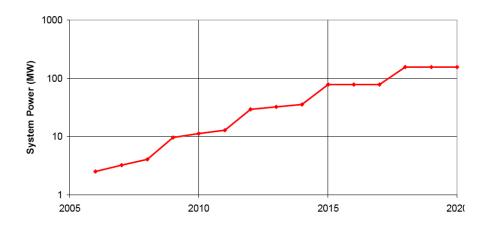

Over the course of the last few decades the scientific community greatly benefited from steady advances in compute performance. Until the early 2000's this performance improvement was achieved through rising clock rates. This enabled plug-n-play performance improvements for all codes. In 2005 the stagnation of CPU clock rates drove the computing hardware manufactures to attain future performance through explicit parallelism. Now the HPC community faces a new, even bigger challenge. So far performance gains were achieved through replication of general-purpose cores and nodes. Unfortunately, rising cluster sizes resulted in skyrocketing energy costs - a paradigm change in HPC architecture design is inevitable. In combination with the increasing costs of data movement, the HPC community started exploring alternatives like GPUs and large arrays of simple, low-power cores (e.g. BlueGene) to offer the better performance per Watt and greatest scalability.

As in general science, the seismic community faces large-scale, complex computational challenges that can only be limited solved with available compute capabilities. Such challenges include the physically correct modeling of subsurface rock layers. This thesis analyzes the requirements and performance of isotropic (ISO), vertical transverse isotropic (VTI) and tilted transverse isotropic (TTI) wave propagation kernels as they appear in the Reverse Time Migration (RTM) imaging method. It finds that even with leading-edge, commercial off-the-shelf hardware, large-scale survey sizes cannot be imaged within reasonable time and power constraints.

This thesis uses a novel architecture design method leveraging a hardware/software co-design approach, adopted from the mobile- and embedded market, for HPC. The methodology tailors an architecture design to a class of applications without loss of generality like in full custom designs. This approach was first applied in the Green Flash project, which proved that the co-design approach has the potential for high energy efficiency gains. This thesis presents the novel Green Wave architecture that is derived from the Green Flash project. Rather than focusing on climate codes, like Green Flash,

Green Wave chooses RTM wave propagation kernels as its target application. Thus, the goal of the application-driven, co-design Green Wave approach, is to enable full programmability while allowing greater computational efficiency than general-purpose processors or GPUs by offering custom extensions to the processor's ISA and correctly sizing software-managed memories and an efficient on-chip network interconnect. The lowest level building blocks of the Green Wave design are pre-verified IP components. This minimizes the amount of custom logic in the design, which in turn reduces verification costs and design uncertainty.

In this thesis three Green Wave architecture designs derived from ISO, VTI and TTI kernel analysis are introduced. Further, a programming model is proposed capable of hiding all communication latencies. With production-strength, cycle-accurate hardware simulators Green Wave's performance is benchmarked and its performance compared to leading on-market systems from Intel, AMD and NVidia. Based on a large-scale example survey, the results show that Green Wave has the potential of an energy efficiency improvement of  $5\times$  compared to x86 and  $1.4\times-4\times$  to GPU-based clusters for ISO, VTI and TTI kernels.

## Zusammenfassung

Im Laufe der vergangenen Jahrzehnte profitierte die Wissenschaft von stetigen Leistungssteigerungen im Hochleistungsrechnen. Bis Anfang des neuen Jahrtausends wurden diese insbesondere durch höhere Taktraten der Prozessoren erreicht. Durch einfaches Austauschen älterer Prozessoren durch eine neue Generation wurde bessere Leistung für alle Codes erreicht. Diese Entwicklung endete im Jahre 2005. Mit 4 Ghz waren Prozessoren an eine Grenze gestoßen, bei der Wärmeentwicklung und Stromverbrauch nicht weiter gesteigert werden konnten um höhere Taktraten zu ermöglichen. Um zukünftige Leistungssteigerungen zu ermöglichen, wurden Taktraten gesenkt und Leistung durch ausnutzen expliziten Parallelismus, innerhalb eines "Shared Multiprocessors", erreicht. Heute steht die High-Performance Computing Gemeinschaft vor einer neuen, noch größeren, Herausforderung. Um den stetig wachsenden Leistungshunger im wissenschaftlichen Rechnen zu befriedigen, wurden immer mehr Prozessoren in HPC Systemen verbaut. Genau wie Mitte des ersten Jahrzehnts die Leistungsaufnahme eines einzelnen Prozessors an seine Grenzen stieß, gilt dies auch für Großrechner von heute, bei denen die Leistungsaufnahme und damit die Kosten für Energie und Infrastruktur, über ökonomisch und ökologisch, vertretbare Grenzen hinausgehen. Ein radikaler Wandel in der HPC ist deshalb unausweichlich. Auf Grund dessen rücken alternative Ansätze, wie etwa GPUs und "Many-Core" Systeme, verstärkt in den Fokus von Wissenschaft und Industrie.

Insbesondere die Öl- und Gas-Industrie sieht sich enormen Herausforderungen gegenübergestellt um physikalisch korrekte Abbildungen des Untergrundes, für explorative Zwecke zu erstellen. Diese Arbeit analysiert drei wesentliche Wellenpropagationskernel wie sie für die Reverse Time Migration (RTM) verwendet werden: für isotrope, vertikal transversal isotrope und geneigt transversal isotrope Medien.

Die Analysen dieser Arbeit zeigen, dass auch auf Computersystemen neuester Generation solche Algorithmen, angewandt auf große Explorationsvolumen und kurze Rechenzeiten, von der Leistungsaufnahme für kein Rechenzentrum zu vertreten sind.

In dieser Arbeit wird ein neuartiger "Hardware/Software Co-Design" Ansatz für HPC Architektur benutzt um signifikante Verbesserungen gegenüber allen evaluierten, markterhältlichen Systemen zu erreichen und RTM selbst für große Gebiete ermöglicht. Es wird eine neue Prozessorarchitektur mit dem Namen "Green Wave" vorgestellt, welche auf eine Klasse von Algorithmen optimiert ist und sich somit, anders als bei voll angepassten Designkonzepten, nicht auf spezielle Kernel beschränkt. Green Wave basiert auf Tensilica's hoch-effizienten LX4 Prozessor, der das Hinzufügen von kernelspezifischen Instruktionen ermöglicht. Mit weiterem Anpassen des Chipdesigns durch "Local-Stores" und einem effizientem "Network-on-Chip" wird eine bestmögliche Energieeffizienz erreicht. Die weiteren Grundbausteine von Green Wave sind vor-verifizierte, markterhältliche Hardwarekomponenten, um Verifikations- und Produktionskosten möglichst gering zu halten. Anhand der vorgestellten Programmiermodellen für Green Wave, werden mit dem Tensilica "Instruction Set Simulator" (ISS) zyklengenaue Leistungsbenchmarks erstellt und werden mit den evaluierten Architekturen von Intel, AMD und NVidia, verglichen. Die Ergebnisse zeigen, dass Energieeffizienz-Verbesserungen von ca. 5x gegenüber x86 basierten Architekturen und 1.4x bis 4x gegenüber GPU basierten Systemen erreicht werden.

## Acknowledgements

I'd like to thank my advisor Professor Ulrich Bruening, head of the Computer Architecture Group of the University of Heidelberg. He accepted me as his PhD student and his always friendly support and experience made it possible for me to finish this thesis. I greatly benefited from his incredible experience in computer architecture. I will always remember his great advice and valuable lessons.

I'd like to thank Franz-Josef Pfreundt head of the Competence Center High Performance Computing (CC-HPC) department at the Fraunhofer ITWM. With his knowledge about the research taking place at Lawrence Berkeley National Laboratory (LBNL) in Berkeley, California he initiated the cooperation for this thesis. The support through the Fraunhofer scholarship gave me the security to complete my study.

I want to thank Erich Strohmaier, head of LBNL's Future Technology Group (FTG) and John Shalf, head of the Advanced Technologies Group (ATG). I highly benefited from their support and guidance. Especially, I need to thank John Shalf and the great Green Flash team who made me part of the exciting project back in 2009 at my first visit to the LBNL and their support for the Green Wave project later on. I know that John's time is very valuable and appreciate every minute he spent on discussions with me.

Special thanks go to Sam Williams and David Donofrio. I greatly benefited from Sam's incredible experience in software optimization and compute architectures. Only with David's help and expertise in hardware architecture I was able to apply the gained experience from the application analysis to the Green Wave design. He introduced me to the simulation tools and offered a lot of his valuable time for discussions and problem solving. This study couldn't be done without him.

My thank goes to all researches at the Fraunhofer ITWM who advised me in seismic questions. Special thanks go to Norman Ettrich, Daniel Gruenewald. Both spent quite some time with me discussing seismic processing and wave-equation kernels.

I would like to thank Paulius Micikevicius from NVIDIA for his benchmarking and participation. He enabled me to compare my own benchmark results to the fastest wave-propagation kernels on leading-edge GPU hardware.

I want to thank everyone I had the honor to sit in the same room with. I would like to mention Filip Blagojevic and Khaled Ibrahim. I will always remember the advice you gave me and the lively discussions we had.

Finally, I would like to thank all my friends and family who supported and believed in me even when I didn't believe in myself.

Thank you!

# Contents

| Li       | st of        | Figur  | es                                                              | vii |  |

|----------|--------------|--------|-----------------------------------------------------------------|-----|--|

| Li       | st of        | Table  | S                                                               | xi  |  |

| 1        | Introduction |        |                                                                 |     |  |

|          | 1.1          | Outlin | ne                                                              | 6   |  |

| <b>2</b> | The          | Basic  | s of Seismic Processing                                         | 9   |  |

|          | 2.1          | Funda  | mentals of Seismic Processing                                   | 10  |  |

|          |              | 2.1.1  | Seismic Processing Workflow                                     | 11  |  |

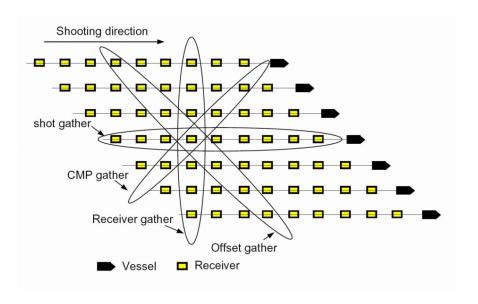

|          | 2.2          | Seismi | ic Depth Migration                                              | 16  |  |

|          |              | 2.2.1  | The Wave Equation                                               | 18  |  |

|          |              | 2.2.2  | The Isotropic Wave Equation (ISO)                               | 20  |  |

|          |              | 2.2.3  | Vertical Transverse Isotropy (VTI)                              | 21  |  |

|          |              | 2.2.4  | Tilted Transverse Isotropy (TTI)                                | 22  |  |

|          | 2.3          | Appro  | eximation of the Acoustic 2-way Wave Equation                   | 23  |  |

|          |              | 2.3.1  | Integral Methods                                                | 24  |  |

|          |              | 2.3.2  | An example Partial Differential Equation (PDE): The Finite Dif- |     |  |

|          |              |        | ference Method (FDM) $\dots$                                    | 25  |  |

|          |              | 2.3.3  | Implicit Solutions for the Finite Difference Method             | 26  |  |

|          |              | 2.3.4  | Explicit Solutions for FDM                                      | 29  |  |

|          |              | 2.3.5  | The Approximation Order                                         | 30  |  |

|          |              | 2.3.6  | Computational Requirements of Explicit Finite-Difference Kernel | 30  |  |

|          | 2.4          | The R  | Leverse-Time Migration (RTM) Imaging Method                     | 32  |  |

|          |              | 2.4.1  | Mathematical Background                                         | 32  |  |

|          |              | 242    | RTM Schemes                                                     | 35  |  |

|   | 2.5               | Seism                                                                                       | ic Survey                                                                                                                                                                                                                                      | 39                                                       |

|---|-------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   | 2.6               | Summ                                                                                        | nary                                                                                                                                                                                                                                           | 40                                                       |

| 3 | Con               | $\mathbf{npute}$                                                                            | Architectures: State-of-the-Art                                                                                                                                                                                                                | 41                                                       |

|   | 3.1               | Comp                                                                                        | uter Architecture: An Overview                                                                                                                                                                                                                 | 41                                                       |

|   | 3.2               | Evalua                                                                                      | ated Node Architectures                                                                                                                                                                                                                        | 42                                                       |

|   |                   | 3.2.1                                                                                       | Intel Nehalem X5550 (Nehalem)                                                                                                                                                                                                                  | 44                                                       |

|   |                   | 3.2.2                                                                                       | AMD Opteron 6172 (Magny Cours)                                                                                                                                                                                                                 | 45                                                       |

|   |                   | 3.2.3                                                                                       | Intel Xeon E5-2687W (Sandy Bridge)                                                                                                                                                                                                             | 46                                                       |

|   |                   | 3.2.4                                                                                       | NVIDIA Tesla M2090 (Fermi)                                                                                                                                                                                                                     | 46                                                       |

|   | 3.3               | Relate                                                                                      | ed Architectures                                                                                                                                                                                                                               | 49                                                       |

|   |                   | 3.3.1                                                                                       | Intel Many Integrated Core Architecture (MIC)                                                                                                                                                                                                  | 49                                                       |

|   |                   | 3.3.2                                                                                       | Field Programmable Gate Array (FPGA)                                                                                                                                                                                                           | 50                                                       |

|   |                   | 3.3.3                                                                                       | IBM Cell Broadband Engine Architecture (CBEA)                                                                                                                                                                                                  | 51                                                       |

|   | 3.4               | Summ                                                                                        | nary                                                                                                                                                                                                                                           | 52                                                       |

| 4 | Eva               | luated                                                                                      | Architectures Performance and Efficiency Analysis                                                                                                                                                                                              | 53                                                       |

|   | 4.1               | Refere                                                                                      | ence Kernel Benchmark                                                                                                                                                                                                                          | 53                                                       |

|   |                   |                                                                                             |                                                                                                                                                                                                                                                |                                                          |

|   |                   | 4.1.1                                                                                       | Single-Node Benchmark Setup                                                                                                                                                                                                                    | 54                                                       |

|   | 4.2               |                                                                                             | Single-Node Benchmark Setup                                                                                                                                                                                                                    | 54<br>56                                                 |

|   | 4.2               |                                                                                             |                                                                                                                                                                                                                                                |                                                          |

|   | 4.2               | Perfor                                                                                      | mance Estimations                                                                                                                                                                                                                              | 56                                                       |

|   | 4.2               | Perfor                                                                                      | Arithmetic Intensity                                                                                                                                                                                                                           | 56<br>57                                                 |

|   | 4.2               | Perfor 4.2.1 4.2.2                                                                          | Arithmetic Intensity                                                                                                                                                                                                                           | 56<br>57<br>59                                           |

|   | 4.2               | Perfor<br>4.2.1<br>4.2.2<br>4.2.3                                                           | Arithmetic Intensity                                                                                                                                                                                                                           | 56<br>57<br>59<br>60                                     |

|   |                   | Perfor<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                         | Arithmetic Intensity                                                                                                                                                                                                                           | 56<br>57<br>59<br>60<br>61                               |

|   |                   | Perfor<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5                                         | Memory Bandwidth Ceiling                                                                                                                                                                                                                       | 56<br>57<br>59<br>60<br>61<br>63                         |

|   |                   | Perfor<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Refere                               | Arithmetic Intensity                                                                                                                                                                                                                           | 56<br>57<br>59<br>60<br>61<br>63<br>64                   |

|   |                   | Perfor<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Refere<br>4.3.1<br>4.3.2             | Arithmetic Intensity  Memory Bandwidth Ceiling  Floating-Point Throughput Ceiling  The Roofline Model  Summary  ence Kernel Benchmark Results  Domain Decomposition                                                                            | 56<br>57<br>59<br>60<br>61<br>63<br>64<br>64             |

| 5 | 4.3               | Perfor<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Refere<br>4.3.1<br>4.3.2<br>Conclude | Arithmetic Intensity  Memory Bandwidth Ceiling  Floating-Point Throughput Ceiling  The Roofline Model  Summary  ence Kernel Benchmark Results  Domain Decomposition  Benchmark Results                                                         | 56<br>57<br>59<br>60<br>61<br>63<br>64<br>64<br>65       |

| 5 | 4.3               | Perfor<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Refere<br>4.3.1<br>4.3.2<br>Concl-   | Arithmetic Intensity  Memory Bandwidth Ceiling  Floating-Point Throughput Ceiling  The Roofline Model  Summary  ence Kernel Benchmark Results  Domain Decomposition  Benchmark Results  usions                                                 | 56<br>57<br>59<br>60<br>61<br>63<br>64<br>64<br>65<br>66 |

| 5 | 4.3<br>4.4<br>Lim | Perfor<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>Refere<br>4.3.1<br>4.3.2<br>Concl-   | Arithmetic Intensity  Memory Bandwidth Ceiling  Floating-Point Throughput Ceiling  The Roofline Model  Summary  ence Kernel Benchmark Results  Domain Decomposition  Benchmark Results  usions  Performance and Efficiency using COTS Hardware | 56<br>57<br>59<br>60<br>61<br>63<br>64<br>65<br>66       |

|   |      | 5.1.3   | Cache Blocking                                                             | 71 |

|---|------|---------|----------------------------------------------------------------------------|----|

|   |      | 5.1.4   | Cache Bypass                                                               | 73 |

|   |      | 5.1.5   | Translation Lookaside Buffer (TLB) Optimization                            | 74 |

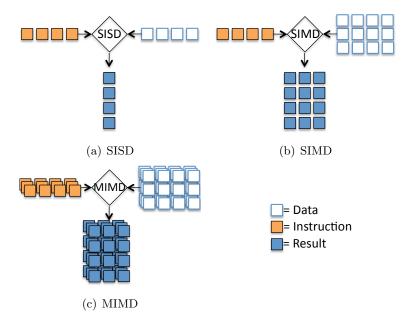

|   |      | 5.1.6   | Single Instruction Multiple Data (SIMD)                                    | 74 |

|   | 5.2  | Instru  | ction-Level Parallelism                                                    | 77 |

|   |      | 5.2.1   | Loop Unrolling                                                             | 77 |

|   | 5.3  | Thread  | d-Level Parallelism                                                        | 78 |

|   |      | 5.3.1   | Task Parallelism                                                           | 79 |

|   |      | 5.3.2   | Domain Decomposition                                                       | 80 |

|   | 5.4  | Kernel  | Specific Optimizations                                                     | 82 |

|   |      | 5.4.1   | Pre-Computation for TTI                                                    | 82 |

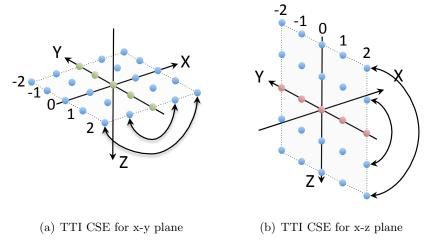

|   |      | 5.4.2   | Common Subexpression Elimination (CSE)                                     | 82 |

|   | 5.5  | GPU (   | Optimizations                                                              | 85 |

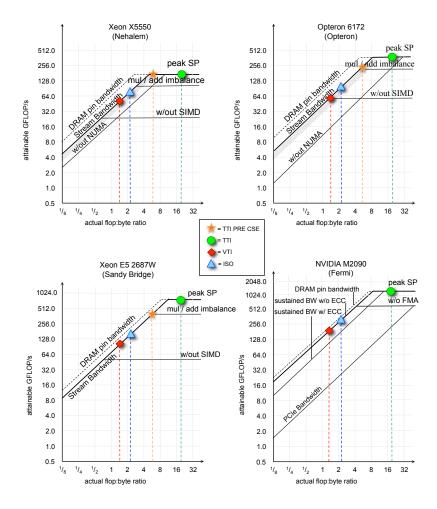

|   | 5.6  | Optim   | ization Summary and Extended Roofline Model                                | 87 |

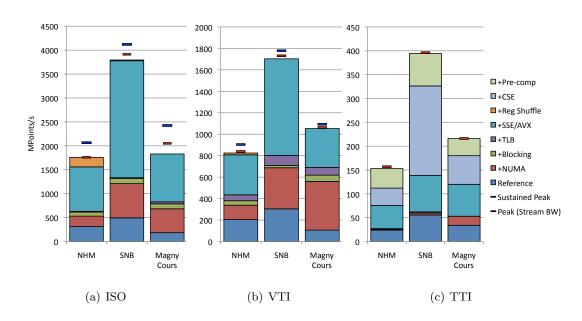

|   | 5.7  | Bench   | mark Analysis of Optimized Kernels                                         | 89 |

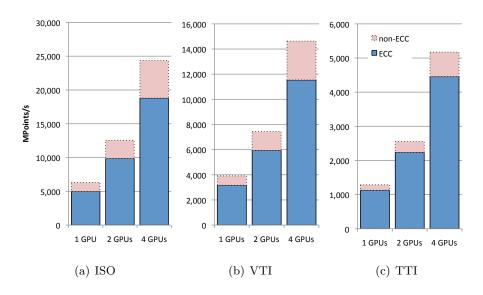

|   |      | 5.7.1   | GPU Performance                                                            | 91 |

|   |      | 5.7.2   | Single-Node Energy Efficiency                                              | 92 |

|   | 5.8  | Single- | -Node Summary and Conclusion                                               | 94 |

|   | 5.9  | Multi-  | Node Benchmark                                                             | 96 |

|   |      | 5.9.1   | Node-Level Parallelism                                                     | 96 |

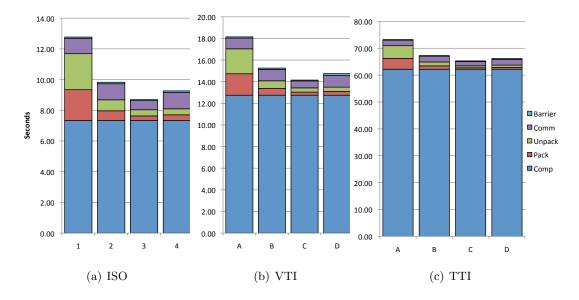

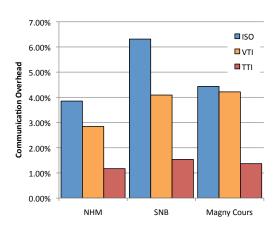

|   |      | 5.9.2   | Multi-Node Communication Overhead Analysis                                 | 98 |

|   |      | 5.9.3   | Multi-Node Programming Model for GPUs                                      | 01 |

|   |      | 5.9.4   | Node Volume Optimization                                                   | 02 |

|   | 5.10 | Estima  | ated Cluster Power Consumption                                             | 04 |

|   | 5.11 | Conclu  | asion                                                                      | 05 |

| 6 | Har  | dware   | , Software Co-Design Methodology                                           | 07 |

|   | 6.1  | The E   | nergy-Efficiency Challenge                                                 | 08 |

|   | 6.2  | The G   | reen Flash Project                                                         | 09 |

|   | 6.3  | Tensili | ica X<br>tensa Processor Generator Toolchain (XPG) $\ \ldots \ \ldots \ 1$ | 11 |

|   |      | 6.3.1   | Tensilica Instruction Extension (TIE)                                      | 12 |

|   |      | 6.3.2   | The Green Flash Architecture                                               | 15 |

|   |      | 6.3.3   | Green Flash Chip Power Modeling                                            | 16 |

|   |     | 6.3.4  | Green Flash Chip Area Modeling                                        | 117        |

|---|-----|--------|-----------------------------------------------------------------------|------------|

|   |     | 6.3.5  | Green Flash Chip Performance Modeling $\ \ldots \ \ldots \ \ldots$    | 117        |

|   | 6.4 | Co-De  | sign for Exascale (CoDEx)                                             | 118        |

|   |     | 6.4.1  | Research Accelerator for Multiple Processors (RAMP)                   | 119        |

|   | 6.5 | Summa  | ary                                                                   | 120        |

| 7 | The | Green  | Wave Programming Model and Requirement Analysis                       | <b>123</b> |

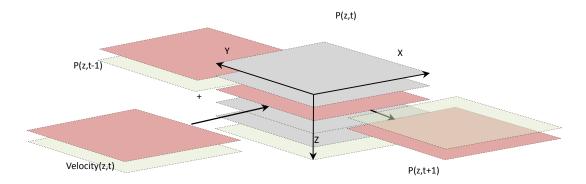

|   | 7.1 | The P  | lane Scheme Programming Model                                         | 123        |

|   | 7.2 | Estima | ation of the Number of Processing Units                               | 125        |

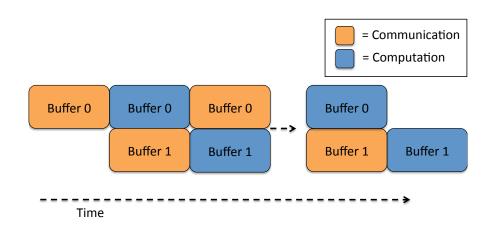

|   |     | 7.2.1  | Multi-buffering via Direct Memory Access (DMA) $\ \ldots \ \ldots$    | 127        |

|   | 7.3 | Estima | ation of Local Memory Size                                            | 129        |

|   | 7.4 | Estima | ation of Main Memory Size                                             | 131        |

|   | 7.5 | Estima | ation of Main Memory Bandwidth Requirements                           | 132        |

|   | 7.6 | Estima | ation of NoC Requirements                                             | 134        |

|   | 7.7 | Summa  | ary                                                                   | 136        |

| 8 | The | Green  | Wave Architecture and Single-Node Study                               | 137        |

|   | 8.1 | The G  | reen Wave Node                                                        | 137        |

|   |     | 8.1.1  | Local-Store Size and Core Count $\ \ldots \ \ldots \ \ldots \ \ldots$ | 138        |

|   |     | 8.1.2  | Local Store Access Latency                                            | 139        |

|   |     | 8.1.3  | Core Design Optimizations                                             | 140        |

|   |     | 8.1.4  | Fused Multiply-Add Support                                            | 145        |

|   |     | 8.1.5  | Instruction Profiling                                                 | 146        |

|   |     | 8.1.6  | Main Memory                                                           | 146        |

|   |     | 8.1.7  | Network-on-Chip (NoC)                                                 | 147        |

|   |     | 8.1.8  | Power Consumption Modeling                                            | 149        |

|   |     | 8.1.9  | Chip Size Estimation                                                  | 151        |

|   |     | 8.1.10 | Green Wave Architecture Summary                                       | 152        |

|   | 8.2 | A Sing | ele-Node Study                                                        | 154        |

|   |     | 8.2.1  | The Green Wave Roofline Model $\hdots$                                | 154        |

|   |     | 8.2.2  | Instruction Performance Limitations                                   | 155        |

|   |     | 8.2.3  | Memory Bandwidth Performance Limitations                              | 157        |

|   |     | 8.2.4  | Energy Efficiency Comparison based on Performance Estimations         | 158        |

|   |     | 8 2 5  | Summary and Conclusion                                                | 158        |

|              |            | 8.2.6   | A Single-Node Benchmark                 | 160 |

|--------------|------------|---------|-----------------------------------------|-----|

|              |            | 8.2.7   | Benchmark Analysis                      | 162 |

|              |            | 8.2.8   | Single-Node Study: Conclusion           | 164 |

| 9            | <b>A</b> ( | Green V | Wave Multi-Node Study                   | 167 |

|              | 9.1        | Green   | Wave Node Volume Analysis               | 168 |

|              | 9.2        | Green   | Wave Inter-Node Communication           | 169 |

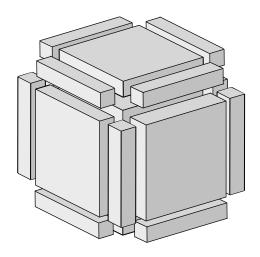

|              | 9.3        | Green   | Wave Cluster Topology                   | 171 |

|              | 9.4        | Green   | Wave Multi-Node Performance Estimations | 172 |

|              | 9.5        | Green   | Wave Multi-Node Optimizations           | 174 |

|              | 9.6        | Multi-  | Node Estimation Summary & Conclusion    | 174 |

|              | 9.7        | The G   | Freen Wave Cluster Architecture         | 174 |

|              |            | 9.7.1   | Mass Storage Requirement Estimation     | 175 |

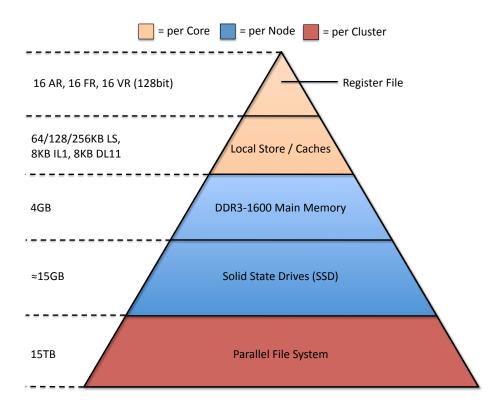

|              |            | 9.7.2   | The Green Wave Cluster Memory Hierarchy | 179 |

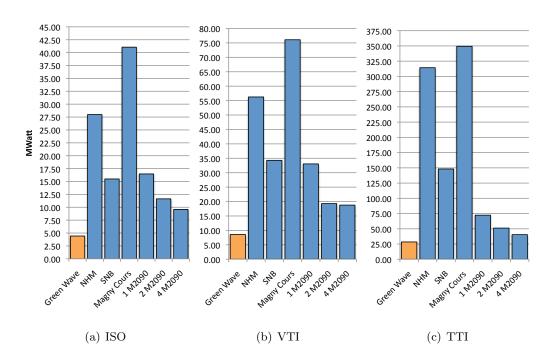

|              |            | 9.7.3   | Cluster Power Consumption Comparison    | 180 |

|              | 9.8        | Green   | Wave Design Comparison                  | 181 |

|              | 9.9        | Summ    | ary & Conclusion                        | 182 |

| 10           | Cor        | clusio  | n & Future Work                         | 185 |

| Re           | efere      | nces    |                                         | 191 |

| $\mathbf{G}$ | lossa      | ry      |                                         | 201 |

# List of Figures

| 1.1  | Development of Transistor Count                                                           | 2  |

|------|-------------------------------------------------------------------------------------------|----|

| 1.2  | Power Consumption of HPC Systems                                                          | 3  |

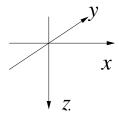

| 2.1  | The Seismic Coordinate System                                                             | 10 |

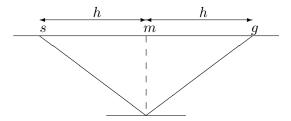

| 2.2  | The Source-Receiver Coordinates Scheme                                                    | 13 |

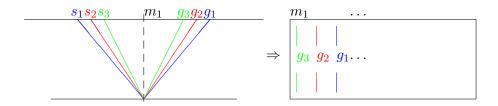

| 2.3  | Common-Midpoint-Gather sorting                                                            | 14 |

| 2.4  | Trace to Common-Shot-Gather sorting                                                       | 14 |

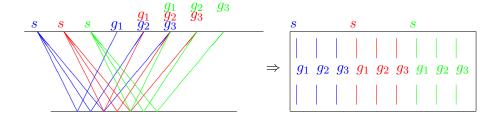

| 2.5  | Data Gathering Methods                                                                    | 15 |

| 2.6  | The Smooth Velocity Field of the Synthetic Marmousi Data Set                              | 16 |

| 2.7  | An Subset of Methods for Seismic Depth Migration                                          | 17 |

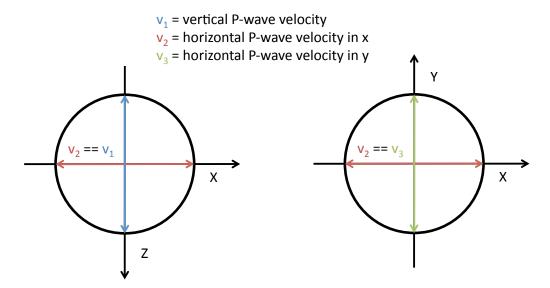

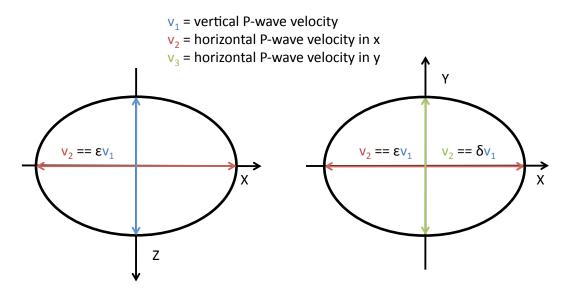

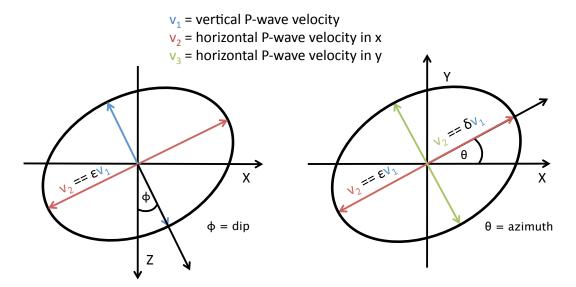

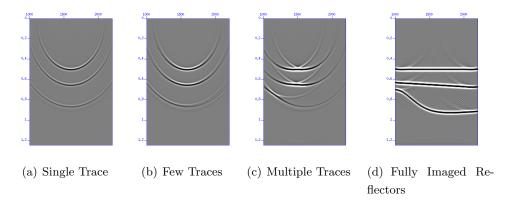

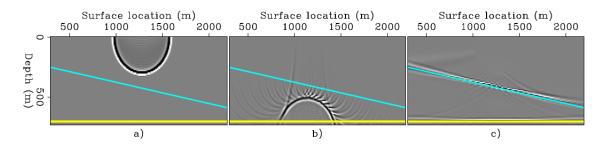

| 2.8  | Isotropic Wave Propagation                                                                | 21 |

| 2.9  | Vertical Transverse Isotropic Wave Propagation                                            | 22 |

| 2.10 | Tilted Transverse Isotropic Wave Propagation                                              | 23 |

| 2.11 | Ray-Tracing based Imaging                                                                 | 25 |

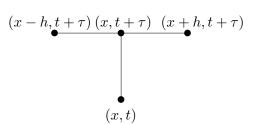

| 2.12 | Stencil of the implicit first-order Finite-Difference Scheme $\ \ldots \ \ldots \ \ldots$ | 27 |

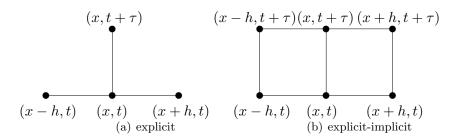

| 2.13 | Stencil of an explicit (a) and a mixed explicit-implicit (b), first-order in              |    |

|      | time finite-difference scheme                                                             | 29 |

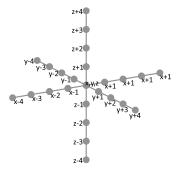

| 2.14 | ISO, VTI $2^{nd}$ Order in Time, $8^{th}$ Order in Space Stencil                          | 30 |

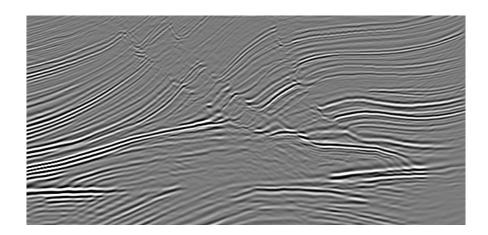

| 2.15 | Marmousi Migration Result                                                                 | 33 |

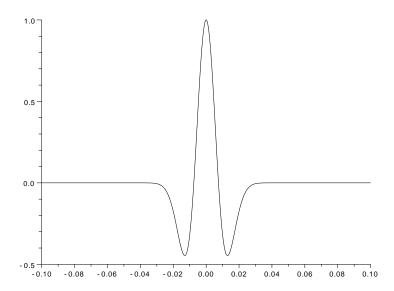

| 2.16 | The Ricker Wavelet                                                                        | 34 |

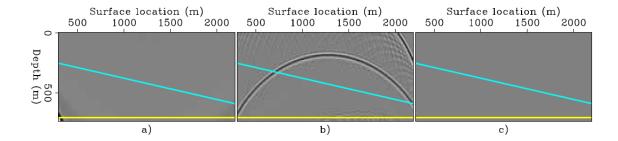

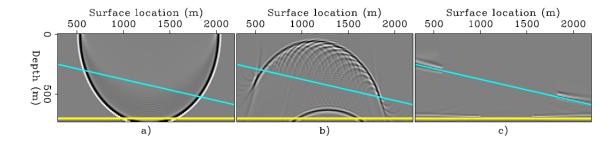

| 2.17 | RTM Example                                                                               | 36 |

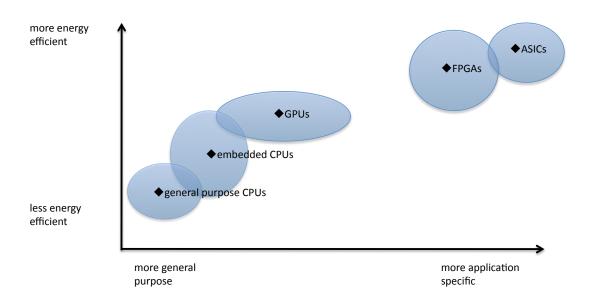

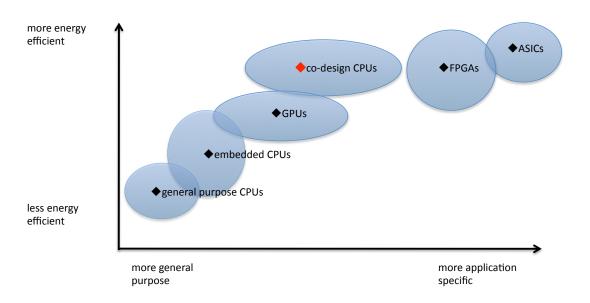

| 3.1  | Energy Efficiency and Specificity of COTS Hardware                                        | 43 |

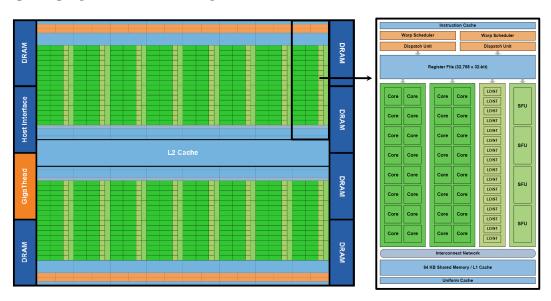

| 3.2  | The NVIDIA Fermi GPU                                                                      | 48 |

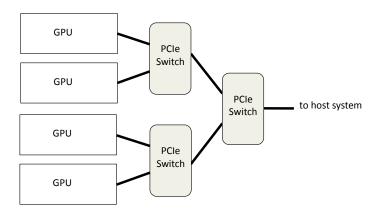

| 3.3  | Multi-GPU Node Configuration                                                              | 49 |

## LIST OF FIGURES

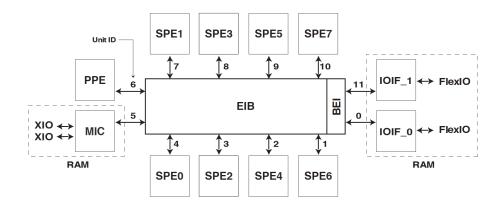

| 3.4  | The Cell Broadband Engine Architecture (CBEA) 52                          |

|------|---------------------------------------------------------------------------|

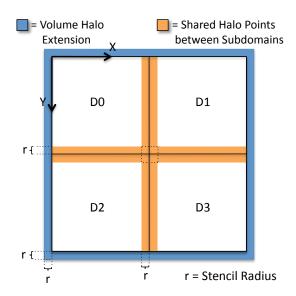

| 4.1  | Domain Decomposition with Halo Region                                     |

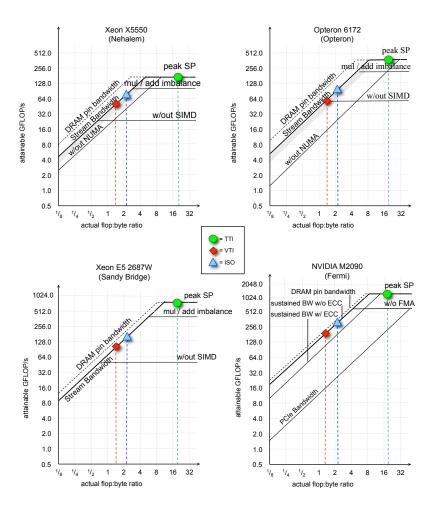

| 4.2  | The Roofline Model                                                        |

| 4.3  | The Domain Decomposition on Carver and Hopper                             |

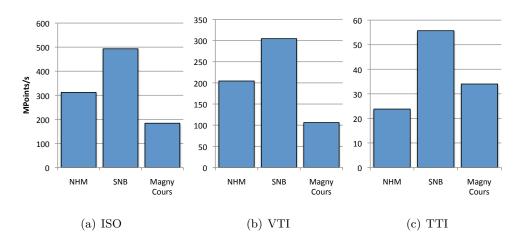

| 4.4  | Reference Single Node Throughput Comparison                               |

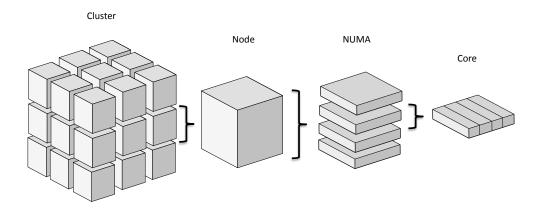

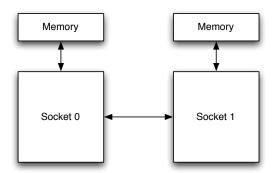

| 5.1  | NUMA                                                                      |

| 5.2  | Cache Blocking Example                                                    |

| 5.3  | Vectorization Approaches                                                  |

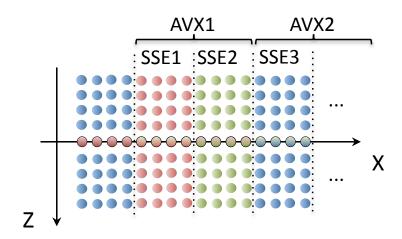

| 5.4  | A 2D Visualization of SSE and AVX Vectorization                           |

| 5.5  | Loop Unrolling and Reordering                                             |

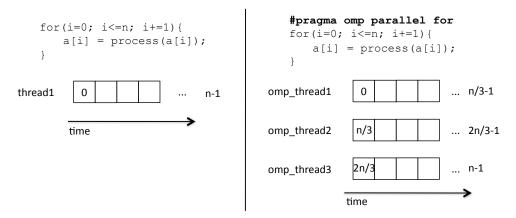

| 5.6  | OpenMP Example                                                            |

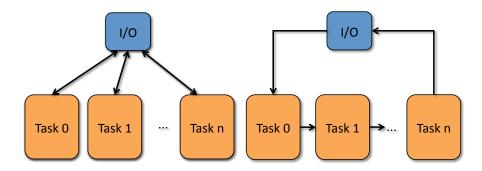

| 5.7  | Task Parallelization                                                      |

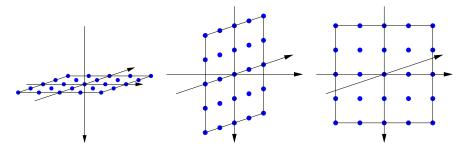

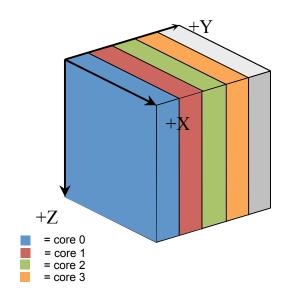

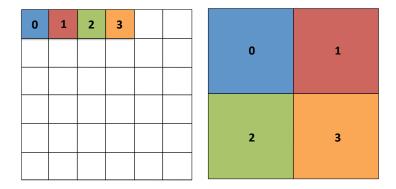

| 5.8  | Data Decomposition Examples                                               |

| 5.9  | Common Subexpression Elimination for TTI                                  |

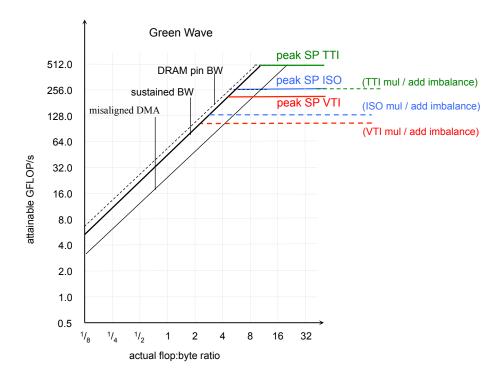

| 5.10 | Extended Roofline Model                                                   |

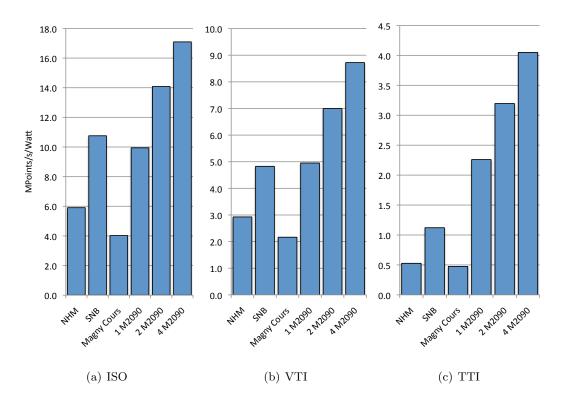

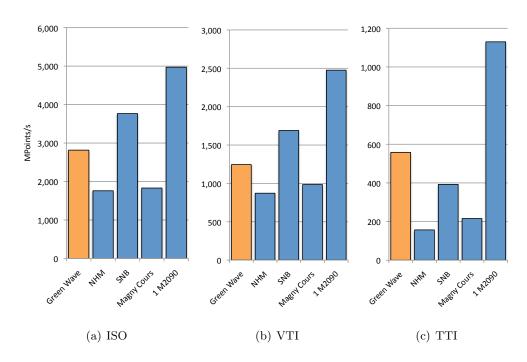

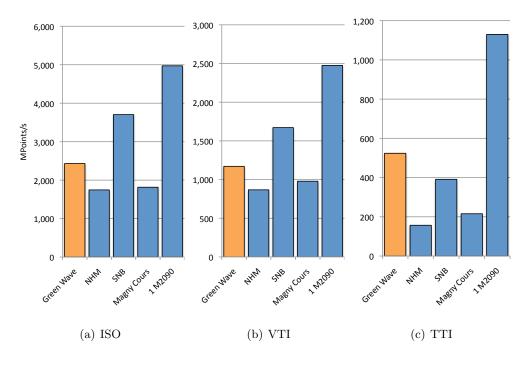

| 5.11 | RTM kernel performance                                                    |

| 5.12 | GPU performance                                                           |

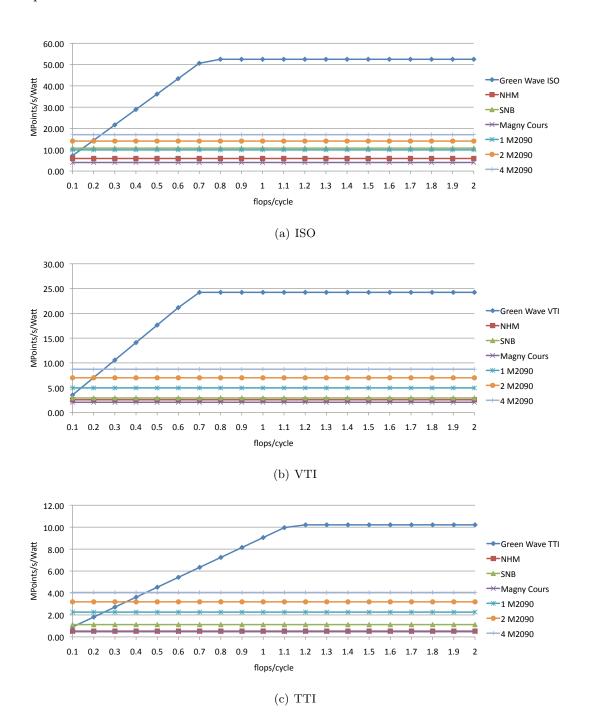

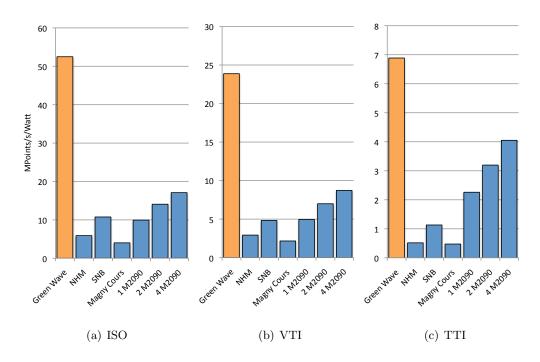

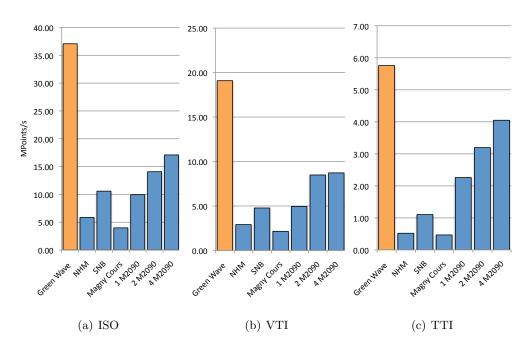

| 5.13 | Energy Efficiency for optimized Kernels                                   |

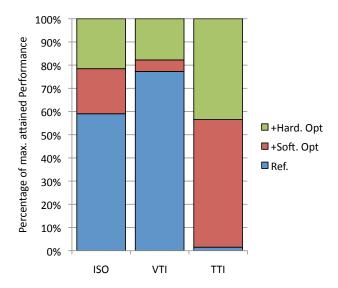

| 5.14 | Optimization Levels                                                       |

| 5.15 | Multi-Node Domain Decomposition                                           |

| 5.16 | Time Breakdown of the MPI Implementation on Hopper 99                     |

| 5.17 | Communication Overhead                                                    |

| 5.18 | Cluster Power Consumption Estimation                                      |

| 6.1  | The Tensilica Workflow                                                    |

| 6.2  | The Green Flash on-chip Network with Cores                                |

| 6.3  | The Berkeley Emulation Engine 3                                           |

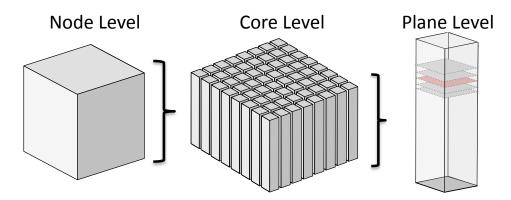

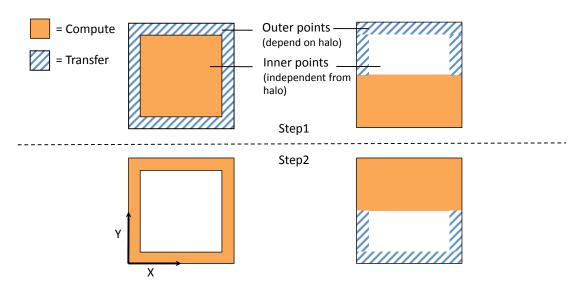

| 7.1  | Domain Decomposition for Green Wave                                       |

| 7.2  | Double Buffering                                                          |

| 7.3  | Streaming Planes including Multi-buffering and all ISO Planes $\dots$ 128 |

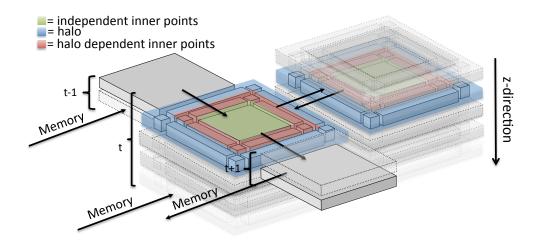

| 7.4  | Node Subdomain with TTI Halos                                             |

| 7.5  | Inter-Core Communication Schemes 13                                       |

## LIST OF FIGURES

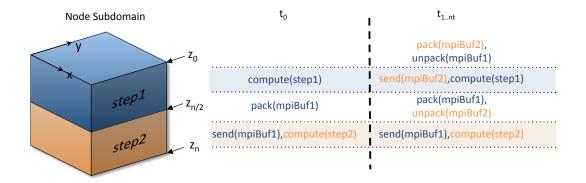

| 7.6  | Illustration of the plane scheme, including double buffering and halo      |

|------|----------------------------------------------------------------------------|

|      | exchange                                                                   |

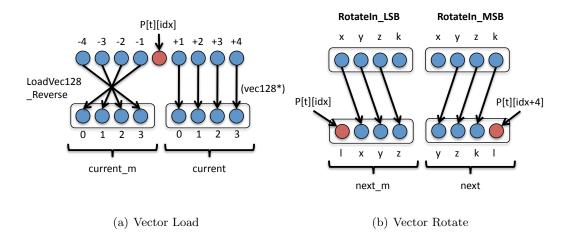

| 8.1  | Vector Register load and rotate Instructions                               |

| 8.2  | TTI Instruction Profile                                                    |

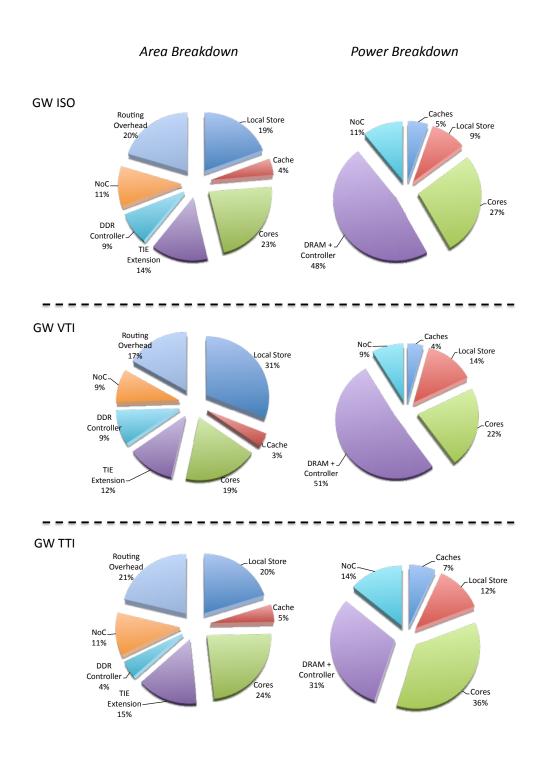

| 8.3  | Green Wave Die Area and Power Breakdown                                    |

| 8.4  | The Green Wave Roofline Model                                              |

| 8.5  | Green Wave energy efficiency in relation to achieved flops per cycle $159$ |

| 8.6  | Effects of Green Wave Software and Hardware Optimization 161               |

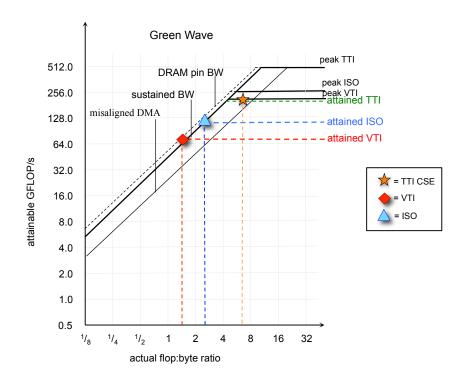

| 8.7  | The Green Wave Roofline Model including kernels                            |

| 8.8  | Green Wave Throughput in MPoints/s                                         |

| 8.9  | Green Wave Energy Efficiency in MPoints/s/Watt                             |

| 9.1  | Volume including Halos                                                     |

| 9.2  | Green Wave Inter-Node Communication Scheme                                 |

| 9.3  | Green Wave Multi-Node Performance Benchmark                                |

| 9.4  | Green Wave Multi-Node Energy Efficiency Benchmark                          |

| 9.5  | The Green Wave Memory Hierarchy                                            |

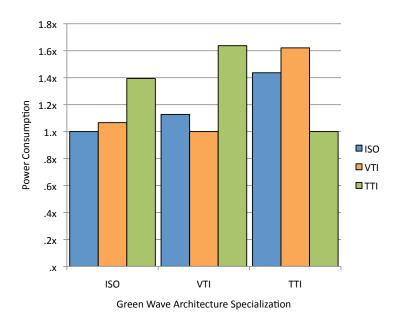

| 9.6  | Power Requirements of Cluster Setups for a fixed Time-to-Solution of       |

|      | one Week                                                                   |

| 9.7  | Green Wave Architecture Design Comparison                                  |

| 10.1 | Green Wave energy Efficiency and Specificity                               |

## LIST OF FIGURES

## List of Tables

| 3.1 | Details of the evaluated architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 44          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 4.1 | Kernel Memory Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58          |

| 4.2 | Characteristics of ISO, VTI and TTI Wave Equation Implementations $% \left( 1\right) =\left( 1\right) +\left( 1\right) +$ | 58          |

| 4.3 | Peak Performance in MPoints/s based on Memory Bandwidth as only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

|     | Limitation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60          |

| 4.4 | Estimated Performance in MPoints/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64          |

| 5.1 | Kernel Memory Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 83          |

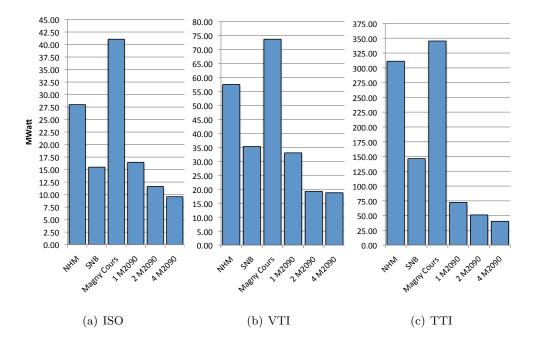

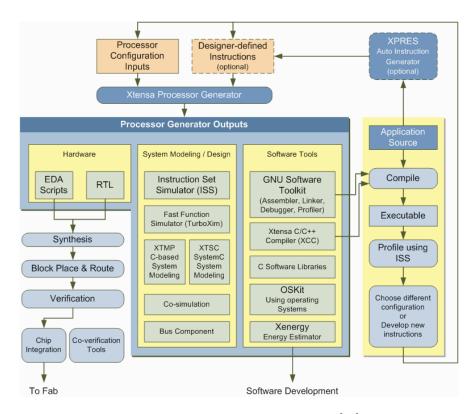

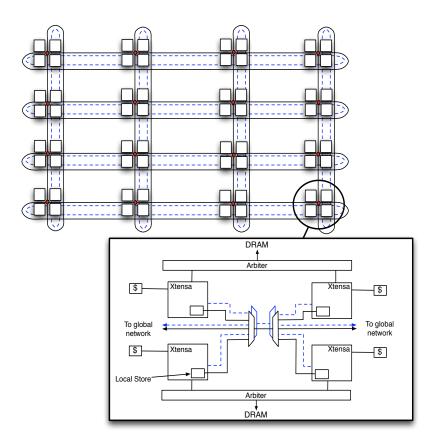

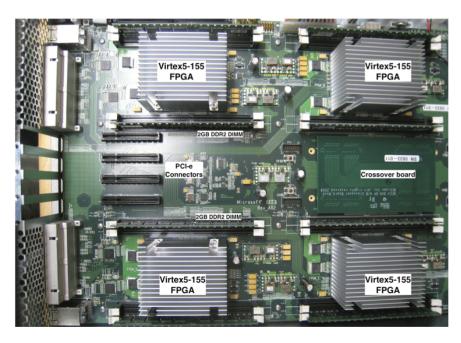

| 5.2 | Unit translation from Gflops/s to MPoints/s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 89          |