# DISSERTATION

submitted to the

Combined Faculty of Natural Sciences and Mathematics

of the

Ruprecht–Karls University Heidelberg

for the degree of

Doctor of Natural Sciences

put forward by

M.Sc. Felix Zahn

born in Mannheim, Baden-Württemberg

Heidelberg, 2020

# Energy-Efficient Interconnection Networks for High-Performance Computing

Advisor: Professor Dr. Holger Fröning

Date of oral exam: .....

# Abstract

In recent years, energy has become one of the most important factors for designing and operating large scale computing systems. This is particularly true in high-performance computing, where systems often consist of thousands of nodes. Especially after the end of Dennard's scaling, the demand for energyproportionality in components, where energy is depending linearly on utilization, increases continuously. As the main contributor to the overall power consumption, processors have received the main attention so far. The increasing energy proportionality of processors, however, shifts the focus to other components such as interconnection networks. Their share of the overall power consumption is expected to increase to 20% or more while other components further increase their efficiency in the near future. Hence, it is crucial to improve energy proportionality in interconnection networks likewise to reduce overall power and energy consumption. To facilitate these attempts, this work provides comprehensive studies about energy saving in interconnection networks at different levels.

First, interconnection networks differ fundamentally from other components in their underlying technology. To gain a deeper understanding of these differences and to identify targets for energy savings, this work provides a detailed power analysis of current network hardware.

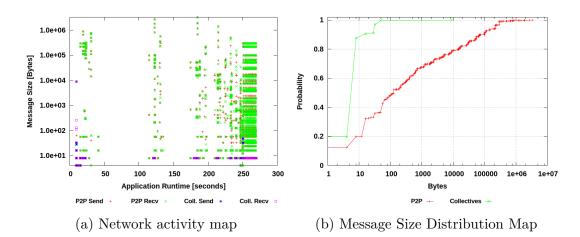

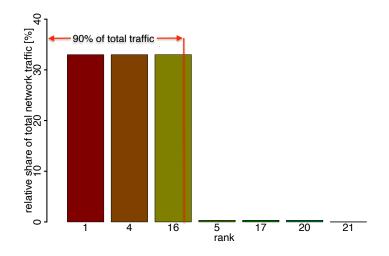

Furthermore, various applications at different scales are analyzed regarding their communication patterns and locality properties. The findings show that communication makes up only a small fraction of the execution time and networks are actually idling most of the time. Another observation is that point-to-point communication often only occurs within various small subsets of all participants, which indicates that a coordinated mapping could further decrease network traffic.

Based on these studies, three different energy-saving policies are designed, which all differ in their implementation and focus. Then, these policies are evaluated in an event-based, power-aware network simulator. While two policies that operate completely local at link level, enable significant energy savings of more than 90% in most analyses, the hybrid one does not provide further benefits despite significant additional design effort. Additionally, these studies include network design parameters, such as transition time between different link configurations, as well as the three most common topologies in supercomputing systems.

The final part of this work addresses the interactions of congestion management and energy-saving policies. Although both network management strategies aim for different goals and use opposite approaches, they complement each other and can increase energy efficiency in all studies as well as improve the performance overhead as opposed to plain energy saving.

# Zusammenfassung

In den letzten Jahren ist Energie zu einem der wichtigsten Faktoren für Entwurf und Betreiben großer Rechensysteme geworden. Dies gilt insbesondere für das Hochleistungsrechnen, wo Systeme oft aus Tausenden von einzelnen Rechenknoten bestehen. Besonders nach dem Ende des Dennard Scaling steigt der Bedarf an energieproportionalen Komponenten, bei denen die Energie linear von der Auslastung abhängt, kontinuierlich an. Als hauptverantwortliche Komponente für den Gesamtstromverbrauch haben die Prozessoren bisher die größte Aufmerksamkeit erhalten. Die zunehmende Energieproportionalität von Prozessoren verlagert jedoch den Schwerpunkt auf andere Komponenten wie zum Beispiel Verbindungsnetzwerke. Es wird erwartet, dass ihr Anteil am Gesamtstromverbrauch auf 20% oder mehr ansteigt, während andere Komponenten in naher Zukunft ihre Effizienz weiter steigern werden. Daher ist es von entscheidender Bedeutung, die Energieproportionalität in Verbindungsnetzwerken zu verbessern, um den Gesamtleistungs- und Energieverbrauch ebenfalls zu senken. Diese Arbeit trägt zu dieser Aufgabe bei, indem sie Energieeinsparungen in Verbindungsnetzwerken auf verschiedenen Ebenen umfassend analysiert.

Verbindungsnetzwerke unterscheiden sich in ihrer zugrunde liegenden Technologie elementar von anderen Komponenten. Um ein tieferes Verständnis dieser Unterschiede zu gewinnen und Ziele für Energieeinsparungen zu identifizieren, bietet diese Arbeit eine detaillierte Leistungsanalyse der aktuellen Netzwerk-Hardware.

Darüber hinaus werden verschiedene Anwendungen unterschiedlicher Skalierung hinsichtlich ihrer Kommunikationsmuster und Loakalitätseigenschaften analysiert. Die Ergebnisse zeigen, dass die Kommunikation nur einen kleinen Bruchteil der Ausführungszeit ausmacht und die Netzwerke die meiste Zeit tatsächlich ungenutzt bleiben. Eine weitere Beobachtung ist, dass Endezu-Ende-Kommunikation oft nur innerhalb verschiedener kleiner Teilmengen aller Teilnehmer stattfindet, was darauf hindeutet, dass ein maßgeschneidertes Zuordnen von Prozessen auf physikalische Rechenkerne die Netzwerkauslastung weiter verringern könnte.

Auf der Grundlage dieser Studien werden drei verschiedene Energiesparstrategien entworfen, die sich alle in ihrer Umsetzung und ihrem Schwerpunkt unterscheiden. Diese Strategien werden dann in einem ereignisbasierten Netzwerksimulator mit integriertem Energiemodell evaluiert. Während zwei Strategien, die vollständig lokal auf Linkebene arbeiten, in den meisten Analysen signifikante Energieeinsparungen von mehr als 90% ermöglichen, bietet die hybride Strategie trotz erheblichen zusätzlichen Designaufwands keine weiteren Vorteile. Darüber hinaus umfassen diese Studien Netzwerkdesignparameter, wie z.B. die Transitionzeit zwischen verschiedenen Linkkonfigurationen, sowie die drei häufigsten Topologien, die genutzt werden um Supercomputer zu entwerfen.

Abschließend werden im letzten Teil der Arbeit Wechselwirkungen von Congestion Management und Energiesparmaßnahmen thematisiert. Obwohl beide Netzmanagementstrategien unterschiedliche Ziele verfolgen und entgegengesetzte Ansätze verwenden, ergänzen sie sich gegenseitig und können die Energieeffizienz in allen Studien erhöhen und Performanzindikatoren im Gegensatz den reinen Energiesparstrategien verbessern.

# Table of contents

| 1        | 1 Introduction                                |                                                                                 |                                                  |                                                    |  |  |  |  |

|----------|-----------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|--|--|--|--|

| <b>2</b> | Background: Interconnection Networks          |                                                                                 |                                                  |                                                    |  |  |  |  |

|          | 2.1                                           | Switch                                                                          | Level Architecture                               | 11                                                 |  |  |  |  |

|          |                                               | 2.1.1                                                                           | Data Transmission                                | 11                                                 |  |  |  |  |

|          |                                               | 2.1.2                                                                           | Network Interface                                | 12                                                 |  |  |  |  |

|          |                                               | 2.1.3                                                                           | Links                                            | 12                                                 |  |  |  |  |

|          |                                               | 2.1.4                                                                           | Switches                                         | 14                                                 |  |  |  |  |

|          |                                               | 2.1.5                                                                           | Message Switching                                | 15                                                 |  |  |  |  |

|          | 2.2                                           | System                                                                          | n Level Network Design                           | 18                                                 |  |  |  |  |

|          |                                               | 2.2.1                                                                           | Topologies                                       | 19                                                 |  |  |  |  |

|          |                                               | 2.2.2                                                                           | Routing                                          | 24                                                 |  |  |  |  |

|          | 2.3                                           | Messa                                                                           | ge Passing Interface                             | 29                                                 |  |  |  |  |

|          |                                               |                                                                                 |                                                  |                                                    |  |  |  |  |

| 3        | $\mathbf{En}$                                 | ergy P                                                                          | roportionality in Interconnection Networks       | 31                                                 |  |  |  |  |

| 3        | <b>En</b><br>3.1                              |                                                                                 | Consumption       Interconnection       Networks | <b>31</b><br>32                                    |  |  |  |  |

| 3        |                                               |                                                                                 |                                                  |                                                    |  |  |  |  |

| 3        |                                               | Power                                                                           | Consumtion                                       | 32                                                 |  |  |  |  |

| 3        |                                               | Power<br>3.1.1<br>3.1.2                                                         | Consumtion                                       | 32<br>33                                           |  |  |  |  |

| 3        | 3.1                                           | Power<br>3.1.1<br>3.1.2                                                         | Consumtion                                       | 32<br>33<br>35                                     |  |  |  |  |

| 3        | 3.1                                           | Power<br>3.1.1<br>3.1.2<br>Switch                                               | Consumtion                                       | 32<br>33<br>35<br>36                               |  |  |  |  |

| 3        | 3.1                                           | Power<br>3.1.1<br>3.1.2<br>Switch<br>3.2.1<br>3.2.2                             | Consumtion                                       | 32<br>33<br>35<br>36<br>37                         |  |  |  |  |

| 3        | 3.1<br>3.2                                    | Power<br>3.1.1<br>3.1.2<br>Switch<br>3.2.1<br>3.2.2                             | Consumtion                                       | 32<br>33<br>35<br>36<br>37<br>38                   |  |  |  |  |

| 3        | 3.1<br>3.2                                    | Power<br>3.1.1<br>3.1.2<br>Switch<br>3.2.1<br>3.2.2<br>Link H                   | Consumtion                                       | 32<br>33<br>35<br>36<br>37<br>38<br>40             |  |  |  |  |

| 3        | 3.1<br>3.2                                    | Power<br>3.1.1<br>3.1.2<br>Switch<br>3.2.1<br>3.2.2<br>Link F<br>3.3.1<br>3.3.2 | Consumtion                                       | 32<br>33<br>35<br>36<br>37<br>38<br>40<br>41       |  |  |  |  |

| 3        | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Power<br>3.1.1<br>3.1.2<br>Switch<br>3.2.1<br>3.2.2<br>Link F<br>3.3.1<br>3.3.2 | Consumtion                                       | 32<br>33<br>35<br>36<br>37<br>38<br>40<br>41<br>41 |  |  |  |  |

| 4 Application Analyses |                                           |         |                                                                                                            |       |  |  |  |  |

|------------------------|-------------------------------------------|---------|------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|

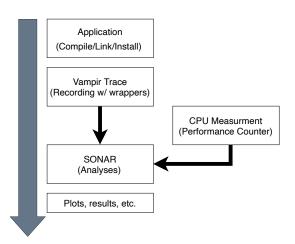

|                        | 4.1                                       | SONA    | R                                                                                                          | 48    |  |  |  |  |

|                        |                                           | 4.1.1   | Metrics                                                                                                    | 48    |  |  |  |  |

|                        |                                           | 4.1.2   | Concept                                                                                                    | 50    |  |  |  |  |

|                        | 4.2                                       | Locali  | ty and Selectivity in Exascale Proxy Miniapps                                                              | . 51  |  |  |  |  |

|                        |                                           | 4.2.1   | Metrics                                                                                                    | 52    |  |  |  |  |

|                        |                                           | 4.2.2   | Methodology                                                                                                | 56    |  |  |  |  |

|                        |                                           | 4.2.3   | Hardware Parameters                                                                                        | . 57  |  |  |  |  |

|                        |                                           | 4.2.4   | Results                                                                                                    | 60    |  |  |  |  |

| 5                      | Sim                                       | ulatior | n Tools                                                                                                    | 73    |  |  |  |  |

|                        | 5.1                                       | Netwo   | rk Simulator                                                                                               | 73    |  |  |  |  |

|                        |                                           | 5.1.1   | SAURON Simulator                                                                                           | 74    |  |  |  |  |

|                        | 5.2                                       | Energy  | y-Aware Simulations                                                                                        | 78    |  |  |  |  |

|                        |                                           | 5.2.1   | Energy Features                                                                                            | 79    |  |  |  |  |

|                        |                                           | 5.2.2   | Traffic Pattern                                                                                            | 80    |  |  |  |  |

|                        | 5.3                                       | MPI T   | Traces                                                                                                     | . 81  |  |  |  |  |

|                        |                                           | 5.3.1   | DUMPI Traces                                                                                               | 82    |  |  |  |  |

|                        |                                           | 5.3.2   | VEF Traces                                                                                                 | 83    |  |  |  |  |

| 6                      | Energy Saving in Interconnection Networks |         |                                                                                                            |       |  |  |  |  |

|                        | 6.1                                       | Appro   | ach                                                                                                        | 88    |  |  |  |  |

|                        |                                           | 6.1.1   | Energy Saving Management                                                                                   | 88    |  |  |  |  |

|                        |                                           | 6.1.2   | Power State Granularity                                                                                    | 90    |  |  |  |  |

|                        | 6.2                                       | Energy  | y Saving Policies                                                                                          | 92    |  |  |  |  |

|                        |                                           | 6.2.1   | $On/Off \ldots \ldots$ | 92    |  |  |  |  |

|                        |                                           | 6.2.2   | High/Low                                                                                                   | 96    |  |  |  |  |

|                        |                                           | 6.2.3   | Awake                                                                                                      | 98    |  |  |  |  |

|                        | 6.3 Evaluating Policies                   |         | ating Policies                                                                                             | 98    |  |  |  |  |

|                        |                                           | 6.3.1   | Applications                                                                                               | 99    |  |  |  |  |

|                        |                                           | 6.3.2   | Methodology                                                                                                | . 101 |  |  |  |  |

|                        |                                           | 6.3.3   | Evaluation                                                                                                 | 105   |  |  |  |  |

|                        | 6.4                                       | Combi   | ining Energy Saving Policies and Congestion Management                                                     | 110   |  |  |  |  |

|                        |                                           | 6.4.1   | Congestion Management                                                                                      | . 111 |  |  |  |  |

|                        |                                           | 6.4.2   | Methodology                                                                                                | 112   |  |  |  |  |

|                        |                                           | 6.4.3   | Evaluation                                                                                                 | 115   |  |  |  |  |

| <b>7</b>   | Disc           | viscussion                                                                                                                                 |  |  |  |  |  |  |

|------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|            | 7.1            | Related Work $\ldots \ldots 128$                |  |  |  |  |  |  |

|            | 7.2            | Workload Analysis                                                                                                                          |  |  |  |  |  |  |

|            |                | 7.2.1 Locality and Selectivity                                                                                                             |  |  |  |  |  |  |

|            |                | 7.2.2 Topology Effects $\dots \dots \dots$ |  |  |  |  |  |  |

|            |                | 7.2.3 Network Utilization $\ldots \ldots 130$                               |  |  |  |  |  |  |

|            | 7.3            | Energy Savings                                                                                                                             |  |  |  |  |  |  |

|            |                | 7.3.1 Policies $\ldots \ldots 137$                     |  |  |  |  |  |  |

|            |                | 7.3.2 Energy-Saving Parameters                                                                                                             |  |  |  |  |  |  |

|            |                | 7.3.3 Topologies $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $133$                                                      |  |  |  |  |  |  |

|            | 7.4            | Congestion Management $\ldots \ldots 134$                                   |  |  |  |  |  |  |

|            | 7.5            | Dutlook                                                                                                                                    |  |  |  |  |  |  |

| 8          | Con            | lusion 139                                                                                                                                 |  |  |  |  |  |  |

| Lis        | st of          | igures 145                                                                                                                                 |  |  |  |  |  |  |

| Lis        | List of tables |                                                                                                                                            |  |  |  |  |  |  |

| References |                |                                                                                                                                            |  |  |  |  |  |  |

# Introduction

Historically, the steady increase of computational power was driven by the decreasing size of integrated circuits and rising clock rates, described by Moore's law. This performance increase was facilitated by Dennard's scaling [1], which states that decreasing feature sizes also result in a proportional decrease in power consumption so that the power consumption per area remains constant. Additionally, pipelining and Instruction-Level Parallelism (ILP) ensured further performance scaling within a single Central Processing Unit (CPU). With mitigating clock rate growth in the 2000s, parallelism ensured further performance scaling. At about 2005, multi-core processors began to take over from single-core processors, which means multiple cores were integrated into one die. In order to take advantage of these parallel cores, software engineers followed this trend by shifting to Thread-Level Parallelism (TLP).

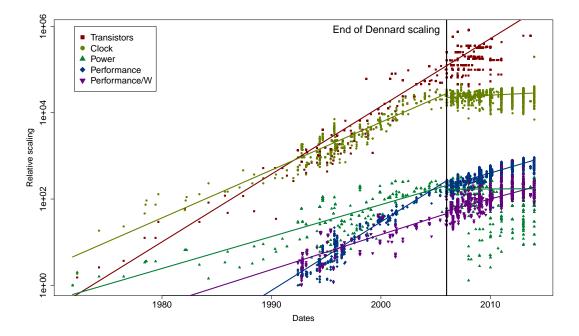

While Moore's law remains still valid, Dennard's scaling has come to an end [2]. Hence, the number of transistor devices per chip is still increasing, but power density for chips has reached its limit. As a result, chips have to operate within a strict power budget. This leads to more specialized functional units on a chip, which can efficiently perform narrower tasks. However, not all of these functional units can operate simultaneously to ensure compliance with the power budget. Transistors or areas on the chip that are not used because of power capping are referred to as dark silicon. Consequently, power and energy efficiency are some of the main drivers for the performance of today's computing systems. Figure 1.1 depicts the trends of these different design features over time. It can be clearly

#### Introduction

seen that performance steeply rises until 2006. At the end of Dennard's scaling (indicated by the vertical line), the increase of clock rates ends, which finally leads to a flattening of the performance trend.

Fig. 1.1 Technology scaling trends for various features.

Beyond specialized on-chip functional units and the increase of the number of cores per die, parallelization also includes the introduction of accelerators. The most common example for such an accelerator is a Graphics Processing Unit (GPU), which are highly parallel vector processors.

The growing number of parallel units in one system raises the demand for communication and data exchange between them. At the node level, different cores or functional units use an on-chip network (communication between parallel cores) or system networks, such as NVLink or Peripheral Component Interconnect Express (PCIe), (communication with accelerating units) to communicate and transfer data. Communication between distinguished nodes, however, is performed on interconnection networks. Furthermore, multiple nodes are clustered together to meet the demand for more computational power by further increasing the parallelism of a system. Hence, the performance requirements for these networks are rather challenging.

### **High-Performance Computing**

High-Performance Computing (HPC) describes systems that are designed for maximal computing performance using cutting edge technology. It takes up a predestined position in the field of computational science and is mostly performed on a supercomputer. The prime targets of these systems are often computeintensive, scientific workloads. These applications cover a wide range of different scientific applications, including weather forecasts, physical simulations, molecular modeling, nuclear research, quantum mechanics, and artificial intelligence.

Great efforts are made to meet the increasing demand for higher computational power of these compute-intensive applications, and promising new hardware and concepts are often tested in these systems. Hence, HPC is playing a pioneering role in the area of computational performance and is possibly affecting almost all other kinds of computing systems. HPC systems were the first to rely extensively on parallelization and were also heavily affected by the end of Dennard's scaling. While further performance scaling is now rather based on additional hardware accelerators, power supply, and heat dissipation remain the main challenges of high-performance computing at both chip- and system-level.

Adding specialized acceleration units affects the system's overall power consumption. Not only do these added components contribute through their respective power consumption but they also increase the need for additional data movements. This trend becomes even more important with the increasing number of compute nodes in HPC systems. Hence, the growing demand for more and more computing power also leads to special requirements on the interconnection network, such as high bandwidth and low latency. The continuing optimization of hardware and network protocols lead to highly specialized networks, which differ from general-purpose networks. For example, networks in HPC systems are commonly lossless. This means, that the network guarantees that no packets are dropped on their way from sender to receiver, which can be exploited to reduce performance overhead in the network protocols significantly.

The next milestone for HPC to be taken in the near future is a system that enables exascale computing  $(10^{18} \text{ FLOP/s})$ . Although computational power can be easily increased by adding more parallel units, the main challenge remains to build such a system at reasonable acquisition and operational costs. The US Department of Energy (DoE) has set the goal to design such a system within a power budget of 20 MW<sup>1</sup>. Hence, energy-efficiency is one of the main design goals in new HPC systems.

## **Energy Proportionality**

Operating an exascale system with current technologies and a strict power budget becomes even more challenging due to the lack of energy proportional hardware components. The concept of energy proportionality, which was first introduced by Barroso et al. [3], means that the power consumption of each component should be proportional to its utilization. For instance, if a CPU is working half the time and idling for the other half, the effective energy consumption of a perfect energy-proportional CPU would also be halved.

This approach originates from data centers and cloud installations, which usually operate at low utilization but are designed to handle peak loads. Although HPC installations commonly operate at higher utilization, not all components are evenly utilized. While great efforts have been made to increase energyproportionality in processing units as the main contributors to the overall power consumption, other components rather operate constantly at peak power. As a result, the remaining components increase their impact on the overall power consumption, although their contribution is rather low at Thermal Design Power (TDP). This effects particularly interconnection networks, which are expected to become one of the main power-consuming components as the development of energy-proportional processing units progresses. Multiple analyses show that their share of the overall power consumption will increase in the near future to up to 30% [4], [5]. Furthermore, the 2015 International Technology Roadmap for Semiconductors (ITRS) report predicts that soon data center power consumed by networking and switching will exceed the aggregated power consumed by storage and cooling [6].

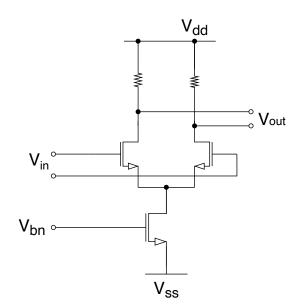

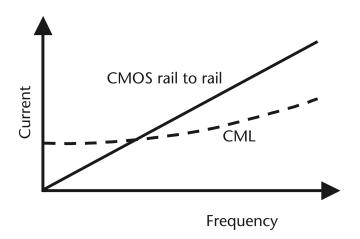

The situation is further complicated by the fact that well-established power saving mechanisms from other components cannot be simply adopted due to fundamental design differences. In contrast to most other CMOS-based components, interconnection networks heavily rely on Current Mode Logic (CML), which enables higher frequencies and stronger drivers at a given power budget.

$<sup>^{1}</sup> https://science.osti.gov/-/media/ascr/ascac/pdf/reports/Exascale_subcommittee_report.pdf, accessed: 2020-02-05$

As its name suggests, CML relies on a static current which makes its power consumption robust against frequency scaling. To gain further insights about the power consumption of interconnection networks and which energy-saving mechanisms are suitable are analyzed in Chapter 3. These energy-saving capabilities are also affected by the applications running on these systems. Generally, HPC applications tend to utilize system resources much more in opposed to common cloud workloads. However, our studies in Chapter 4 show that HPC workloads are also suitable for energy savings, particularly in interconnection networks. These analyses demonstrate that there is no perfect overlap of computation and data movements in a huge variance of different HPC and exascale proxy applications [7], [8].

Although few related works aim to tackle these problems, they rather focus on optimizations of particular settings. This includes a given interconnect technology/provider, such as Energy-Efficient Ethernet (EEE) [9] or Mellanox' InfiniBand [10], or single topologies, in particular fat trees [11]. None of these works study the interactions with other network management strategies, for example, congestion management.

To draw a comprehensive picture of energy-saving in the interconnection network, this work follows a technology-independent approach, which is evaluated in a variety of different scenarios. In Chapter 6, three simple energy-saving policies are introduced, which reflect different trade-offs between performance and aggressiveness in energy-saving [12], [13]. To evaluate these policies, they are tested in a cycle-accurate simulator in different settings, including multiple topologies, applications, and scales. While using a simulator enables technologyindependent testing of policies, the parameter set is derived from different kinds of real-world network technologies and is inside the scope of what is technically feasible. Overall, all configurations show high capabilities for energy saving and the introduced policies are able to reduce link energy by 92.7% on average by only increasing the execution time by an average of 5.7%. However, there are also few configurations that seem not to be suitable for energy saving. Although energy can still be saved their execution time is significantly increased.

Building on top of these first studies, the interaction of the power-saving policies with congestion management is investigated in Section 6.4. The main challenge for a possible synergy is that they are pursuing fundamentally different goals. While energy-saving policies benefit from few traffic flows that highly

#### Introduction

utilize links, congestion management aims for evenly split traffic flows over the entire network. Despite the combination of both has not been studied before, they both seem to complement each other and work well together [14].

### Contributions

This work makes the following major contributions:

- 1. Network power analyses a detailed analysis of various components of a modern interconnection network is performed. The different components of a switch fabric are studied at different scales, and the main contributors to the overall power consumption are identified. As a result, sweet spots for energy saving in the design and possible power-saving approaches are identified. The insights of this analysis are elaborated in Chapter 3.

- 2. Application analyses to identify energy-saving capabilities a large variety of different communication patterns of exascale proxy applications is studied regarding their suitability for energy saving. Especially sparse communication and long computation phases are highly suitable since these patterns cause long idling periods in the network. Furthermore, new metrics are introduced to indicate locality in these patterns, which can be exploited to further reduce network traffic. Details are found in Chapter 4.

- 3. Energy-aware discrete event-based simulation of interconnection networks an existing OMNeT++-based, cycle-accurate simulator is extended with energy features. These include the power consumption of all major components according to their particular configuration, which enables the introduction of discrete power states. These power states are used for energy measurements as well as comprehensive energy and power state analyses. More details are provided in Chapter 5.

- 4. Introduction of energy-saving policies based on the previous analyses, different energy-saving policies are introduced. These policies, which focus either on aggressive power saving or better performance, are easy to implement and show promising results regarding their energy-saving capabilities. Thereby, a decentralized approach is used to reduce management overhead. Furthermore, their interference with congestion management,

another traffic flow management system, is investigated. While congestion management is essential for HPC interconnection networks, both techniques follow contrary approaches and present a potential for conflicts. These studies are presented in Chapter 6.

### **Dissertation Outline**

The remainder of this work is structured as follows:

- Chapter 2 provides an overview of the structure of interconnection networks. This includes the hardware architecture of common switches, switching and routing schemes, as well as a brief introduction into message passing.

- Chapter 3 provides a power analysis of different components inside a switch fabric. Based on these insights and considering underlying design technologies, the best approaches for energy savings are identified.

- In Chapter 4, a wide range of HPC applications is analyzed regarding their energy-saving opportunities. The selected applications are based on the DoE's exascale mini-applications, representing a wide range of common workloads and communication patterns.

- Chapter 5 provides an overview of the methodology and tools that are used to determine the energy consumption and savings of different approaches. The majority of the energy studies are based on a network simulator that is capable of replaying Message Passing Interface (MPI) traces or generating synthetic traffic patterns.

- In Chapter 6 three different energy-saving policies are introduced and analyzed regarding their energy-saving potential and impact on the overall performance on exemplary HPC applications. Also, the interaction of these policies with often-used congestion management strategies is studied on synthetic traffic patterns.

- Chapter 7 provides an overview of related works and discusses the findings of the previous chapters. Finally, a brief outlook about future research directions is given.

- Chapter 8 summarizes and concludes this work.

# Publications

This section provides the works in context of this dissertation that have been published in international conferences and journals with peer review.

- F. Zahn, P. Yebenes, S. Lammel, P. J. Garcia, and H. Fröning, "Analyzing the energy (dis-) proportionality of scalable interconnection networks," in 2nd IEEE International Workshop on High-Performance Interconnection Networks in the Exascale and Big-Data Era (HiPINEB), 2016, pp. 25–32.

- S. Lammel, F. Zahn, and H. Fröning, "Sonar: Automated communication characterization for hpc applications," in High Performance Computing, M. Taufer, B. Mohr, and J. M. Kunkel, Eds., Cham: Springer International Publishing, 2016, pp. 98–114

- F. Zahn, S. Lammel, and H. Fröning, "Early experiences with saving energy in direct interconnection networks," in IEEE 3rd International Workshop on High-Performance Interconnection Networks in the Exascale and Big-Data Era (HiPINEB), Feb. 2017, pp. 33–40.

- F. Zahn, A. Schäffer, and H. Fröning, "Evaluating energy-saving strategies on torus, k-ary n-tree, and dragonfly," in IEEE 4th International Workshop on High-Performance Interconnection Networks in the Exascale and Big-Data Era (HiPINEB), Feb. 2018, pp. 16–23.

- F. Zahn, S. Lammel, and H. Fröning, "On link width scaling for energyproportional direct interconnection networks," Concurrency and Computation: Practice and Experience, vol. 31, no. 2, e4439, 2019.

- F. Zahn, P. Yebenes, J. Escudero-Sahuquillo, P. J. Garcia, and H. Fröning, "Effects of congestion management on energy saving techniques in interconnection networks," in International Workshop of High-Perfomance Interconnection Networks in the Exascale and Big-Data Era (HiPNEB), Feb. 2019, pp. 9–16.

- F. Zahn and H. Fröning, "On network locality in mpi-based hpc applications," in 49th International Conference on Parallel Processing - ICPP (ICPP '20), Edmonton, AB, Canada: ACM, New York, NY, USA, Aug. 2020, p. 11.

# **Background: Interconnection Networks**

With the increasing size of parallel systems, the importance of networks increases likewise. Thereby, networks are used for various connection purposes, ranging from small distance connections between functional units up to long distances, spanning the world wide web. This wide range of networks can be clustered into four major groups of networks [15]:

- 1. Network on Chip (NoC): They are used to connect multiple functional units of a System on Chip (SoC), such as processor cores, caches, or register files. Although their connection distances are limited to the order of centimeters, they provide multiple advantages over traditional buses, such as increased energy efficiency, better scaling, or support for asynchronous clock domains.

- 2. System Area Networks (SAN): This type of network is usually used to connect multiple processors or processor to memory in multicomputer systems. These networks can include several thousands of such devices and are usually used in the context of data centers or supercomputers. Since these systems have to meet ambitious performance requirements and computation tended to be a bottleneck, customized hardware is often used in the context of these systems [16], such as the Infiniband standard [17] or Intel's Omnipath [18].

- 3. Local Area Network (LAN): LANs are designed to cover small geographical areas, reaching from buildings over few adjacent buildings up to campus

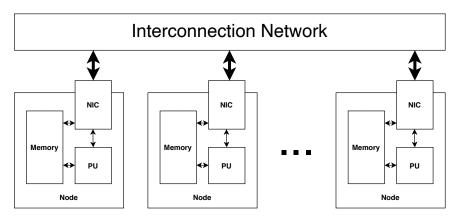

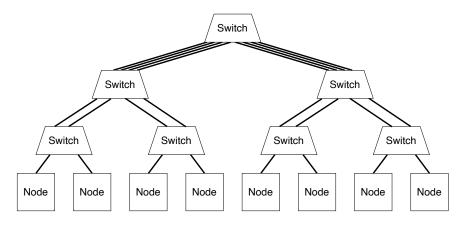

Fig. 2.1 Design scheme for parallel SAN systems.

areas [19]. Most commonly, Ethernet is used to connect autonomous computing systems in this type of network [15].

4. Wide Area Network (WAN): WANs are distributed over large geographical areas, which scale up to thousands of kilometers, and can include many millions of computers. Because of the large distances and amount of transferred data, today's WANs are usually composed of fast optical connections. The Internet WAN is probably the most prominent representative of this network class.

There are no sharp lines between these types of networks and some examples are overlapping two types. However, interconnection networks in HPC systems are generally located in the area of SANs.

Figure 2.1 depicts the schematic set-up a parallel HPC system. These systems consist of a variety of nodes that are equipped with one or more processing and memory units. Additionally, every node has an interface, which is called Network Interface Controller (NIC), that enables communication via the interconnection network with other nodes. Although Uniform Memory Architecture (UMA) shared-memory systems, in which the network connects several processing units with external memory, are also representatives of SANs, they do not scale well and are limited to rather small systems. Therefore, these studies focus on large-scale, distributed shared-memory systems equipped with specialized custom interconnection networks.

#### 2.1 Switch Level Architecture

Transferring data on the network requires interactions of multiple protocols, software stacks, and different hardware components. To enable a better understanding of these processes the Open Systems Interconnection (OSI) project developed a model that describes networks as a series of layers. These layers ease the understanding of processes in the network and responsibilities of particular units or protocols. The focus on this section is on different designs and processes in the two lowest layers, the link and physical one.

#### 2.1.1 Data Transmission

When data is exchanged between network clients (processors or memory), they communicate in units of messages [20]. These messages are created in the application layer (layer 7) and contain additional metadata, such as memory addresses and receiver information, and the actual data that a client wants to transfer. These messages do not limit the amount of data that can be sent and can have an arbitrary length. Since the physical interface demands for a uniform format, the messages are further processed in the NIC. Regarding the OSI model, this takes place in the transport layer (layer 4).

Here, the messages are partitioned into packets. These packets start with a specified header format, which contains information about the sender, receiver, length, and other data that is required by the routing unit, followed by a payload with the actual data or parts of it. Packets end with a tail, that includes an error-detection check, such as Cyclic Redundancy Check (CRC). Although payload length in today's interconnection networks can have a volatile length, their maximum is often limited to a few megabytes. If the message length exceeds the maximum payload length, the message is split up into the resulting number of packets.

In layer 3, the network layer, addresses are handled, routing information is added, and generally routing decisions are made. The lowest layers, (link and physical layer) are responsible for the actual data transmission and error detection and recovery [19]. In this layer, packets are split again into smaller parts for performance reasons. First, they are divided into Flow Control Unit (FLIT) frames. These units are determined by the flow control and buffer structures. In the physical layer, FLITs can further be sliced into Physcial Units (PHIT) which corresponds to the physical width of a link [21]. However, data transmission in the context of this work is observed at packet granularity, since it focuses on the network layer. At the receiving side, each message is reversely processed in the opposite order of all layers.

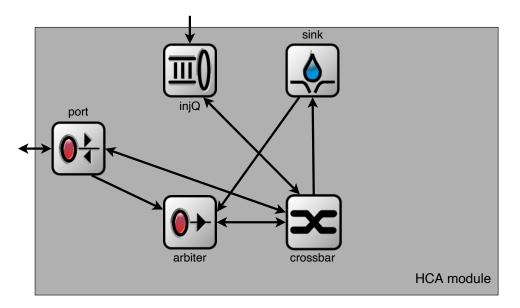

#### 2.1.2 Network Interface

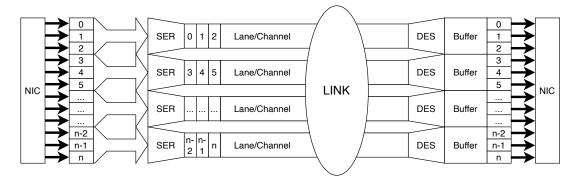

The NIC is the host interface that connects a node to the interconnection network to source and sinks packets. One the host side, the NIC is directly connected to the internal bus of the host node and on the network side either to a switch or another NIC. Since the NIC has to handle this two-way traffic, its particular architecture is highly dependent on the network and the host [22].

Essentially, the NIC contains an embedded processor to format packets, which includes splitting up messages and creating a header with all necessary routing and control information, and perform end-to-end error checks [23]. Furthermore, it may be equipped with substantial input and output buffer compared to switches.

#### 2.1.3 Links

Links or channels are physical connections between two network entities. They are either composed of one or more electrical wires or optical fiber and connectors at both ends [23]. Although a wide range of different standards and designs exist, they all share the same purpose of transmitting analog signals from a sender to the receiver, where the original digital data stream is obtained. Links can be either uni- or bidirectional. In HPC systems bidirectional links are widely used and, therefore, all links are assumed to be bidirectional in the context of this work.

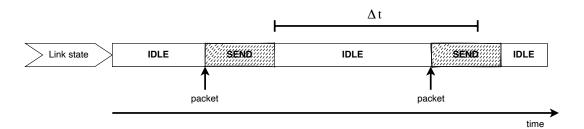

Links can vary in length, clocking scheme, and width [23]. Electrical links are capable of transmitting data over distances of up to about 100m [24], but since the RC delay in wires increases square of the length, longer cable length demand for stronger, more power-consuming drivers [23]. Additionally, losses due to skin effect, dielectric losses, etc. in these cable increase with cable length, whereas losses in optical fibers are rather small. However, the optical cable requires connectors to transform the digital electrical data stream to an optical signal. Clocking in the interconnection link can either be synchronous and asynchronous. While asynchronous links obtain a simpler design and interface, they result in lower frequencies and produce significant power overhead to achieve specific bandwidths [25]. Therefore, asynchronous links are not suitable for HPC systems. Synchronous links, however, require constant clock recovery, for example via Phase-Locked Loop (PLL) and Clock and Data Recovery (CDR). As a consequence, synchronous links are sending idle pattern when no data is transmitted to ensure word alignment. The width of links is determined by the number of parallel wires or lanes inside one link. Although increasing the number of lanes is a sophisticated way to improve bandwidth at a given frequency, only limited scaling is possible. The two main restrictions that limit the link width are crosstalk inside the cable and a more important pin count limitation due to the spatial extent of the backplane [15].

This limit of link width also drives the need for serialization and deserialization (ser/des) technology at both ends of the links. On the transmitting side (TX), the parallel data stream that arrives at the NIC is usually wider than the link. Hence, this data stream needs to be serialized according to the link width. Since transmission on the interconnection network aims to at least provide the same bandwidth as internal data paths, the transmitting frequency has to be higher by the same factor as the ratio between the bus and link widths. On the receiving side (RX), this faster serial analog data stream is checked for correctness and deserialized back to a parallel data stream.

Operating data streams at different frequencies also requires buffers to store data that cannot be processed immediately. These buffers can be designed in different ways. Typically, links are equipped with either input or output buffers, or both. Output buffered links have the advantage of head of line blocking prevention, which is explained more detailed in chapter 6, since all packets obtain the same status. However, all incoming packets have to be directly processed and stored in the respective output buffer. This requires an internal speedup of switches of the same factor as there are parallel lanes inside one link. Therefore, this very expensive solution is rarely implemented in lossless networks [15]. In the following, the part of the NIC or switch, which contains the ser/des and buffers for one link, is referred to as linkport.

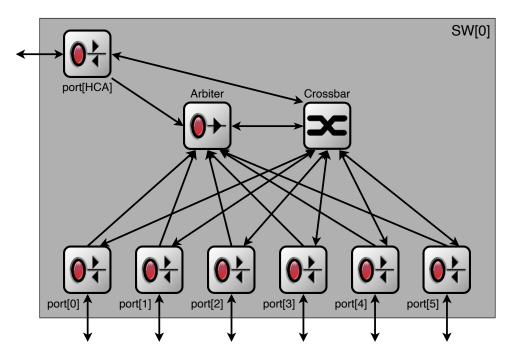

#### 2.1.4 Switches

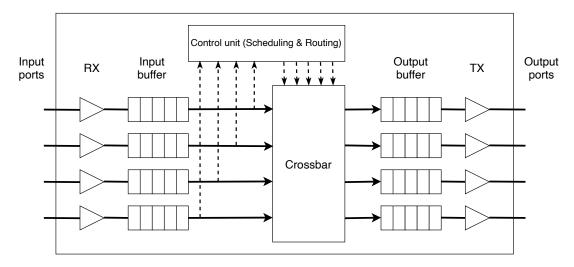

Switches are network entities with a set of input ports, output ports, and an internal crossbar that connects every input to every output port [23]. Additionally, a switch is equipped with control units, such as an arbiter or routing unit. Figure 2.2 depicts the scheme of an exemplary switch, introducing all relevant components. On the left side, there are input ports (RX), including input buffers, and on the right side the output ports (TX) along with output buffers. As previously mentioned, the actual buffer structure may include input or output buffer, or a combination of both, depending on the network implementation. Note that for bidirectional links the input and output ports are located in the same physical linkport. For most switches applies that the number of input ports equals the number of output ports and this number is referred to as the switch's radix or degree. The core of the switch is the crossbar and the corresponding control units. A  $n \times m$  crossbar connects n inputs to m outputs without intermediate stages [20]. By definition, each output must be connected to at most one input port, which has to be ensured by the control unit, namely arbiter, and routing unit. The former schedules the order in which packets are processed and forwarded. The latter makes the routing decision for each packet, for example, based on routing tables, and configures the crossbar in a way that the input port of the current packet connects to the right output port. When the packet has passed the crossbar, the arbiter selects the next packet and the routing unit configures the crossbar accordingly to the new routing information. The complexity of these control units depends on the routing and scheduling algorithm [23].

Although crossbars are non-blocking, they are not suitable for larger networks due to their poor scalability [20]. Not only do costs increase as  $n^2$  for an  $n \times n$ crossbar but also the pin count limitation and scheduling problems become prohibitive. These scaling issues affect the performance of high-radix switches so that low diameter switched provide lower latencies, fewer contention, and higher throughput at the same bisection bandwidth [26]. Therefore, modern high-radix switches are internally composed of multiple smaller crossbars that are connected in a hierarchical pattern, which improves latency significantly and reduces area by almost half [27].

Fig. 2.2 Switch blueprint with essential components.

#### 2.1.5 Message Switching

The last major domain of the link and data layer, and already interfering with the network layer, is message or packet switching. This includes the switching techniques that are implemented in the network and different flow control mechanisms [16]. However, this does not include routing decisions or network paths but message processing inside the switch or the network in general.

#### Message Switching Techniques

The message switching policy controls how packets are routed inside a switch, e.g. the procedure that happens between the arrival of a packet at the input port and the departure of the same packet at the output port. The time between these two events is referred to as routing delay and is mainly driven by the time it takes to process routing information and set up the internal logic [16]. Depending on various factors, such as application types, vendors, or timing constraints, multiple different message switching techniques exist.

The first and one of the simplest message switching techniques is circuit switching [20]. In this approach, two nodes establish a permanent physical link between them, which is reserved exclusively for communication of this node pair. In the beginning, the source node sends a header packet to the destination, which establishes the path along with all switches in between. Once this header packet arrives at the destination node, this node acknowledges the source node that the path is set up. After the path is established all data can be transmitted directly to the destination node and it sinks there. At the end of the data stream, a footer indicates the end of the message, and the path is released along the way. Circuit switching is especially sufficient for application with sparse communication and long messages. Note that networks that rely on circuit switching require almost no buffers since they only have to store other header packets, and no flow control. However, this is not feasible for most systems, since these established paths prohibit other network flows that are sharing the same resources. Additionally, long set up times cause a significant overhead for smaller messages. The impact of this overhead decreases with increasing message size.

Packet switching [16] refines the idea of circuit switching. Instead of sending all data at once, messages are split up into packets of a pre-defined maximum length. Each packet is equipped with its header and can be transmitted independently. In the simplest version, each packet is stored entirely in each intermediate network node or switch, before it is forwarded to the next node (store and forward). This technique is much more suitable for frequent smaller messages since only segments (e.g. single links) are occupied by a single packet, which enables more simultaneous traffic flows in the networks. But this also increases the overhead. The amount of data that is transferred on the network increases, since each packet got its header instead of one header per message. Furthermore, the routing delay might increase since each packet is routed individually, and also the demand for buffers increases, since packets have to be stored entirely after each hop.

In order to tackle some of these disadvantages, virtual cut-through switching [16] was introduced. This technique is also based on packet switching but represents an alternative to the store and forward approach. In the store and forward approach, a packet is stored completely before it is routed to the next node. That implies that the header, which arrives first, is first evaluated when the tail of the packet is stored in the buffer. Virtual cut-through switching aims to minimize this delay. In this technique, the header is evaluated instantly when it arrives and, consequently, routing decisions and configurations can be made simultaneously the arrival of the residual packet. Hence, the header might leave the switch, before the packet is stored completely, and the remaining parts are just routed the same way. This effective pipelining of packets does not only reduce the routing delay inside each switch but also dispense the need for output buffers since packets can be routed right away. If there is heavy traffic on the network and packets have to wait before the can be forwarded to the next node, the header is blocked and the packet drops back to the packet switching case, where the packet is stored completely in the input buffer.

The last message switching technique in the context of this work is wormhole switching [16]. This technique is similar to virtual cut-through switching but aims to reduce buffer requirements. Packet switching and virtual cut-through switching require large buffer sizes to temporarily store packets in the worst case when the network is highly utilized. Therefore, the wormhole switching technique further splits packets up in smaller pieces (FLIT). The size of a FLIT is determined by the flow control and buffers are usually dimensioned to store a few FLITs simultaneously. This scheme basically increases the number of pipeline stages by potentially spreading a single packet over multiple switches and buffers, respectively. While on low traffic virtual cut-through and wormhole switching are very similar, they behave significantly differently on higher loads. The smaller transfer units decrease the probability of blocking other traffic flows. Thus, wormhole switching significantly reduces average message latency and buffer requirements [16].

#### Flow Control

The flow control mechanism manages the available resources in a network, such as buffer capacities, bandwidth, or control states [20]. To avoid high latencies caused by dropped packets, HPC interconnection networks are usually lossless. This means, that packets are not dropped by the network and the receiver does not have to acknowledge the reception of the packet. Especially in lossless HPC networks, a good flow-control is crucial to avoid the losses of packets due to overflowing buffers on the one hand and ensuring efficient utilization of available network resources on the other hand.

The most basic flow control mechanisms are bufferless [20]. This means that packets are not stored if a certain resource is not available but either routed differently or simply dropped. While this is easy to implement and they are not sufficient for lossless networks. The majority of flow control schemes are buffered and rely on some version of a request/acknowledgment protocol.

The simplest implantation of buffered flow control is a link-level handshake [23]. Here, the source sends a request to the destination, when a FLIT is ready to be sent. Then, the destination acknowledges the receipt of this flit and the sender can request a link for the next FLIT. More sophisticated flow control

schemes aim to reduce synchronization overhead. The most commonly used approaches are Xon/Xoff (Stop&Go) and credit-based flow controls [15]. The former assumes low buffer levels at the receiver and sends packets whenever they reach the linkport. When the buffers on the receiving side obtain high occupancy levels, the receiver notifies the sender with a stop message and a go message, respectively, when the buffer occupancy has decreased. These notifications are usually either transmitted on additional control wires or encoded in control packets [15]. In a credit-based flow control, the sender obtains a credit count that represents the number of FLITs that can be stored in the destination's input buffer [20]. Then, the flow control is throttling network traffic injection when the buffer on the receiving side fill up [15]. To keep track of the buffer levels at the receiving side, the credit counter is reduced every time a FLIT is sent. If the counter reaches zero, this means the input buffer on the receiving side is full and the sender stalls until new credits are available. On the receiving side, the destination sends a credit back, when a FLIT is further processed and its buffer space is freed.

Both techniques are used in modern interconnection networks, depending on the purpose, vendor, etc. Credit-based flow controls usually cause more overhead than a Xon/Xoff, since every processed FLIT causes a credit message, where the latter only needs notifications at high buffer occupancy levels. However, Xon/Xoff requires more than the double buffer size compared to credit-based systems because they need enough buffer size to prevent overflows before the stop notification arrives at the sender side [15]. Since the sender stops sending when it runs out of credits, overflows are impossible with credit-based flow controls. Generally, both techniques can only provide full link bandwidth, when the buffers are well-dimensioned for the distance between the source and destination [15].

### 2.2 System Level Network Design

Besides the technical features of switches and channels, which are part of layers one and two in the OSI model, the second main domain corresponds to layer three, the network layer. This includes the physical layout, e.g. the pattern in which single compute nodes are connected, and routing of the interconnection network.

#### 2.2.1 Topologies

The topology describes the layout in which compute nodes are connected. Formally, they are described by a graph G(N,C) with a set of nodes (compute nodes or switches) N and a set of links that connects graph nodes [16]. Multiple features are used to characterize topologies [16], including:

- Node degree: it is a measure for direct topology, which describes the number of directly connected neighbor nodes.

- Diameter: is defined by the maximum shortest path in the network.

- Regularity: indicates whether all nodes have the same degree or not.

- Symmetry: describes if the network looks the same from every node's perspective.

- Bisection bandwidth: The minimum bandwidth that is achieved when dividing the network into two halves.

The layout also impacts significantly a network's performance in terms of latency and bandwidth as well as costs in terms of hardware expenses, cooling, and spatial design.

While there are plenty of different topologies for general-purpose networks, HPC systems consist of thousands of nodes and require additionally good scalability. In general, three different classes of topologies are distinguished. In direct topologies, each NIC has an integrated switch [20]. This limits the switch radix due to spatial reasons but reduces latency for network accesses. The group of indirect topologies, in which nodes are always connected through external switching devices, is further divided into two classes: hierarchical and non-hierarchical indirect topologies. Hierarchical networks are composed of discrete layers, where each distinct layer is designed with individual functions to accomplish its purpose. A non-hierarchical indirect topology can often be described as Multistage Interconnection Networks (MIN). In order to overcome the crossbar scaling problem, MINs are used by organizing smaller switches in multiple stages in a way that connectivity between every source/destination pair is ensured [15].

To cover all of these classes, one representative each is used in the following studies.

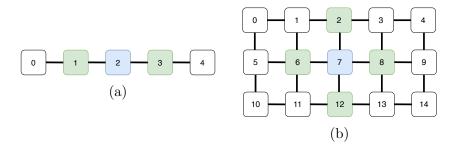

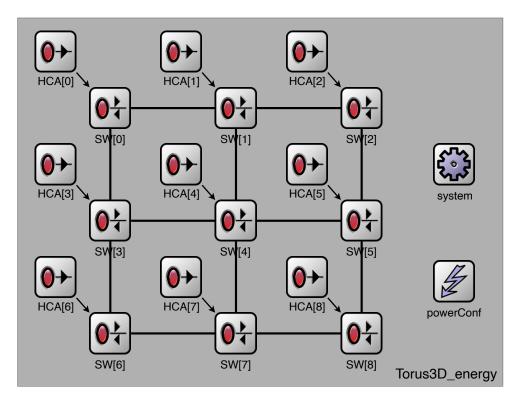

#### **3D** Torus

In the context of network topologies, tori exist in multiple dimensionalities. A torus refers to a grid, which is equipped with wraparound links at the edge of every dimension. Hence, a torus forms a ring in every dimension, which halves the diameter by two compared to a regular grid. In off-chip networks, the most common one is the 3D torus, which corresponds to an enhanced mesh and is usually designed as direct topology. Figure 2.3 depicts a 2x2x2 torus with the characteristic wrap-around links in every dimension.

Fig. 2.3 Example 2x2x2 3D torus topology.

This regular and symmetric topology provides multiple advantages. First, as in all direct topologies, is the integration of the switch inside the NIC reduces the latency. This layout is only feasible because each node is only connected to its small set of neighbors. The switch radix that can be integrated into the NIC is limited by the dimensions of the slot in the backplane. However, this modular design enables good scalability and easily allows for expansions with additional nodes without the need to fully reconfigure the entire system. In terms of hardware costs, the neighbor-based connection pattern allows the torus to get along with a relatively large amount of short and cheaper electrical cables up to a certain scale. On the downside, this design results in a fast increasing diameter and the comparatively low bisection bandwidth. Table 2.1 compares the basic aspects of the other topologies used in context if this work.

|               | 3D Torus | Fat Tree                        | Dragonfly             |

|---------------|----------|---------------------------------|-----------------------|

| Diameter      | x+y+z    | $2(\log_{k/2} N)$               | 3  or  5              |

| Regularity    | +        | +                               | +                     |

| Symmetry      | +        | -                               | -                     |

| # of switches | N        | $N/k \times (2\log_{k/2}N - 1)$ | N/p                   |

| # of links    | 3N       | $N(\log_{k/2} N)$               | $N(\frac{a+h}{2p}+1)$ |

Table 2.1 Properties of the studied topologies. N indicates the total number of end nodes, k the switch radix, and x, y, z, the number of nodes per dimension in the torus. The parameter a, p, andh are design parameters of the Dragonfly and are described further in the respective section.

#### Fat Tree

The next studied topology is tree-based and, therefore, a representative of nonhierarchical indirect topologies. For a small set of end nodes, it is sufficient to connect these nodes through only one switch. However, as the number of nodes increases, the crossbar scaling problem prohibits a further switch radix scaling. MINs provide a solution to this problem. They consist of multiple smaller switches that are connected in specific patterns to emulate larger radices. Generally, tree-based graphs are suitable patterns for MINs, and form a subset of these. However, some designs are more suitable than others. For instance, a regular binary tree provides very poor bisection bandwidth since the root becomes the bottleneck for most of the traffic.

A tree-based topology that aims to tackle this disadvantage is the fat tree, which provides the same bisection bandwidth at every stage [28]. To achieve this, the branches become thicker at the same scale as there are leaves connected to a switch. An exemplary configuration of eight nodes is illustrated in Figure 2.4. However, this is only a schematic depiction, as fixed switch radices require a more advanced connection pattern.

Formally, to remain a constant bandwidth at all stages, the switch ports (k) for each vertex at stage *i* grow by  $k^i$ , except for the root stage, which is only equipped with downward links. This is usually accomplished by using  $k^{i-1}$  switches per vertex. Therefore, each stage consists of 2N/k switches, which results in  $2N/k \times (\log_{k/2} N)$  total switches (minus N/k switches at the root stage) [15]. In particular, this configuration is a special instance of a clos network.

Besides regularity and good bisection bandwidth, fat trees can be scaled

Fig. 2.4 Example k-ary n-tree topology.

simply by adding additional stages. However, it is almost impossible to extend an existing configuration due to the complex connection pattern between single switches and stages. Therefore fat tree systems are not as adaptable to new requirements as for e.g. tori networks. Furthermore, larger configurations demand an increasing amount of more expensive optical cables, as they are used to connect stages close to the root. Overall the fat tree is widely used in HPC system for its beneficial properties. The top 3 of the fastest supercomputers in 2019 are equipped with fat tree-based interconnection networks, namely Summit, Sierra, and Sunway TaihuLight.

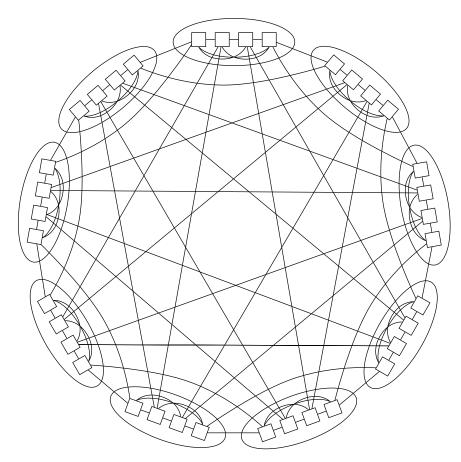

#### Dragonfly

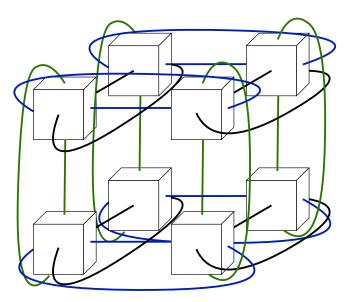

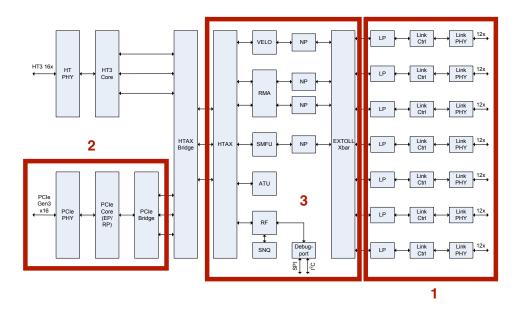

The last class of hierarchical indirect topologies is represented by the dragonfly [29]. The design goal of this rather new topology was to minimize the number of optical channels in order to reduce hardware costs. Besides, this also results in an overall low diameter. Like all hierarchical networks, the dragonfly is composed of different levels. Sets of compute nodes are organized to groups, with originally one group located in one cabinet. The compact spatial distances enable the usage of short and cheap electrical channels. These groups are then connected at the global level using long optical links between different cabinets. An exemplary dragonfly structure is depicted in Figure 2.5. The particular design is then determined by the three core parameters p (the number of compute nodes connected to each switch), a (the number of switches per group), and h (the number of global links in each switch). The remaining design then results from these parameters, such as the total number of groups (g = ah + 1) or compute

nodes (N = ap(ah + 1)). Kim et al. do not provide a strict rule on how to select these parameters particularly. However, they recommend to follow the rule  $a \ge 2h$  and  $2p \ge 2h$  to ensure a balanced network.

Fig. 2.5 Example of a dragonly topology with nine groups.

Applying this rule results in a maximum ratio from global to local links of 1/3. Additionally, the dragonfly uses generally fewer channels than the other investigated topologies. This comparable low number of links in addition to a remaining amount of network traffic rises the risk of congestions. To prevent these, special requirements must be met by the routing in order to balance the traffic evenly over the network. Furthermore, depending on the number of groups and the number of global links, it is not ensured that all groups are fully interconnected. While the original paper does not provide any information about this layout, various schemes for global links exist. Palm tree is one commonly used scheme and is also applied in the context of this work. In this pattern the *n*th global link of a group connects to the *n*th group, the (n+1)th link to ne (n+1)th group, etc. Formally, port *i* with  $i \in (0, ..., s-2)$  of switch *j* with

$j \in (0, ..., s - 1)$  is connected to group  $(i + j + 1) \mod s$ , where s is the total number of switches [30].

Derived from this topology, there exist other topologies that aim to tackle particular limits of the dragonfly, such as slimfly that aims to ensure better resiliency than the dragonfly [29] and dragonfly+, which increases scalability [31]. However, the focus of this work remains on the original dragonfly topology.

#### 2.2.2 Routing

While protocols in the data link layer define the procedure of data exchange between two distinguished nodes connected by one link and topologies define the physical layout of the interconnection network, the routing provides the formal description of the route a message is traversing along in the network. In particular, the routing algorithm reduces the set of possible paths to a limited set of legal paths [23], whereby legal paths must not be necessarily the shortest path between two nodes. Usually, routing algorithms are tailored to particular topologies or classes of topologies. They can exploit certain topology properties to provide different guarantees or to make certain performance trade-offs [23]. For example, some commonly used routing algorithms depart from the shortest path in order to achieve a load balancing over the network and reduce the probability of occurring congestions. Although there exists a large variance in routing algorithms, the ones used in the context of this work are introduced here.

Generally, there are two major classes of routing algorithms: deterministic and adaptive routing. The former are statically computed and there is one deterministic path between every source and destination pair. This allows the network to initialize the routing during set up time and store the calculated results in a fast Look Up Table (LUT). Therefore, there are no further routing computations during execution time necessary. The second advantage of one predefined path between source and destination is the guaranteed packet ordering since all buffer structures are First In First Out (FIFO)s.

The latter class, by contrast, makes it routing decisions during execution time. The ability to adjust routes dynamically to current conditions can provide significant performance advantages, especially in congested situations. For example, if there is a hot spot in the network, where many traffic flows combine, the routing can adjust to this situation and redirect single paths. However, this comes at the price of additional computing resources in the routing unit and higher complexity to observe certain guarantees, such as packet order or livelock freedom. Hereby, livelocks refer to the situation in which paths that have an unbounded number of allowed non-minimal hops from packet sources, for instance, may result in packets never reaching their destinations [15]. Particularly adaptive routing algorithms are susceptible to livelocks since different switching instances in the network can make contrary decisions which cause a packet to swing between continuously.

#### Deadlock

A network anomaly that commonly needs to be prevented by the routing is the deadlock. A deadlock occurs, when some packets cannot advance towards their destination because the buffers requested by them are full [16]. If multiple packets block and request mutual resources, they or locked forever. In particular, a deadlock arises, when the following necessary conditions are met [19]:

- Mutual exclusion: At least one resource must be held in a non-shareable mode; that is, only one process at a time can use the resource. If another process requests that resource, the requesting process must be delayed until the resource has been released. For instance, a packet is stored in the buffer is holding the memory space exclusively.

- Hold and wait: A process must be holding at least one resource and waiting to acquire additional resources that are currently being held by another process. For example, if the packet in the buffer is ready to be sent, but the flow control has no credits.

- No preemption: Resources cannot be preempted; that is, a resource can be released only voluntarily by the process holding it after that process has completed its task. The output buffer in which the packets were stored is only released when the packet was transmitted successfully.

- Circular wait: A set  $\{P_0, P_1, \ldots, P_n\}$  of waiting processes must exist such that  $P_0$  is waiting for resource held by  $P_1$ ,  $P_1$  is waiting for a resource held by  $P_2$ , ...,  $P_{n-1}$  is waiting for a resource held by  $P_n$  and  $P_n$  is waiting for a resource held by  $P_0$ .

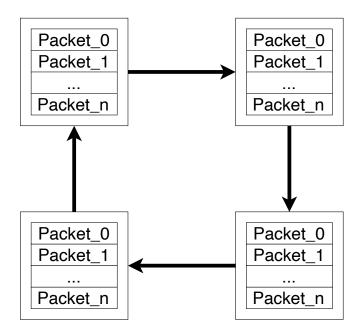

Fig. 2.6 Schematical Illustration of a deadlock. Each buffer is completely filled and requesting to send packet to the next node.

Figure 2.6 depicts a deadlock it the network schematically. In this four-node ring, each buffer is filled with packets and the packets are addressed to the next node. Since the buffers are full, the flow control does not allow to send any packet and the whole network stays in this state forever.

Commonly, there are two main strategies to handle deadlocks: deadlock avoidance and recovery. In the former approach, the routing algorithm avoids deadlocks by breaking one of the four conditions. Although all conditions are evenly effective to avoid deadlocks, usually the routing algorithm selects paths in a way that they cannot form a cyclic dependency [15]. The latter approach starts from the premise that deadlocks are only exceptions and occur rarely, and there is no prevention necessary. If a deadlock situation arises, it is then identified and resolved by the routing algorithm. Two common approaches to resolve a deadlock situation are dropping certain packets, that are causing the deadlock or redirecting them to special deadlock recovery resources [15].

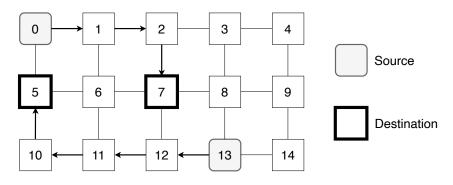

#### **Dimension Order Routing**

Dimension order routing is a deterministic routing algorithm that is most commonly used in mesh and tori networks. The procedure of this routing algorithm is to route packets by crossing dimensions in a particular order, nullifying the offset

in one dimension before routing to the next one [16], as depicted in Figure 2.7.

Fig. 2.7 Schematic illustration of dimension order routing.

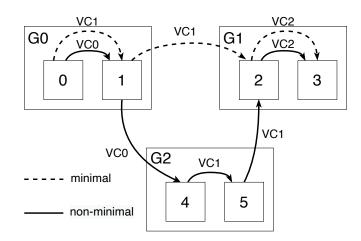

The order in which the dimensions are run through is usually indicated by a short extension of the algorithm name, such as xyz-dimension order routing. This algorithm is easy to implement and results in a shortest-path routing, which also prevents livelocks. However, there are also some downsides. While dimension order routing guarantees deadlock-freedom for mesh topologies, this does not hold true for tori networks, since their wrap-around links cause a ring in each dimension. One simple way of deadlock prevention in dimension order routing is the introduction of Virtual Channel (VC)s [32]. The usage of multiple virtual channels on the same physical channel brakes up the circular wait condition and guarantees deadlock freedom. Another problem of dimension order routing is load balancing. One major goal of a routing algorithm is to split up the traffic evenly over the network. The dimension ordering approach of this algorithm, however, causes an imbalanced load between single dimensions. In particular, the majority of the traffic traverse to the first dimension and decreases at every following dimension.

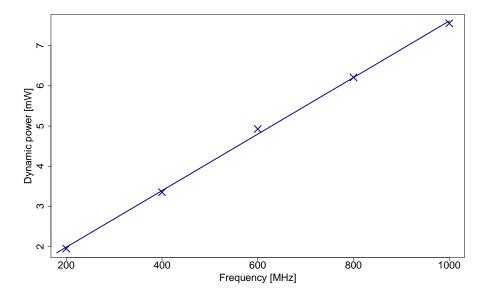

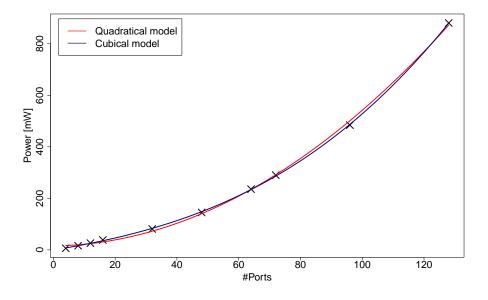

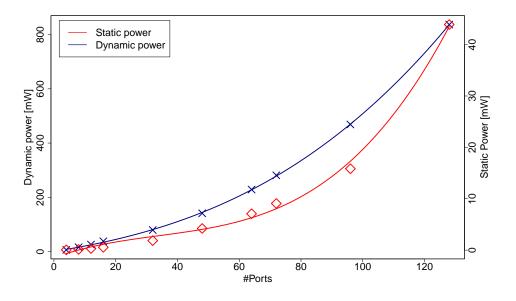

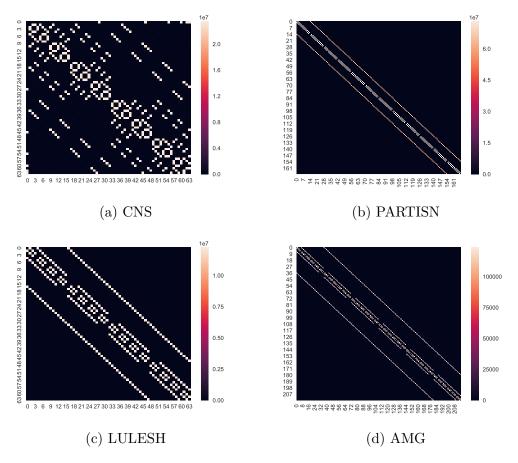

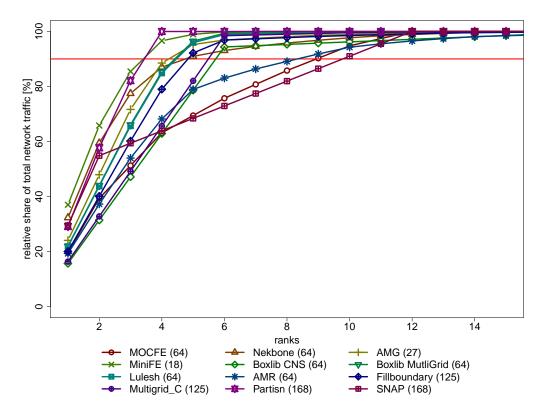

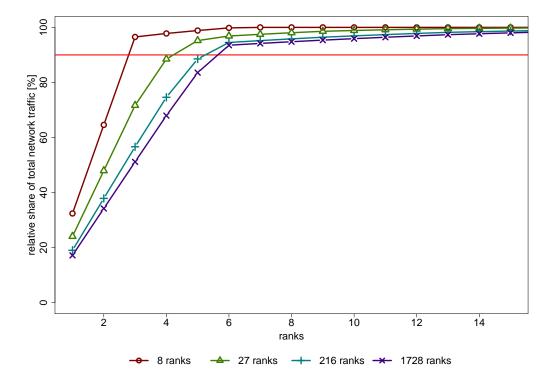

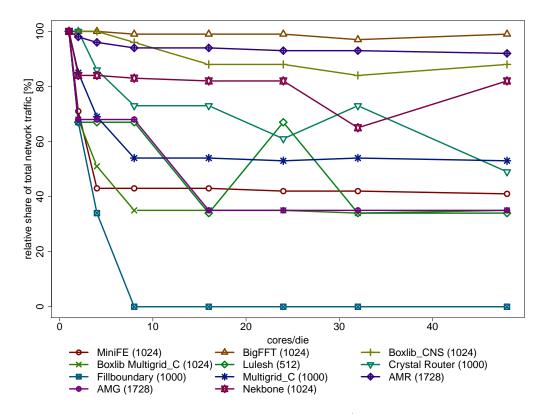

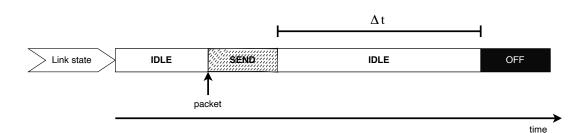

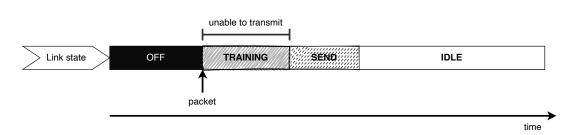

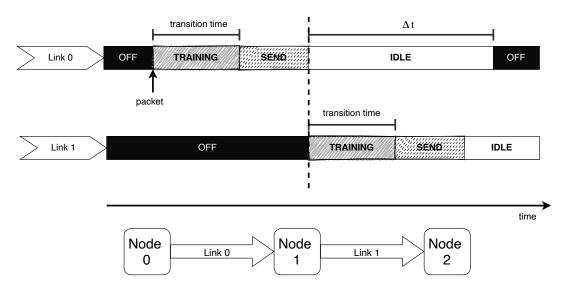

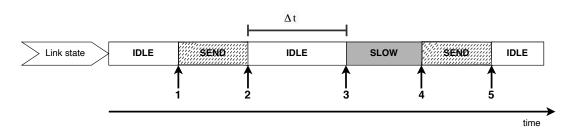

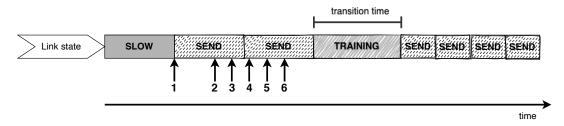

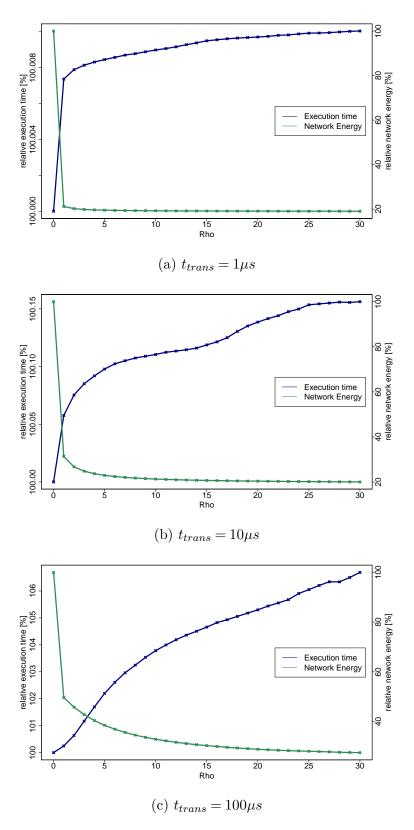

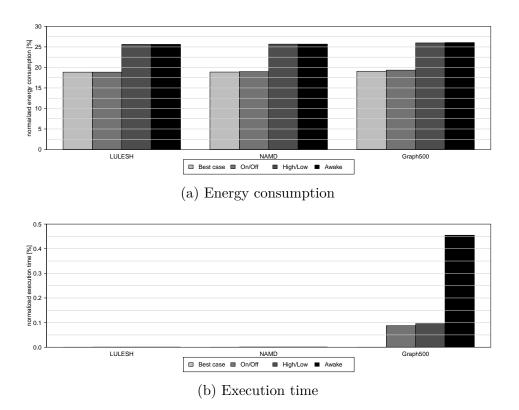

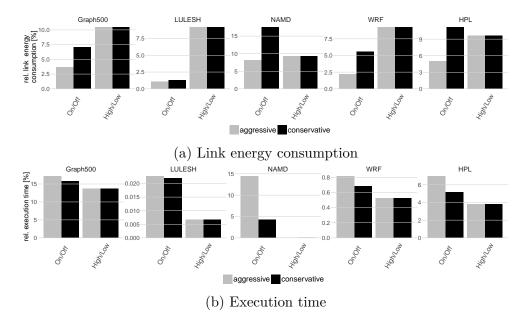

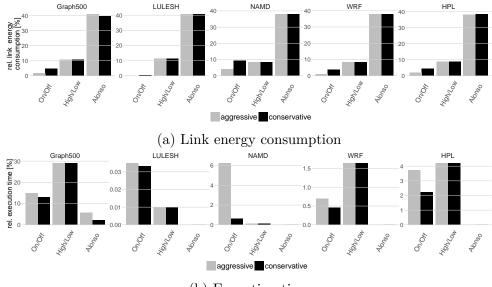

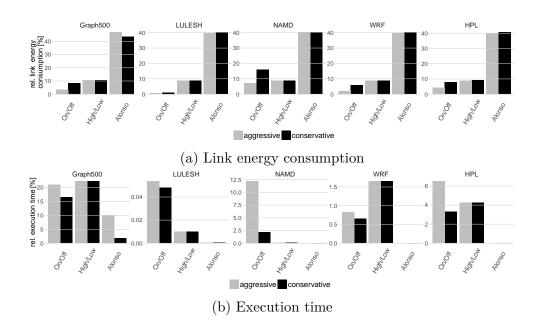

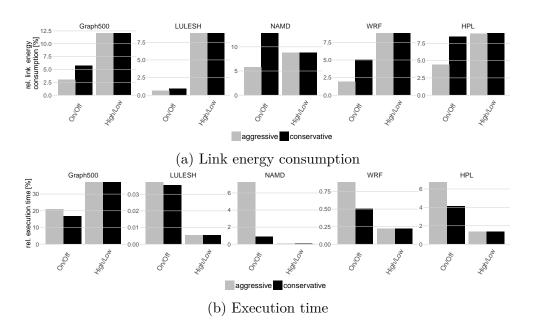

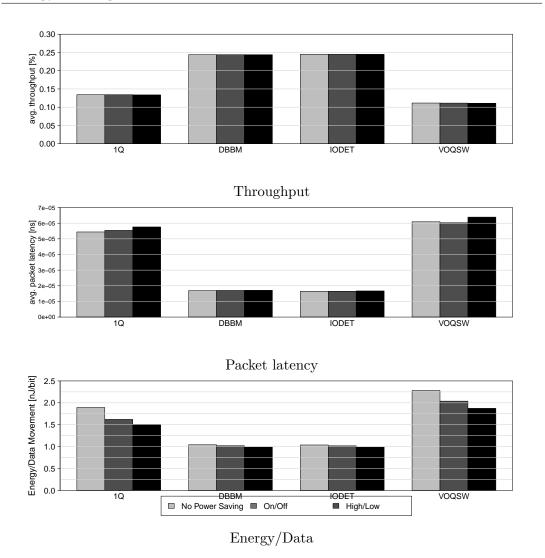

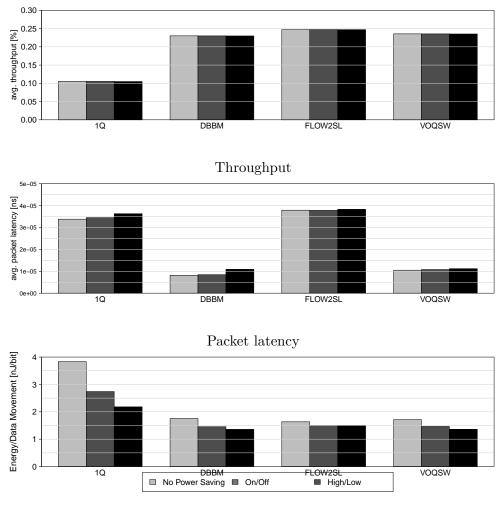

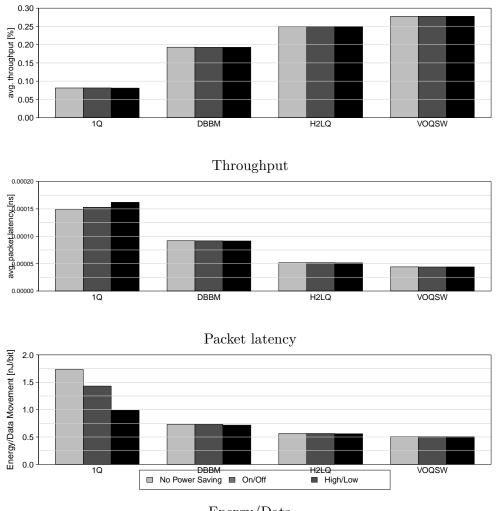

### **Up-Down Routing**