## Dissertation

submitted to the Combined Faculty of Natural Sciences and Mathematics of Heidelberg University, Germany for the degree of **Doctor of Natural Sciences**

Put forward by

## **Christian Mauch**

born in: Stuttgart

Oral examination: 14.12.2021

Operating Accelerated Neuromorphic Hardware – A Scalable and Sustainable Approach

### **Referees:**

Dr. habil. Johannes Schemmel (Heidelberg University) Prof. Dr. Hans-Christian Schultz-Coulon (Heidelberg University)

#### Abstract

Accelerated mixed-signal neuromorphic hardware presents a promising approach to overcome run time and scalability issues of software-based neural network simulations. It accomplishes this by physical emulation of the neuronal dynamics via specialized analog circuitry instead of numerical calculations. However, facilitating the advantage of such highly custom hardware with a similar convenience as conventional simulators poses various challenges. This thesis addresses these in two ways:

First a multi-layered software architecture developed for the second-generation BrainScaleS neuromorphic systems is presented. Well-defined interfaces allow utilization of the hardware in different stages of development with the appropriate level of abstraction. The upper layers provide an interface to efficiently describe neuroscience experiments and handle automated translation of population-based spiking neural network graphs to valid hardware configurations and experiment flow programs. Suitable run time performance and scalability of the software are verified by extensive measurements while usability is demonstrated via an SNN-based Sudoku solver. The second part covers the challenges of supplying novel compute hardware as a research platform to the neuroscience community. A convenient and robust multi-user access is facilitated via customization of the prevalent SLURM resource scheduler to the requirements of neuromorphic experiment workflows. Finally, a monitoring infrastructure vital for system commissioning and experiment reproducibility is established. ii

#### Zusammenfassung

Beschleunigte neuromorphe digital-analoge Hardware ist ein vielversprechender Ansatz zur Überwindung der Laufzeit- und Skalierbarkeitsproblemen von softwarebasierten Simulationen neuronaler Netze. Erreicht wird dies durch die physikalische Emulation der neuronalen Dynamik mittels spezialisierter analoger Schaltungen anstelle von numerischen Berechnungen. Es ist jedoch eine Herausforderung, die Vorteile solcher hochgradig spezialisierter Hardware mit einem ähnlichen Komfort wie bei herkömmlichen Simulatoren zu verbinden. In dieser Arbeit werden diese auf zwei Arten angegangen:

Im ersten Teil wird eine mehrschichtige Softwarearchitektur für die zweite Generation der BrainScaleS neuromorphen Systeme vorgestellt. Gut definierte Schnittstellen ermöglichen die Nutzung der Hardware in verschiedenen Entwicklungsstadien mit der entsprechenden Abstraktionsebene. Die oberen Schichten bieten eine Schnittstelle zur effizienten Beschreibung neurowissenschaftlicher Experimente und zur automatischen Übersetzung populationsbasierter Graphen pulsbasierter neuronaler Netze in valide Hardwarekonfigurationen und Experimentablaufprogramme. Die geeignete Laufzeitleistung und Skalierbarkeit der Software wird durch umfangreiche Messungen verifiziert, während die Benutzerfreundlichkeit anhand eines Sudoku-Lösers auf Basis pulsbasierter Netze demonstriert wird. Der zweite Teil befasst sich mit den Herausforderungen, die mit der Bereitstellung dieser neuartigen Hardware als Forschungsplattform für die neurowissenschaftliche Gemeinschaft verbunden sind. Ein handlicher und robuster Mehrbenutzerzugang wird durch die Anpassung des weit verbreiteten SLURM-Ressourcenmanagers an die Anforderungen neuromorpher Experimentabläufe ermöglicht. Abschließend wird eine Überwachungsinfrastruktur eingerichtet, die für die Inbetriebnahme des Systems und die Reproduzierbarkeit der Experimente unerlässlich ist.

iv

## Contents

| 1 | Intr       | oductio                            | on                                                | 1  |  |  |

|---|------------|------------------------------------|---------------------------------------------------|----|--|--|

| 2 | Background |                                    |                                                   |    |  |  |

|   | 2.1        | Spikin                             | ng Neural Networks                                | 5  |  |  |

|   |            | 2.1.1                              | The Leaky Integrate-and-Fire Model                | 5  |  |  |

|   |            | 2.1.2                              | The Adaptive Exponential Integrate-and-Fire Model | 7  |  |  |

|   |            | 2.1.3                              | Multi-Compartment Neuron Models                   | 7  |  |  |

|   |            | 2.1.4                              | Synaptic Input and Plasticity                     | 7  |  |  |

|   |            | 2.1.5                              | Network Topologies                                | 8  |  |  |

|   | 2.2        | Neuro                              | omorphic Computing Platforms                      | 8  |  |  |

|   |            | 2.2.1                              | Computational Neuroscience Workflow               | 9  |  |  |

|   |            | 2.2.2                              | Neuromorphic Approaches                           | 10 |  |  |

|   |            | 2.2.3                              | BrainScaleS-1                                     | 12 |  |  |

|   |            | 2.2.4                              | BrainScaleS-2                                     | 16 |  |  |

|   | 2.3        | Softwa                             | are Development Concepts                          | 19 |  |  |

| 3 | Neu        | Neuromorphic Software Architecture |                                                   |    |  |  |

|   | 3.1        | Archit                             | tecture                                           | 24 |  |  |

|   |            | 3.1.1                              | Goals and Requirements                            | 24 |  |  |

|   |            | 3.1.2                              | Software Stack Overview                           | 26 |  |  |

|   |            | 3.1.3                              | Prior Work                                        | 29 |  |  |

|   |            | 3.1.4                              | Collaborative Work                                | 30 |  |  |

|   | 3.2        | Comn                               | nunication                                        | 31 |  |  |

|   |            | 3.2.1                              | Connection Interface                              | 31 |  |  |

|   |            | 3.2.2                              | Back-Ends                                         | 32 |  |  |

|   | 3.3        | Hardv                              | vare Abstraction                                  | 33 |  |  |

|   |            | 3.3.1                              | Coordinates                                       | 34 |  |  |

|   |            | 3.3.2                              | Container                                         | 36 |  |  |

|   |            | 3.3.3                              | Runtime Control                                   | 39 |  |  |

|   |            | 3.3.4                              | Hardware Database                                 | 42 |  |  |

|   |            | 3.3.5                              | Performance                                       | 43 |  |  |

#### CONTENTS

|   |               | 3.3.6                  | Example Studies                   | 46  |  |  |  |

|---|---------------|------------------------|-----------------------------------|-----|--|--|--|

|   | 3.4           | Experiment Description |                                   |     |  |  |  |

|   |               | 3.4.1                  | Signal-Flow Graph Description     | 47  |  |  |  |

|   |               | 3.4.2                  | Abstract Network Description      | 51  |  |  |  |

|   | 3.5           | Modeli                 | ing Wrapper                       | 53  |  |  |  |

|   |               | 3.5.1                  | PyNN                              | 53  |  |  |  |

|   |               | 3.5.2                  | PyTorch                           | 57  |  |  |  |

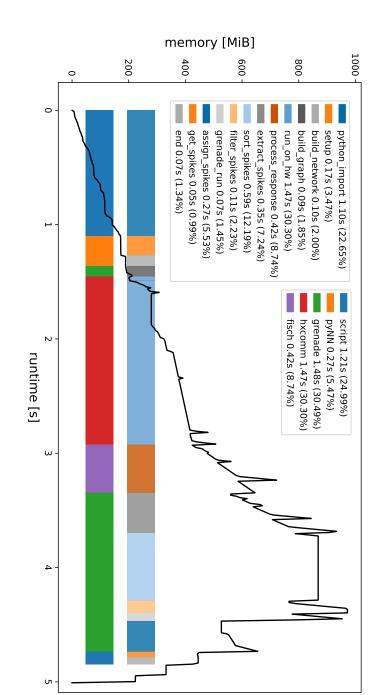

|   | 3.6           | Full Sta               | ack Analysis                      | 58  |  |  |  |

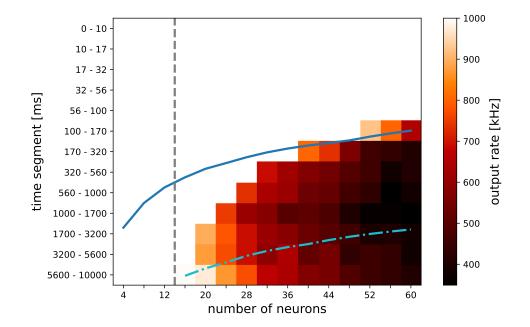

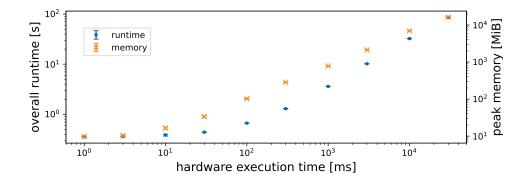

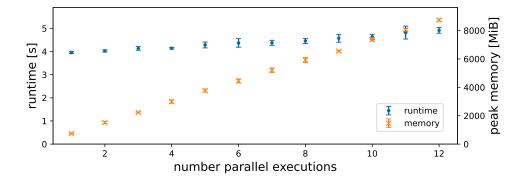

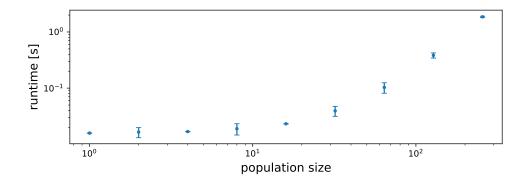

|   |               | 3.6.1                  | Scaling with Run Time             | 58  |  |  |  |

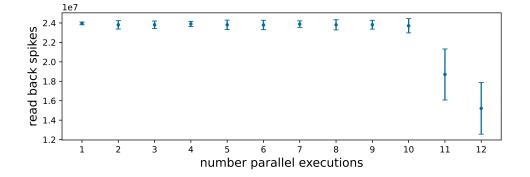

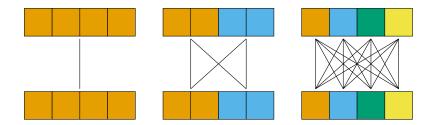

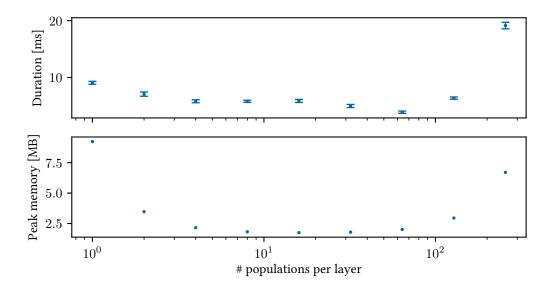

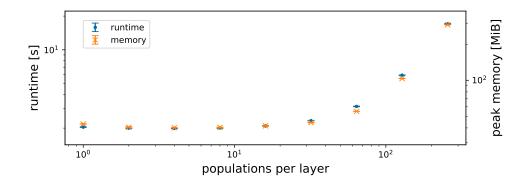

|   |               | 3.6.2                  | Scaling with Network Topology     | 66  |  |  |  |

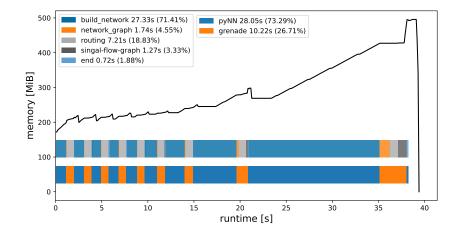

|   |               | 3.6.3                  | Impact on Experiment Workflow     | 70  |  |  |  |

|   | 3.7           | Sudokı                 | u Solver                          | 71  |  |  |  |

|   |               | 3.7.1                  | Experiment Setup                  | 72  |  |  |  |

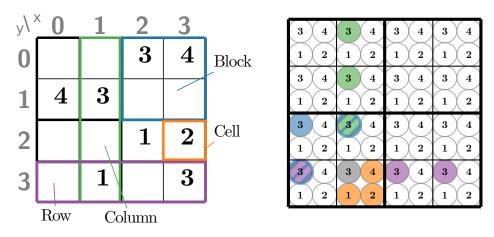

|   |               | 3.7.2                  | Chosen Sudoku Puzzles             | 73  |  |  |  |

|   |               | 3.7.3                  | Network Analysis                  | 73  |  |  |  |

|   |               | 3.7.4                  | Run Time Performance              | 75  |  |  |  |

|   |               | 3.7.5                  | Outlook                           | 77  |  |  |  |

|   |               |                        |                                   |     |  |  |  |

| 4 | Neu           | romorp                 | phic Platform Operation           | 79  |  |  |  |

|   | 4.1           | Resour                 | rce Management                    | 79  |  |  |  |

|   |               | 4.1.1                  | Prelude                           | 80  |  |  |  |

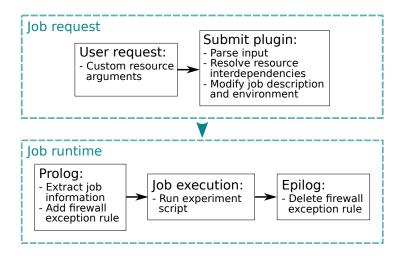

|   |               | 4.1.2                  | Resource Scheduler Configuration  | 83  |  |  |  |

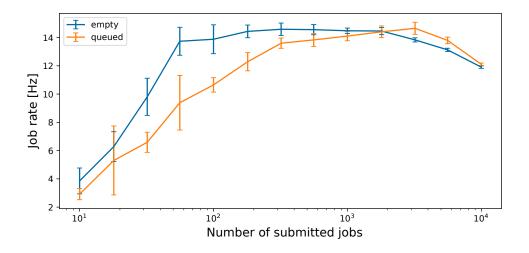

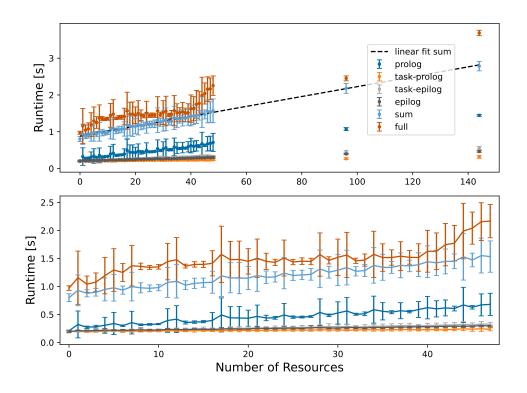

|   |               | 4.1.3                  | Baseline Performance              | 84  |  |  |  |

|   |               | 4.1.4                  | Resource Isolation                | 86  |  |  |  |

|   |               | 4.1.5                  | Native Resource Request API       | 87  |  |  |  |

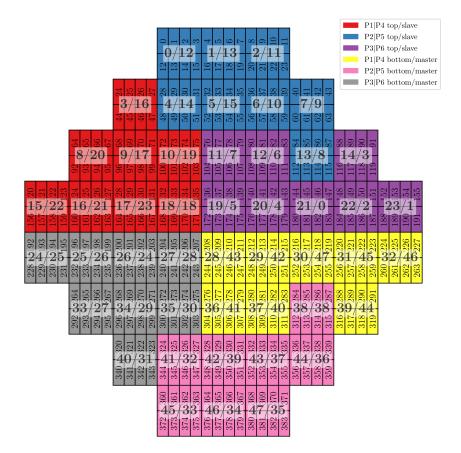

|   |               | 4.1.6                  | Automated Neighbor Initialization | 92  |  |  |  |

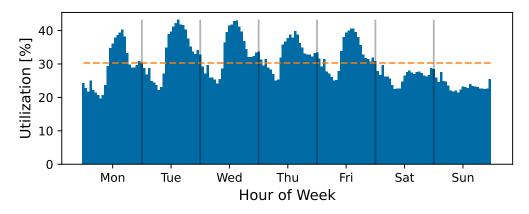

|   |               | 4.1.7                  | Scheduler Utilization Analysis    | 100 |  |  |  |

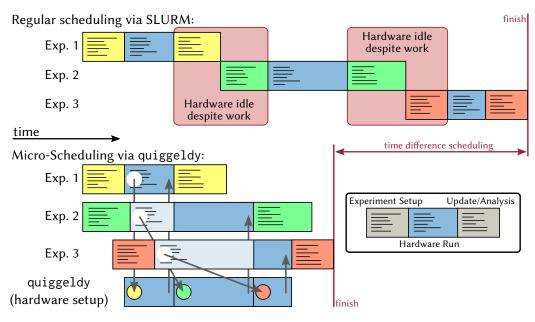

|   |               | 4.1.8                  | Micro Scheduler                   | 106 |  |  |  |

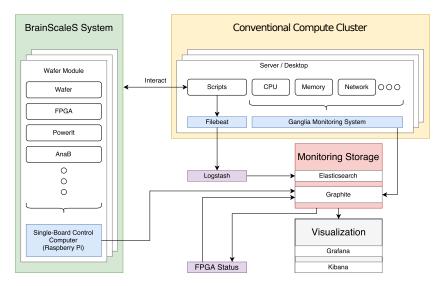

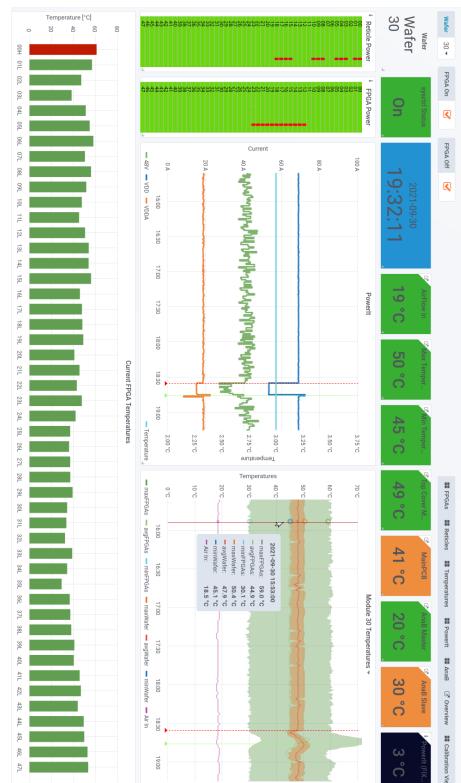

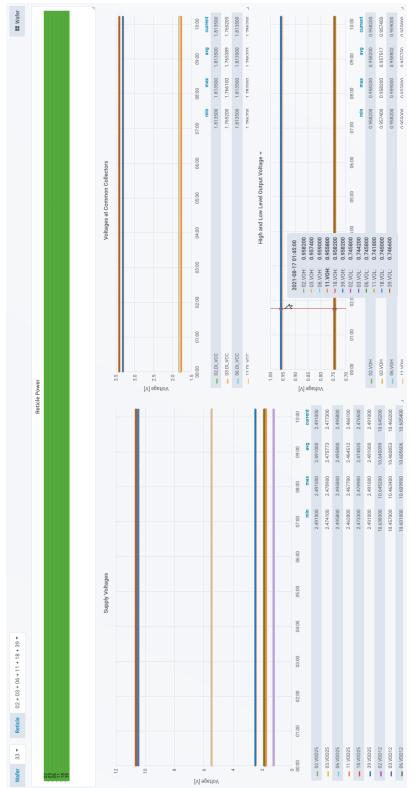

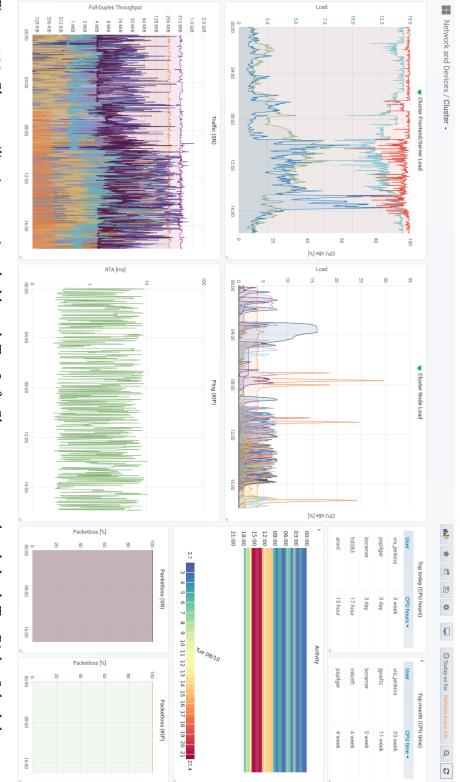

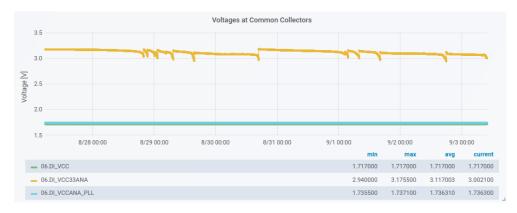

|   | 4.2           | Monito                 | oring and Alerting                | 108 |  |  |  |

|   |               | 4.2.1                  | Aggregation and Storage           | 109 |  |  |  |

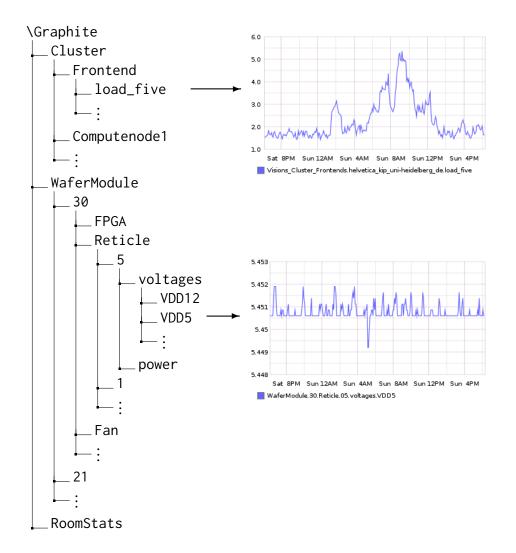

|   |               | 4.2.2                  | Visualization                     | 112 |  |  |  |

|   |               | 4.2.3                  | Alerting                          | 117 |  |  |  |

|   |               | 4.2.4                  | Findings                          | 117 |  |  |  |

|   |               |                        | C C                               |     |  |  |  |

| 5 | Con           | clusion                | and Outlook                       | 119 |  |  |  |

| A | Contributions |                        |                                   |     |  |  |  |

|   | A.1           | Publica                | ations                            | 125 |  |  |  |

|   | A.2           |                        | vision                            | 127 |  |  |  |

|   |               | -                      |                                   |     |  |  |  |

vi

| B | Mea                                           | Measurement Conditions      |     |  |  |  |  |

|---|-----------------------------------------------|-----------------------------|-----|--|--|--|--|

|   | B.1 Software State for Performed Measurements |                             |     |  |  |  |  |

|   |                                               | B.1.1 BrainScaleS-1         | 129 |  |  |  |  |

|   |                                               | B.1.2 BrainScaleS-2         | 129 |  |  |  |  |

|   |                                               | B.1.3 Slurm                 | 130 |  |  |  |  |

|   |                                               | B.1.4 Sudoku Solver         | 130 |  |  |  |  |

|   | B.2                                           | Compute Node Specifications | 132 |  |  |  |  |

| С | Acro                                          | onyms                       | 133 |  |  |  |  |

| D | ) Bibliography                                |                             |     |  |  |  |  |

### vii

CONTENTS

viii

# Chapter 1

## Introduction

The nervous system, and in particular the brain, is the evolutionary result for the need of animals to interact with their environment. It comprises a myriad of interconnected nerve cells also called neurons, from which astonishing cognitive capabilities emerge. The field of computational neuroscience strives to develop models that explain and replicate the functionality of these systems. Spiking Neural Networks (SNNs) are one of the basic models to describe the brains structure and investigate its computational capabilities. The complexity of such models and systems often necessitates numerical simulations. Traditionally these simulations are performed in software on conventional compute architectures [Diesmann et al. 2002; Hines et al. 2003; EPFL et al. 2008]. However, they become compute and time intensive, especially with scaled up network sizes. For example, a human-scale brain simulation of the cerebellum comprising  $6.8\cdot10^{10}$  neurons and  $5.4 \cdot 10^{12}$  synapses was conducted utilizing all 82 944 compute nodes of the K supercomputer [Yamazaki et al. 2021]. One minute of non-functional network activity took over 10 hours of wall-clock simulation time, a slowdown by a factor of about 600. Moreover, the K supercomputer has an average power consumption of about 12 MW [Yamamoto et al. 2014]. Reasons for these huge compute requirements are, on the one hand, that solving the differential equations describing the neuron dynamics is numerically expensive. On the other hand, distribution of the spike events between the hundreds of compute nodes introduces a significant communication overhead [Zenke et al. 2014].

These challenges were met with different approaches, from efficiency improvements in traditional numerics to optimization in event distribution [Pronold et al. 2021a]. Another approach is the development of dedicated hardware to physically emulate neural networks, which is called neuromorphic computing and was first coined by Caver Mead [Mead 1989; Mead 1990]. The term has been applied more broadly in recent years, to any specialized hardware that mimics structure and behavior of neural systems. Various neuromorphic computing devices were developed over the years, from FPGA-based accelerators to full-custom digital or mixed-signal chips [Indiveri et al. 2011; Furber et al. 2012; Hu et al. 2014; Davies et al. 2018].

One such approach, the BrainScaleS (BSS) architecture [Schemmel et al. 2010; Schemmel et al. 2020], is the focus of this thesis. It implements a physical representation of the neuron dynamics in the form of analog circuits, i.e., no numerical computations are performed. However, the distribution of spike events throughout the network is performed via a digital bus system, thereby making it a mixed-signal system. The chosen circuit dimensions allow the neuromorphic substrate to operate with speed-up of  $10^3$  to  $10^5$  compared to real-time. This high acceleration factor enables the investigation of long term neural development experiments previously not possible as biological years could be emulated in mere hours wall-clock time. These advantages however come with trade-offs to generality and precision. Regarding generality, the neuron model and its parameter range are fixed to the chosen design whereas in software simulation these can be chosen arbitrarily. Limited precision is caused by variations in the analog substrate as well as constraints in parameter resolution, mostly only a few bits, compared to floating-point precision in software. Furthermore, the physical emulation of the neuronal dynamics entails a continuous operation, meaning it cannot be halted and continued later on. Therefore, one has to cope with these trade-offs during operation.

Neuromorphic hardware not only provides means to expedite neuroscience research but could usher in new computing paradigms. The ever-increasing thirst of human society for compute power could be quenched due to Moore's law [Moore 1965]. It is an empirical observation that "predicts" a doubling of integration density in microcircuits, or effectively in compute power, every two years. However, over the last decade this evolution has encountered a number of roadblocks [Theis et al. 2017] which lead to the pursue of novel non-von-Neumann architectures [Neumann 1945]. The renascence of Artificial Neuronal Networks (ANNs) in Machine Learning (ML) at the beginning of the 2010s through deep learning [Krizhevsky et al. 2012; LeCun et al. 2015; Tan et al. 2018] is, at least algorithmically, a step in the direction of such a paradigm shift. Various tasks formerly thought of as requiring "human level intelligence" have been solved with this approach [Silver et al. 2016; OpenAI et al. 2019]. Their breakthrough was made possible by performant specialized algorithms for matrix multiplication utilizing Graphics Processing Units (GPUs). However, deep learning with ANNs still has a huge computational cost leading to development to even more specialized hardware like Google's Tensor Processing Unit (TPU) [Jouppi et al. 2017].

Another big role for the success of ANNs in ML was played by various software frameworks like TensorFlow [Abadi et al. 2015] or PyTorch [Paszke et al. 2019a]. They allow researchers to formulate experiments in high-level interfaces which

abstract away the underlying hardware operations. Thus, one can take advantage of GPUs or TPUs without requiring a deep knowledge of the technical background. Likewise, the facilitation of specialized neuromorphic hardware also requires specialized software to fully exploit its advantages [Rhodes et al. 2018; Lin et al. 2018].

The first main goal of this thesis is the design and development of a sophisticated software architecture for the BrainScaleS Generation 2 (BSS-2) neuromorphic hardware system. It aims to support a similar high-level workflow that abstracts away as many system specifics as possible so that researchers can focus on their experts and not on hardware particularities. To this end, several aspects of system operation need to be covered such as handling of communication, abstraction of hardware components, managing runtime control and defining high-level experiment descriptions. All these aspects need to cope with the particular characteristics of the analog hardware. For example, the high acceleration factor and continuous network emulation set high demands on throughput as well as latency. Similarly, scalability and sustainability of the software are important to handle changes in hardware makeup and evolution to large-scale systems. This is especially true in an academic environment where the stay of researchers is shorter than the lifetime of the hard- and software.

The main purpose of the BSS neuromorphic hardware is to facilitate computational neuroscience experiments. To this end, the Electronic Visions(s)<sup>1</sup> group as part of the Human Brain Project [Markram 2012] strives to provide access to theses systems as computing platforms for the scientific community. The second major goal of this thesis is to ensure that conducting science with this platform is robust, convenient and, most notably, reproducible. Typically large scale neuroscience simulations, like most other large scale simulations, are run in super-computing centers also called High Performance Computings (HPCs). There multi-user access to the compute nodes is managed via resource schedulers. Likewise, access to the neuromorphic hardware systems is supported by a resource scheduler customized to the particular characteristics of the hardware. Furthermore, reproducibility and robustness of experiments are facilitated by an extensive monitoring infrastructure.

## **Thesis Outline**

The thesis is structured as follows:

Chapter 2 provides an introductory insight into the most relevant topics of this thesis. First, an introduction to biological spiking neural networks is given in section 2.1. Then, the concept of neuromorphic computing, especially in

<sup>&</sup>lt;sup>1</sup>https://www.kip.uni-heidelberg.de/vision/

the context of computational neurosciences, is discussed further in section 2.2. Subsequently, sections 2.2.3 and 2.2.4 give an overview of the neuromorphic systems covered in this thesis, namely BrainScaleS Generation 1 (BSS-1) and BSS-2. Furthermore, general concepts of software engineering and their relevance to science, in particular the collaborative workflow practiced in the Electronic Vision(s) group, are discussed in section 2.3.

Building on this, chapter 3 presents the developed software framework facilitating utilization of the BSS-2 hardware. It discusses the particular requirements that accelerated neuromorphic hardware and neuroscience experiments have on software design and the resulting decisions regarding the chosen software architecture. A short overview of the architecture is given as an orientation which is subsequently followed up with more detailed explanations in sections 3.2 to 3.5. Chapter 3 is then concluded by demonstrating the viability and usability of the software by extensive performance measurements (section 3.6) and an exemplary neural network experiment (section 3.7).

Chapter 4 discusses the efforts regarding platform operation. First, the customizations to the Simple Linux Utility for Resource Management (Slurm) resource scheduler are described in section 4.1. This includes an analysis of the hardware utilization via scheduler usage statistics. Secondly the extensive monitoring infrastructure is described in section 4.2, which facilitates robust and reproducible platform operations.

Chapter 5 summarizes and discusses the achievements and limitations of the conducted thesis. It is concluded by an outlook regarding future of the systems, in particular their scale-up.

## Chapter 2

## Background

## 2.1 Spiking Neural Networks

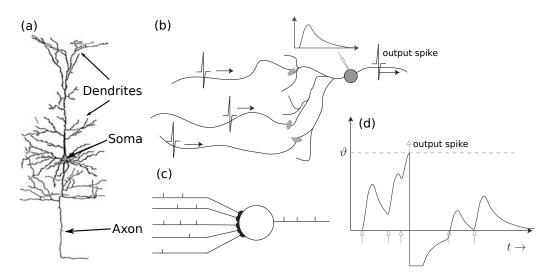

Spiking Neural Networks (SNNs) are used to describe and investigate the dynamics of the neurons and their connections found in the brain. Figure 2.1 illustrates the principle of spiking neurons and their synaptic interconnection, going from biological neurons to a simple abstract model. Action potentials, also called spikes, travel along the axon of the pre-synaptic neurons and induce a change in membrane potential of the post-synaptic neuron. If the change was positive the connection or synapse is called excitatory and in case of negative change it is called inhibitory. The post-synaptic neuron typically has hundreds to thousands of pre-synaptic connections which it accumulates. With enough input events in quick succession it can emit a spike itself.

This of course is a simplification of all the mechanisms present in real biological neurons. There are several models which describe these mechanisms with varying detail, with the Hodgkin–Huxley model [Hodgkin et al. 1952] being one of the most influential. It is relatively complex computational wise as it incorporates the dynamics of sodium and potassium ion-channels to describe the neuron behaviour. However, the full detail of these dynamics are not always necessary when investigating the behaviour of large neural networks. Therefore, in many simulations of large networks simpler neuron models are utilized, two of which are also implemented in the BSS hardware and explained in the following.

### 2.1.1 The Leaky Integrate-and-Fire Model

The LIF neuron model is a simple yet prevalent model as its dynamics are often sufficient to describe functional networks [Stein 1967]. Its dynamics are illustrated

Figure 2.1: Abstraction of the functionality of spiking neurons. (a) Illustration of a biological neuron. (b) Functionality of spike input accumulation. Axons of pre-synaptic neurons are connected to dendrites of the accumulating post-synaptic neuron via synapses (gray ellipses). An incoming spike event leads to rises of the neuron membrane potential, which then decays back to the resting potential (see inlet). If enough excitatory input spikes arrive in quick succession the accumulating neuron fires, i.e., emits a spike itself. (c) Abstract representation of a neuron receiving multiple incoming spike sequences which result in an outgoing spike sequence, thereby performing non-linear information processing. (d) Neuron membrane dynamics triggered by spike input according to the LIF neuron model. With enough input spikes the membrane potential reaches the threshold  $\vartheta$ . This results in quick reset of the membrane potential and emission of an outgoing spike. Modified from Grüning et al. 2014.

in fig. 2.1(d) and described by the following equation.

$$C_{\rm m} \frac{\mathrm{d}V_{\rm m}}{\mathrm{d}t} = -g_{\rm leak}(V_{\rm m} - V_{\rm leak}) + I \tag{2.1}$$

Without any synaptic input I the membrane potential  $V_{\rm m}$  rests at the leakage potential  $V_{\rm leak}$ . An incoming spike event elicits an input current I which charges the membrane capacitance  $C_{\rm m}$ . The resulting potential then decays back to  $V_{\rm leak}$ with the time constant  $\tau_{\rm m} = C_{\rm m}/g_{\rm leak}$ , where  $g_{\rm leak}$  is the leakage conductance. Enough excitatory input events in short succession bring  $V_{\rm m}$  over the threshold  $\vartheta$ , which triggers an outgoing spike. Simultaneously, the membrane potential is brought to the reset potential  $V_{\rm reset}$  for a duration defined by a refractory time constant  $\tau_{\rm ref}$ .

#### 2.1.2 The Adaptive Exponential Integrate-and-Fire Model

The Adaptive Exponential Integrate-and-Fire (AdEx) neuron model [Brette et al. 2005] is an extension to the LIF model that remedies some of its limitations [Markram et al. 2004]. On the one hand, an adaptive term is added that provides the neuron with some capability to remember its past states prior to a reset. On the other hand, an exponential term is added that promotes spiking the closer the membrane potential is already to the threshold. These additional terms allow recreation of complex fire patterns found in biology that the LIF model is not capable of producing. Extending Equation (2.1) with these terms results in:

$$C_{\rm m} \frac{dV_{\rm m}}{dt} = -g_{\rm leak}(V_{\rm m} - V_{\rm leak}) + g_{\rm leak}\Delta_{\rm T} \cdot \exp(\frac{V_{\rm m} - V_{\rm T}}{\Delta_{\rm T}}) - w + I$$

(2.2)

$$\tau_w \frac{\mathrm{d}w}{\mathrm{d}t} = a(V_{\rm m} - V_{\rm leak}) - w \tag{2.3}$$

with w being the adaptation current which is parametrized by a time constant  $\tau_w$  and an adaptation constant a. Once a spike is emitted w is increased by an amount b. Regarding the exponential term,  $\Delta_T$  defines the scaling factor and  $V_T$  the exponential onset.  $V_T$  is typically set closely below the firing threshold  $\vartheta$ . Setting w and  $\Delta_T$  to 0 results again in the LIF equation (eq. (2.1)).

#### 2.1.3 Multi-Compartment Neuron Models

Until now neurons had no spacial structure, i.e, were regarded as points. However, as seen in fig. 2.1a, real biological neurons have a spacial extension that also affects their behaviour. To model such behaviour the concept of compartmental models was introduced [Gerstner et al. 2002] in which multiple point neurons, i.e., the compartments, are interconnected to form larger structures. When using the LIF model to describe the individual compartments, the dynamics of one compartment i are given by the equation:

$$C_i \frac{\mathrm{d}V_i}{\mathrm{d}t} = -g_{\mathrm{mem},i} V_i + \sum_k g_{\mathrm{spine},ik} (V_k - V_i) + I_i \tag{2.4}$$

where  $g_{\text{mem},i}$  describes the conductance to the membrane of the individual compartment and  $g_{\text{spine},ik}$  the conductance between connecting compartments.

#### 2.1.4 Synaptic Input and Plasticity

In the previous eqs. (2.1) and (2.2) the synaptic input was abstracted as an arbitrary input current. Shape, amplitude and duration of this input current vary depending

on the synapse type and its parameters. Two prominent synapse types are Current Based (CUBA) synapses and Conductance Based (COBA) synapses.

The primary parameter that defines the strength of the interconnectivity between two neurons is the synaptic weight. The dynamics and therefore functionality of neural networks greatly depend on these weights. One of the major features of neural networks is their ability to learn which is among others facilitated by modification of this weight. The capability to modify the synaptic input strength is called synaptic plasticity and can occur on differing time scales depending on the type of plasticity model or rule. For example Short-term Plasticity (STP) as the name suggest happens on short time scales, i.e., milliseconds to seconds [Tsodyks et al. 1997]. It reduces or increases the strength of the synaptic input depending on how active the neuron is. This for example can represent the depletion of neurotransmitters in biological neurons. One of the first concepts in synaptic learning, i.e, long-lasting changes to synaptic weights, is the Hebbian theory [Hebb 1949] which is colloquially summarized as "Cells that fire together wire together". More explicitly the synaptic weight is strengthened or weakened depending on the temporal correlation between arrival of pre-synaptic spikes and emission of a post-synaptic spikes. Spike Timing Dependent Plasticity (STDP) [Markram et al. 1997] is a widespread plasticity rules that applies the Hebbian theory.

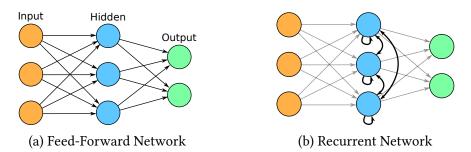

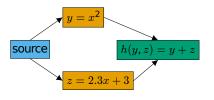

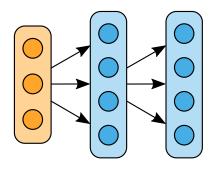

#### 2.1.5 Network Topologies

The structure of neural networks, i.e., the interconnection between neurons, is crucial to their functionality as much as or even more so than the dynamics of the individual neurons. Neural networks are typically illustrated as graphs where the vertices represent neurons and edges the synaptic connections. The most common example of neural network structures is the feed forward network, illustrated in fig. 2.2a. It is a simple example ANN structure to describe deep learning in ML, with a typical application being image classification tasks. The input signals are propagated through one or more hidden layers resulting in a desired activity of the output layer, this typically being only one active neuron. If the network graph is cyclic, i.e., there are connections that feed back activity, it becomes a recurrent network (see fig. 2.2b). This can provide the network with a quasi memory which is for example utilized for time sequence data such as speech.

### 2.2 Neuromorphic Computing Platforms

Modern neuroscience research that aims to decipher the brain is highly interdisciplinary and cost intensive leading to endeavors like the BRAIN Initiative [Insel

Figure 2.2: Common neural network structures. (a) Separate layers are connected in one direction, consequently signals are also propagated and processed only in one direction, hence the name feed-forward. (b) Additional recurrent connections can function as quasi memory, e.g., for time series data such as speech.

et al. 2013] or the Human Brain Project [Markram 2012]. They aim to consolidate efforts by sharing access to large-scale experiment platforms as is similar for large-scale physics projects in astronomy or high energy physics. The following section will give a short overview of neuromorphic computing platforms, in particular the BSS systems. First however, the typical workflow for large-scale neural network research is discussed. Especially the neuroscience software tools like simulator frameworks are introduced as they serve as connection points to the neuromorphic platforms.

### 2.2.1 Computational Neuroscience Workflow

#### **Neuroscience Software**

In computational neuroscience, like in most other computation centric research fields, shared software tools emerge to consolidate efforts. One category of such tools are dedicated spiking neural network simulators, of which a few are shortly presented highlighting their different main applications. The *NEST* simulator [Diesmann et al. 2002] is specialized for large-scale point neuron simulations with focus on scaling on HPC clusters through intrinsic Message Passing Interface (MPI) support. It tries in particular to address the bandwidth and memory bottlenecks of event distribution over compute nodes [Pronold et al. 2021a; Pronold et al. 2021b]. The *NEURON* [Hines et al. 2003] and *Arbor* [Akar et al. 2019] simulators focus on multi compartment models. *Brian2* [Stimberg et al. 2019] focuses flexibility, e.g., with convenient description of custom neuron models. They are several approaches to accelerate these CPU-based simulators with GPU-based back-ends like *GeNN* [Yavuz et al. 2016] or *CARLsim*[Chou et al. 2018].

Kulkarni et al. 2021 benchmarks several of those simulators and reinforces that there is no one-fits-all simulator but most have their particular use case. However,

it is not always clear which simulator is best applicable in a given situation. Common back-end agnostic interfaces were developed to ease switching between simulator frameworks and facilitating comparability. The most prominent being *PyNN* [Davison et al. 2009a] and *Nengo* [Bekolay et al. 2014].

In recent years many ML learning inspired approaches where adopted for SNN, for example, the back-propagation trough time algorithm [Werbos 1990] or LSTM cells [Bellec et al. 2018]. Consequently, ML frameworks like *TensorFlow* [Abadi et al. 2015] or *PyTorch* [Paszke et al. 2019a] found their way into the neuroscience community, with the latter being more prominent [He 2019]. Vice versa, the sparsity in information transport of SNN and therefore potential energy efficiency, peaked interest in the ML community. Resulting from this are SNN extensions to *pytorch* like *BindsNET* which utilize similar population based interfaces of SNN simulators.

#### **High Performance Computing**

Large-scale SNN neuroscience experiments typically demand high computation capabilities, not only for the simulation of the networks themselves but also for preand post-processing, e.g., of large spike data. As high computation capabilities are needed in a plethora of research fields, collaboratively funded High Performance Computing (HPC) clusters like the Jülich Supercomputing Centre are operated. Challenges for construction and operations of super-compute clusters are for example setup of a suitable connection topology of the compute nodes to provide balanced data exchange. To facilitate the distributed compute resources inter process communication is needed, for example handled via MPI. Furthermore, sharing of compute resources for multiple users needs to be ensured, which is solved by resource schedulers.

In typical HPC environments simulations take several hours up to weeks, which consequently leads to long waiting times. Therefore, researchers first prototype their experiment scripts on a small scale allowing for relatively fast feedback-loops. Only then they submit long running jobs to the cluster.

In a similar vein, neuromorphic computing platforms also need to manage shared access for researchers. Chapter 4 presents how this is facilitated for the BSS platform.

#### 2.2.2 Neuromorphic Approaches

The field of neuromorphic computing emerged from the desire to overcome the limitations of conventional simulations of SNNs and the constraints of the von-Neumann architecture. It saw a strong growth in the 2010s, similar to the rise of ANNs in ML, resulting in different technological approaches [Schuman et al.

2017]. They range from FPGAs-based emulations [Wang et al. 2018] to custom digital and mixed-signal ASICs [Indiveri et al. 2011; Benjamin et al. 2014; Merolla et al. 2014] or even new materials like memristors [Hu et al. 2014; Li et al. 2018] and photonics [Feldmann et al. 2019].

As this thesis focuses on the facilitation of neuromorphic computing platforms an overview is given of systems which are already available to the community, including the necessary software support. For a broader overview of neuromorphic devices please refer to Schuman et al. 2017; Thakur et al. 2018; Li et al. 2018; Young et al. 2019.

#### SpiNNaker

The SpiNNaker neuromorphic platform developed at the University of Manchester mainly tackles the issue of spike distribution between computation cores of conventional numerical simulators [Furber et al. 2012]. It does this by interconnecting a multitude of general purpose Advanced RISC Machines (ARM) compute cores with a routing mesh to efficiently handle spike transfer between the cores. Each core is connected to its top, right and diagonally top right neighbor resulting in a two-dimensional torus mesh for the complete network topology. A single SpiNNaker chip utilizes 17 ARM cores where 48 of those chips are combined on large circuit boards which again are interconnected to build up the full system. It thus incorporates over  $10^6$  of these ARM processors which are able to simulate over  $10^9$  neurons with 10 000 synapses each. As the performed computation is general purpose, arbitrary neuron models and plasticity rules are supported. Real-time simulation speed is possible however slowdown occurs depending on the simulated model. Regarding software support, SpiNNaker provides a *PyNN* back-end as a experiment interface [Rhodes et al. 2018].

#### Loihi

The Loihi neuromorphic chip developed by Intel implements specialized fully digital circuits which calculate the neuron dynamics in discrete time steps [Davies et al. 2018]. One Loihi chip contains 128 neuromorphic cores which implement up to 130 000 LIF neurons with 1000 CUBA synapses each. These neurons can be combined to form larger logical neurons. Synaptic plasticity is facilitated by a learning framework which allows to define custom update rules from a set of given functions and observables to operate on. The cores are connected to a 2D bus system allowing arbitrary connections within a chip. However, fan-in and fan-out, i.e., maximum number of connections to other neurons, of these cores is limited, thus neuron placement is constrained and needs to be handled. Each core runs asynchronously within a time step however the spike events between

cores need to be synchronised effectively constraining the overall performance to the slowest core. 768 of those chips are combined in a rack-mount which thus has the capacity to simulate over  $10^8$  neurons [Intel 2020]. Experiment description for the Loihi system is supported via multiple interfaces such as a custom population based Application Programming Interface (API) [Lin et al. 2018] similar to *PyNN*, a *Nengo*<sup>1</sup> back-end and a *Tensorflow* like API [Rueckauer et al. 2021]. Unfortunately the work behind Loihi and conducted research on it is shrouded by non disclosure agreements.

#### BrainScaleS

The BrainScaleS (BSS) neuromorphic hardware developed by the Electronic Vision(s) group at the University of Heidelberg [Schemmel et al. 2010; Schemmel et al. 2020] does not simulate neuron dynamics numerically but emulate them in physical representations of the underling neuron model. Multiple different chip generations where developed of which a short overview is given. The predecessor chip *Spikey* marks the first chip generation developed by the group [Schemmel et al. 2006]. Its main application was as portable single chip system however also a multi chip system was designed [Philipp et al. 2007]. Large-scale networks were then more specifically targeted with the BSS systems. As facilitation of BSS-1 and BSS-2 are central elements of this thesis they are described in more detail in section 2.2.3 and section 2.2.4 respectively.

#### 2.2.3 BrainScaleS-1

The BSS-1 hardware is the first generation of systems developed in the Electronic Vision(s) group with the explicit goal to provide large-scale accelerated SNN emulation. It utilizes wafer-scale integration to implement up to 196 608 AdEx neurons (section 2.1.2) and over 40 million COBA synapses (section 2.1.4) on a single wafer module, illustrated in fig. 2.3a. Each wafer consist of  $8 \times 48 = 384$  so-called High-Input Count Analog Neuronal Network (HICANN) chips that implement 512 neurons each. In contrast to conventional chip manufacturing, single chip dies are not cut out but kept intact to be interconnected via an additional post-processing layer. This post-processing also provides connection pads for, e.g. supply voltages, analog readout or communication. Multiple neuron circuits can be combined, in groups of up to 64, by directly connecting their membranes to form larger neurons with increases synaptic fan-in. It is to note that this functionally does not constitute multi compartment capabilities as described in section 2.1.3. The presented overview of BSS-1 is constrained to information

<sup>&</sup>lt;sup>1</sup>https://www.nengo.ai/nengo-loihi/ 2021-09-16

(a) Silicon Wafer(b) Wafer Module

which is primarily relevant for chapter 4 and as background for BSS-2. A more detailed description of the system is given in Schemmel et al. 2010.

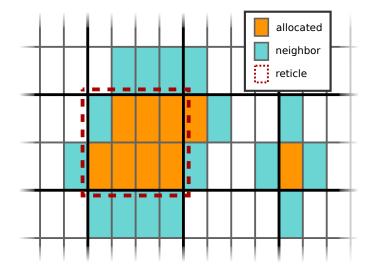

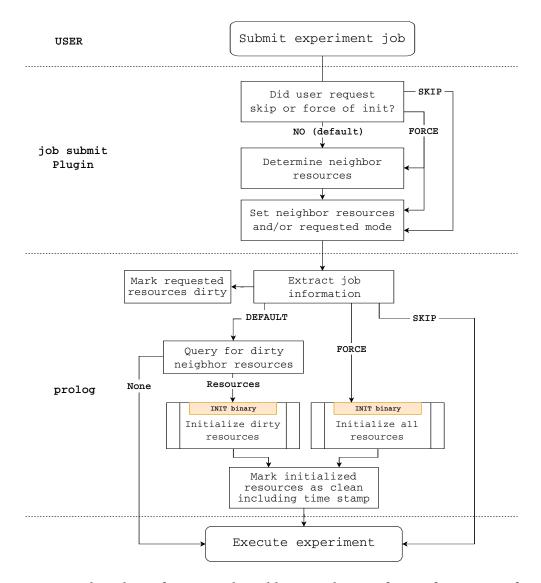

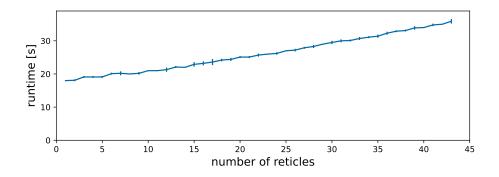

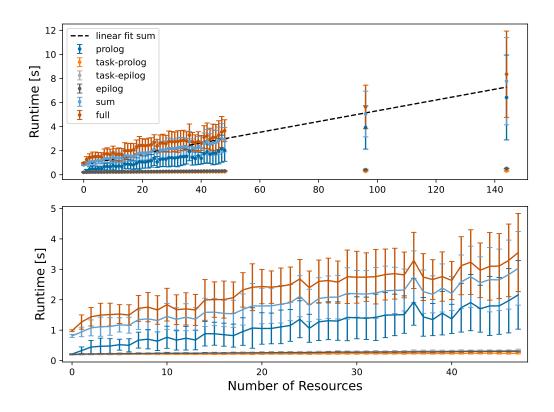

Figure 2.3: BSS-1 neuromorphic wafer module. (a): Post-processed silicon wafer with zoom-in to a single HICANN chip. One wafer comprises 8×48=384 of these chips, where groups of eight HICANNs are called a *reticle* (dashed smaller grid on wafer). Each chip implements 512 neuron circuits with 220 synapses each, where multiple circuities can be combined to form larger neurons. At maximum granularity, 196 608 neurons with 220 synapses each are realized or at minimum granularity 3072 neurons with 14 080 synapses each. Spike transmission is handled via a digital bus system that spans horizontally and vertically over the wafer, with additional connections on- and off-wafer. (b): Exploded view of a wafer module with its various components (dimensions: 50 cm×50 cm×15 cm). A: silicon neuromorphic wafer B: 48 communication FPGAs C: analog readout module D: supply voltage distribution E: main PCB interconnecting all components. Modified from Müller et al. 2020b.

#### Neuron dynamics

The AdEx neuron dynamics are physically time-continuously emulated by analog circuitry implemented in 180 nm Complementary Metal-Oxide-Semiconductor (CMOS) technology. It operates at a speedup of 10<sup>3</sup> to 10<sup>5</sup> compared to biological real-time, which is a consequence of the circuit dimensions deliberately chosen by the hardware designers. All parameters of the implemented AdEx model are configurable, to a certain degree, resulting in the range for the speedup. These configurable parameters need to be provided in analog, i.e., as voltages or currents.

To this end, an analog neuron parameter storage is implemented by floating gates cells, which take a digital value as input. One of their downsides is a high trialto-trial variation, i.e., writing the same digital value multiple times results in varying analog values. This can be somewhat circumvented utilizing the inherent longevity of the written values for consecutive experiments.

#### Spike Transmission

Spike events are transmitted via a digital bus system that stretches over the wafer in a mesh like structure, thus making the BSS-1 architecture mixed-signal. When a neuron spikes it emits a digital packet containing its address. This packet is either directly sent off chip or propagated over the wafer to all target neurons via a pre-determined configurable routing. Similarly, external events can be inserted onto the chip. Events are duplicated at mesh nodes if necessary. When a packet passes a target chip, the synapse array then checks the source address of events and forwards it to the neuron if the addresses match. FPGA-to-chip data transfer is implemented via two communication technologies. On the one hand an Low-Voltage Differential Signaling (LVDS) high-speed link, hereinafter simply called high-speed link. And on the other hand a much slower but robust communication channel via Joint Test Action Group (JTAG). The latter is used to initialize the links or as a fallback when physical link connection is faulty.

#### Auxiliary Hardware

To utilize the neuromorphic wafers a multitude of auxiliary hardware is needed. Figure 2.3b shows an exploded view of the various modular components constituting a BSS-1 wafer module. 48 FPGA boards provide a communication interface for configuration and spike data. Further boards provide readout for analog data, i.e., neuron membrane voltages, and generation of various supply voltages. All components are interconnected via a central PCB.

#### **Platform Setup**

The BSS-1 compute platform constitutes several wafer modules, conventional computes nodes for experiment control and analysis as well as the necessary communication infrastructure. Figure 2.4 shows a photograph of the fully assembled platform.

#### **Fixed Pattern Noise**

One of the major challenges when working with analog circuitry are the inherent parameter variations due to the underlying CMOS manufacturing process. This

Figure 2.4: BSS-1 neuromorphic computing platform. Up to 4 wafer modules are mounted in a rack. Each wafer is connected via  $48 \times 1 \text{ Gbit/s}$  ports. Conventional compute nodes are mounted in middle rack and connected to the setups via 10 Gbit/s switches.

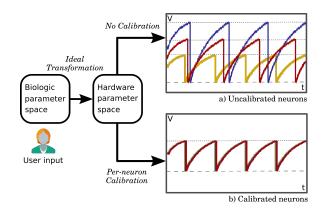

means, setting model parameters for multiple neurons to the same value results in different behaviour. To circumvent this, calibration is applied which finds particular parameter settings so that neurons show similar behaviour. The concept is illustrated in Figure 2.5. This calibration however cannot completely hide all variations due to the limited parameter resolution on hardware. Furthermore, the available parameter range might not be sufficiently large that all neurons can be calibrated for a desired parameter set.

#### **Software Support**

The BSS-1 computing platform provides support for the *PyNN* API via a custom back-end. The underlying software stack manages translation of the abstract experiment description to a valid hardware configuration and executes it. Müller et al. 2020b presents a more detailed view of the BSS-1 software and system operation, which includes work covered in chapter 4. Several of these concepts are also presented in chapter 3 which addresses the design of the BSS-2 software architecture.

Figure 2.5: Principle of neuron parameter calibration. User specifies a parameter sets. Fixed pattern noise inherent to the substrate leads to variations in behaviour without calibration (a). With applied calibration (b), parameters are slightly modified to compensate variations, resulting in similar neuron behaviour. Taken from Müller et al. 2020b.

#### 2.2.4 BrainScaleS-2

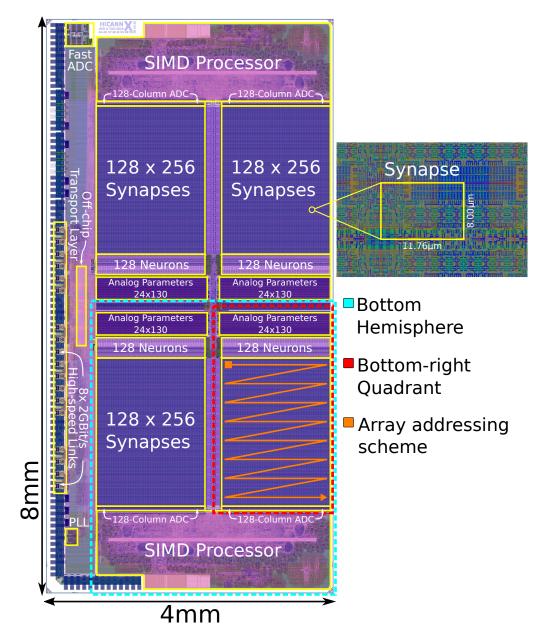

The BSS-2 chip generation represents the shift from 180 nm to 65 nm CMOS technology. A change to the higher resolution manufacturing process enabled several improvements and new features which are explained in the following. Nevertheless, the core principles stay the same, neuron dynamics are physically emulated as analog circuits in a mixed-signal system. As described in section 2.2.2 there were two prototype generations for BSS-2, the HICANN-DLS and the HICANN-X chips. Conceptually both are similar with HICANN-X for the most part being a scaled up version of HICANN-DLS, going from 32 neurons with 32 synapses each to 512 neurons with 256 synapses. Therefore only the most current iteration, the HICANN-X v2 chip, is described, especially its differences to BSS-1. Hereinafter BSS-2 refers to this chip version.

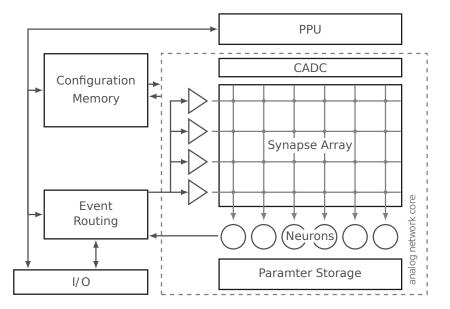

#### **Chip Overview**

The BSS-2 chip implements 512 AdEx neurons with 256 CUBA synapses each. Parameter ranges of the analog circuits were chosen to provide an acceleration of about 10<sup>3</sup> compared to biological real-time. This speedup is one order of magnitude smaller than on BSS-1 which was decided to relax timing constraints.

A simplified schematic of the chip functionality and relevant components is illustrated in fig. 2.6 and is explained in the subsequent sections. It is a stark abstraction of the actual highly symmetrical and repetitive chip layout which can be seen in fig. 2.7 on the left. For more in-depth descriptions refer to Schemmel et al. 2020.

Figure 2.6: Abstract schematic of the BSS-2 chip-layout and functionality. The dotted box on the right annotates the analog network core, i.e., neurons and their synapses. It is surrounded by data-flow and control logic which are connected to the off-chip I/O. Taken from Billaudelle et al. 2020.

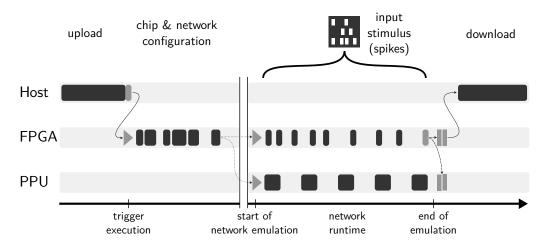

#### I/O

Data in- and output of the chip is handled via a communication FPGA. It handles timed release of configuration data and spike events onto the chip as well as data readout. Multiple spike events can be packed into single communication packets to further utilize the limited bandwidth. This results in spikes taking up 4 bit in compressed and 8 bit in uncompressed case [Karasenko 2020].

#### **Configuration Memory**

Configuration memory represents access to the configuration space of the various on chip components. This configuration covers for example control parameters for the operation points of components but also digital parameters of the network components like synaptic weights.

#### **Analog Parameter Storage**

Storage of the analog neuron circuit parameters was changed from floating gates on BSS-1 to a capacitive memory [Hock 2014]. One of the main advantages of this approach are significantly lower trial-to-trial variations.

#### **Event Routing**

Event routing handles interconnection of neuron spike in- and output as well as on- and off-chip spike sources. Such a routing is needed as full static connectivity becomes infeasible rather quickly. Off-chip sources correspond to either host computer generated events or events from other chips in future multi-chip experiments. On-chip exist a configurable spike generator which generates either regular or Poisson distributed spike sequences. The digital packets representing spike events contain the address of the source neuron. An event packet is then filtered by the components involved in routing according to this address. The challenging part then becomes to find a valid routing under the given constraints (see section 3.4.2).

#### **On-Chip Analog Readout**

Another improvement over BSS-1 are extensive on-chip analog readout capabilities. On the one hand, there is a Analog-to-Digital Converter (ADC) with high temporal resolution which can readout analog parameters of one neuron at a time. As its primary application is the readout of membrane voltages it is called MADC. On the other hand, there are lower resolution ADCs for each neuron/synapse column, hence called CADC. There, a trade-off can be made between temporal resolution and number of concurrent read out columns. They are primarily used to read out correlation capacitors, which are in turn used to facilitated STDP like learning rules (section 2.1.4) via the Plasticity Processing Unit (PPU). Alternatively they can be utilized to readout membrane voltages, albeit with a significantly lower resolution than the MADC.

#### **Plasticity Processing Unit**

The so-called Plasticity Processing Unit (PPU) is a general purpose 32 bit Single Instruction Multiple Data (SIMD) processor integrated on the same substrate with the primary intent to implement arbitrary plasticity rules, hence the name [Friedmann 2013]. It is based on the PowerPC architecture with a custom-built vector unit extension. It provides parallel computation for plasticity relevant observables, namely the synapse array and results from the correlation sensors. Most other observable can be accessed in a serial fashion. Available C and C++ compiler support for the PowerPC instruction set was extended for the vector unit allowing to write efficient code conveniently [Heimbrecht 2017]. This code can then be loaded into the PPU memory for later execution. Due to its general purpose nature it is furthermore utilized, for example, as an experiment controller or a virtual environment for accelerated robotics applications [Wunderlich et al. 2019; Schreiber 2021].

18

#### 2.3. SOFTWARE DEVELOPMENT CONCEPTS

#### **Multi Compartment Capabilities**

Furthermore, the chip provides multi compartment capabilities as described in section 2.1.3. However, these capabilities are not explicitly covered in this thesis. Kaiser et al. 2021 provides further insight into their application.

#### **Analog Multiply-Accumulate**

BSS-2 provides in addition to the SNN operation also the capabilities to perform analog matrix multiplications. This is implemented with the same circuitry but with a different configuration set, that transforms the synapse matrix and neuron circuit into multiply accumulate units. This operation mode can be utilized to perform ANN-based ML task for example demonstrated in Stradmann et al. 2021. However, these capabilities are not applied in this thesis as the main focus lies on spiking operation. Nevertheless, the software architecture described in chapter 3 fully covers this use case.

#### **Platform Setup**

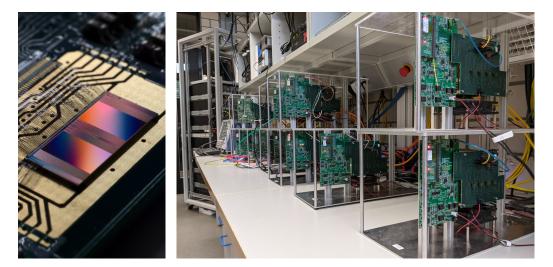

The BSS-2 chips are not yet ready for wafer-scale integration, nevertheless they are already utilized in several studies with smaller scale networks [Billaudelle et al. 2020; Göltz et al. 2021; Czischek et al. 2021]. Figure 2.7 shows photographs of a bonded BSS-2 chip and several single chip setups constitution the current state of the BSS-2 computing platform. They are connected to several compute nodes for experiment control and analysis.

## 2.3 Software Development Concepts

A significant portion of the work conducted in this thesis covers the design and development of software to facilitate neuromorphic research. As the lifetime of the neuromorphic experiment platform, including its software, typically exceeds the stay of individual group members it needs to be sustainable. This necessitates a sufficient level of software quality. However, the impact of software quality and sustainability in science is an open issue [Hatton 2007; Merali 2010], down to the ambiguity of its definition [Venters et al. 2014].

A plain example of bad software quality is wrong code, often simply called bugs. One prominent case was the discovery of bugs in functional Magnetic Resonance Imaging (fMRI) analysis tools which question the validity of a multitude of studies [Eklund et al. 2016]. Another more tragic example were the Therac-25 accidents, where software bugs and insufficient quality-control culminated in administration of radiation overdoses leading to at least 3 fatalities and 3 seriously

Figure 2.7: BSS-2 neuromorphic computing platform. Left: Single bonded HICANN-X chip. Image taken from Müller et al. 2020a. Right: Lab setups each carrying a single neuromorphic chip which is covered by the white plastic cap (top left). Each setup is connected via  $1 \frac{\text{Gbit}}{\text{s}}$  Ethernet which is controlled by a communication FPGA (not visible, on the back). Conventional compute nodes are mounted in a rack and connected to the setups via  $10 \frac{\text{Gbit}}{\text{s}}$  switches (left background).

injured [Leveson et al. 1993]. Neuromorphic systems are not yet in a state to endanger human lives, nevertheless, correctness needs to be a primary goal.

Further aspects to software quality, that are maybe not directly apparent, are, for example, code readability or type safety. To provide better context short introductions to software engineering concepts, tools and best practices is given which are applied in this thesis.

**Testing** Virtually all code contains errors and therefore needs to be tested extensively. There are several approaches to verify desired code behaviour, one being so-called unit testing. Its principle is to test individual contained parts of the code base as it is easier to manage testing for small modules. Conversely, integration testing describes verifying the correct operation of large sections or the entire code base. They are necessary as unit testing does not cover the interactions between units.

**Code Readability** If the task or logic code is easy to grasp it has good readability. This can be facilitated by consistent formatting, e.g., indents, or comments describing the intent of the code. But also avoiding convoluted nesting of condi-

#### 2.3. SOFTWARE DEVELOPMENT CONCEPTS

tionals and loops helps readability. So-called code linter tools can be utilized to automate consistent formatting, reducing load on the developer.

**Code Duplication** Duplicate code, i.e., multiple code segments that fulfill the same task, is undesirable. It introduces unnecessary maintenance-overhead and can make code less readable. Duplicate code segments should therefore be refactored to a single source of truth that is easier to maintain.

**Technical Dept** Technical dept is used to describe the pitfall of choosing a quick but insufficient solution instead of a sustainable but more time-involving solution. The former leads to accumulation of development costs in the future, i.e. dept. Examples are, skipping implementation of tests or insufficient documentation.

**Version Control** Software source code is often a living document which is frequently modified. Version control tools provide a means to track and uniquely identify these changes to code. This is especially valuable when multiple persons work in the same code base.  $Git^2$  is a prominent version control tool and utilized for the software development conducted in the Electronic Vision(s) group.

**Code Review** Code Review describes the practice that changes to code, typically done via version control, are reviewed other developers. It is ubiquitous in open-source and industrial software development as a means to increase software quality [Bird et al. 2013]. The Electronic Vision(s) group practices code review not only for quality assurance but also as a learning method for new group members which, as physics students, typically do not have a pronounced software background. To this end the *gerrit*<sup>3</sup> framework is utilized by the group.

**Continuous Integration** Continuous Integration describes the practice of constantly verifying all changes done to the code base. By ensuring that all changes do not break any tests the software continuously remains in a usable state.

<sup>&</sup>lt;sup>2</sup>https://git-scm.com/ 2021-09-16

<sup>&</sup>lt;sup>3</sup>https://www.gerritcodereview.com/ 2021-09-16

## Chapter 3

## Neuromorphic Software Architecture

The previous chapter introduced the BSS neuromorphic hardware platform in the context of computational neuroscience. Furthermore, some concepts of software engineering were introduced that are relevant for the work in this chapter. The following presents the software framework that enables utilization of the BSS-2 neuromorphic hardware.

First, different challenges and requirements to the software, like the high acceleration factor, are highlighted in section 3.1. The resulting design decisions for the software architecture are discussed. To this end a broad overview of the various layers is given, including a discussion regarding the collaborative nature of the performed software work. A more detailed descriptions of these layers follows in the subsequent sections. Afterwards, performance measurements utilizing all layers are conducted to validate their proper implementation, in section 3.6. In particular, scalability towards multi-chip experiments is investigated. The chapter is concluded by a 4×4 Sudoku solver demonstrating the capabilities of hard- and software.

The concepts presented in the following chapter are explained in the context of the latest BSS-2 chip generations. However, most concepts are applicable not only to the specific substrate but to any hardware system with similar application and constraints. They are the culmination of the design and development efforts of many previous chip generations.

### 3.1 Architecture

#### 3.1.1 Goals and Requirements

Designing and implementing a software framework that enables convenient utilization of novel neuromorphic devices is no small feat. On one side of the spectrum, custom designed hardware needs to be abstracted and controlled. And on the other side high-level experiment frameworks need to be supported which automatically handle the hardware specifics to provide efficient workflows.

To provide better context the different goals and requirements are discussed in the following. First, the various potential users with diverse scientific background are characterized. Then, relevant modes of operation of a neuromorphic system are explained. Finally, the resulting requirements to performance are highlighted.

#### **Target Users**

Computational neuroscience is a highly interdisciplinary research field. As a consequence potential users of a neuromorphic device have varying areas of expertise and expectations regarding its usage. Furthermore, typical workflows during development and commissioning of the systems differs from typical neuroscience experiment-workflow. A hardware developer may require low-level access for fast prototyping and testing of individual components. On the other hand, for high-level neuroscience experiments as much hardware specifics as possible, e.g. topological constraints or fixed pattern noise, should be automatically taken care of. Thus, usage of the systems needs to be supported on different levels of abstraction.

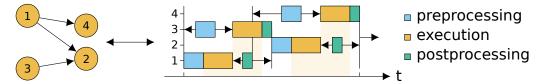

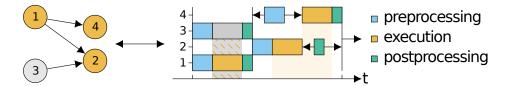

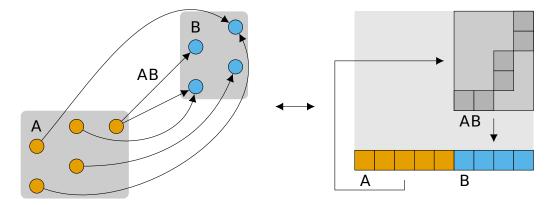

#### **Experiment Usage Modes**

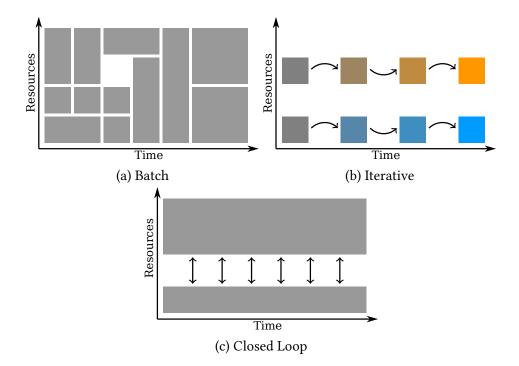

To provide a suitable software framework that utilizes the neuromorphic hardware efficiently one first needs to consider potential modes of operation. We differentiate between three main experiment usage modes, shown in fig. 3.1.

**Batch** In batch mode each experiment can be independently executed. Each individual run fully describes neural network configuration and spike input. Such experiments can be parallelized by consecutive execution on multiple hardware setups to increase throughput. Example experiments of this category are long-running learning experiments utilizing on-chip plasticity capabilities.

**Iterative (in-the-loop)** The iterative or also called in-the-loop usage describes experiments with multiple consecutive hardware runs that depend on the previ-

Figure 3.1: Sketch of different usage modes of neuromorphic hardware. Blocks represent execution instances on the hardware.

ous execution. Compared to batch experiments individual hardware executions are typical shorter lived. On first iteration a neural network with some initial conditions is executed on hardware. Response data, for example spike trains are read back and analyzed. For the following run weights or spike input are modified according to some learning update rule. This is repeated until convergence of some optimization criteria is reached. Examples are learning methods inspired by machine learning approaches like the back propagation algorithm [Rumelhart et al. 1986; Bellec et al. 2019].

**Closed Loop** Closed loop experiments differ compared to batch or iterative insofar as that the experiment controller is time-coupled to the network emulation. This demands tight constraints to communication latency and performance. Typical examples are sensor-motor loops where an agent navigates a virtual environment.

The rest of this chapter will focus on the first two usage modes. An exemplary work that focuses on closed loop operation utilizing the on-chip processor (PPU) can be found in Schreiber 2021.

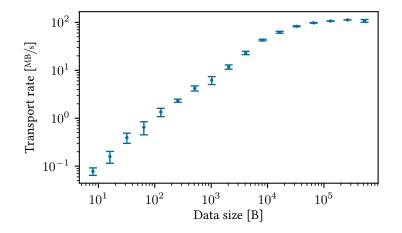

#### Performance

The aforementioned use cases and the nature of analog neuromorphic hardware create certain requirements to a software stack. Especially the high acceleration factor of 10<sup>3</sup> and time-continuous emulation necessitate performant software. As the network emulation cannot be paused data transfer and processing throughput need to be high. Simultaneously low latency is relevant in particular for iterative use cases due to their sequential nature.

## 3.1.2 Software Stack Overview

Taking the requirements explained in the previous section into account an overview of the developed software stack is given. First, the utilized programming languages are and considerations to sustainability are discussed. Afterwards the architecture of different layers is shortly presented. It aims to provide an introduction of the overarching idea with the individual layers being explained in more detail in subsequent sections.

#### **Utilized Programming Languages**

The two programming languages dominantly utilized in the software stack are C++ and Python. The core of most layers is written in C++ due to is high performance and efficiency. Its multi-paradigm support allows for different approaches to the various tasks required to utilize neuromorphic hardware. Due to its strongly-typed nature many issues can already be tackled at compile time further increasing performance and correctness. A further reason for its use is legacy - most already existing code which can be reused is written in C++.

Python is prevalent in the natural sciences due to its flexibility, ease of use and thus relative low learning curve. There are a myriad of Python libraries improving efficiency for scientific workflows, e.g., *numpy*<sup>1</sup>, *pandas*<sup>2</sup> or *matplotlib*<sup>3</sup>. Supporting a Python interface gives access to all these valuable tools. Therefore, virtually all frameworks in neuroscience and machine learning provide a Python API with the BSS-2 software stack being no exception [Abadi et al. 2015; Rhodes et al. 2018; Lin et al. 2018; Paszke et al. 2019a]. To this end the library *genpybind* [Klähn 2020] is employed which provides automated wrapping of C++ via code annotations. Yet, providing support for both languages leads to design constraints for the APIs connecting the various layers.

<sup>&</sup>lt;sup>1</sup>http://numpy.scipy.org 2021-07-20

<sup>&</sup>lt;sup>2</sup>https://pandas.pydata.org/ 2021-07-20

<sup>&</sup>lt;sup>3</sup>https://matplotlib.org/ 2021-07-20

#### 3.1. ARCHITECTURE

#### **Sustainability**

Development of neuromorphic chips is a long-lasting effort over several years, involving changes to various parts of system design. The software therefore needs to be sustainable, e.g., easily adaptable to changes of hardware components. This is achieved by separating the software in multiple independent layers, i.e., splitting it up in modules. Layering is a very common architecture pattern that allows, if executed properly, changes to parts of a code base, e.g. communication, with only minor changes to rest of the code. This requires well-defined APIs for the individual layers which has the additional benefit of providing access to experimenters on different levels of abstraction.

The single-chip prototype setups are planned with multi-chip or even wafer scale operation in mind. This demands bearing parallel execution on multiple chip instance in mind when designing the software architecture. Furthermore, the ability to unit test sections of code should also be taken into account to increase stability and sustainability.

#### **Developed Layers**

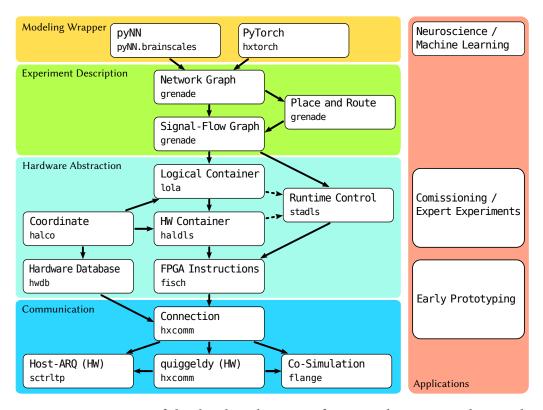

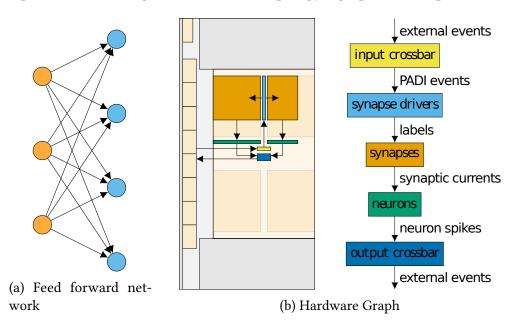

As explained earlier structuring software into well-defined layers is vital in keeping it maintainable and extendable. Figure 3.2 shows a schematic of the developed software architecture and its various applications on different levels.

The stack will be described from a bottom up view as this is the typical development priority when implementing a new chip. The presented schematic is not exhaustive and only shows layers and corresponding repositories directly relevant for experiment control and abstraction of the BSS-2 neuromorphic hardware. All mentioned repositories are open source under the *GNU Lesser General Public License v2* and available at https://github.com/electronicvisions.

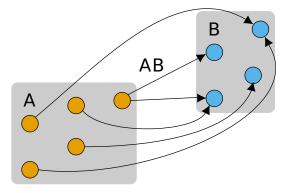

**Communication** The first step to utilize hardware systems, from the software point of view, is the ability to send and receive data. With proper abstraction the underlying transport protocol and technology should be interchangeable. Communication is therefore structured into a common connection interface *hxcomm* that supports various back-ends (cf. section 3.2).

**Hardware Abstraction** The next higher layer category is the *hardware abstraction*, presented in section 3.3. Responsibility of this layer can be compared to device drivers. It provides an abstract structure of the various hardware and chip components and their control flow.

Within this category the lowest layer is the abstraction of control FPGA instructions. Combined with communication this is already sufficient to provide

Figure 3.2: Overview of the developed BSS-2 software architecture and its applications. Left side: Colored boxes in background represent categories of different levels of abstraction. White boxes represent individual layers with their specific repositories names and their dependencies. Right side: Various applications on their corresponding abstraction levels, i.e., which APIs they utilize. See text for detailed description of the individual components.

an interface for fast prototyping in early stages of system development, i.e., manually setting addresses and bits.

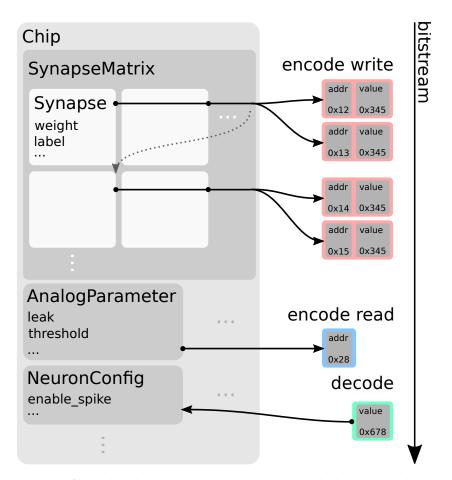

An intuitive structure of the convoluted address space is provided by the *coordinate* layer. It represents each hardware component via custom ranged types that can be converted to other corresponding types.

A structured representation of the configuration space of hardware components is implemented in the *container* layer. These containers also define de- and encoding of their abstract representation to the on-hardware data formatting. A pair of coordinate and container objects then represent the state of a uniquely identifiable hardware component.

The *runtime control* layer provides an interface to describe timed sequenced of read and write instructions of such coordinate-container pairs as well es spike events. These timed sequences, also called playback programs, can then be loaded to and executed on the hardware which sends back record response data. On this level of abstraction most of commissioning and early expert experiments are conducted (section 3.3.6).

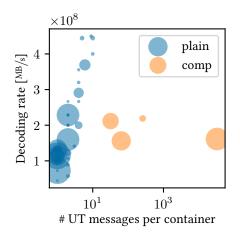

**Experiment Description** To effectively utilize the hardware especially for larger experiments an abstract description of neural network experiments is needed. First a signal-flow graph representing the hardware configuration is defined. It contains a hardware abstraction graph and an experiment flow description interface that utilizes these graphs.

Building on-top of the signal-flow graph description a high-level abstract representation of neural network topology is developed. An automated translation from this high level abstraction to a valid hardware configuration is handled by a place and route interface. Detailed explanation can be found in section 3.4.

**Modeling Wrapper** Various back-end agnostic modeling languages emerged to provide access to various simulators or neuromorphic hardware systems to a wide range of researchers. The BSS-2 software stack comprises wrappers to two of such modeling frameworks, namely *PyNN* [Davison et al. 2009b] and *PyTorch* [Paszke et al. 2019b]. Their goal is to hide as many hardware specifics as possible which is not always expedient to fully exploit all capabilities of specif hardware back-ends. The necessary trade-offs and modifications to the APIs are described in section 3.5.

## 3.1.3 Prior Work

The Electronic Vision(s) group accumulated valuable experience regarding hardware as well as software design over the past two decades. Many aspects in this thesis profit from and built upon the results acquired during development of previous chip generations, especially BSS-1 [Brüderle 2009; Müller 2014; Jeltsch 2014]. A short overview of the lessons learned during their development and operation is given. Likewise, it is discussed how they influenced the earlier explained architecture of the BSS-2 software stack.

Most requirements for the BSS-2 system previously explained in section 3.1.1 also apply to BSS-1. Thus, several principles like layering, coordinates or abstraction of hardware components into container were already utilized. One aspect lacking was a clear separation of communication and hardware abstraction, in particular data de- and encoding. The encoding and decoding functionalities directly performed corresponding read and write command to the hardware which hamper serialization and abstraction of different communication back-ends Therefore a deliberate effort is made to separate the different layers as well as possible.

Another inadequate aspect was that hardware specifics where abstracted away too early in too low levels of the software stack. This complicated debugging in higher levels of the software stack as not the full set of possible hardware features and observables was accessible.

Nevertheless, many concepts and feature proved valuable. For example the Ethernet based custom ARQ-protocol connecting FPGA and hostiles could directly be reused. Also, the coordinate framework could be utilized as is explained later in section 3.3.1.

## 3.1.4 Collaborative Work

Development, commissioning and operation of novel neuromorphic devices is a long-lasting effort of dozens of people. Especially software development is highly collaborative manifesting for example in the code review based workflow practiced by the group (section 2.3). Since the introduction of the first BSS hardware architecture E. Müller leads the software development efforts and provides architectural guidance. Still, almost all detailed software design decisions are discussed and decided as a group. For clarity, an overview of the contributions from the author as well as other main contributors to the software architecture are stated. Major contributions are additionally stated again at the beginning of each section. E. Müller is a common contributor and thus not mentioned below.

#### Section 3.2 Communication

The connection interface was developed by Y. Stradmann, O. Breitwieser and P. Spilger in collaboration with FPGA developers. The author integrated the HostARQ communication back-end, added various stability and enhancement changes including a protocol versioning scheme. The Co-simulation back-end was mainly developed by P. Spilger. The quiggeldy back-end was developed by O. Breitwieser.

#### Section 3.3 Hardware Abstraction

Initial conceptualization and implementation of coordinates, container and runtime control were performed by the author, J. Klähn and D. Stöckel for the HICANN-DLS chip. The initial implementation for this chip was finalized by P. Spilger. Additional extensions and further improvements for the full-size HICANN-X chip were performed by the author and P. Spilger.

#### **Section 3.4 Experiment Description**

Conceptualization and implementation was done by P. Spilger during his master thesis [Spilger 2021] which the author co-supervised. The

author contributed by validation work and performance analysis presented in this thesis.

#### Section 3.5 Modeling Wrapper

The PyNN back-end was established by Milena Czierlinski during her bachelor thesis [Czierlinski 2020] which the author co-supervised. The author subsequently refactored, improved the implementation and added various features including calibration injection, manual neuron placement or quiggeldy micro-scheduler support. P. Spilger and the author integrated the experiment description layer which was validated in this thesis.

# 3.2 Communication

Communication describes the ability to exchange data between a host machine and an instance of neuromorphic hardware be it real or simulated. It represents the lowest level of the software stack and specifics of the implemented communication protocol should be irrelevant to upper layers. Communication layer is therefore split into a connection API and the various abstracted away back ends.

## 3.2.1 Connection Interface

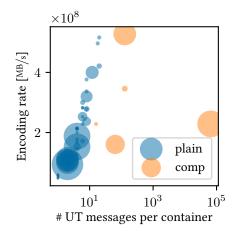

The basic instructions a communication interface needs to provide are sending and receiving of data. Execution and receiving of data to and from the chip is managed by the controlling FPGA in a chunk like fashion, which is explained in more detail in section 3.3.3. Hence, the interface is designed to take one or multiple messages, i.e. a vector, to be sent and returns a vector of response data and potential run time statistics like connection stability and errors. Furthermore, the interface is typed to support differentiation of various FPGA-to-hardware transport protocols like JTAG [IEEE 2001], Serial Peripheral Interface (SPI) or *omnibus* [Friedmann 2015] which are represented by so called UT-messages [Karasenko 2020]. Multiple on chip transport protocols are supported as they have vastly different trade-offs between throughput and stability. These protocols should not be confused with the different possible host-to-FPGA communication protocols implemented by the back-ends explained in following sections.

Another useful feature of this layer is the ability to choose a desired communication back-end at runtime either explicitly in code or through environment variables. This allows fast and easy switching between different back-ends, e.g., during testing on different setups without changing or recompiling code. Furthermore, extension to other potential communication back-ends, e.g., PCI-Express, is properly encapsulated.

## 3.2.2 Back-Ends

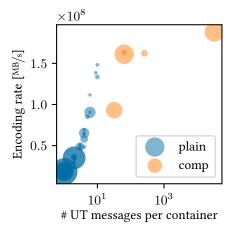

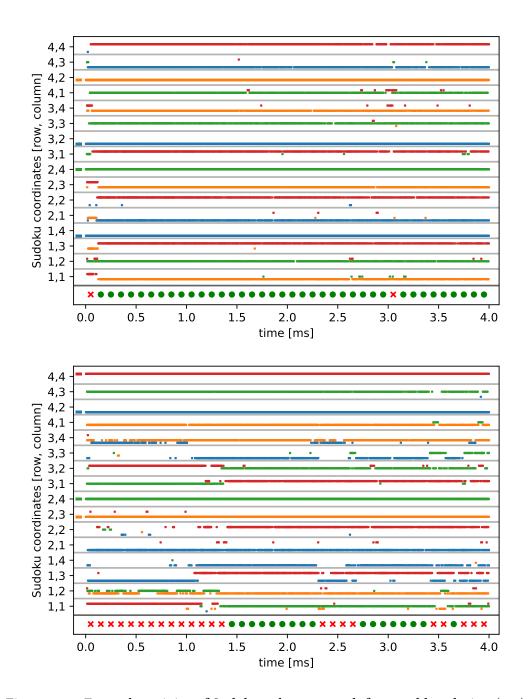

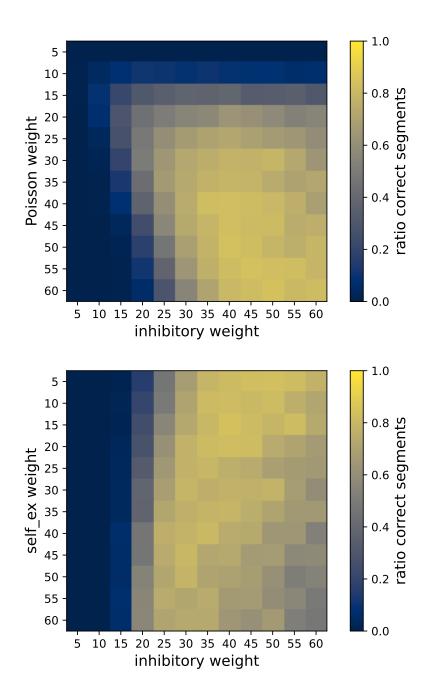

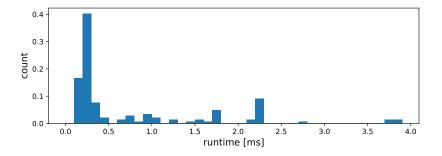

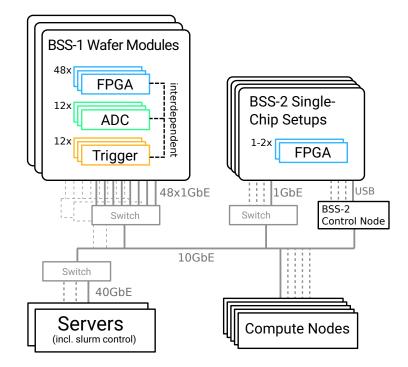

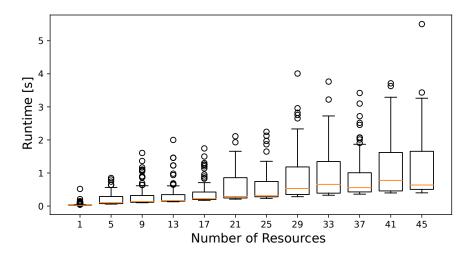

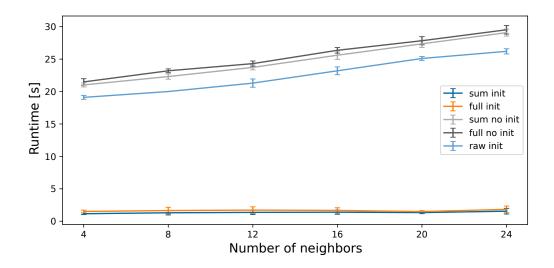

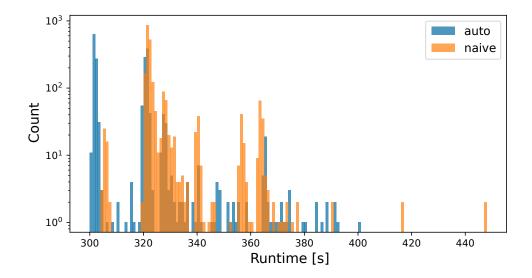

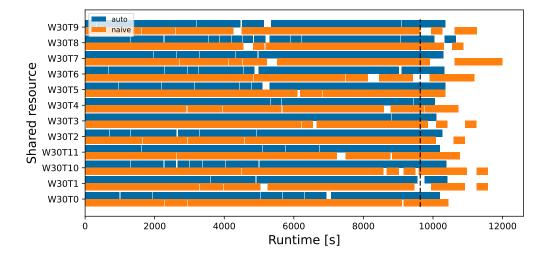

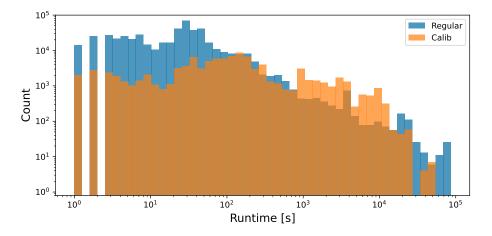

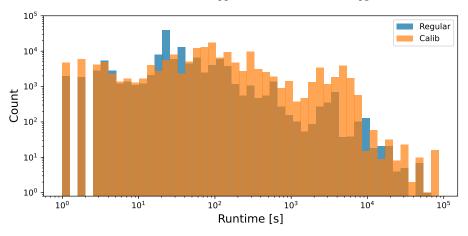

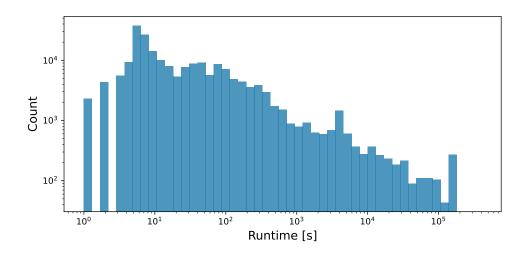

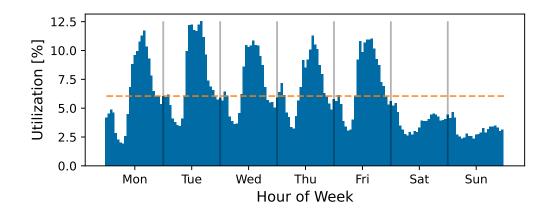

#### **Host-ARQ**