# Dissertation submitted to the Combined Faculty of Mathematics, Engineering and Natural Sciences of Heidelberg University, Germany for the degree of Doctor of Natural Sciences

Put forward by Lorenzo Sanfilippo born in: Desio, Italy

Oral examination: 29.10.2025

Referees: Prof. Dr. Hans-Christian Schultz-Coulon

Prof. Dr. Peter Fischer

# Abstract

The High-Luminosity LHC (HL-LHC) at CERN will significantly increase the collision rate at CERN, presenting major challenges for detector operation, particle reconstruction, triggering and analysis. This thesis addresses the critical role of high-precision 40 MHz timing distribution in the ATLAS experiment, focusing on the development, implementation, and validation of the Local Trigger Interface (LTI) module—a key component of the Phase-2 Trigger and Data Acquisition (TDAQ) system upgrade.

We detail the architecture and operation of the LTI module, including its FPGA-based design, optical and electrical I/O interfaces, clocking system, and integration with ATLAS subsystems. Extensive studies were conducted to evaluate phase stability and mitigate timing uncertainties introduced by temperature variations, transceiver resets, and hardware-induced jitter. Using tools such as Digital Dual Mixer Time Difference (DDMTD) and Transmitter Phase Interpolator (TxPI), we demonstrate picosecond-level timing resolution under realistic operating conditions.

In addition to component-level validation under laboratory conditions, the LTI module was tested in integration setups with the ATLAS Liquid Argon Calorimeter and High-Granularity Timing Detector. Our results confirm the LTI's capability to provide deterministic, low-jitter timing across large-scale distributed systems such as the ATLAS detector. This work supports the broader effort to enable accurate event reconstruction and reliable triggering in the HL-LHC era.

#### Zusammenfassung

Der High-Luminosity LHC (HL-LHC) am CERN wird die Kollisionsrate drastisch erhöhen und stellt damit erhebliche Anforderungen an den Detektorbetrieb, die Teilchenrekonstruktion, das Triggersystem und die Analyse. Diese Doktorarbeit befasst sich mit der entscheidenden Rolle der hochpräzisen Verteilung des 40 MHz-Taktes im ATLAS-Experiment, mit Fokus auf die Entwicklung, Implementierung und Validierung des Local Trigger Interface (LTI) Moduls - einer zentralen Komponente des Phase-2 Upgrades des Trigger- und Datenerfassungssystems (TDAQ).

Die Architektur und Funktionsweise des LTI-Moduls werden im Detail beschrieben,

einschließlich des FPGA-basierten Designs, der optischen und elektrischen Schnittstellen, des Taktungssystems, sowie der Integration mit den ATLAS-Subdetektoren. Zur Bewertung der Phasenstabilität und zur Minderung von Timing-Unsicherheiten, die durch Temperaturänderungen, Transceiver-Resets und Hardware-Jitter verursacht werden, wurden umfangreiche Studien durchgeführt. Mit Werkzeugen wie der Digital Dual Mixer Time Difference (DDMTD) und dem Transmitter Phase Interpolator (TxPI) wird eine Zeitauflösung im Pikosekundenbereich unter realistischen Betriebsbedingungen demonstriert.

Neben der Validierung auf Komponentenebene in Laborumgebung wurde das LTI-Module auch in Integrationsumgebungen mit dem ATLAS-Flüssigargon-Kalorimeter und dem High-Granularity Timing Detector getestet. Die Ergebnisse bestätigen die Fähigkeit des LTI-Moduls, deterministischen und jitterarmen Takt in einem großen und verteilten System wie dem ATLAS-Detektor bereitzustellen. Diese Arbeit leistet einen wichtigen Beitrag zur präzisen Ereignisrekonstruktion und zu einem zuverlässigen Betrieb des Triggersystems am HL-LHC.

# Contents

| $\mathbf{A}$ | bstra        | ct     |                                                         | iii |

|--------------|--------------|--------|---------------------------------------------------------|-----|

| 1            | Intr         | oducti | ion                                                     | 1   |

|              | 1.1          | High-I | Luminosity LHC                                          | 7   |

|              | 1.2          | Autho  | r's Contributions                                       | 8   |

| 2            | The          | ATLA   | AS experiment                                           | 11  |

|              | 2.1          | The A  | TLAS detector                                           | 11  |

|              |              | 2.1.1  | Coordinate system                                       | 13  |

|              |              | 2.1.2  | Magnets system                                          | 14  |

|              |              | 2.1.3  | Inner Detector                                          | 15  |

|              |              | 2.1.4  | Calorimeter System                                      | 17  |

|              |              | 2.1.5  | Muon Spectrometer                                       | 20  |

|              |              | 2.1.6  | Specialized forward detectors                           | 22  |

|              | 2.2          | The A  | TLAS Trigger and Data Acquisition system                | 24  |

|              |              | 2.2.1  | L1Calo Trigger                                          | 26  |

|              |              | 2.2.2  | L1Muon Trigger                                          | 27  |

|              |              | 2.2.3  | L1 Topological Processor                                | 29  |

|              |              | 2.2.4  | Muon-to-Central Trigger Processor                       | 30  |

|              |              | 2.2.5  | Central Trigger Processor                               | 31  |

|              |              | 2.2.6  | Beam pickup based timing system                         | 37  |

|              |              | 2.2.7  | Trigger, Timing and Control System                      | 38  |

|              |              | 2.2.8  | Readout System                                          | 39  |

|              |              | 2.2.9  | High-Level Trigger (HLT)                                | 40  |

|              |              | 2.2.10 | Data Acquisition (DAQ)                                  | 41  |

|              |              | 2.2.11 | TDAQ Software Framework                                 | 41  |

| 3            | $Th\epsilon$ | ATLA   | AS Phase-2 upgrades                                     | 45  |

|              | 3.1          | Overv  | iew of the ATLAS Phase-2 upgrade                        | 45  |

|              |              | 3.1.1  | Physics-driven requirements for the Phase-2 TDAQ system | 48  |

|   |     | 3.1.2 | Limitations of the Phase-1 TDAQ system      |

|---|-----|-------|---------------------------------------------|

|   | 3.2 | The P | hase-2 TDAQ System                          |

|   | 3.3 | Hardw | vare trigger                                |

|   |     | 3.3.1 | Level-0 muon trigger                        |

|   |     | 3.3.2 | Level-0 calorimeter trigger                 |

|   |     | 3.3.3 | Global Trigger Processor                    |

|   |     | 3.3.4 | Muon-to-Central Trigger Processor Interface |

|   |     | 3.3.5 | Central Trigger Processor                   |

|   | 3.4 | Reado | ut and event processing                     |

|   |     | 3.4.1 | Front-End Link eXchange readout system      |

|   |     | 3.4.2 | Data handlers and event routing             |

|   |     | 3.4.3 | Dataflow system                             |

|   |     | 3.4.4 | Event filter and final selection            |

| 1 | The | Logol | Trigger Interface 59                        |

| 4 | 4.1 |       |                                             |

|   | 4.1 |       | •                                           |

|   | 4.2 |       | r and Timing Control signals                |

|   | 4.4 |       | ioning and LTI operation modes              |

|   | 4.4 |       | ardware architecture                        |

|   | 4.0 | 4.5.1 |                                             |

|   |     | 4.5.1 | 1                                           |

|   |     | 4.5.2 | System-on-Module (SoM)                      |

|   |     | 4.5.4 | Clocking system                             |

|   |     | 4.5.4 | Memory                                      |

|   |     | 4.5.6 | Power and cooling                           |

|   |     | 4.5.7 | Modularity and monitoring                   |

|   | 4.6 |       | ation in the TTC distribution               |

|   | 4.7 | _     | ation with the TDAQ system                  |

|   | 1.1 | 4.7.1 | Modular software architecture               |

|   |     | 4.7.2 | Configuration abstraction and reuse         |

|   |     | 4.7.3 | LTI Monitoring Integration                  |

|   | 4.8 |       | ostic, monitoring and control               |

|   | 1.0 | 4.8.1 | Runtime monitoring and status reporting     |

|   |     | 4.8.2 | Board-level control and reset handling      |

|   |     | 4.8.3 | Environmental monitoring and protection     |

|   |     | 4.8.4 | Debugging and traceability                  |

|   | 4.9 |       | phase monitoring and control                |

|   |     |       |                                             |

## CONTENTS

|   |      | 4.9.1   | Digital Dual Mixer Time Difference                            |  |            | 74  |

|---|------|---------|---------------------------------------------------------------|--|------------|-----|

|   |      | 4.9.2   | Transmitter phase interpolator                                |  |            | 76  |

|   | 4.10 | Transc  | eiver operation and link initialization                       |  |            | 77  |

|   |      | 4.10.1  | Conventions for high-speed serial links                       |  |            | 77  |

|   |      | 4.10.2  | Transceiver architecture and serial communication             |  |            | 78  |

|   |      | 4.10.3  | Link bring-up and synchronization                             |  | . <b>.</b> | 78  |

| 5 | Clo  | ck pha  | se stability studies                                          |  |            | 81  |

|   | 5.1  | Experi  | imental setup and instrumentation                             |  | . <b>.</b> | 82  |

|   |      | 5.1.1   | LTI hardware platforms                                        |  | . <b>.</b> | 82  |

|   |      | 5.1.2   | LTI boards configuration                                      |  | . <b>.</b> | 84  |

|   |      | 5.1.3   | Phase measurement instrumentation                             |  | . <b>.</b> | 85  |

|   |      | 5.1.4   | Temperature control                                           |  |            | 87  |

|   |      | 5.1.5   | Software and control architecture                             |  | . <b>.</b> | 90  |

|   |      | 5.1.6   | Test scenarios                                                |  |            | 90  |

|   | 5.2  | Opera   | tional temperature analysis from ATLAS 2024 data              |  | . <b>.</b> | 91  |

|   | 5.3  | Charac  | cterization of timing tools                                   |  | . <b>.</b> | 94  |

|   |      | 5.3.1   | Measurement duration and dependence on averaging depth .      |  | . <b>.</b> | 95  |

|   |      | 5.3.2   | Deglitch threshold selection                                  |  | . <b>.</b> | 96  |

|   |      | 5.3.3   | DDMTD resolution                                              |  | . <b>.</b> | 97  |

|   |      | 5.3.4   | TxPI resolution characterization                              |  | . <b>.</b> | 98  |

|   | 5.4  | Phase   | determinism after transceiver reset                           |  |            | 99  |

|   |      | 5.4.1   | GTH Transceivers                                              |  | . <b>.</b> | 100 |

|   |      | 5.4.2   | GTY transceivers                                              |  |            | 101 |

|   | 5.5  | Tempe   | erature-induced phase drifts with controlled thermal sweeps . |  |            | 102 |

|   | 5.6  | Mitiga  | tion strategies for phase indeterminism and phase drifts      |  |            | 103 |

|   |      | 5.6.1   | Rx-fanout reset procedure                                     |  |            | 105 |

|   |      | 5.6.2   | Clock fiber                                                   |  | . <b>.</b> | 105 |

|   |      | 5.6.3   | Compensation algorithm                                        |  | . <b>.</b> | 107 |

|   | 5.7  | Integra | ation tests                                                   |  |            | 112 |

|   |      | 5.7.1   | Liquid Argon calorimeter                                      |  |            | 112 |

|   |      | 5.7.2   | High-Granularity Timing Detector                              |  |            | 113 |

| 6 | Ope  | ration  | al strategies and guidelines for the LTI software             |  |            | 119 |

|   | 6.1  | Link b  | oring-up and board configuration                              |  |            | 120 |

|   | 6.2  | Start o | of monitoring and compensation logic                          |  |            | 121 |

|   | 6.3  |         | ic monitoring and compensation loop                           |  |            |     |

|   | 6.4  |         | f run and transition to idle                                  |  |            |     |

|   | 6.5  | Error   | handling and degraded operation                               |  |            | 123 |

| $\alpha$ | $\sim$ | V. | $\Gamma$ | $\Box$ | , n | V.         | $\Gamma$ | $\Gamma_{\mathcal{S}}$ | ١ |

|----------|--------|----|----------|--------|-----|------------|----------|------------------------|---|

| C        | ( )    | 1  |          |        | Η,  | <b>ا</b> ا |          |                        | ١ |

| 7 | Conclusions & outlook | 127   |

|---|-----------------------|-------|

|   | Acknowledgements      | . 129 |

# List of Figures

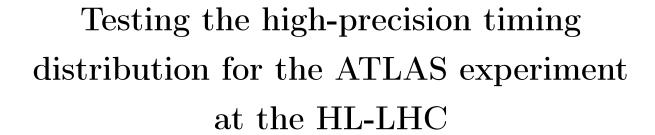

| 1.1  | CERN's accelerator complex [3]                                                     | 2  |

|------|------------------------------------------------------------------------------------|----|

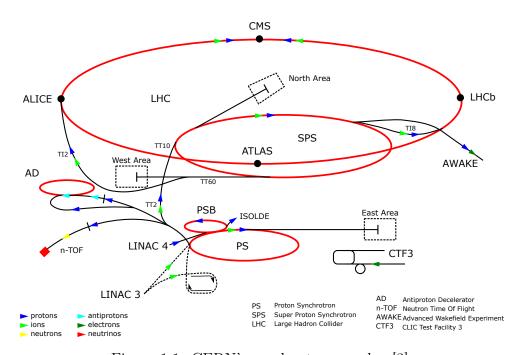

| 1.2  | TTC backbone distribution (highlighted in magenta). Starting from the              |    |

|      | LHC RF at P4, passing through the CCC, and to the main experiments.                |    |

|      | Only the CMS experiment at P5 receives timing signals directly from P4             | 4  |

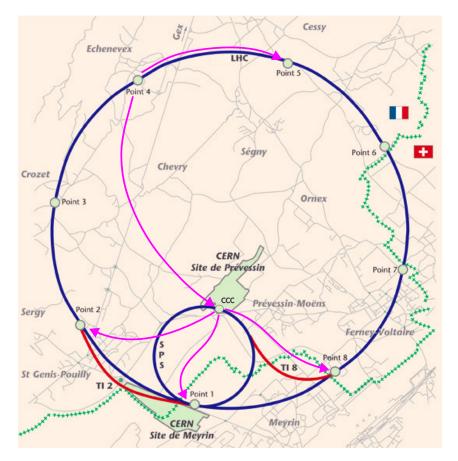

| 1.3  | LHC filling scheme for a typical Run-3 configuration. The horizontal axis          |    |

|      | shows the bunch slot index, while the vertical axis indicates whether the          |    |

|      | slot is filled                                                                     | 4  |

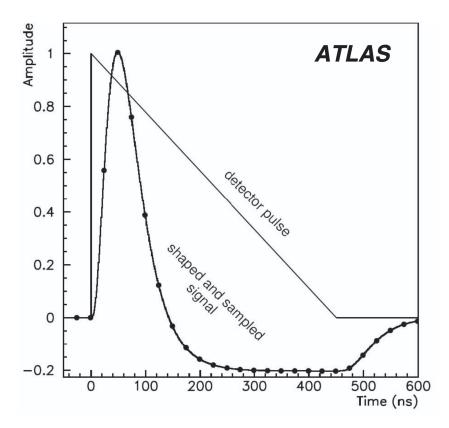

| 1.4  | Shaped bipolar signal from the ATLAS liquid-argon calorimeter [7]                  | 6  |

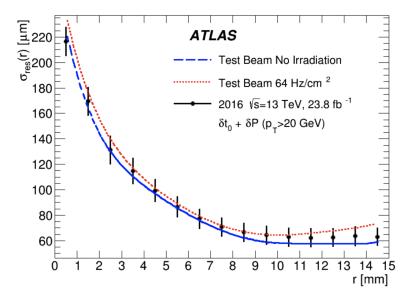

| 1.5  | Single-hit spatial resolution of ATLAS MDT chambers as a function of drift         |    |

|      | radius, based on 2016 Run-2 data [8]                                               | 7  |

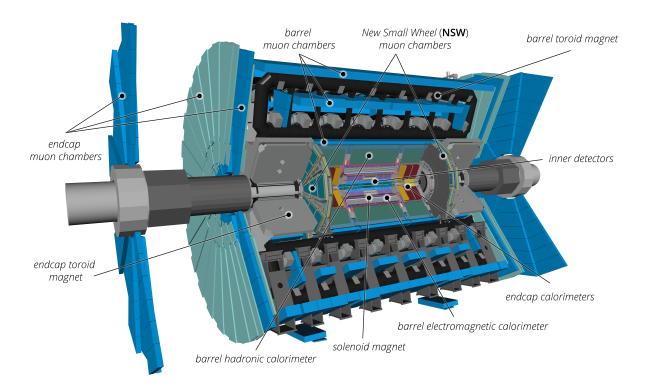

| 2.1  | Cut-away view of the ATLAS detector, illustrating the main sub-detectors           |    |

|      | arranged in a layered structure around the interaction point [15]                  | 12 |

| 2.2  | Layout of ATLAS superconducting magnet systems [16]                                | 14 |

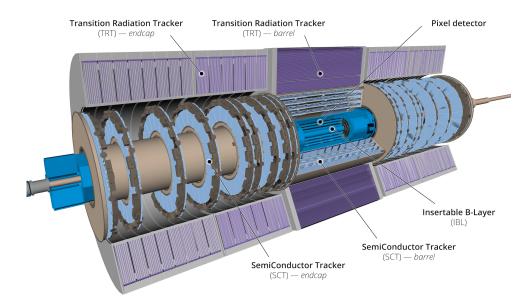

| 2.3  | Cut-away view of the ATLAS inner detector [15]                                     | 15 |

| 2.4  | Cut-away view of the ATLAS calorimeter system [15]                                 | 18 |

| 2.5  | Cut-away view of the ATLAS muon spectrometer [15]                                  | 21 |

| 2.6  | Schematic representation of latency definitions in the ATLAS Level-1 trig-         |    |

|      | ger system [27]                                                                    | 25 |

| 2.7  | Schematic overview of the TDAQ system after the Phase-I upgrade. Adapted           |    |

|      | from [28]                                                                          | 26 |

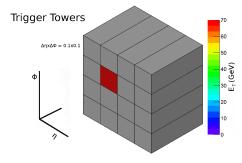

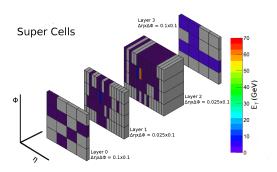

| 2.8  | Simulated energy deposit of a $E_T = 70 \text{GeV}$ electron in the L1Calo trigger |    |

|      | system. Figures adapted from [29]                                                  | 27 |

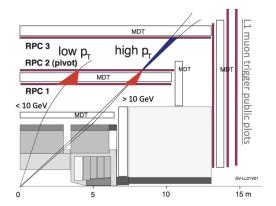

| 2.9  | Examples of hit coincidences in the muon spectrometer trigger sectors [30].        | 28 |

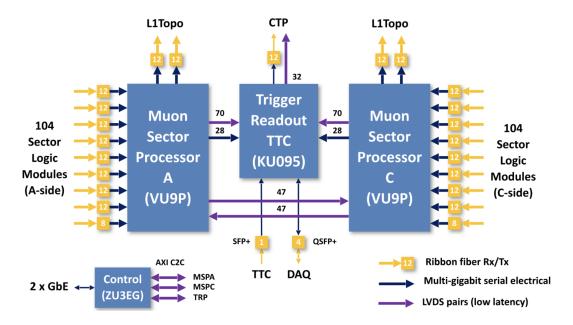

| 2.10 | Block diagram of the Phase-1 MUCTPI (v3)                                           | 30 |

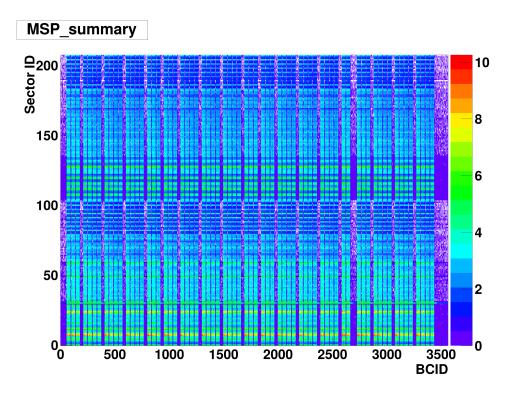

| 2.11 | A MUCTPI monitoring histogram showing the per-bunch rates of muon                  |    |

|      | candidates per-sector. The unit of the temperature gradient is kHz                 | 32 |

| 2.12 | Functional diagram of the Level-1 Accept formation in the Central Trigger          |    |

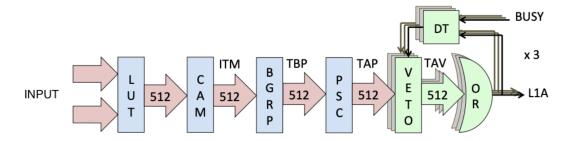

|      | Processor during Run 3                                                             | 36 |

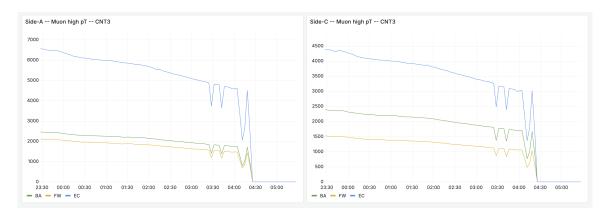

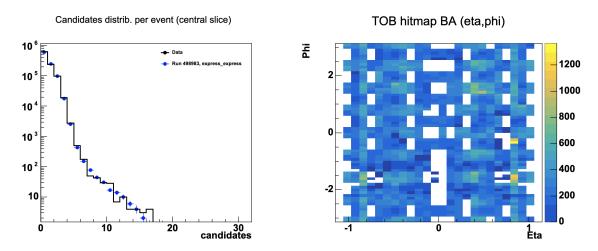

|         | Grafana dashboard of MUCTPI Sector Logic Input rates, showing data for high- $p_T$ muons ( $\geq 12\text{GeV}$ ) per sector type on Side-A Offline MUCTPI DQM histograms from ATLAS run 505244: (left) muon candidate multiplicity per event; (right) TOB hitmap in $\eta$ - $\phi$ coordinates for the barrel sectors | 43                              |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

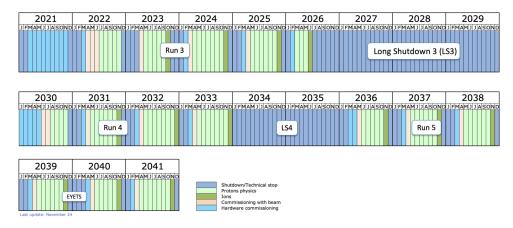

| 3.1     | Planned LHC operational schedule from Run-3 through Run 5, showing Long Shutdown 3 during which the Phase-2 upgrades will be installed. Run-4, beginning in 2030, marks the start of HL-LHC operation [2]                                                                                                              | 45                              |

| 3.2     | Overview of the Phase-2 ATLAS Trigger and Data Acquisition (TDAQ) architecture                                                                                                                                                                                                                                         | 50                              |

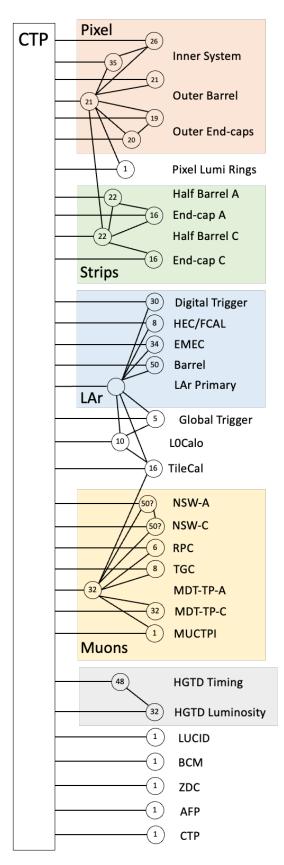

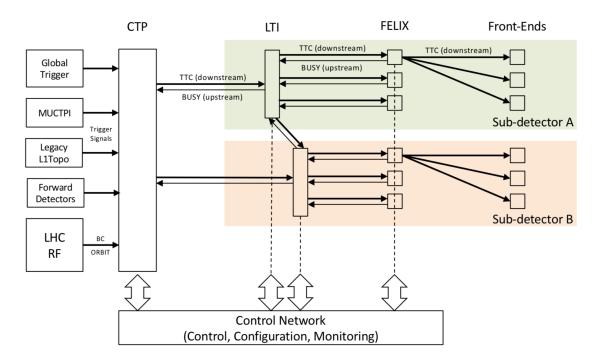

| 3.3     | TTC network layout showing the CTP-LTI and LTI-LTI connections [56]                                                                                                                                                                                                                                                    | 57                              |

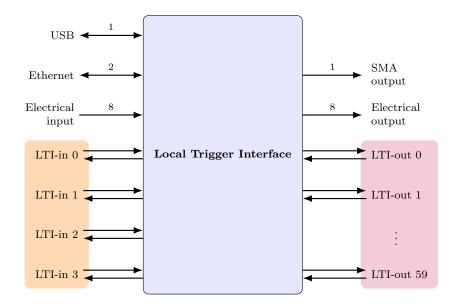

| 4.1     | LTI interfaces                                                                                                                                                                                                                                                                                                         | 62                              |

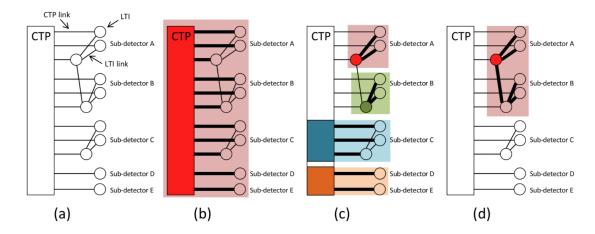

| 4.2     | Examples of TTC partition configurations [56]                                                                                                                                                                                                                                                                          | 63                              |

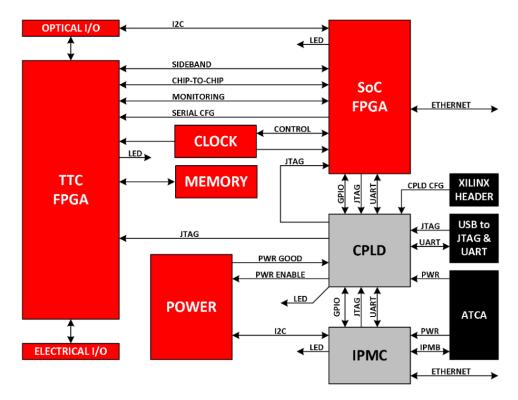

| 4.3     | LTI board block diagram [58]                                                                                                                                                                                                                                                                                           | 64                              |

| 4.4     | Two Firefly modules connected to one MPO output. Source: [59]                                                                                                                                                                                                                                                          | 67                              |

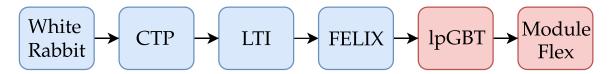

| 4.5     | TTC context diagram [56]                                                                                                                                                                                                                                                                                               | 69                              |

| 4.6     | TTC distribution for the HGTD, from the White Rabbit to the front-end                                                                                                                                                                                                                                                  |                                 |

| 4.7     | electronics                                                                                                                                                                                                                                                                                                            | 70                              |

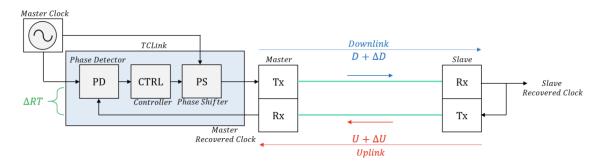

|         | order $\Delta D$ is proportional to $\Delta RT$ [61]                                                                                                                                                                                                                                                                   | 73                              |

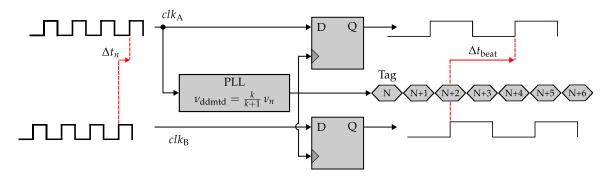

| 4.8 4.9 | DDMTD Diagram, adapted from [64]                                                                                                                                                                                                                                                                                       | <ul><li>74</li><li>76</li></ul> |

| 5.1     | LTI evaluation kits used for phase stability studies                                                                                                                                                                                                                                                                   | 83                              |

| 5.2     | Fully populated LTI prototype #3                                                                                                                                                                                                                                                                                       | 83                              |

| 5.3     | Block-level diagram of the setup for the recovered clock phase measurement.                                                                                                                                                                                                                                            | 84                              |

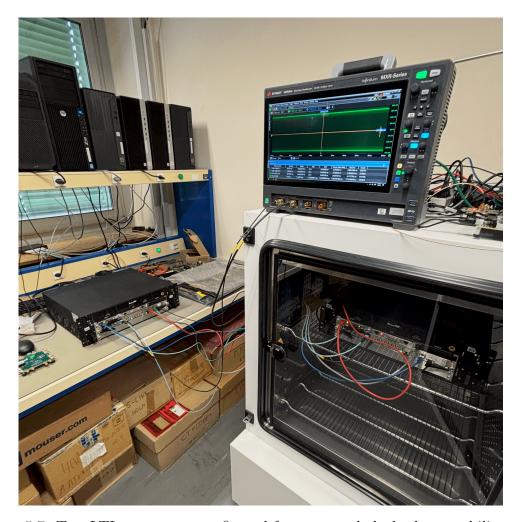

| 5.4     | Example Keysight MXR254A measurement screen. The display window was adjusted for better readability                                                                                                                                                                                                                    | 86                              |

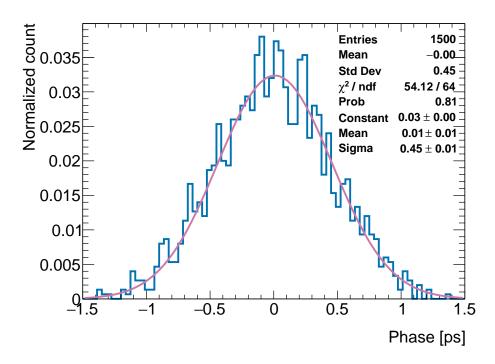

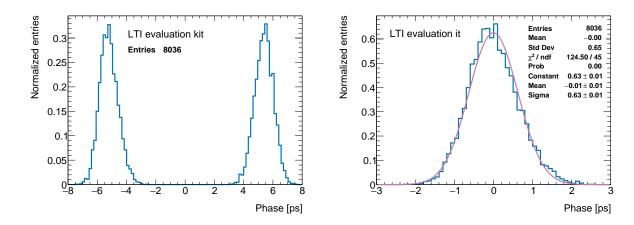

| 5.5     | Distribution of averaged phase measurements over 1500 oscilloscope acquisitions, without transceiver resets                                                                                                                                                                                                            | 86                              |

## LIST OF FIGURES

| 5.6  | Distribution of averaged phase measurements over 1500 DDMTD acquisi-                                                                                                  |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | tions, without transceiver resets                                                                                                                                     | 88  |

| 5.7  | Two LTI prototypes configured for recovered clock phase stability tests                                                                                               | 89  |

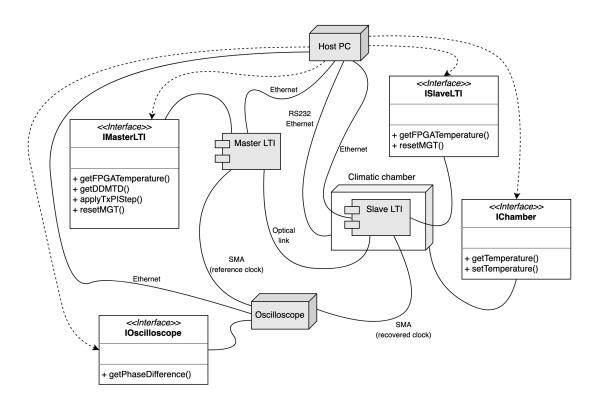

| 5.8  | Software and control architecture of the test setup, showing device interconnections                                                                                  | 91  |

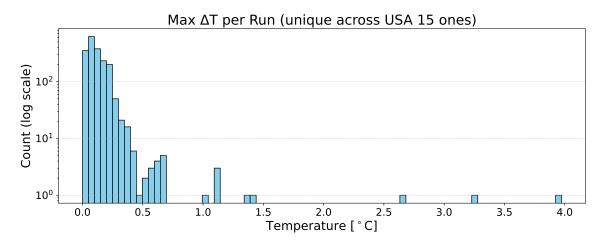

| 5.9  | Histogram of maximum temperature excursions during 2024 ATLAS operations. For each run only the counting cavern region with the largest value                         |     |

|      | is selected                                                                                                                                                           | 92  |

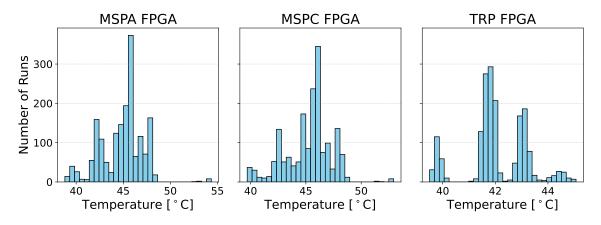

| 5.10 | Histogram of average MUCTPI FPGAs silicon die temperatures across all the ATLAS 2024 run                                                                              | 93  |

| 5.11 | MUCTPI FPGA temperature measurements timeline for the ATLAS run 472879                                                                                                | 94  |

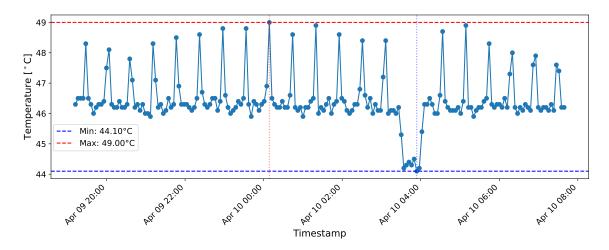

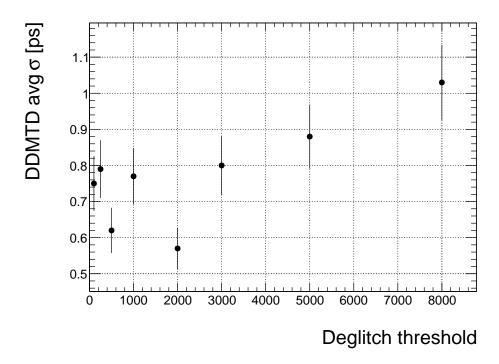

| 5.12 | Comparison of duration per sample vs. total averaging depth $N_{\text{avg}}$ for firmware-only and software-only averaging configurations                             | 96  |

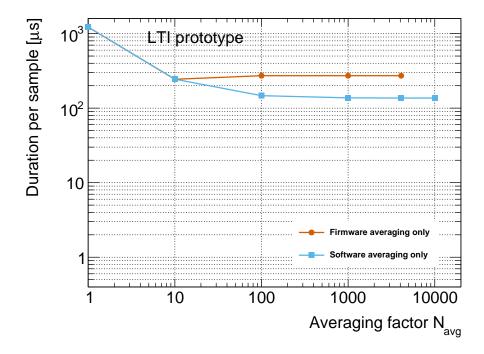

| 5.13 | Average DDMTD standard deviation $\sigma$ as a function of the deglitch threshold, measured on the LTI prototype                                                      | 97  |

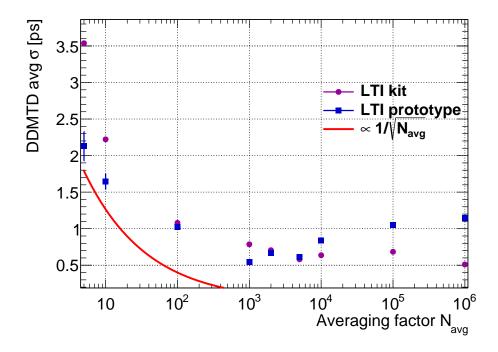

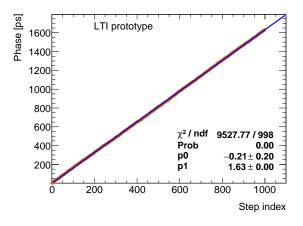

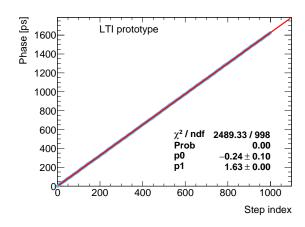

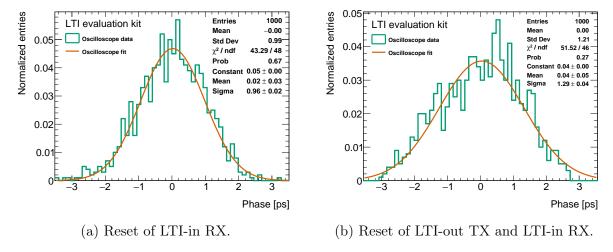

| 5.14 | Standard deviation of 100 DDMTD phase measurements versus total averaging depth $N_{\rm avg} = N_{\rm sw} \times N_{\rm fw}$ , comparing results from the LTI kit and | 91  |

| F 1F | the LTI prototype                                                                                                                                                     | 98  |

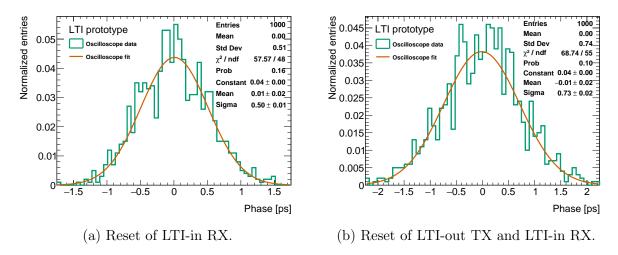

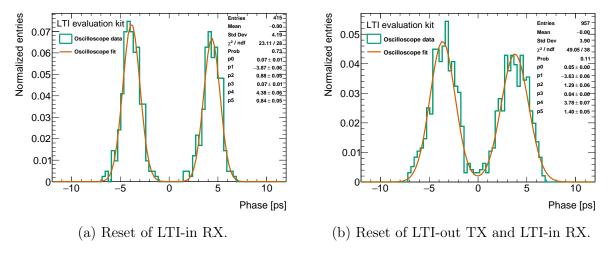

| 5.15 | Oscilloscope recovered clock phase distributions after resetting the GTH transceivers at constant temperature for the LTI evaluation kit                              | 99  |

| 5.16 | Oscilloscope recovered clock phase distributions after resetting the GTH transceivers at constant temperature for the LTI evaluation kit                              | 101 |

| 5.17 | Oscilloscope recovered clock phase distributions after resetting the GTH transceivers at constant temperature for the LTI prototype                                   | 101 |

| 5.18 | Oscilloscope recovered clock phase distributions after resetting the GTY transceivers at constant temperature for the LTI evaluation kit                              |     |

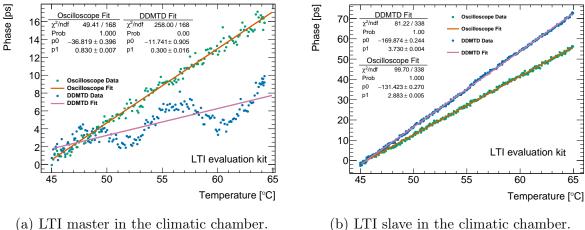

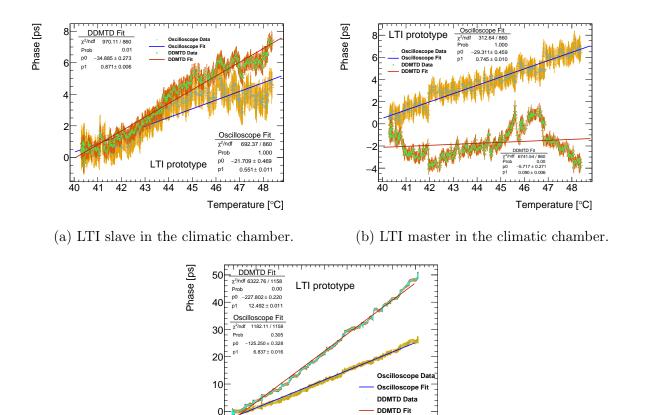

| 5.19 | LTI evaluation kit phase monitoring data with either LTI master or slave                                                                                              |     |

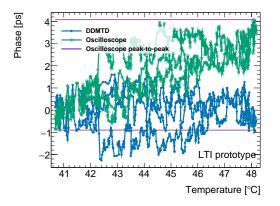

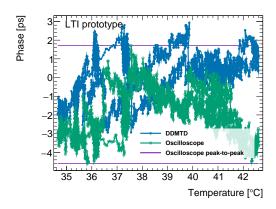

| 5.20 | are in the climatic chamber                                                                                                                                           | 104 |

| 5.21 | (b), or 40 m of optical fibers (c) are in the climatic chamber                                                                                                        |     |

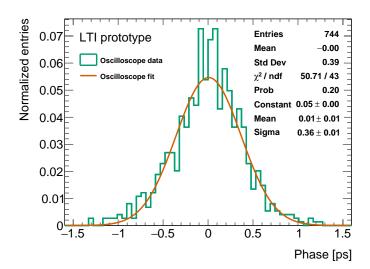

| 5.22 | LTI prototype recovered clock phase distribution with the "clock fiber" configuration                                                                                 | 106 |

| 5.23 | DDMTD phase compensation of either LTI slave (a), LTI master (b) or 40 m of optical fibers (c)                                                                        |     |

| 5 94 | Comparison of measured and predicted phase drift using the temperature-                                                                                               | 100 |

| J.44 | based regression model                                                                                                                                                | 109 |

| 5.25 | Residual analysis of the temperature-based regression model                     |

|------|---------------------------------------------------------------------------------|

| 5.26 | Phase compensation algorithm in action, with either LTI master or slave         |

|      | in the climatic chamber                                                         |

| 5.27 | Clock distribution chain from LTI to HGTD Module Flex used for integra-         |

|      | tion tests during the HGTD FELIX expert week. In blue the "off-detector"        |

|      | elements, while in red the "on-detector" electronics                            |

| 5.28 | Left: Startup phase difference between LTI and Module Flex, measured            |

|      | with an oscilloscope after repeated resets of the FELIX RX transceiver.         |

|      | Right: Startup phase versus FPGA temperature                                    |

| 5.29 | HGTD module setup inside a copper-shielded box. The orange flex PCBs            |

|      | (Module Flex) connected the lpGBT outputs to the timing detector modules. $116$ |

| 5.30 | FELIX-based data acquisition rack during integration tests. The LTI (bot-       |

|      | tom) distributed the clock to FELIX, while an oscilloscope monitored the        |

|      | startup phase of the recovered clock at the Module Flex against the LTI         |

|      | reference clock                                                                 |

| 6.1  | Context diagram of the LTI application within the ATLAS remote control          |

|      | system                                                                          |

| 6.2  | State machine diagram of the LTI software aligned with the Finite State         |

|      | Machine (FSM) transitions of the ATLAS remote control system 125                |

| 6.3  | Activity diagram of the LTI phase monitoring and compensation loop $126$        |

|      |                                                                                 |

# List of Tables

| 3.1 | Comparison of CTP and other parameters between Phase-1 and Phase-2    | 53  |

|-----|-----------------------------------------------------------------------|-----|

| 3.2 | Sliding window parameters for HL-LHC physics data-taking              | 54  |

| 4.1 | Summary of TTC signals handled by the LTI. Source: [56]               | 60  |

| 5.1 | Climatic chambers used for LTI tests                                  | 88  |

| 5.2 | Measurement duration scaling with firmware averaging $(N_{\rm sw}=1)$ | 95  |

| 5.3 | Measurement duration scaling with software averaging $(N_{\rm fw}=1)$ | 95  |

| 5.4 | Summary of compensation outcomes                                      | 111 |

| 5.5 | RMS jitter budget and startup phase spread to the HGTD Module Flex    | 115 |

# Chapter 1

# Introduction

The European Organization for Nuclear Research (CERN) is an international research organization based in Geneva, Switzerland, dedicated to the study of fundamental particles and their interactions. Its primary scientific objective is to test and extend the Standard Model of particle physics, which currently provides the most comprehensive description of known elementary particles and three of the four fundamental forces: electromagnetic, weak, and strong interactions. The Standard Model does not incorporate gravity and is known to be incomplete [1].

At the center of CERN's experimental program is the Large Hadron Collider (LHC), a circular superconducting collider with a circumference of 27 km, located approximately 100 m underground along the France–Switzerland border. The LHC is capable of colliding proton–proton, proton–ion, and ion–ion beams<sup>1</sup> at the highest energies ever achieved in a laboratory setting. These collisions are studied with large-scale detectors to explore the properties of known particles and probe for potential signs of physics beyond the Standard Model [1].

There are four main interaction points along the LHC ring, each hosting a major experiment: ATLAS, CMS, ALICE, and LHCb. ATLAS and CMS are general-purpose detectors optimized for a wide range of physics goals, including precision measurements, Higgs boson studies, and searches for Physics Beyond the Standard Model (BSM). ALICE is designed to investigate the properties of strongly interacting matter under extreme conditions, such as those created in heavy-ion collisions, where a Quark–Gluon Plasma (QGP) is expected to form. LHCb focuses on flavor physics, particularly the study of heavy-flavor hadrons and CP violation in the quark sector.

The LHC ring is divided into eight sectors, numbered sequentially around the circumference, with the junctions between sectors referred to as "Points" (P1–P8). Four of these points host the main experiments: P1 (ATLAS), P2 (ALICE), P5 (CMS), and P8

$<sup>^{1}</sup>$ Heavy-ion runs at the LHC have primarily used fully stripped lead nuclei ( $^{208}$ Pb $^{82+}$ ), while recent short runs have also included oxygen ( $^{16}$ O $^{8+}$ ) and neon ( $^{20}$ Ne $^{10+}$ ) beams for lighter-ion studies.

(LHCb), while others contain major accelerator systems and facilities.

The LHC began operations in 2010 and has delivered collisions in successive multiyear periods known as "runs". To sustain and improve detector performance in the face of increasing luminosity, and to meet the physics goals of the data-taking, a series of hardware and software improvements have been implemented. Major improvements are usually implemented during Long Shutdown periods, following every run, during which both the accelerator and the experiments undergo maintenance and upgrades. The most recent such program, known as the Phase-1 upgrades, was carried out during Long Shutdown 2 (2019–2022) and prepared all LHC experiments for the higher luminosities and more challenging conditions of Run-3. At the time of writing, the LHC is operating in Run-3, which is scheduled to conclude in mid-2026 and be followed by the Long Shutdown 3 [2].

The LHC is the final stage in CERN's accelerator complex, a series of interconnected machines that progressively accelerate and prepare the particle beams. The acceleration chain includes Linac4, the Proton Synchrotron Booster (PSB), the Proton Synchrotron (PS), and the Super Proton Synchrotron (SPS), which together deliver protons at 450 GeV to the LHC. A schematic overview of this complex is shown in Figure 1.1.

Figure 1.1: CERN's accelerator complex [3].

Inside the LHC, two counter-rotating proton beams circulate in ultra-high-vacuum beam pipes, guided by superconducting dipole magnets and focused in the transverse plane by quadrupole magnets. The longitudinal beam structure is composed of discrete proton packets known as bunches. Each bunch contains approximately  $1.1 \times 10^{11}$  protons, whose organization is governed by the superconducting radio-frequency (RF) system located at P4.

The LHC RF system operates at the master frequency of 400 MHz, which defines discrete RF buckets separated by 2.5 ns. In principle, each RF bucket can hold a bunch of protons. Even so, in nominal operating conditions the bunches can occupy every tenth bucket. This frequency division defines the 40 MHz bunch clock, and consecutively 3564 bunch slots spaced 25 ns. In addition to the bunch clock, the RF system also produces the once-per-turn **Orbit** signal, which has a period of 89 µs and a pulse width of 1 µs.

The bunch clock is the heartbeat of the LHC and its experiments. Almost everything is synchronous to the bunch clock: collisions, detector readout, front-end digitization, and data selection pipelines. This means that at any time the bunch clock (and the Orbit) has to be distributed everywhere with the best possible quality.

The bunch clock and Orbit signals for each beam are distributed through the Trigger, Timing and Control (TTC) backbone, a CERN-wide optical network that delivers the timing signals to the CERN Control Center (CCC), and to all LHC experiments. The backbone employs standard VME<sup>2</sup>-format RF optical transmitters and receivers, ensuring low-jitter transmission over long distances — with a typical output jitter of about 10 ps RMS at the experiment side [5]. The "jitter" refers to small, rapid variations in the timing of a signal or event. It is the deviation from the expected, regular timing of a signal or process. Figure 1.2 shows the TTC backbone distribution from P4 to the main experiments, passing from the CCC.

In the ATLAS experiment, the TTC backbone signals are received in the counting room, which hosts the off-detector electronics next to the main experimental cavern. An electronics module recovers the clocks and Orbit markers with a jitter RMS of about 11 ps [6] before distributing them via the ATLAS-specific TTC network to all front-end systems. More information on the connection between global-TTC and ATLAS-TTC will be provided in Section 2.2.7.

The synchronization of ATLAS with the bunch clock is affected by the specific filling scheme of the LHC beams. The filling scheme determines which RF buckets are populated and which are left empty. The filling scheme represents a trade-off between maximizing collision rates, machine-protection requirements and overlapping interactions within the detector. Figure 1.3 shows a typical filling scheme.

After injection at 450 GeV, the beams are accelerated to a top energy of 6.8 TeV per beam, corresponding to a center-of-mass energy  $\sqrt{s} = 13.6$  TeV; at this point the beams are focused and brought into collision. In general the detectors are kept recording as many physics events as possible, however only the events corresponding to LHC stable beams are used for physics analyses. With the beam configuration in place and stable collisions achieved, attention turns to the physics processes that these collisions can produce and how they are recorded.

<sup>&</sup>lt;sup>2</sup>Versa Module Eurocard [4]

Figure 1.2: TTC backbone distribution (highlighted in magenta). Starting from the LHC RF at P4, passing through the CCC, and to the main experiments. Only the CMS experiment at P5 receives timing signals directly from P4.

Figure 1.3: LHC filling scheme for a typical Run-3 configuration. The horizontal axis shows the bunch slot index, while the vertical axis indicates whether the slot is filled.

Since only a small fraction of the millions of collisions occurring every second can be recorded, experiments at the LHC rely on fast and efficient data selection systems. In the case of ATLAS, a two-level trigger architecture is used: the hardware-based Level-1 (L1) Trigger reduces the event rate from 40 MHz, corresponding to a 25 ns bunch spacing. Front-end electronics are required to sample detector signals at precise intervals, with timing alignment typically accurate to within a few nanoseconds. Even small deviations can result in signals being assigned to the wrong bunch crossing, degrading both triggering efficiency and offline reconstruction performance.

The interpretation of detector signals in a collider experiment like ATLAS relies on accurate temporal alignment with the LHC's bunch structure. Sub-Detectors such as calorimeters and muon chambers produce analog signals with characteristic pulse shapes and time profiles. To reconstruct these signals correctly, front-end electronics must sample them at specific, phase-locked intervals relative to the 40 MHz bunch clock. Even nanosecond-level misalignments can distort the signal shape, lead to incorrect energy reconstruction, or cause hits to be assigned to the wrong bunch crossing.

The Timing, Trigger, and Control (TTC) system is responsible for distributing this clock, along with synchronous control signals, to thousands of front-end modules throughout the detector. It ensures that all channels operate within a coherent global timing framework, enabling accurate signal digitization, consistent trigger decisions, and proper event reconstruction. Low-jitter, phase-stable timing distribution is therefore essential to maintaining detector performance and data integrity, even under standard LHC running conditions.

This requirement is especially stringent for sub-detectors with long signal integration times. In calorimeters, for example, analog pulses can span multiple bunch crossings. The ATLAS liquid-argon (LAr) calorimeter uses bipolar shaping, with signals that peak approximately 50 ns after the interaction and extend beyond 400 ns. Sampling must occur at precisely calibrated phases relative to the bunch clock. A timing offset on the order of 1 ns can significantly affect the measured energy and cause energy deposits to be assigned to the wrong vertex in high pile-up conditions [7]. This is illustrated in Figure 1.4, which shows the shaped LAr pulse and sampling points.

Muon systems are similarly sensitive. Muons typically traverse several meters from the interaction point to the outermost detector layers, and their arrival time depends on both geometry and momentum. Timing calibration ensures that hits in drift tubes or resistive plate chambers are correctly assigned to their bunch crossing. Offsets of just a few nanoseconds can result in misassigned or missed hits. In drift-based detectors, such misalignment affects the conversion from drift time to spatial coordinate, which degrades track and momentum reconstruction.

The role of precise timing is particularly evident in the performance of ATLAS muon

drift tube (MDT) chambers. These detectors measure the distance of a muon from the wire based on the time required for ionization electrons to drift across the gas volume. This drift time must be calibrated against the global TTC-distributed clock. In Run-2, after calibrating individual tube offsets, an average single-hit spatial resolution of  $81.7 \pm 2.2$  µm was achieved across the MDT system [8]. Given a typical drift velocity of  $30 \,\mu\text{m/ns}$ , this level of spatial resolution corresponds to timing precision at the 1–2 ns level. Maintaining such synchronization is essential for accurate hit reconstruction and reliable muon tracking. Figure 1.5 shows the spatial resolution as a function of drift radius.

Figure 1.4: Shaped bipolar signal from the ATLAS liquid-argon calorimeter [7].

These challenges become more severe at high luminosity, when many overlapping interactions occur within the same bunch crossing. Accurate timing is not only required to assign signals to the correct bunch crossing, but also to suppress pile-up. Maintaining precise timing across all detector systems is therefore not a technical detail, but it is essential to achieving high-quality reconstruction and efficient triggering. Upcoming detector upgrades aim to enhance both in-time and out-of-time pile-up rejection by incorporating high-resolution timing layers with precision below 50 ps, enabling four-dimensional vertex reconstruction.

Figure 1.5: Single-hit spatial resolution of ATLAS MDT chambers as a function of drift radius, based on 2016 Run-2 data [8].

# 1.1 High-Luminosity LHC

The end of LHC Run-3, scheduled for mid-2026, will be followed by the Long Shutdown 3 (LS3), extending until mid-2030. During this period the Phase-2 upgrade program will be implemented in preparation for the High-Luminosity LHC (HL-LHC) phase. The HL-LHC aims to increase the LHC's instantaneous luminosity by a factor of five to seven, reaching up to  $7.5 \times 10^{34} {\rm cm}^{-2} {\rm s}^{-1}$ , allowing for the collection of a much larger dataset and improving sensitivity to rare physics processes. However, this increase in performance also presents major challenges for the experiments in terms of data volume, radiation tolerance, and the need for tighter timing and trigger control. The increased luminosity will lead to an average of  $\langle \mu \rangle = 200$  simultaneous inelastic collisions per bunch crossing, which significantly complicates event reconstruction and analysis.

At these pile-up levels, vertex reconstruction and track-to-vertex association become increasingly challenging, particularly in the forward region. While the upgraded Inner Tracker (ITk) provides excellent performance in the central region, its longitudinal impact parameter resolution degrades at high pseudorapidity, exceeding 200 µm at  $|\eta| > 2.5$  [9]. To maintain efficient pile-up rejection in the forward region, the High-Granularity Timing Detector (HGTD) will be installed in the range  $2.4 < |\eta| < 4.0$ , providing a per-track time resolution of approximately 30 ps [10]. This enables four-dimensional vertexing<sup>3</sup>, improving the association of tracks and calorimeter deposits to the correct primary in-

$<sup>^{3}</sup>$ Four-dimensional vertexing refers to the process of reconstructing collision vertices not just in space, but also in time.

teraction. Achieving this timing precision requires a low-jitter clock distribution system. The Local Trigger Interface (LTI) will be the new ATLAS module distributing the experiment's master clock signal. Its function is essential to ensure that high-resolution timing detectors such as the HGTD receive a phase-stable, low-jitter reference signal, as any fluctuations in the distributed clock would directly degrade timing performance and reduce the efficacy of 4D vertexing in the high pile-up environment of the HL-LHC.

More details about the ATLAS upgrades in view of the HL-LHC will be given in Chapter 3.

## 1.2 Author's Contributions

The work presented in this thesis was carried out within the ATLAS Collaboration during Run-3 and in preparation for the ATLAS HL-LHC upgrade.

The author played a central role in the development of the Local Trigger Interface (LTI), a key component responsible for distributing timing and trigger signals to ATLAS sub-detectors in the HL-LHC era. A central focus of this work was the study of clock phase stability: evaluation kits and prototypes were tested to identify potential sources of instability, quantify their impact on timing performance, and investigate mitigation strategies for long-term drifts caused by temperature variations within the LTI and its environment. In addition, the author was responsible for the configuration and implementation of the LTI control software and actively defined its operational logic and integration strategies.

Beyond upgrade activities, the author was responsible for the operation of the Run-3 ATLAS Central Trigger system, a core element of ATLAS data-taking. This work included on-call expert support, maintenance of the timing infrastructure, and the development and upkeep of monitoring tools. In particular, the author developed and maintained a Central Trigger monitoring package that ensured the stability and reliability of data-taking conditions.

The author's ATLAS Qualification Task (a prerequisite for full authorship within the collaboration) was also carried out in the Central Trigger system. It focused specifically on monitoring and data quality, and its successful completion granted the author full ATLAS authorship. Together, these efforts span both upgrade development and Run-3 operations, supporting the technical infrastructure, reliability, and evolution of the ATLAS trigger and timing systems in preparation for the HL-LHC.

As a member of the ATLAS Collaboration, the author has been included in the author list of all official ATLAS physics publications since January 2024. In addition, the author was co-author of selected ATLAS internal and public notes within the Level-1 Central Trigger group. While the author did not participate directly to the writing of these

#### 1.2. AUTHOR'S CONTRIBUTIONS

documents, technical and operational work described in this thesis was incorporated into the results they present. The most relevant notes are:

- Integration and commissioning of the ATLAS Muon-to-Central-Trigger-Processor Interface for Run-3 [11], ATL-COM-DAQ-2021-083, CERN (2021). This note presented work the author carried out as a CERN Technical Student. Although the publication preceded the start of the doctoral program, the author continued related integration and operational activities on this system throughout the doctoral research.

- Phase-II Upgrade of the ATLAS L1 Central Trigger [12], ATL-DAQ-PROC-2024-007, CERN (2024). While the note itself describes the high-level design and status of the Phase-2 upgrade for the Central Trigger, the author's contributions were at the technical and operational level supporting this broader activity.

- High-Precision Timing Distribution in the ATLAS Phase-2 upgrade [13], CERN (2024). During the poster session of the October 2024 ATLAS week the author presented the status of my studies on clock phase stability and mitigation procedures with LTI evaluation kits. This poster presentation marked the first internal ATLAS publication on this topic.

1 Introduction

# Chapter 2

# The ATLAS experiment

This chapter provides an overview of the ATLAS Experiment. The first part describes briefly the main ATLAS sub-detectors, while the second part introduces the Run-3 ATLAS Trigger and Data Acquisition (TDAQ) system.

## 2.1 The ATLAS detector

ATLAS is a general-purpose particle detector designed to investigate a wide range of physics phenomena resulting from high-energy proton—proton, ion—ion or proton—ion collisions. It is built with a forward—backward symmetric cylindrical geometry and nearly complete coverage in solid angle. The detector is composed of several concentric subsystems, each optimized to measure specific properties of particles. For each selected bunch crossing, the full event from the detector readout is reconstructed. This includes all the collisions that occurred within that 25 ns interval. Typically, only one of these collisions, referred to as the primary hard-scatter interaction, is of interest for physics analyses. The goal is to assign tracks to the primary vertex so that reconstructed objects originate from the hard scattering. For this reason pile-up interactions are also reconstructed and must be taken into account [14].

Surrounding the collision point from the inside out, the sub-detectors are:

- Inner detector for measurements of charge, trajectories and momentum of charged particles. The inner detector is enclosed by a solenoidal magnet.

- Electromagnetic and hadronic calorimeters for energy measurements of electrons, taus, photons and hadrons.

- Muon spectrometer for identification and momentum determination of muons. The muon spectrometer operates within a large air-core toroidal magnet system.

The detector measures approximately 46 m in length and 25 m in height, with a total mass of about  $7 \times 10^6$  kg [14]. A schematic longitudinal cut-away view of the detector is shown in Figure 2.1.

Figure 2.1: Cut-away view of the ATLAS detector, illustrating the main sub-detectors arranged in a layered structure around the interaction point [15].

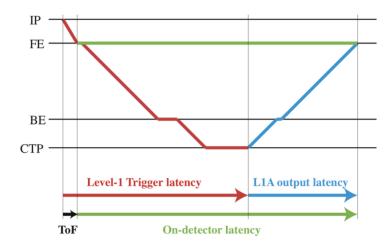

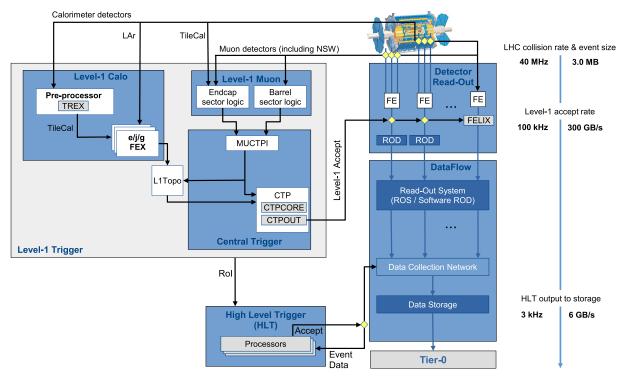

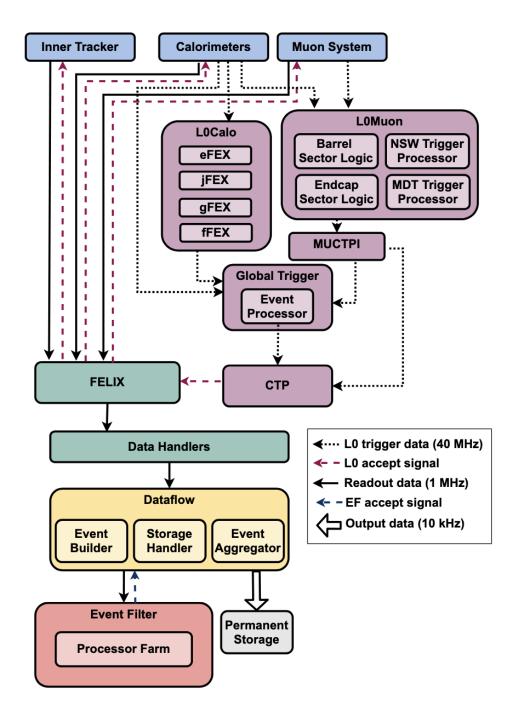

In addition to its diverse sub-detectors, ATLAS relies on a Trigger and Data Acquisition system to decide, in real time, which of the bunch crossings are stored for analysis. The TDAQ operates in two stages: a fixed-latency hardware-based Level-1 (L1) trigger and a software-based High-Level Trigger (HLT). The L1 trigger must deliver a decision within a maximum latency of 2.5 µs, reducing the event rate from 40 MHz to about 100 kHz. Events accepted by the L1 Trigger are fully read out and processed by the HLT, which applies refined reconstruction algorithms to bring the output rate down to around 3 kHz for permanent storage.

The diverse range of physics goals pursued at the LHC imposes several stringent design requirements on the ATLAS detector [14]:

- Fast and radiation-hard electronics to withstand high radiation levels and allow real-time signal processing.

- High spatial and temporal granularity to handle intense particle fluxes and mitigate event pile-up.

#### 2.1. THE ATLAS DETECTOR

- Precision muon momentum measurements across a broad range of momenta, along with reliable charge determination.

- Excellent electromagnetic calorimetry for identifying and measuring photons and electrons, along with robust hadronic calorimetry for accurate jet reconstruction and missing transverse energy (MET) measurements.

- Efficient tracking and vertex reconstruction for charged particles, even under highluminosity conditions.

- Wide pseudorapidity acceptance and full azimuthal coverage to maximize detection efficiency and transverse energy reconstruction.

## 2.1.1 Coordinate system

The coordinate system used in ATLAS is a right-handed Cartesian system with its origin at the center of the detector, located at the nominal interaction point [14]. The positive x-axis points towards the center of the LHC ring, while the z-axis is aligned along the beam direction. The positive y-axis points upwards, though it is slightly tilted with respect to the vertical due to the overall inclination of the LHC tunnel.

In the transverse plane, cylindrical coordinates  $(r, \phi)$  are used, where  $\phi \in [-\pi, \pi]$  is the azimuthal angle measured around the beam axis from the x-axis, and r is the radial distance from the interaction point [14]. The polar angle  $\theta \in [0, \pi)$  is measured from the positive z-axis, but it is more commonly expressed in terms of the pseudorapidity  $\eta$ , which is defined as:

$$\eta = -\ln\left[\tan\left(\frac{\theta}{2}\right)\right]. \tag{2.1}$$

Regions of the detector close to the beam axis are often referred to as "forward" (for  $|\eta| \gtrsim 2.5$ ). Additionally, the side of the detector where z > 0 is called side A, and the side where z < 0 is referred to as side C.

For distance measurements in the  $(\eta, \phi)$  space, the separation variable  $\Delta R$  is defined as:

$$\Delta R = \sqrt{(\Delta \eta)^2 + (\Delta \phi)^2}.$$

(2.2)

This variable is dimensionless and represents the angular distance between two objects in the detector, combining differences in pseudorapidity and azimuth.

## 2.1.2 Magnets system

Achieving precise reconstruction of charged particle momenta in ATLAS, especially at the multi-TeV scale, requires a strong and well-shaped magnetic field over large detector volumes. The magnetic field across the ATLAS detector is produced by four systems of superconducting magnets: one solenoid, one barrel toroid, and two endcap toroids [14]. The cryogenic infrastructure supplies both liquid and gaseous helium at temperatures of 4.5 K and 60 K respectively, to cool the superconducting coils and to maintain thermal shielding [14]. The configuration of the magnet systems is shown in Figure 2.2.

Figure 2.2: Layout of ATLAS superconducting magnet systems [16].

The choice of magnet technologies and geometry was driven by the need for large active volumes and strong magnetic fields. These parameters are critical for achieving good momentum resolution. To first order, the transverse momentum resolution scales as  $\sigma_{p_T}/p_T \propto p_T/(BL^2)$ , where B is the magnetic field strength and L is the tracking length [17].

The solenoid magnet is aligned coaxially with the beam line and surrounds the Inner Detector. Located immediately outside the Inner Detector volume and inside the cryostat of the electromagnetic calorimeter barrel, it generates an axial magnetic field of approximately 2 T used for inner tracking. Because the solenoid is located in front of the calorimeter, its design had to minimize the amount of dead material which degrades the calorimeter energy resolution. For this reason, it was constructed using Al-stabilized NbTi with a thickness of only 4.5 cm, corresponding to about 0.66 radiation lengths [16].

The endcap toroid magnets generate magnetic fields of up to 3.5 T in the regions surrounding the endcap calorimeters. Their distinctive gear-like structure allows them to interlock with the barrel toroid at an angle of 22.5°, improving the field coverage and

#### 2.1. THE ATLAS DETECTOR

Figure 2.3: Cut-away view of the ATLAS inner detector [15].

providing a smooth transition between the barrel and endcap regions [14].

The typical bending power of the magnetic system is around 3 T m in the barrel and up to 6 T m in the endcap regions [16]. Due to the finite number of coils, the magnetic field deviates from an ideal toroidal shape and exhibits a periodic ripple pattern in azimuth. As a result, the bending power experienced by a particle depends on its initial position, direction, charge, and momentum. These local variations degrade the momentum resolution, particularly in the barrel–endcap transition region, where a sizable radial field component is present [14].

### 2.1.3 Inner Detector

The inner detector (ID) is the innermost tracking system of ATLAS, surrounding the beamline in a high-radiation environment. It operates in the axial magnetic field provided by the central solenoid (see section 2.1.2). The ID provides tracking coverage up to  $|\eta| < 2.5$  and is used to reconstruct primary and secondary vertices [15].

It consists of three sub-detectors arranged in concentric cylindrical layers: the pixel detector (PIX), the semiconductor tracker (SCT), and the transition radiation tracker (TRT). The full system is contained in a cylindrical volume 2.1 m in diameter and 6.2 m in length [15]. The inner detector is shown in Figure 2.3.

The inner detector information is not used in the L1 trigger. Real-time track reconstruction at L1 would require processing the full inner detector hit pattern within the 2.5 µs latency window. The inner detector tracks are used in the high-level trigger and offline reconstruction.

Pixel Detector (PIX): The PIX consists of four barrel layers of silicon pixel sensors with a total of about 92 million readout channels. The innermost layer, the insertable B-layer (IBL), was installed during Long Shutdown 1 after Run-1 to maintain performance under higher pile-up conditions [18]. Pixel pitch in the IBL is  $50 \,\mu\text{m} \times 250 \,\mu\text{m}$  in the  $r\phi$  and z directions, respectively. In the other three layers the pitch is  $50 \,\mu\text{m} \times 400 \,\mu\text{m}$ . The spatial resolution is approximately  $8 \,\mu\text{m}$  in  $r\phi$  and  $40 \,\mu\text{m}$  in z for the IBL, and  $10 \,\mu\text{m}$  in  $r\phi$  and  $115 \,\mu\text{m}$  in z for the other layers.

Semiconductor Tracker (SCT): The SCT is located outside the PIX and consists of four barrel layers and nine disks in each endcap. Each module contains two single-sided silicon microstrip sensors mounted back-to-back at a stereo angle of about 40 mrad. The strips on both sensors are nearly parallel to z, but the stereo tilt causes them to shift sideways in  $r\phi$  as z increases. A track crossing the module therefore produces hits on different strip numbers in the two sensors, and the offset is proportional to the z-position of the hit [19]. This geometry allows the reconstruction of both the  $r\phi$  coordinate and the second coordinate (z in the barrel, r in the endcaps) from a single module. In total, the SCT contains about 4000 modules with roughly six million strips. The spatial resolution is about 16 µm in  $r\phi$  and 580 µm in z. Two different tracks can be resolved if they are distant more than 200 µm from each other [19].

Transition Radiation Tracker (TRT): The TRT is the outermost ID sub-detector and consists of straw drift tubes arranged in the barrel and endcap regions. Each straw is a 4 mm diameter cylindrical drift chamber with a central gold-plated tungsten anode wire, operated at a cathode potential of  $-1.5\,\mathrm{kV}$  [14]. A charged particle crossing a straw ionizes the gas, and the electron drift time to the anode is used to determine the track's radial distance from the wire. Since Run 3, the TRT straw tubes have been operated with an argon-based gas mixture (70% Ar, 27% CO<sub>2</sub>, 3% O<sub>2</sub>) [15], replacing the previous xenon-based mixture due to its high cost and limited availability [15]. The TRT provides about 30 tracking measurements per charged particle, with an intrinsic resolution of 120  $\mu$ m in  $r\phi$ . In addition, the TRT read-out measures the time-over-threshold for each straw signal, which is proportional to the energy deposited in the gas. Combining this information across many straws yields an estimate of the track's average energy loss (dE/dx). Layers of polypropylene radiators are interleaved between straw planes to increase the production of transition-radiation photons from highly relativistic particles. Transition-radiation deposits are typically 8–10 keV per hit for electrons and about 2 keV for pions, enabling electron identification [20].

## 2.1.4 Calorimeter System

Calorimeters are detectors that measure the energy of particles by causing them to interact with a dense material, which initiates a cascade of secondary particles known as a particle shower. The total energy of the primary particle is then inferred by measuring the energy deposited by the shower within an active medium. This is in contrast to tracking detectors, which measure particle momentum by observing their trajectories. The composition and shape of the particle shower depend on the type and energy of the primary particle ( $e^{\pm}$ ,  $\gamma$ , or hadrons). This distinction motivates two main applications of calorimeters: (i) electromagnetic calorimeters and (ii) hadronic calorimeters.

Electromagnetic calorimeters are optimized to measure electrons and photons, which develop showers dominated by bremsstrahlung and pair production. Hadronic calorimeters are designed to measure hadrons, such as protons and neutrons, whose showers are initiated primarily through strong interactions. In practice, hadronic showers also contain a sizable electromagnetic component, arising mostly from the decay of neutral pions  $(\pi^0 \to \gamma \gamma)$ . Consequently, a fraction of the hadronic shower energy is deposited in the electromagnetic calorimeter, while the remainder is absorbed in the hadronic calorimeter. Compared to electromagnetic showers, hadronic showers are typically more complex and spatially larger, requiring greater material depth for full containment. Their development involves a broad range of particles and processes, including the production of slow neutrons, which may travel long distances before depositing their energy.

Beyond their physics application, calorimeters can also be classified by their structure. They can be homogeneous—constructed from a single material that both initiates and detects showers—or sampling calorimeters, which consist of alternating absorber and active layers. The absorber, often made of high-Z materials such as lead, tungsten, or steel, initiates repeated electromagnetic or hadronic interactions that produce cascades of secondary particles. The active medium converts the passage of shower particles into a measurable signal: in liquid argon calorimeters this is done via ionization of the liquid argon (LAr), producing a drift current, while in scintillator calorimeters it is done via scintillation light collected by optical fibers.

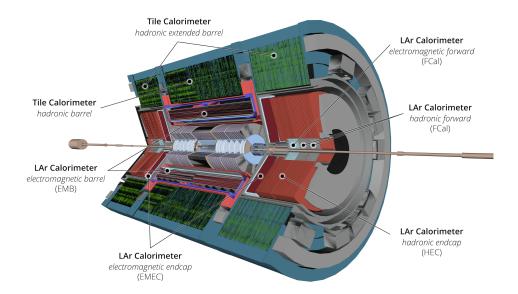

The ATLAS calorimeter system consists of two main concentric structures with nearly full azimuthal coverage around the beam axis: the Liquid Argon (LAr) calorimeter and the Tile calorimeter, as shown in Figure 2.4.

Spatial segmentation in calorimeters allows measurement of the direction and position of showers. Calorimeter measurements also provide the basis for calculating MET, which is essential for identifying non-interacting particles such as neutrinos.

Figure 2.4: Cut-away view of the ATLAS calorimeter system [15].

## Liquid Argon (LAr) Calorimeters

The ATLAS liquid argon (LAr) calorimeters are sampling calorimeters that use liquid argon as the active medium and dense metals as absorbers. Liquid argon is chosen for its excellent radiation tolerance and stable, linear response. Operation requires cryogenic cooling to about 87 K inside hermetically sealed cryostats to ensure signal quality and avoid contamination [7].

The system includes four main sections:

- Electromagnetic Barrel: covers the central region up to  $|\eta| < 1.475$ .

- Electromagnetic Endcaps: extend coverage to  $1.375 < |\eta| < 3.2$ .

- Hadronic Endcaps: positioned behind the electromagnetic endcaps and covering the same  $\eta$  range.

- Forward Calorimeter: extends coverage to the forward region  $3.1 < |\eta| < 4.9$ .

The electromagnetic barrel and endcap calorimeters use an accordion geometry to provide continuous azimuthal coverage. Copper electrodes are embedded between lead absorber plates, dividing the argon gap into two half-gaps for bipolar signal readout. The accordion geometry also facilitates a fast signal readout by providing a short signal path to the front-end electronics located at the detector's inner and outer radii. The electromagnetic sections have a total thickness exceeding 22 radiation lengths in the barrel and 24 radiation lengths in the endcaps, ensuring full containment of electromagnetic showers.

#### 2.1. THE ATLAS DETECTOR

The hadronic endcap calorimeters consist of two independent wheels per endcap, segmented longitudinally by copper plates of 25 mm (inner wheel) and 50 mm (outer wheel) thickness. Combined with the electromagnetic calorimeter in front, the total depth corresponds to about 10 nuclear interaction lengths, which is sufficient to contain most high-energy hadronic showers in the endcap region for ATLAS physics requirements [7].

The forward calorimeters operate in the high-radiation forward region. They provide an almost full  $\eta$  coverage as needed to measure  $E_T^{\text{miss}}$ , and help to shield the muon spectrometer. The absorbers are in copper for the electromagnetic section and in tungsten for the hadronic section. Each forward calorimeter module contains three longitudinal segments: the innermost copper section optimized for electromagnetic energy measurements, and two tungsten sections optimized for hadronic energy.

The bipolar ionization signals from the LAr calorimeters are shaped and amplified in the front-end boards. Shaping times of approximately 400 ns optimize noise performance while limiting pile-up sensitivity. The shaped signals are sampled every 25 ns and stored in pipeline memories deep enough to accommodate the 2.5 µs L1 trigger latency.

Starting in Run-3, the front-end boards on the trigger path perform real-time digital processing to form trigger primitives, namely a summary of energy collected over a specific, predefined region of the calorimeter. The granularity of these primitives was improved in the barrel electromagnetic layers, with layer-specific energy readout enabling improved shower-shape discrimination [15]. These digital sums provide the input to the calorimeter-based trigger selection system, described later in Section 2.2.1.

### Tile Calorimeter

The Tile calorimeter, located immediately outside the electromagnetic barrel, covers the central region up to  $|\eta| < 1.7$ . It consists of a barrel section and two extended barrels, segmented azimuthally into 64 modules. Radially, the calorimeter is divided into three layers. The system provides a total depth of approximately 9.7  $\lambda$  at  $\eta = 0$ , ensuring sufficient energy containment for hadronic showers.

The Tile calorimeter is also a sampling calorimeter, using plastic scintillating tiles as the active medium and iron plates as absorbers. Scintillation light produced in the tiles is collected via wavelength-shifting fibers and directed to photomultiplier tubes.

Photomultiplier signals are shaped with a fast bipolar shaper ( $\tau \approx 50 \,\mathrm{ns}$ ) to suppress out-of-time pile-up, then digitized every 25 ns and stored in front-end pipeline memory pending the trigger decision.

In parallel, a low-latency analog summation path combines photomultiplier signals into fixed  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$  trigger-tower sums. These analog sums are transmitted and digitized in preprocessor modules for use in the calorimeter trigger system.

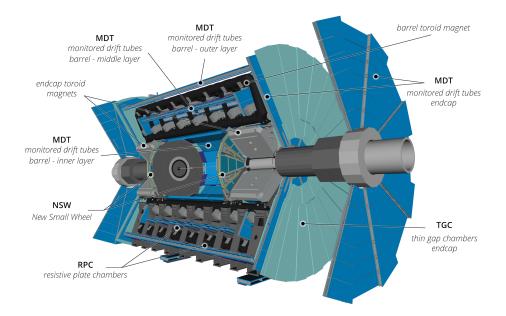

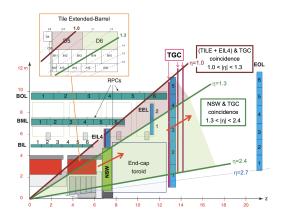

## 2.1.5 Muon Spectrometer

The muon spectrometer is the outermost sub-detector of ATLAS, designed to identify muons and measure their momentum with high precision. It provides standalone momentum measurements in the pseudorapidity range  $|\eta| < 2.7$ , and contributes to the L1 muon trigger up to  $|\eta| < 2.4$ . The system achieves a momentum resolution of about 3% at  $p_T = 100 \,\text{GeV}$  and  $\sim 10\%$  at  $p_T = 1 \,\text{TeV}$  [21].

Muon momentum is determined from the sagitta s of the curved trajectory in the magnetic field generated by the barrel and endcap toroid magnets (see subsection 2.1.2). The sagitta is the maximum perpendicular distance between the reconstructed track and the straight-line chord connecting its entry and exit points in the magnetic field. The toroid field strength is typically sufficient to produce measurable curvature even for high- $p_T$  muons (e.g. sagitta of about 0.5 mm for  $p_T = 1$  TeV compared to a  $\sim 50 \,\mu$ m measurement precision) [21, 14].

The spectrometer combines precision tracking chambers with fast trigger detectors:

- Precision tracking: Monitored Drift Tubes (MDTs) throughout most of the spectrometer, complemented by Micromegas (MM) in the forward region.

- Trigger detectors: Resistive Plate Chambers (RPCs) in the barrel, Thin Gap Chambers (TGCs) in the endcaps, and small-strip TGCs (sTGCs) in the upgraded forward region.

The barrel region contains three concentric cylindrical layers of detectors with an eight-fold  $\phi$  symmetry, split into 16 sectors (eight large, eight small). In the endcaps, detectors are arranged into the "Small Wheel" (innermost) and "Big Wheel" (outermost) structures. Each set of layers with similar geometry is referred to as a station. Starting from Run-3 the New Small Wheel replaces the innermost forward muon station in the region  $1.3 < |\eta| < 2.7$  with detectors capable of both precision tracking and fast triggering under high background conditions. It integrates MM for precision tracking and sTGCs for triggering [15]. This combined system allows the New Small Wheel to deliver triggers with improved spatial and timing resolution, essential for suppressing beam-related background and maintaining high trigger efficiency in the forward region. Figure 2.5 shows the ATLAS muon spectrometer system.

#### **Precision Tracking Detectors**

• Monitored Drift Tubes – MDTs provide high-precision tracking across most of the spectrometer. Each drift tube is a 30 mm diameter aluminum cylinder filled with 93% Ar and 7% CO<sub>2</sub> at 3 bar pressure [15]. A 50 μm gold-plated tungsten—rhenium wire runs along the central axis as the anode, with the tube wall serving as the

#### 2.1. THE ATLAS DETECTOR

Figure 2.5: Cut-away view of the ATLAS muon spectrometer [15].

cathode [21]. Electrons from ionization drift toward the wire, with a maximum drift time of about 700 ns [22]. MDTs are not used in the L1 trigger due to this relatively long drift time, but are essential for offline momentum reconstruction and for refining muon candidates at the HLT. The Phase-I upgrade introduced small MDTs (sMDTs) with 15 mm tube diameter, halving drift times and increasing granularity [15].

• Micromegas – Micromegas detectors are parallel-plate gaseous chambers with separate drift and amplification regions. They achieve typical spatial resolutions of 100 µm and can handle hit rates up to 15 kHz/cm² [23]. The drift gap (5 mm) is operated at 600 V/cm, while the amplification gap (128 µm) operates at 40 to 50 kV/cm [23]. They provide a timing resolution of 5 ns to 10 ns, sufficient to reject of out-of-time backgrounds and to ensure time-coincidence with the TGC trigger signal.

The micromesh between the drift and amplification gaps blocks the majority of avalanche ions, resulting in an ion backflow fraction of only 1–2% at nominal operating fields [23]. This suppression prevents space-charge build-up and preserves spatial and timing performance even at maximum hit rates.

#### **Trigger Detectors**

The trigger detectors provide fast bunch crossing identification and coarse position measurements to seed muon reconstruction. They are designed for nanosecond-level timing resolution, ensuring correct bunch crossing assignment.

• Resistive Plate Chambers – RPCs are parallel-plate gaseous detectors used in

the barrel region ( $|\eta| < 1.05$ ). Each chamber consists of two resistive bakelite plates separated by a 2 mm gas gap, filled with a mixture of 94.7%  $C_2H_2F_4$ , 5%  $C_4H_{10}$ , and 0.3%  $SF_6$ . High voltage of about 9.6 kV is applied across the plates, producing fast avalanches with signal rise times of  $\mathcal{O}(1 \text{ ns})$ . Copper readout strips on the external surfaces of the plates provide measurements in both the  $\eta$  and  $\phi$  views. On-detector front-end cards amplify and discriminate the signals, which are then combined in coincidence matrices to select patterns compatible with muon trajectories. Typical performance includes a time resolution of about 2.5 ns and spatial resolution of 2 cm in  $\eta$  [21].

- Thin Gap Chambers TGCs are multiwire proportional chambers used in the endcap region (1.05 <  $|\eta|$  < 2.4). Each chamber has closely spaced anode wires (1.8 mm pitch) stretched between cathode planes, operated in a gas mixture of 55% CO<sub>2</sub> and 45% n-pentane. This mixture provides high gas gain while suppressing secondary discharges. Readout strips measure the  $\phi$  coordinate, while anode wires provide the  $\eta$  coordinate and precise timing. Signals are processed by on-detector electronics for amplification, shaping, and discrimination before entering pattern-recognition logic. The typical time resolution is 4 ns, sufficient for unambiguous bunch-crossing identification [21]. Spatial resolution is in the order of 4 mm [14].

- Small Thin Gap Chambers The sTGCs are similar in operating principle to standard TGCs but with finer strip segmentation, achieving spatial resolutions of a few hundred µm. They are arranged in quadruplets, with pad electrodes providing coarse hit position information and strips refining the coordinate measurement. On-detector electronics perform fast amplification, shaping, and discrimination; pad signals are processed in dedicated pad trigger ASICs running at 40 MHz for bunch-crossing identification. Strip data are buffered locally for matching with pad coincidences.

# 2.1.6 Specialized forward detectors

In addition to the main sub-detectors, several small forward systems are used primarily for timing, luminosity monitoring, and targeting forward physics signatures.

• ATLAS Forward Proton Detectors (AFP) – The AFP system is located symmetrically on both sides of the ATLAS interaction point, with two "NEAR" stations at  $z \approx \pm 205$  m and two "FAR" stations at  $z \approx \pm 217$  m [24]. Each station houses four planes of 3D silicon pixel tracking detectors, tilted to improve spatial resolution to about 6  $\mu$ m in the horizontal direction. The FAR stations additionally host time-of-flight detectors, providing timing resolutions of  $\mathcal{O}(20 \text{ ps})$  in optimal conditions.

#### 2.1. THE ATLAS DETECTOR

The AFP measures intact protons scattered at very small angles in diffractive and photon-induced processes, enabling precise reconstruction of the proton fractional energy loss<sup>1</sup> and vertex position for exclusive event selection.

- Beam Conditions Monitor (BCM) The BCM employs diamond sensors with a high voltage applied across them to detect the passage of charged particles. It is positioned near the beam pipe at  $z=\pm 1.84$  m. The BCM provides bunch-by-bunch luminosity measurements and beam loss detection with sub-nanosecond timing resolution [14, 15].

- Beam Pick-up Timing (BPTX) The BPTX system consists of electrostatic button pick-up detectors located at  $z=\pm 175$  m from the ATLAS interaction point [25]. The signals are used both in the ATLAS Level-1 trigger to provide a bunch-passage reference and in a dedicated monitoring system to measure the phase between the LHC clock and the beam with better than 100 ps precision. The system also provides bunch-by-bunch intensity and longitudinal structure measurements, and is crucial for ensuring correct synchronization of detector readout with collisions.

- Beam Loss Monitors (BLM) The BLM system protects LHC magnets and other sensitive components by detecting beam losses with ionization chambers and secondary emission monitors placed at critical locations around the ring [26]. In ATLAS, forward BLM devices close to the experiment are used to monitor losses near the interaction region, aiding both machine protection and background diagnostics for physics analyses. They have a large dynamic range, fast response (down to a single LHC turn, 89 µs), and are integrated into the LHC interlock system to request a beam dump if thresholds are exceeded. The forward BLM devices are located at various positions from a few meters to about 250 m from the interaction point in both beam directions [26].

- Minimum-Bias Trigger Scintillators (MBTS) The MBTS is a scintillator detector located on the inner face of the endcap cryostats at z = ±3.6 m. The MBTS are used for triggering events in minimum-bias and forward physics, as well as for measuring luminosity. Thanks to their position, they detect low-energy particles produced at the edges or in the peripheral regions of a collision, helping to select events that are important for studying background processes and the beam's conditions [14].

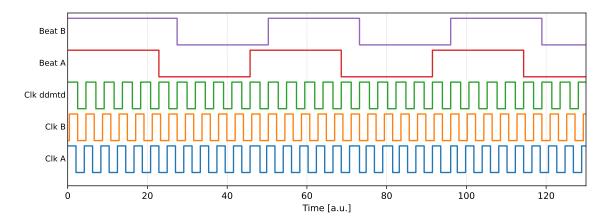

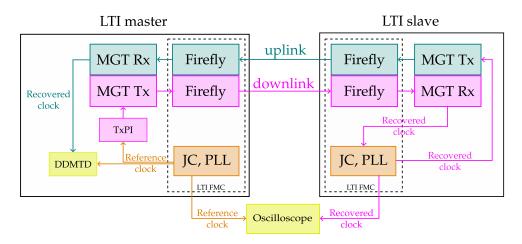

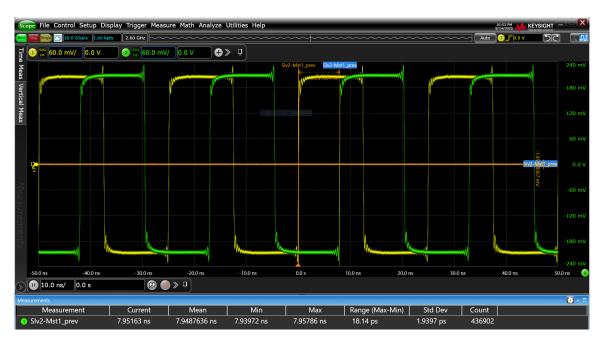

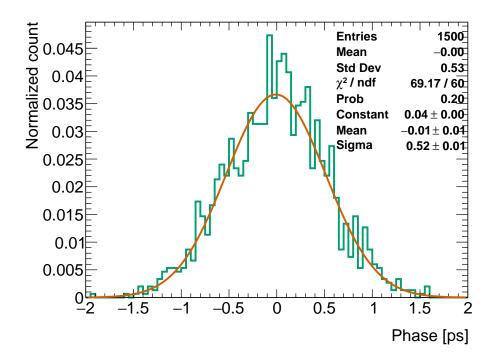

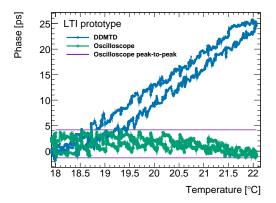

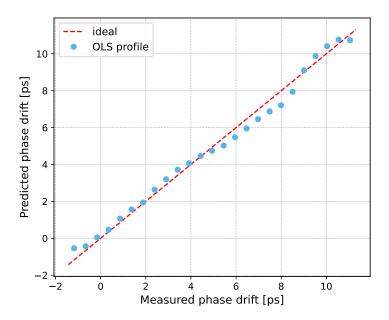

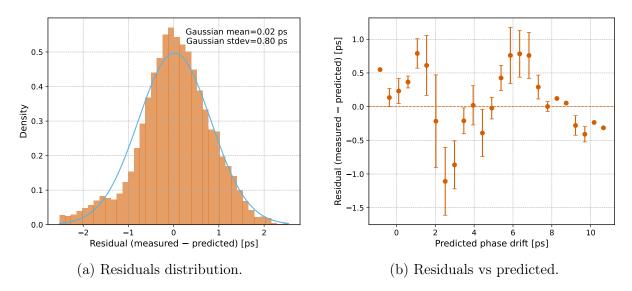

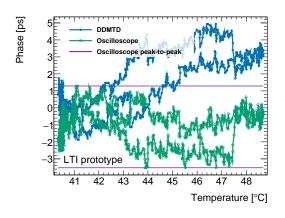

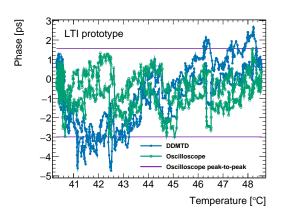

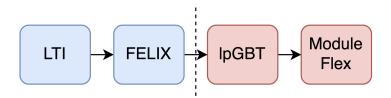

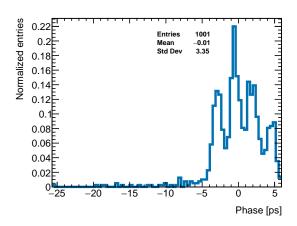

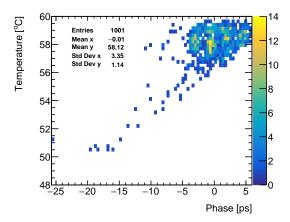

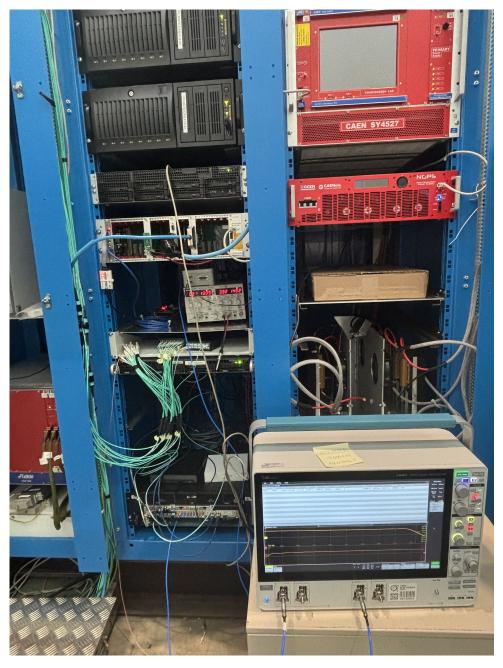

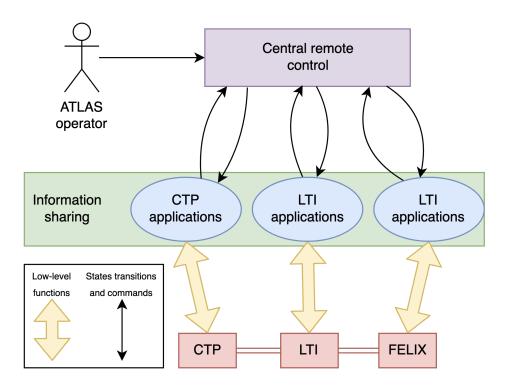

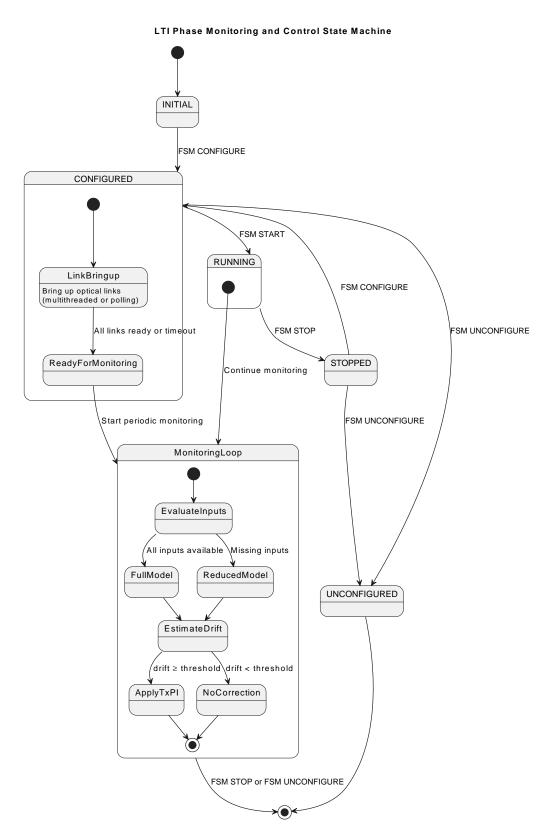

$<sup>^1{\</sup>rm The}$  fraction of the original LHC beam energy that a scattered proton has lost after the interaction at the ATLAS IP