## Dissertation

submitted to the Combined Faculties for the Natural Sciences and for Mathematics

of the Ruperto-Carola University of Heidelberg, Germany

for the degree of Doctor of Natural Sciences

presented by Dipl.-Phys. Daniel Brüderle born in Offenburg, Germany

Date of oral examination: July 8, 2009

# Neuroscientific Modeling with a Mixed-Signal VLSI Hardware System

Referees: Prof. Dr. Karlheinz Meier Prof. Dr. Alain Destexhe

## Abstract

### Neuroscientific Modeling with a Mixed-Signal VLSI Hardware System

Modeling networks of spiking neurons is a common scientific method that helps to understand how biological neural systems represent, process and store information. But the simulation of large-scale models on machines based on the Turing paradigm is subject to performance limitations, since it suffers from an intrinsic discrepancy to the massive parallelism of neural processing in the brain. Following an alternative approach, neuromorphic engineering implements the structure and function of biological neural systems in analog or analog-digital VLSI devices. Neuron and synapse circuits represent physical models that evolve in parallel and in continuous time. Therefore, neuromorphic systems can overcome limitations of pure software approaches in terms of speed and scalability. Recent developments aim at the realization of large-scale, massively accelerated and highly configurable neuromorphic architectures. This thesis presents a novel methodological framework that renders possible the beneficial utilization of such devices as neuroscientific modeling tools. In a comprehensive study, it describes, tests and characterizes an existing prototype in detail. It presents policies for the biological interpretation of the hardware output and techniques for the calibration of the chip. The thesis introduces a dedicated software framework that implements these methods and integrates the hardware interface into a simulator-independent modeling language, which is also supported by various established software simulators. This allows to port experiment descriptions between hardware and software simulators, to compare generated output data and consequently to verify the hardware model. The functionality of the translation methods, the calibration techniques and the verification framework are shown in various experiments both on the single cell and on the network level.

## Neurowissenschaftiches Modellieren mit einer Analog-Digitalen VLSI Hardware

Die Modellierung pulsgekoppelter neuronaler Netzwerke ist eine übliche wissenschaftliche Methode um die Kodierung, die Verarbeitung und die Speicherung von Information in biologischen neuronalen Systemen zu verstehen. Bei der Simulation großskaliger Modelle auf Computern, die nach dem Turingprinzip arbeiten, ergeben sich jedoch Performanzeinbußen aufgrund der Diskrepanz zur intrinsisch hochparallelen Verarbeitungsweise im Gehirn. Einen alternativen Ansatz dazu stellen neuromorphe Hardwaresysteme dar, die die Struktur und Funktion biologischer neuronaler Systeme in analoger oder gemischt analog-digitaler hochintegrierter Schaltungstechnik emulieren. Die Neuronen- und Synapsenschaltungen sind dabei physikalische Modelle, die sich parallel und zeitlich kontinuierlich entwickeln. Daher sind neuromorphe Systeme in der Lage, die Geschwindigkeitsund Skalierungsbeschränkungen reiner Softwarelösungen zu überwinden. Derzeit werden großskalige, massive beschleunigte und hoch konfigurierbare neuromorphe Architekturen entwickelt. Diese Doktorarbeit präsentiert ein neuartiges methodisches Konzept, das die Verwendung solcher Systeme für neurowissenschaftliches Modellieren ermöglicht. Ein bereits verfügbarer Prototyp wird detailliert beschrieben und umfassend getestet. Es werden Techniken eingeführt, die es erlauben, die Ausgabe der Hardware biologisch zu interpretieren und den Chip zu kalibrieren. Software, die im Rahmen dieser Arbeit vorgestellt wird, implementiert diese Methoden. Sie wurde in eine simulatorunabhängige Modellierungssprache eingebettet, die auch von etablierten Software-Simulatoren unterstützt wird. Dadurch können Experimentbeschreibungen zwischen Hardware und Software-Simulatoren ausgetauscht, erzeugte Ergebnisdaten verglichen und damit auch das Hardwaremodell verifiziert werden. Es werden Experimente an einzelnen Neuronen und ganzen Netzwerken präsentiert, die die Funktionalität der Übersetzungs- und Kalibrierungsmethoden sowie des Verifikationsprinzips bestätigen.

# Contents

| Introduction |                                           |         |                                                             |    |  |  |  |  |

|--------------|-------------------------------------------|---------|-------------------------------------------------------------|----|--|--|--|--|

| 1            | Neuroscience and Neuromorphic Engineering |         |                                                             |    |  |  |  |  |

|              | 1.1                                       | The W   | Vorld in the Mind                                           | 7  |  |  |  |  |

|              | 1.2                                       | Moder   | rn Neuroscience – Methods and Models                        | 8  |  |  |  |  |

|              |                                           | 1.2.1   | Studying the Brain                                          | 8  |  |  |  |  |

|              |                                           | 1.2.2   | Insights through Modeling                                   | 11 |  |  |  |  |

|              |                                           | 1.2.3   | Software Simulators vs. Neuromorphic Hardware               | 11 |  |  |  |  |

|              |                                           | 1.2.4   | Requirements for the Establishment of Neuromorphic Modeling | 13 |  |  |  |  |

|              | 1.3                                       | Utilize | ed Neuroscientific Concepts                                 | 14 |  |  |  |  |

|              |                                           | 1.3.1   | High-Conductance States                                     | 14 |  |  |  |  |

|              |                                           | 1.3.2   | Models of Synapse Response Dynamics                         | 15 |  |  |  |  |

|              |                                           | 1.3.3   | Synaptic Learning                                           | 16 |  |  |  |  |

|              | 1.4                                       | The F.  | ACETS Research Project                                      | 17 |  |  |  |  |

|              |                                           |         | 0                                                           |    |  |  |  |  |

| 2            | Neu                                       | -       | ohic Substrate                                              | 19 |  |  |  |  |

|              | 2.1                                       | Chip-I  | Based Neural Network Model                                  | 19 |  |  |  |  |

|              |                                           | 2.1.1   | Technology and Dimensions                                   | 19 |  |  |  |  |

|              |                                           | 2.1.2   | Implemented Model                                           | 20 |  |  |  |  |

|              |                                           | 2.1.3   | Synaptic Plasticity                                         | 25 |  |  |  |  |

|              |                                           | 2.1.4   | Configurability, Ranges and Precision                       | 27 |  |  |  |  |

|              |                                           | 2.1.5   | Stack of Hardware Communication Layers                      | 31 |  |  |  |  |

|              | 2.2                                       | Wafer-  | -Scale Neural Network Model                                 | 34 |  |  |  |  |

|              |                                           | 2.2.1   | Technology and Dimensions                                   | 35 |  |  |  |  |

|              |                                           | 2.2.2   | Implemented Model                                           | 35 |  |  |  |  |

|              |                                           | 2.2.3   | Configurability of the System                               | 37 |  |  |  |  |

|              |                                           | 2.2.4   | Stack of Hardware Communication Layers                      | 38 |  |  |  |  |

| ~            | •                                         |         |                                                             |    |  |  |  |  |

| 3            |                                           |         | nd Techniques                                               | 41 |  |  |  |  |

|              | 3.1                                       | -       | tion Paradigms                                              | 41 |  |  |  |  |

|              |                                           | 3.1.1   | Intended Scenarios of Usage                                 | 42 |  |  |  |  |

|              |                                           | 3.1.2   | Existing Hardware Interfaces                                | 43 |  |  |  |  |

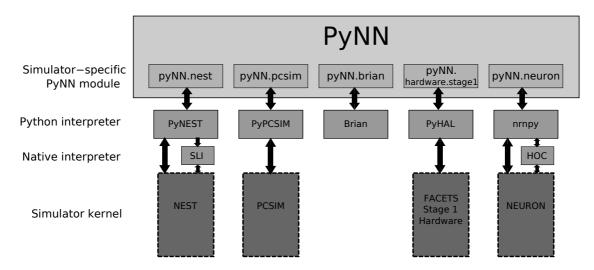

|              |                                           | 3.1.3   | Back-End Agnostic Description and Analysis                  | 44 |  |  |  |  |

|              |                                           | 3.1.4   | Reference Software Simulators                               | 48 |  |  |  |  |

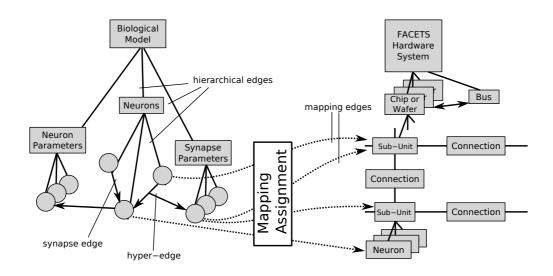

|              |                                           | 3.1.5   | Neuron and Synapse Model Mapping                            | 49 |  |  |  |  |

|              |                                           | 3.1.6   | Network Topology Mapping                                    | 53 |  |  |  |  |

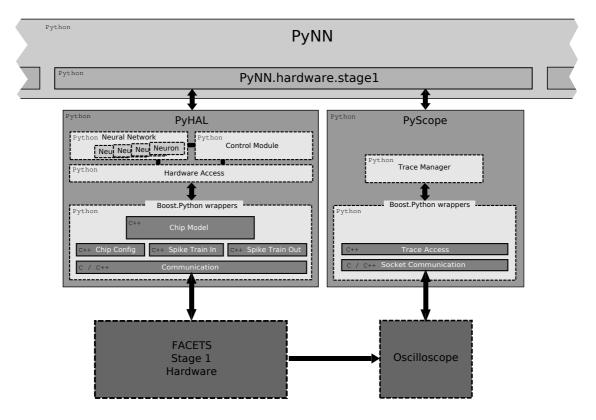

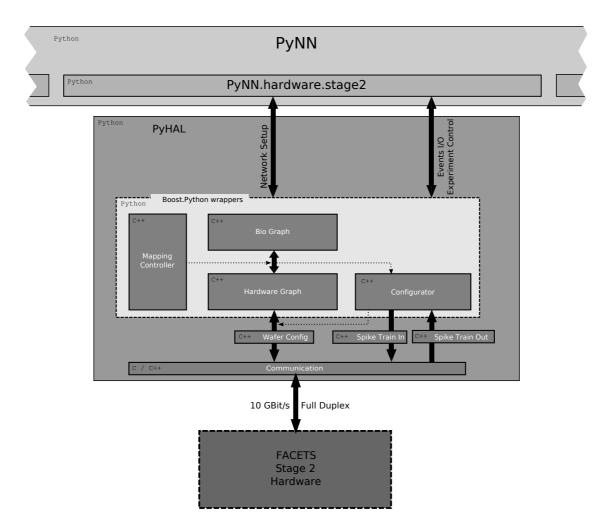

|              | 3.2                                       |         | are Architecture                                            | 57 |  |  |  |  |

|              |                                           | 3.2.1   | Utilized Technologies                                       | 57 |  |  |  |  |

|              |                                           | 3.2.2   | Software Layer Stack                                        | 59 |  |  |  |  |

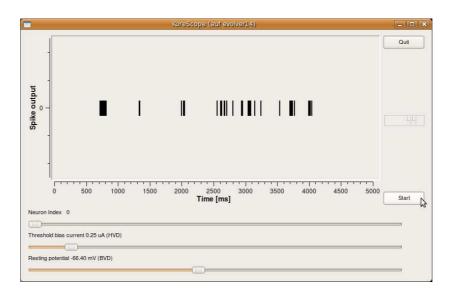

|              |                                           | 3.2.3   | High-Level Software Tools                                   | 64 |  |  |  |  |

|   |                                                | 3.2.4   | Management of Multiple Users and Systems                              | 66  |  |  |  |  |

|---|------------------------------------------------|---------|-----------------------------------------------------------------------|-----|--|--|--|--|

|   |                                                | 3.2.5   | Analog Unit Test Framework                                            | 67  |  |  |  |  |

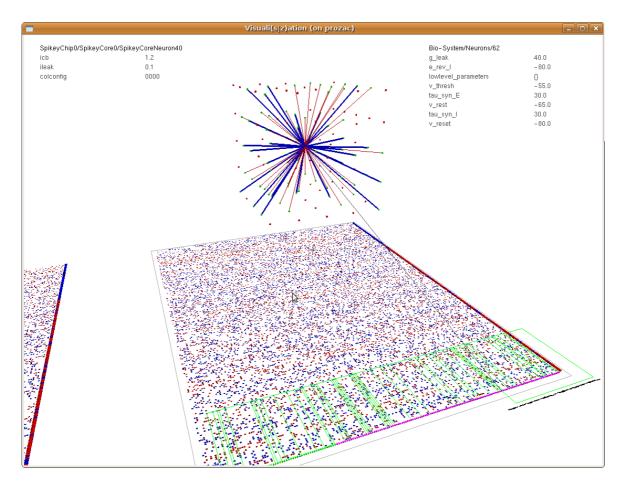

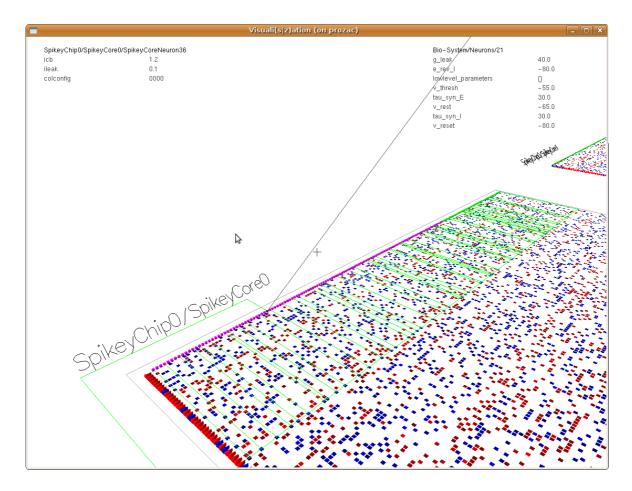

|   |                                                | 3.2.6   | 3D Visualization of Network Mapping                                   | 68  |  |  |  |  |

| 4 | Gair                                           | ning Co | ntrol of Chip Functionality and Imperfections                         | 73  |  |  |  |  |

| - | 4.1                                            | -       | bds for Indirect Access                                               | 73  |  |  |  |  |

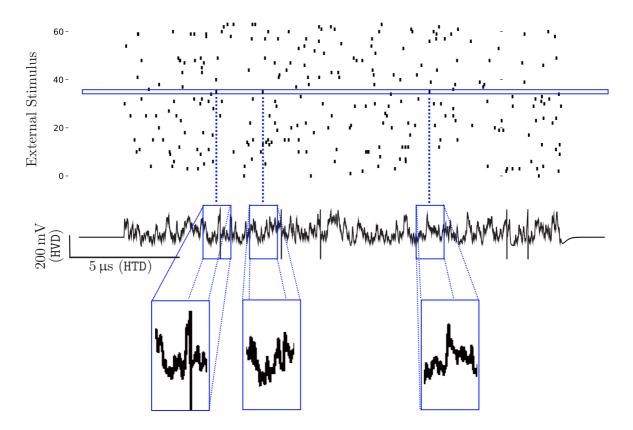

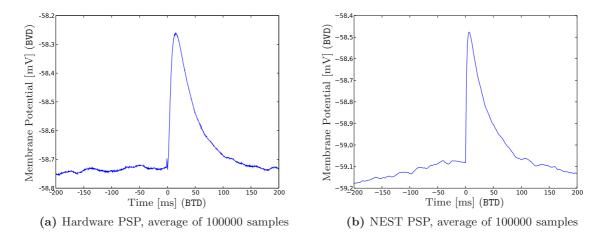

|   | 1.1                                            | 4.1.1   | Spike-Triggered Averaging on Neuromorphic Hardware                    | 74  |  |  |  |  |

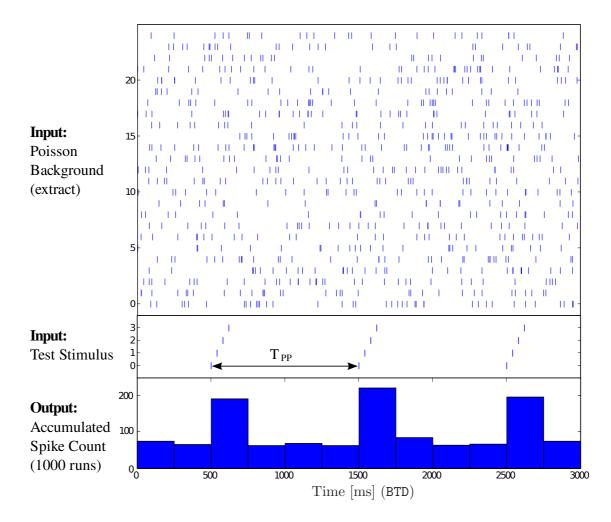

|   |                                                | 4.1.2   | High-Conductance State Test                                           | 76  |  |  |  |  |

|   |                                                | 4.1.3   | Long-Term Plasticity                                                  | 86  |  |  |  |  |

|   |                                                | 4.1.4   | Membrane Time Constants                                               | 88  |  |  |  |  |

|   | 4.2                                            |         | ss-Inherent Imperfections                                             | 91  |  |  |  |  |

|   |                                                | 4.2.1   | Hardware Production                                                   | 91  |  |  |  |  |

|   |                                                | 4.2.2   | Electronic Noise                                                      | 92  |  |  |  |  |

|   | 4.3                                            | Protot  | type-Specific Malfunctions and Design-Related Interferences           | 96  |  |  |  |  |

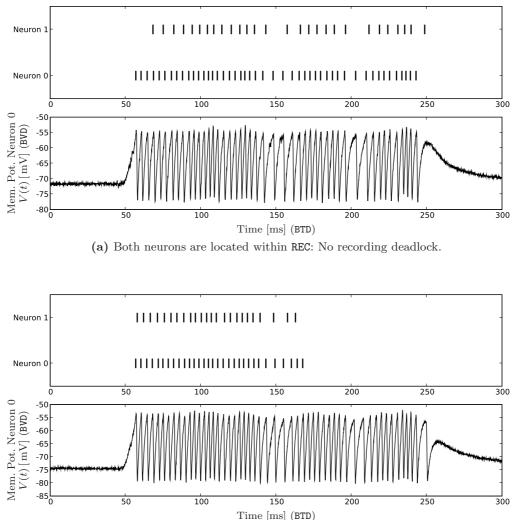

|   | -                                              | 4.3.1   | Spike Recording Deadlocks                                             | 96  |  |  |  |  |

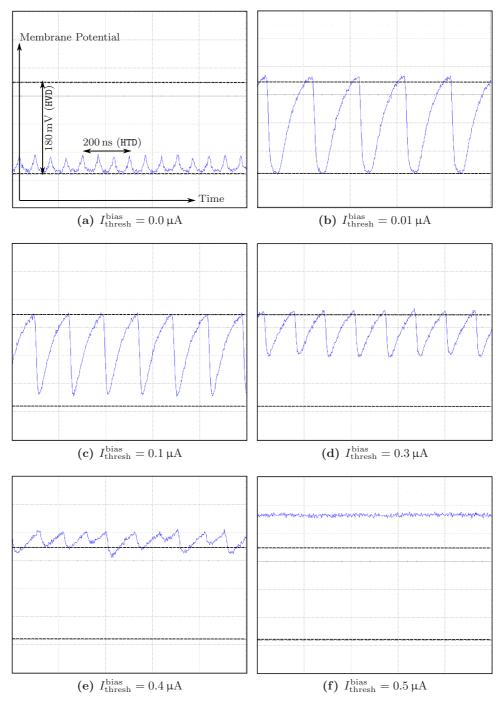

|   |                                                | 4.3.2   | Firing Threshold vs. Reset Potential                                  | 99  |  |  |  |  |

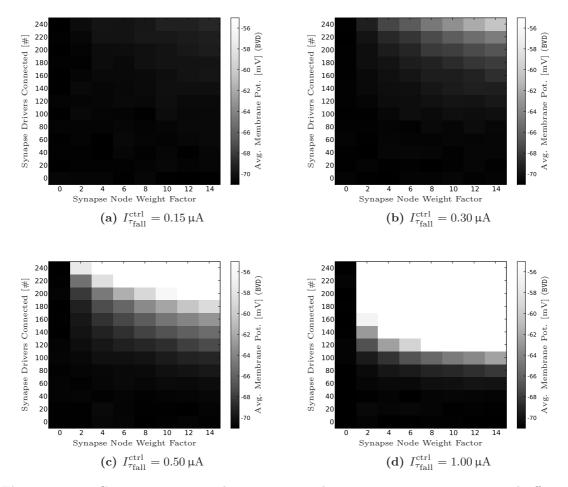

|   |                                                | 4.3.3   | Parasitic Resting Potential Offsets                                   | 102 |  |  |  |  |

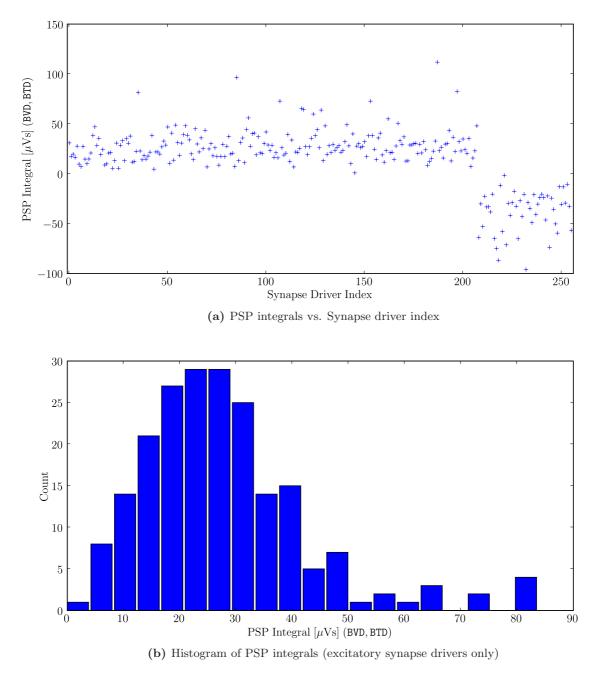

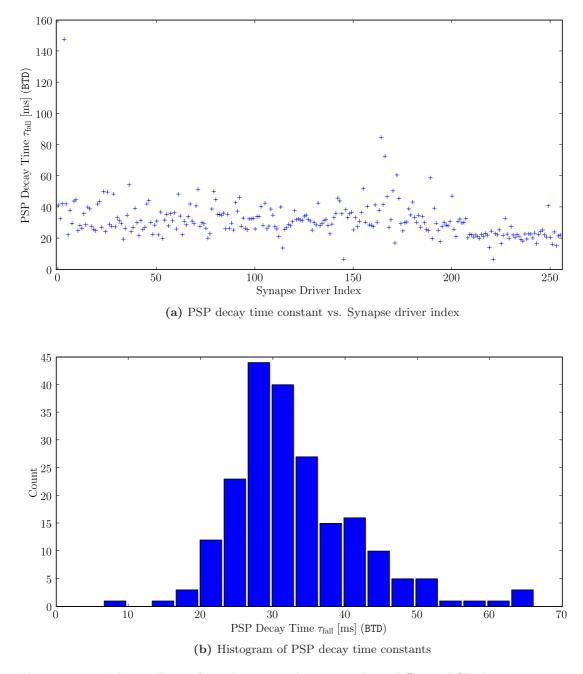

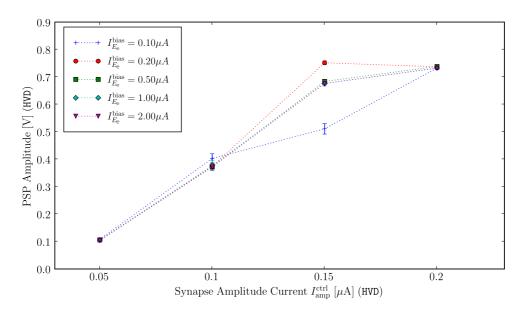

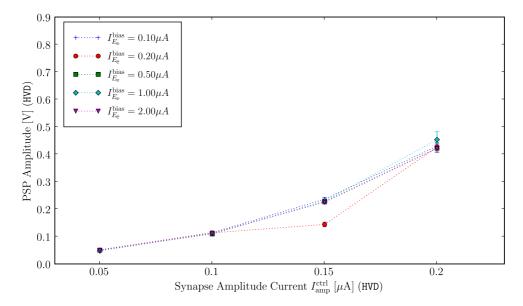

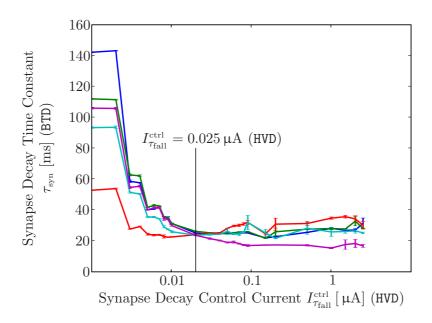

|   |                                                | 4.3.4   | Synapse Driver Efficacies and Time Constants                          | 104 |  |  |  |  |

|   |                                                | 4.3.5   | Dis-Proportionality of Intrinsic Time Constants                       | 109 |  |  |  |  |

|   |                                                | 4.3.6   | Multi-Spikes                                                          | 110 |  |  |  |  |

|   |                                                | 4.3.7   | Limited Spike Input and Output Bandwidth                              | 110 |  |  |  |  |

|   |                                                | 4.3.8   | Crosstalk of Digital Activity                                         | 111 |  |  |  |  |

|   |                                                | 4.3.9   | Clock Problems                                                        | 112 |  |  |  |  |

|   |                                                | 4.3.10  | Insufficient Parameter Range for Synaptic Facilitation and Depression | 113 |  |  |  |  |

|   |                                                | 4.3.11  | STDP Control Problems                                                 | 113 |  |  |  |  |

|   |                                                | 4.3.12  | Spontaneous Ghost Events                                              | 114 |  |  |  |  |

| 5 | Establishing Biologically Realistic Regimes 11 |         |                                                                       |     |  |  |  |  |

| - | 5.1                                            |         | ing of Chip Imperfections                                             | 115 |  |  |  |  |

|   |                                                | 5.1.1   | Releasing Recording Deadlocks                                         |     |  |  |  |  |

|   |                                                | 5.1.2   | Clamping Synapse Driver Base Lines                                    |     |  |  |  |  |

|   |                                                | 5.1.3   | Avoiding Time Bin Losses                                              |     |  |  |  |  |

|   |                                                | 5.1.4   | Providing Sufficiently Low Reference Voltages                         | 117 |  |  |  |  |

|   |                                                | 5.1.5   | Achieving Sufficient Parameter Ranges                                 | 117 |  |  |  |  |

|   | 5.2                                            | Hardw   | vare Calibration                                                      | 118 |  |  |  |  |

|   |                                                | 5.2.1   | Voltage Generator Calibration                                         | 118 |  |  |  |  |

|   |                                                | 5.2.2   | Firing Threshold and Reset Mechanism Calibration                      | 119 |  |  |  |  |

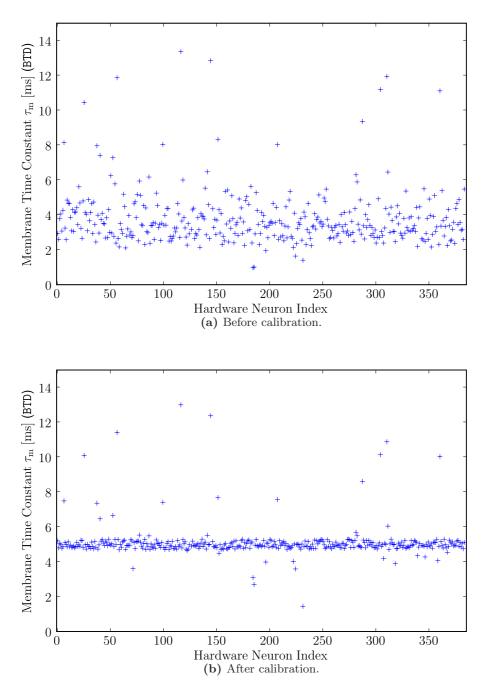

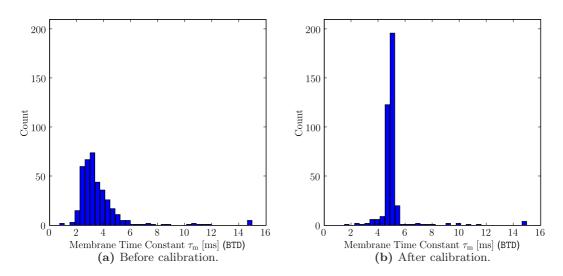

|   |                                                | 5.2.3   | Membrane Time Constant Calibration                                    | 120 |  |  |  |  |

|   |                                                | 5.2.4   | Synapse Dynamics Calibration                                          | 124 |  |  |  |  |

|   |                                                | 5.2.5   | Synapse Weights Calibration                                           | 132 |  |  |  |  |

|   |                                                | 5.2.6   | Calibration Reproducibility and Portability                           | 135 |  |  |  |  |

|   | 5.3                                            | Measu   | res for Cross-Platform Evaluation                                     | 137 |  |  |  |  |

|   |                                                | 5.3.1   | Spike Train Comparison                                                | 137 |  |  |  |  |

|   |                                                | 5.3.2   | Statistical Descriptors of Network Activity                           | 138 |  |  |  |  |

| 6 | Exp                                            | eriment | ts                                                                    | 141 |  |  |  |  |

| - | 6.1                                            |         | Studies and Specifications                                            | 141 |  |  |  |  |

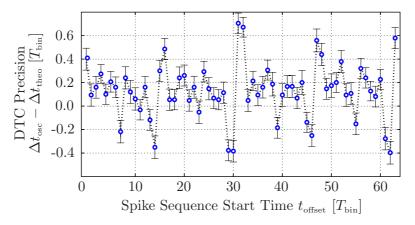

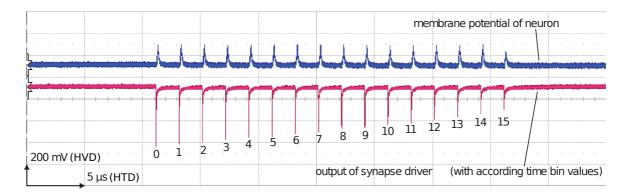

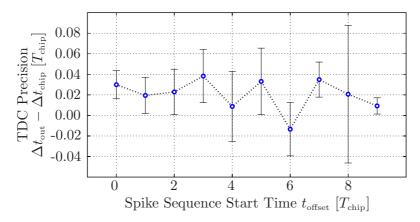

|     |                        | 6.1.1  | Spike Delivery Precision                                   | 142 |  |  |  |  |  |  |

|-----|------------------------|--------|------------------------------------------------------------|-----|--|--|--|--|--|--|

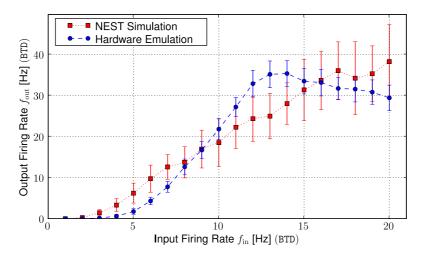

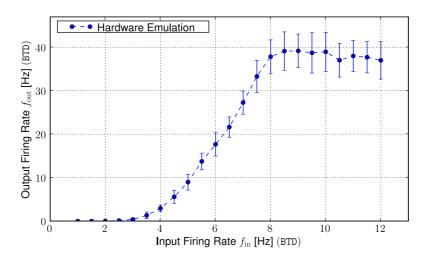

|     |                        | 6.1.2  | Firing Rates                                               | 145 |  |  |  |  |  |  |

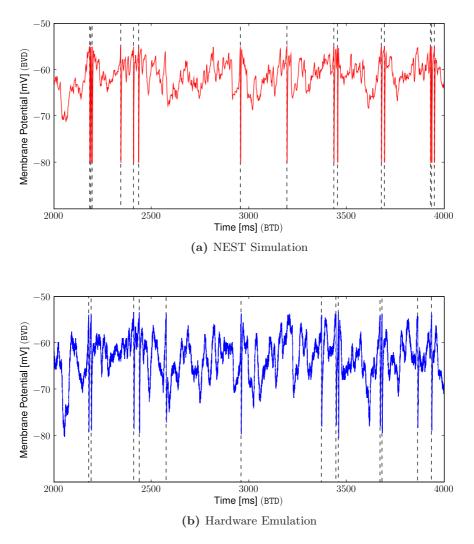

|     |                        | 6.1.3  | Membrane Potentials                                        | 149 |  |  |  |  |  |  |

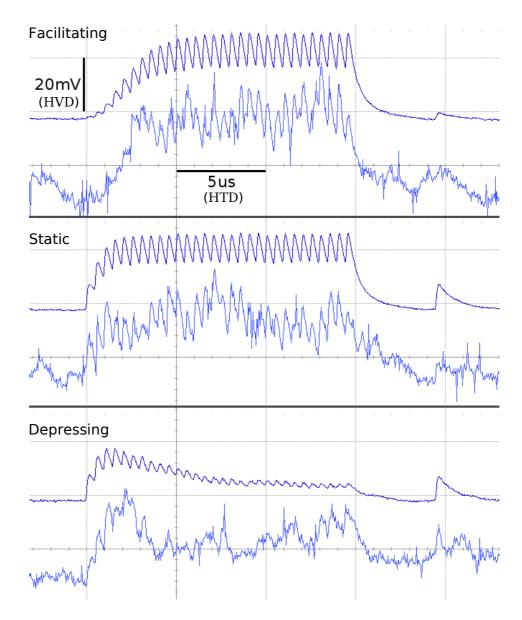

|     |                        | 6.1.4  | Short-Term Plasticity                                      | 152 |  |  |  |  |  |  |

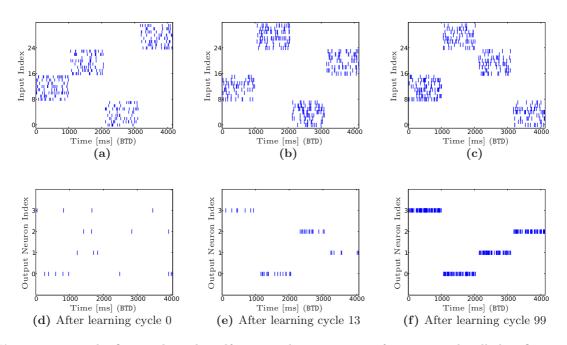

|     |                        | 6.1.5  | Long-Term Plasticity                                       | 154 |  |  |  |  |  |  |

|     | 6.2                    | Explor | ring Network Architectures                                 | 157 |  |  |  |  |  |  |

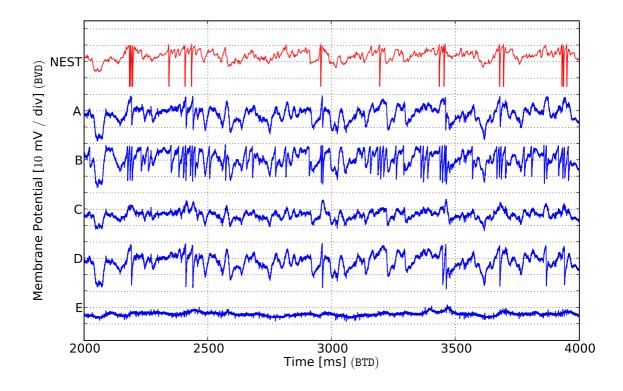

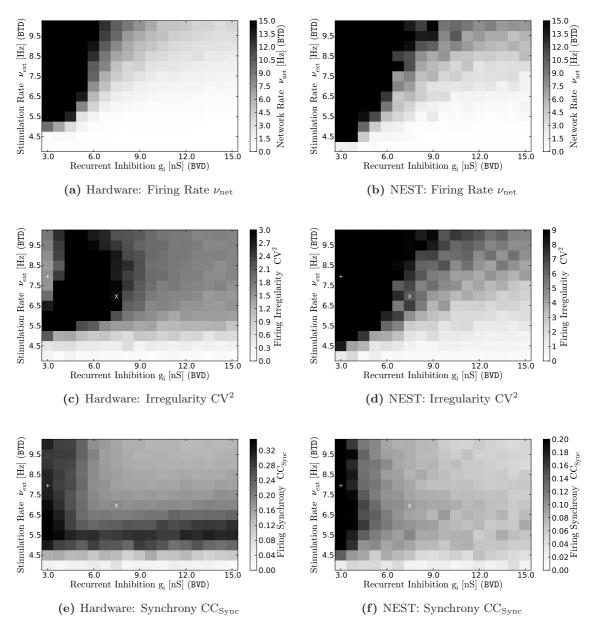

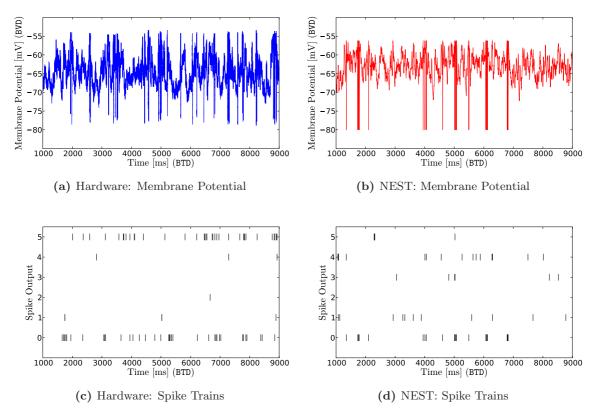

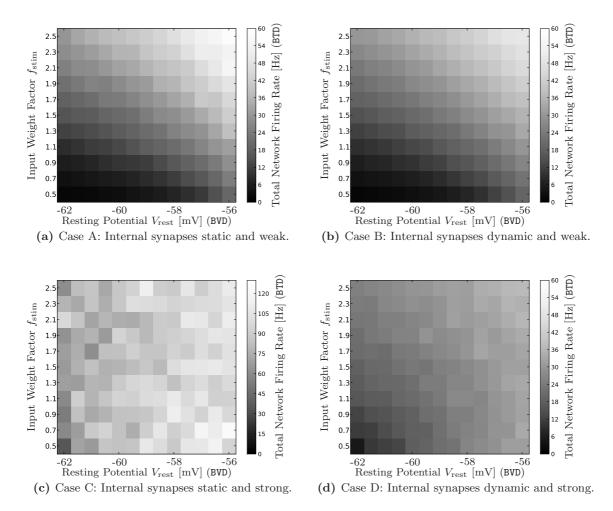

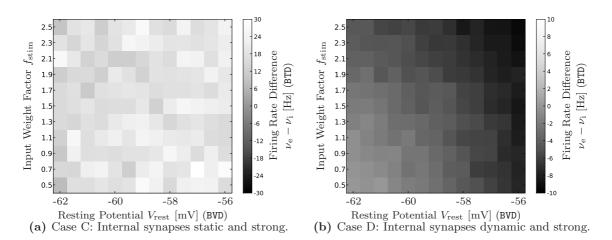

|     |                        | 6.2.1  | Recurrent Network Dynamics: Matching Hardware and Software | 157 |  |  |  |  |  |  |

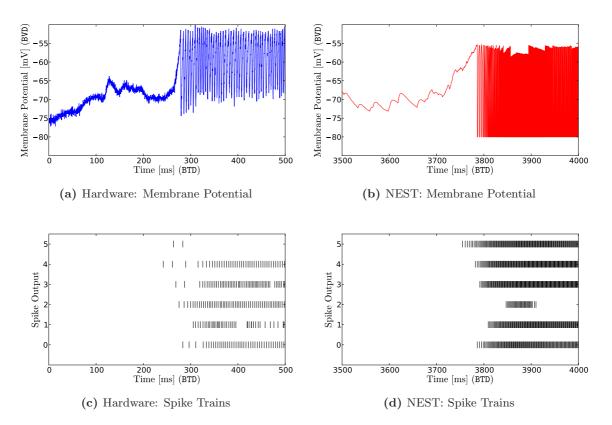

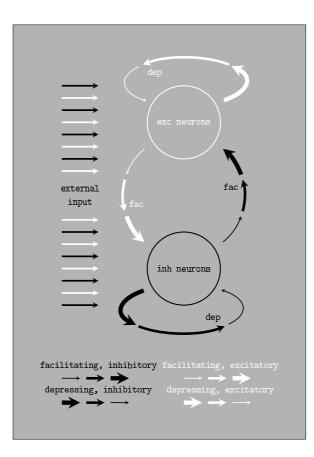

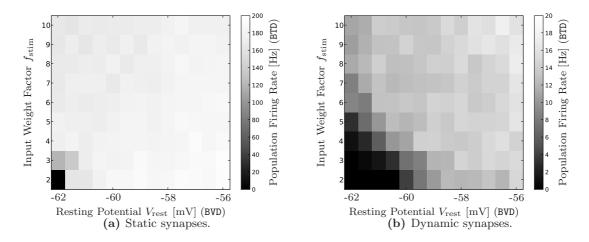

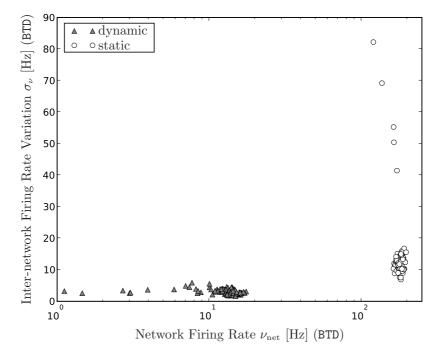

|     |                        | 6.2.2  | Self-Stabilizing Network Architectures                     | 175 |  |  |  |  |  |  |

| Co  | Conclusion and Outlook |        |                                                            |     |  |  |  |  |  |  |

| Α   | A Appendix             |        |                                                            |     |  |  |  |  |  |  |

|     | A.1                    | Simula | ation and Emulation Parameters                             | 196 |  |  |  |  |  |  |

|     | A.2                    | Source | e Code, Documentation and Licences                         | 197 |  |  |  |  |  |  |

|     | A.3                    | Works  | tation Information                                         | 199 |  |  |  |  |  |  |

|     |                        |        |                                                            | 100 |  |  |  |  |  |  |

|     | A.4                    |        | cal Recommendations for the FHW-1 Operation                | 202 |  |  |  |  |  |  |

| Lis |                        |        | cal Recommendations for the FHW-1 Operation                |     |  |  |  |  |  |  |

|     | t of .                 | Practi | cal Recommendations for the FHW-1 Operation                | 202 |  |  |  |  |  |  |

## Introduction

Investigating the brain is a scientific effort that does not need an extensive motivation. Understanding principles of neural information processing is a human concern as fundamental as questions on cosmology or particle physics. In contrast to this, the manifold and diverse methods that are applied in the field of neuroscience have to be permanently put into question. So far, the available approaches are not sufficient to reveal final explanations for all remarkable capabilities inherent to neural systems. Consequently, the technological aspects of neuroscience are subject to ongoing revisions, improvements and innovations. Section 1.2 lists techniques that significantly contributed to the current state of knowledge about neural systems.

Especially due to the technical and technological difficulties in accessing and monitoring the living brain, *modeling* represents an important approach within the spectrum of neuroscientific efforts. A large community of researchers develops models of different neural systems and thereby extracts important insights. These models represent various anatomical fractions of their biological original and incorporate different levels of detail regarding the utilized constituents and the applied structural complexity. Section 1.2.2 provides a selection of recent publications from that field.

One branch of the modeling community uses computers to numerically calculate the emerging dynamics of their models. Driven by the rapid development of available and affordable computational power during the last decades, the importance of this field has steadily grown. But the utilization of computers based on the Turing paradigm (Turing, 1937), i.e. that perform sequential transitions between discrete internal states using a small number of processing units, renders a discrepancy to the massive parallelism of analog neural computation. This implies performance problems (see e.g. Morrison et al., 2005), as will be discussed in Section 1.2.2.

An alternative approach is represented by implementing the structure and function of biological neural systems in analog or mixed-signal<sup>1</sup> VLSI<sup>2</sup> technology, often referred to as *neuromorphic systems* engineering (Mead, 1990; Cauwenberghs, 1999). Building upon the pioneering work of Carver Mead (Mead and Mahowald, 1988; Mead, 1989), electronic engineers have developed neuromorphic devices since the 1980s. They realized remarkable biologically inspired hardware implementations of spike-based information processing systems, such as silicon retinas (Delbrück and Liu, 2004; Serrano-Gotarredona et al., 2006), self-tuning motor control units for robotics (Lewis et al., 2000), attractor memory devices (Vogelstein et al., 2007), self-organizing pattern classifiers (Häfliger, 2007) and many more. Some further examples will be introduced in Section 1.2.3, and the potential, the advantages and the disadvantages of neuromorphic devices will be discussed.

But although the manifold applications are promising, neuromorphic engineering still represents a rather exotic niche within the variety of research fields in neuroscience. So far,

<sup>&</sup>lt;sup>1</sup>Chips that incorporate both digital and analog circuitry are called *mixed-signal* devices.

<sup>&</sup>lt;sup>2</sup>Very-Large-Scale Integration, i.e. the integration of circuits comprising thousands or millions of transistors on one single chip.

the ways in which neuromorphic engineers and modeling neuroscientists can mutually benefit from each other are not symmetrically exploited. Chip designers transfer biological principles to their semiconductor substrates, e.g. the massively parallel operation of simple computing units and locally operating plasticity rules (Bi and Poo, 1997; Markram et al., 1997; Song and Abbott, 2001; Morrison et al., 2008). They reproduce and exploit the intrinsic fault tolerance and the self-optimization features of such architectures (see e.g. Sussillo et al., 2007; Bill, 2008, Section 6.2.2). Still, the focus of most neuromorphic engineering efforts is rather application specific, and the technological development has not yet brought up a neuromorphic device that is flexible and large enough to serve as a neuroscientific modeling tool.

This situation might possibly change in the following years. Within the FACETS research project, which will be introduced in Section 1.4, a novel type of hardware is currently developed (see Schemmel et al., 2006; Ehrlich et al., 2007; Schemmel et al., 2008 and Section 2.2). Devices of that type will combine a massive acceleration, large network sizes and a high configurability with the advantages inherent to analog neuromorphic devices such as power efficiency and a time-continuous operation (see Section 1.2.3). Following this strategy, neuromorphic engineering has the potential to step out of its niche and provide new and relevant input towards the understanding of cortical dynamics.

## Main Questions Addressed In This Thesis

A prototype for such a novel neuromorphic device is already available. It will be introduced in detail in Section 2.1. Based on experimental work with devices of this type, the thesis at hand is an effort to answer the following fundamental questions:

- Can neuromorphic hardware devices of the investigated type serve as modeling tools for neuroscience and provide *new* insights into neural information processing?

- What are the requirements for the acceptance of such neuromorphic tools in the established modeling community?

- What are the qualities of neuromorphic devices that have to be exploited in order to provide a benefit for modelers?

- Which methods have to be applied in order to translate between the hardware domains and the biological model?

- What are the technical challenges and obstacles on the way towards neuroscientific modeling with neuromorphic hardware?

This dissertation suggests a novel set of methods for the realization of neuroscientifically relevant models with neuromorphic hardware. For this purpose, the available prototype hardware system is deployed in various case studies, thereby testing the proposed paradigms.

The utilized chip is not an optimal device for this purpose due to its prototypic nature. It represents an early and thus imperfect developmental stage, and its resources, e.g. the number of neurons and synapses per chip, are limited. Nonetheless, the presented realization of the suggested paradigms yields essential practical experience and solutions for the overcoming of emerging obstacles. The insights gained from this thesis are expected to be useful for the development and operation of future systems. **Technical and Experimental Work** The utilization of the FACETS prototype hardware device implies specific, device-related goals:

- To specify the impact of constituent variations inherent to the employed chip technology.

- To provide calibration methods that deal with these variations.

- To document prototype-specific and design-related problems and, if possible, provide methods to handle them.

- To share technical experience and provide recommendations for the operation of the system.

- To document experiments that have been performed with this device both on the cell level and on the network level.

Dedicated chapters will address these device-specific issues.

## Structure of this Thesis

The present thesis is structured as follows: After this introduction, Chapter 1 will provide background information and references that sketch the status of current research in neuroscience from the point of view of neuromorphic engineering. Methods and models are introduced that are relevant for this thesis. In Chapter 2, the investigated neuromorphic hardware system is described in detail. Chapter 3 outlines scenarios of useful device operation. Based upon these, it describes paradigms for the translation between the hardware domain and the biological model, including the important concept of embedding the system interface into the modeling language PyNN. Furthermore, it describes the full software layer stack that has been implemented to realize the proposed concepts and techniques. Chapter 4 describes the investigation of process-inherent and design-related imperfections of the used chip. In this context, the functionality evaluation of certain sub-modules of the device requires methods for the measurement of specific variables that are not directly accessible. A set of such techniques has been developed and is presented in the beginning of the chapter. After the technical problems have been identified, Chapter 5 introduces methods to overcome these obstacles and to establish biologically realistic activity regimes on the hardware. This includes the handling of chip malfunctions, the calibration of unavoidable constituent variations and the gauging of hardware dynamics with established software simulators. In order to evaluate the biological relevance of a neural network experiment performed in hardware, statistical descriptors of network dynamics are provided which allow for a comparison between output data generated by hardware and software back-ends. Hardware experiments on the single cell and on the network level are described in Chapter 6. Utilizing the previously described methods, the calibration techniques and the introduced software framework, the experiments represent a first proof of concept for the developed neuromorphic modeling framework. A conclusion and discussion of the presented work is given at the end of this thesis, followed by an outlook on ongoing and planned work as well as on estimated further developments in the field.

## Naming Conventions

The hardware device in focus of this thesis implements a physical model of cortical neurons with respect to their information processing dynamics. This model is *not* based on the numerical solving of sets of differential equations with digital logic, which is usually referred to as a *simulation*, but it is composed of microelectronic circuits, i.e. real physical objects which imitate the electric dynamics of real neurons. Therefore, employing such a hardware model will be called an *emulation*.

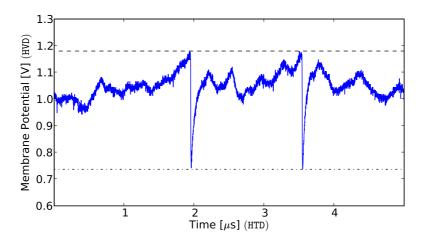

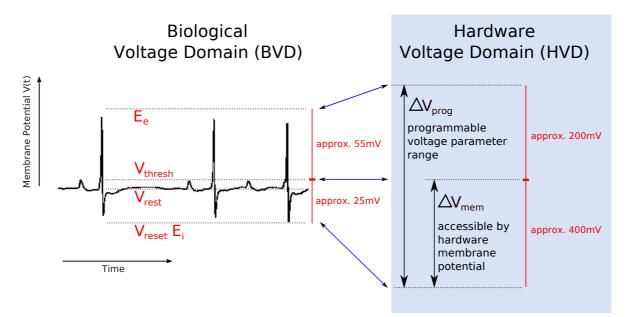

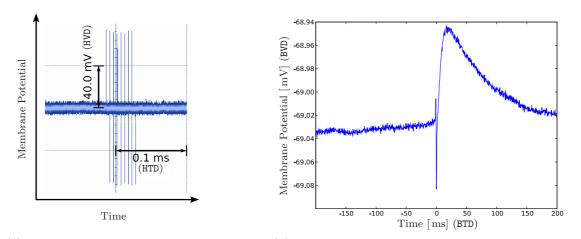

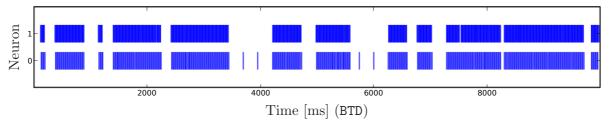

One important feature of the employed hardware device is that its intrinsic time constants are in the order of  $10^5$  times shorter than the corresponding values in the biological original. Hence, the hardware time domain has to be translated into the biological one and vice versa in order to make use of the model. The *hardware time domain* will be abbreviated with HTD throughout this thesis and corresponds to the physical lab time. Unless otherwise expressly mentioned, the applied interpretation (see Section 3.1.5) defines that any emulated biological time is exactly a  $10^5$ -fold of the period measured in HTD. The *biological time domain* will be abbreviated with BTD.

Analogously, the membrane potentials, capacitances, conductances and currents in hardware can be translated to their biological counterparts by a linear transformation, which will be described in Section 3.1.5. In order to avoid confusions regarding these two electrical domains, the abbreviations HVD and BVD will be used, standing for *hardware* and *biological voltage domain*, respectively, but accounting for all transformed electrical dimensions as well.

The hardware devices which have been utilized for the presented work were developed within the research project FACETS (see section 1.4) and serve as prototypes for a much larger system currently under development. Therefore, the prototype system is referred to as the *FACETS Stage 1 Hardware*, and the system currently built as the *FACETS Stage 2 Hardware*. In order to avoid these bulky names throughout the text, they will be abbreviated with FHW-1 and FHW-2, respectively. For the FHW-1 chip, three versions exist already, i.e. the design has gone through two revisions. The short forms FHW-1.1, FHW-1.2 and FHW-1.3 will indicate the utilized chip version. For every chip version, multiple systems exist, which under ideal conditions would behave identically, but which, due to production variations, do not. Hence, for some experimental data, e.g. for chip-to-chip comparisons, the individual index of the employed chip will be given, e.g. FHW-1.3-No.25.

## Cooperations

This thesis incorporates data, methods and findings that have been acquired in collaborations with various people.

**The Hardware System** The utilized FHW-1 system has been developed by Dr. Johannes Schemmel<sup>3</sup> and further members of the Electronic Vision(s) group at the Kirchhoff Institute for Physics in Heidelberg, Germany, under the coordination of Professor Dr. Karlheinz Meier<sup>3</sup>. Dr. Johannes Schemmel, Dr. Andreas Grübl<sup>3</sup>, Dr. Stefan Philipp<sup>3</sup>, Dan Husmann<sup>3</sup> and Sebastian Millner<sup>3</sup> actively supported the work presented in this thesis by providing and

<sup>&</sup>lt;sup>3</sup>Professor Dr. Karlheinz Meier, Dr. Johannes Schemmel, Dr. Andreas Grübl, Dr. Stefan Philipp, Dan Husmann and Sebastian Millner are with the Kirchhoff Institute for Physics, University of Heidelberg, Germany.

servicing the full hardware framework presented in Section 2.1. The experiments presented in Section 6.1.1 have been performed in close collaboration with Dr. Andreas Grübl.

**Supervised Work** The author supervised and coordinated the committed work of Bernhard Kaplan<sup>4</sup>, Eric Müller<sup>4</sup> and Johannes Bill<sup>4</sup> for their diploma theses. Bernhard Kaplan worked on the hardware-specific high-conductance state analysis method presented in Section 4.1.2. Eric Müller contributed to the development of the software framework presented in Section 3.2 and performed measurements of long-term plasticity characteristics in hardware synapses presented in Sections 4.1.3 and 6.1.5. Johannes Bill helped specifying design-related chip malfunctions, contributed methods to handle them and worked on the development of self-tuning network architectures described in Section 6.2.2.

**Further Collaborations** The experiment series presented in Section 6.2.1 have been developed and performed in close collaboration with Jens Kremkow<sup>5</sup>.

The work described in Section 3.1.3 contributes to the PyNN project, which is coordinated and inspired by Andrew Davison<sup>6</sup> and Eilif Muller<sup>7</sup>.

<sup>&</sup>lt;sup>4</sup>Bernhard Kaplan, Eric Müller and Johannes Bill are with the Kirchhoff Institute for Physics, University of Heidelberg, Germany.

<sup>&</sup>lt;sup>5</sup>Jens Kremkow is with the Institut de Neurosciences Cognitives de la Méditerranée, CNRS, Marseille, France, and with the Institute for Neurobiology and Biophysics, University of Freiburg, Germany.

<sup>&</sup>lt;sup>6</sup>Andrew Davison is with the Unité de Neurosciences Intégratives et Computationelles, CNRS, Gif sur Yvette, France.

<sup>&</sup>lt;sup>7</sup>Eilif Muller is with the Laboratory of Computational Neuroscience, Ecole Polytechnique Fédérale de Lausanne, Lausanne, Switzerland.

In the following chapter, the current status of research in neuroscience is sketched (Sections 1.1 and 1.2). Neural network modeling approaches are introduced in Section 1.2.2. Two branches of modeling, namely pure software simulations and physical hardware implementations, are compared in Section 1.2.3. The advantages and disadvantages of both strategies are discussed, and requirements for the establishment of neuromorphic hardware systems as neuroscientifically useful modeling tools are described in Section 1.2.4. A selection of established models of membrane and synapse dynamics as well as models of synaptic plasticity that are relevant for the understanding of the hardware model utilized throughout this thesis are provided in Section 1.3. Since the development of this hardware system and all presented work are embedded into the FACETS research collaboration, the project is outlined in Section 1.4.

## 1.1 The World in the Mind

Every biological organism interacts with its environment. As a part of this process, the acquisition and the use of information about the surrounding world is essential for the survival of every living system. Many forms of life have developed a variety of highly complex organs to optimize both the perception and the processing of information. Sense organs and nervous systems allow to acquire relevant data and generate reactions based upon this input.

The *central nervous system* of an organism performs the integration of sensory input, the control of organism-internal processes and the coordination of motor actions. It intrinsically reflects the world as it is perceived by the individual creature, or, in other words, it represents a model of the niche in which the innervated organism lives. In most organisms, this model is rather static, i.e. actions occur mainly by means of genetically coded and evolutionarily optimized reflexes. In some species, though, the nervous system has developed to a structure that is capable of dynamically adapting its intrinsic world representation to changes in the environment within one individual's lifetime – the organisms can learn. Highly developed forms of such systems are brains, which contain dense networks of intercommunicating nerve cells, so-called *neurons*. Based on the information that is currently perceived and on what

has been perceived in the past, brains generate predictions of what is going to happen next and can therewith generate *reason*able behavior.

Mammalian brains incorporate a structure that has turned out to be evolutionarily very successful, the *neocortex* (or simply *cortex*). The cortex is a layered nervous tissue embracing older (in terms of evolutionary development) parts of the brain. It plays a key role in the processing of sensory information, in motor control tasks, in the formation of memory, in attention and in awareness. In humans, it also significantly contributes to phenomena like language and consciousness.

For centuries, scientists of different disciplines have been researching the functionality of the brain, and today they have a large amount of partly very detailed knowledge to their disposal. Still, a conclusive explanation of many of the remarkable brain capabilities is missing.

## 1.2 Modern Neuroscience – Methods and Models

One of the goals of scientifically studying nervous systems is to understand the mechanisms that underlie the capabilities of neural structures. This section gives a depiction of neuroscientific techniques and advancements that have shaped the modern picture of the brain. Modern methods to access information about the anatomy and the functions of neural tissue are described with a focus on investigating the cortex. Modeling approaches which build upon this information, but which also contribute to the understanding of brain-like information processing, are introduced.

## 1.2.1 Studying the Brain

Charting the morphology and circuitry of the brain and monitoring the processes going on inside of it is still a technological challenge today. The cat visual cortex, for example, incorporates approximately 50,000 neurons per  $1 \text{ mm}^3$ , and each of these neurons connects to approximately 6,000 other cells via so-called *synapses* (Beaulieu and Colonnier, 1985). For a review of basic neocortical neuron and synapse types and their functions see e.g. Douglas et al., 2004. Here, only a very coarse summary of the most basic facts of neural and synaptic structure and function is given.

## Information Processing Constituents

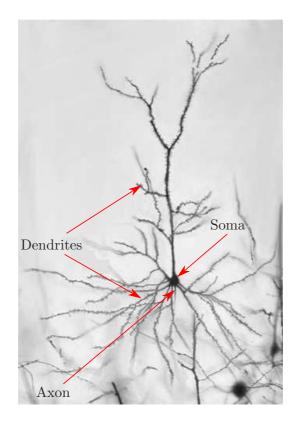

Cortical neurons consist of a cell body (or *soma*) with a diameter typically ranging from about 10  $\mu$ m to 50  $\mu$ m, and of morphological branching structures called the *dendrites* and the *axon*. Via the dendrites the neuron receives input *from* other cells, while along the axon it carries its output to other cells. Information exchange along these wire-like cell extensions is performed by sending so-called *action potentials* or *spikes*. Every neuron exhibits a dynamically evolving electrical potential difference across its cell membrane. Once this *membrane voltage* exceeds a certain *threshold* value, a sharp voltage peak (the action potential) will be generated (or *fired*) by the soma. This *pre-synaptic* spike travels along the axon and arrives at synapses that connect to the dendrites of *post-synaptic* neurons. In these synapses<sup>1</sup>, the release of neurotransmitters is triggered, which changes the properties of ion-channels incorporated in the post-synaptic cell membrane and therewith possibly its firing behavior.

<sup>&</sup>lt;sup>1</sup>Only the case of chemical synapses is considered here. See e.g. Douglas et al., 2004 for a description of *electrical synapses*.

In Figure 1.1, a stained cortical neuron is depicted. It shows an exemplar of the so-called *pyramidal* cell types, which represent the majority of *excitatory* cells in the cortex. The term *excitatory* describes the kind of impact that such a cell has on other neurons in case it sends an action potential: The described release of neuro-transmitters will cause a change in conductance and consequently in a current flow via the post-synaptic cell membrane that temporarily increases this post-synaptic cell's own firing probability. The opposite effect, i.e. the firing probability decrease of a stimulated neuron caused by pulling its membrane potential away from its firing threshold, is referred to as *inhibition*. Both the dendritic and the axonal

Figure 1.1: Photograph of a stained cortical neuron from rat. The soma, the dendrites and the axon are indicated. Courtesy of Grazyna Gorny.

total cable length of a typical pyramidal neuron are in the order of centimeters (Dayan and Abbott, 2001), while the synaptic connections that are spread across these branches have an area diameter of approximately 1  $\mu$ m per contact (Shepherd, 2004). This structural density on a microscopic level makes it extremely difficult to access information about the precise interconnection of the cells. Furthermore, the massive number of brain constituents – the human cortex is assumed to comprise approximately 10<sup>10</sup> cells and 10<sup>14</sup> synapses (Shepherd, 2004) – introduces an additional obstacle on the way towards an understanding of the relation between structure and function.

#### Wiring and Firing

In order to understand computational principles of the brain, both its "hardware", i.e. the morphological aspects of its architecture, and its "software", the neuronal code that is used to represent, process and store information on the basis of spatio-temporal spike patterns (Gerstner and Kistler, 2002), need to be investigated.

In the early 20th century, first staining techniques developed by Camillo Golgi (for a review see Torres-Fernández et al., 2006) revealed important insights into the morphology of single cells and network anatomy, e.g. the layered laminar structure of the cortex (Ramon y Cajal, 1911, reviewed in Douglas and Martin, 2004). Since then, staining and microscopical techniques have significantly improved, and today even the automated identification and tracing of a single axon and dendrite in volumes of dense neural tissue with electron microscopy has become possible (Briggman and Denk, 2006). This has not yet been systematically performed for full vertebrate brains. Even if the complete static morphology of a brain was available, it would lack important information about the dynamical properties of its constituents.

Therefore, measuring the ongoing activity in neural networks *in vivo* and *in vitro* is inevitable and approached with various techniques. An early non-invasive method is the electroencephalography (EEG, Jung et al., 1979), which today is accompanied by magnetoencephalography (MEG, Cohen, 1968; Waldert et al., 2008) and functional magnetic resonance imaging (fMRI, Logothetis et al., 2001). The spatial resolution of fMRI is in the millimeter order, which cannot be achieved with EEG and MEG. The temporal resolution of fMRI is only in the order of two seconds, though, while EEG and MEG can resolve neuronal activity at the sub-millisecond scale. Another possibility to acquire three-dimensional activity-dependent images of brain regions is the positron emission tomography, with a spatial resolution on the millimeter scale and sampling rates of up to 60 Hz (see e.g. Purschke et al., 2005; Langner, 2003).

Invasive methods provide both a high spatial a high temporal resolution, but usually access only tiny fractions of neural tissue at a time. Extracellular recordings reveal local field potentials generated by volumes with diameters in the order of 100  $\mu$ m (Mehring et al., 2003), and intracellular recordings with patch-clamp techniques provide highly resolved current flow and voltage measurements across patches of single neuron membranes (Sakmann and Neher, 1995). By recording neighboring neurons with patch-clamping techniques, the correlation between their membrane potential fluctuations can be determined (Lampl et al., 1999; Okun and Lampl, 2008). Thereby, recording pairs or groups of neurons can reveal the existence of synaptic connections and effects of synaptic plasticity, i.e. the changing impact that a neuron has on another neuron. Long-term changes in such synaptic weights have been observed by correlating the pre-synaptic spiking activity with the post-synaptic spike and membrane recordings (Bi and Poo, 1997; Dan and Poo, 2004; Markram et al., 1997). Short-term synaptic plasticity effects have been investigated with similar techniques (Markram et al., 1998; Zucker and Regehr, 2002).

Voltage-sensitive dyes allow for the temporally and spatially highly resolved recording of hundreds of neighboring neurons at the same time (Jin et al., 2002). The possible volume depth can be increased up to a millimeter by applying multi-photon imaging techniques (Kerr et al., 2005; Xu et al., 1996).

In spite of these and many more highly sophisticated methods, a lot of important questions are left unanswered, e.g. regarding the encoding of information in brains, the neural representation of concepts, the creation and the persistence of memory, the robustness of functionality, the ability to learn and the emergence of creativity, to just name a few.

## 1.2.2 Insights through Modeling

The experimental investigation of neural tissue is inevitable for the generation of a detailed brain knowledge base from which understanding of underlying principles can emerge. The above sketch of neuroscientific measurement techniques indicates the technological difficulties of this endeavor. There are further disadvantages in the experimental study of biological neural systems, for example the following:

- It is hard to control the experimental conditions during *in vivo* studies.

- In vitro preparations do not reflect all aspects of living tissue.

- It is difficult to acquire data with large statistics.

- Ethical issues and animal rights need to be considered.

- Most efforts imply high financial costs.

Models are an essential scientific instrument to describe a system in a problem-specific context. Starting from well defined questions, existing pieces of knowledge, methods and hypotheses are combined and evaluated in order to extract the desired answers and predictions. Especially in research fields on dynamical systems that cannot be fully conceived by experimental methods, like astrophysics and neuroscience, models represent an inevitable approach to test hypotheses and theories.

#### 1.2.3 Software Simulators vs. Neuromorphic Hardware

Models of spiking neurons are normally formulated as sets of differential equations for an analytical treatment or for numerical simulation. In contrast to *in vivo* or *in vitro* studies, a software model offers access to all desired observables at any time. It is arbitrarily flexible in its structure, in its level of detail and in the choice of parameters. There is a large community of scientists who contribute significant insights into neuroscience by applying models that usually draw on experimental data, but abstract and transfer these findings into synthetic systems.

For example, varying integrative properties of neuron membranes have been observed *in vivo* (reviewed in Destexhe et al., 2003) and could be well reproduced and explained by corresponding models (Shelley et al., 2002; Rudolph and Destexhe, 2003; Kumar et al., 2008). *In vivo* evidence for long-term synaptic plasticity (Levy and Steward, 1983; Bi and Poo, 1997; Markram et al., 1997; Dan and Poo, 2004) has led to various mathematical descriptions (see e.g. Bienenstock et al., 1988; Song et al., 2000; Legenstein et al., 2005; Morrison et al., 2007, 2008). Models on various spatial scales and with different trade-offs between constituent detail and network size exist, ranging from highly complex single cell descriptions (Jolivet et al., 2008; Johansson and Lansner, 2007). Considered periods range from short-term plasticity effects on the scale of tens of milliseconds (e.g. Tsodyks and Markram, 1997) to structural synaptic development on the scale of hours and days (e.g. Helias et al., 2008).

But the more complex the underlying neuron model and the size and connectivity of the simulated network grow, the more critical computation time gets. If it comes to large networks, statistics-intensive analyses or long-term observations of network dynamics can become computationally extremely expensive (see e.g. Morrison et al., 2005, 2007). The main bottle-neck is the mapping of the intrinsic parallelism of neural computation to a relatively small number of sequentially operating processors.

Neuromorphic hardware systems represent an alternative approach that can overcome some of the limitations inherent to pure software simulations (for a review see Renaud et al., 2007). In a physical, typically silicon form they mimic the structure and emulate the function of biological neural networks. Neuromorphic hardware engineering has a tradition going back to the 1980s (Mead and Mahowald, 1988; Mead, 1989), and today an active community is developing analog or mixed-signal VLSI models of neural systems.

Inspired by Mead, silicon retinas (Serrano-Gotarredona et al., 2006) and neuromorphic visual processing systems (Merolla and Boahen, 2006) are still in focus of ongoing research, with various applications such as light-weight and power-efficient sensors in flying robots (Netter and Franceschini, 2002), substitutes of biological visual systems useful e.g. for lecture demonstrations (Delbrück and Liu, 2004) or safety sensors in elderly care (Fu et al., 2008). Devices have been developed that serve as self-tuning motor control units for robotics (Lewis et al., 2000). Others resemble hippocampal place cells as attractor memory devices (Vogelstein et al., 2007) or implement self-organizing spike pattern classifiers (Häfliger, 2007; Mitra et al., 2009).

A more immediate contact with neuroscientific research is achieved e.g. by hybrid setups that couple neuromorphic hardware devices with living tissue (Bontorin et al., 2007). Recent developments, which are in focus of this thesis, aim at the utilization of neuromorphic systems as flexible modeling tools to approach neuroscientific questions (Schemmel et al., 2007; Brüderle et al., 2007; Schemmel et al., 2008; Ehrlich et al., 2007).

#### Pros and Cons of Neuromorphic Models

The main advantage of the physical emulation of neural network models, compared to their numerical simulation, arises from the locally analog and massively parallel nature of the computations. This leads to neuromorphic network models being typically highly scalable and being able to emulate neural networks in real time or much faster, independent of the underlying network size. Often, only the inter-chip event-communication bandwidth sets a practical limit on the scaling of network sizes by inter-connecting multiple neural network modules (Costas-Santos et al., 2007; Berge and Häfliger, 2007; Schemmel et al., 2008). Compared to numerical solvers of differential equations which require Von-Neumann-like computer environments (Brette et al., 2006), neuromorphic models have much more potential for being realized as miniature embedded systems with low power consumption.

A disadvantage is the limited flexibility of the implemented models. Typically, neuron and synapse parameters and the network connectivity can be programmed to a certain degree within limited ranges by controlling software. However, changes to the implemented model itself usually require a hardware re-design, followed by production and testing phases. This process normally takes several months.

Unlike most numerical simulations of neural network models, analog VLSI circuits operate in the continuous time regime. This avoids possible temporal discretization artifacts, but also makes it impossible to interrupt an experiment at an arbitrary point in time and restart from an identical, frozen network state (see Section 2.1.2 for the definition of an *experiment run* on such a system).

Furthermore, it is not possible to perfectly reproduce an experiment because the device is subject to noise (see Section 4.2.2), to cross-talk from internal or external signals (see Section 4.3.8), and to temperature dependencies (see Dally and Poulton, 1998). These phenomena often have a counterpart in the biological specimen, but it is highly desirable to control them as much as possible.

Another major difference between software and hardware models is the finiteness of any silicon substrate. This in principle also limits the size of any software model, as it utilizes standard computers with limited memory and processor resources, but for neuromorphic hardware the constraints are much more immediate: The number of available neurons and the number of synapses per neuron have strict limits; the number of manipulable parameters and the ranges of available values are fixed.

#### Exploiting Speed and Scalability

Still, neuromorphic network models are highly scalable at constant speed due to the intrinsic parallelism of their circuit operation. This scalability results in a relative speedup compared to software simulations, which gets more and more relevant the larger the simulated networks become, and which provides new experimental possibilities. A hardware experiment can be repeated many times within a short period, allowing the common problem of insufficient statistics due to lacking computational power to be overcome. Large parameter spaces can be swept to find an optimal working point for a specific network architecture, possibly narrowing the space down to an interesting region which can then be investigated using a software simulator with higher precision. One might also think of longer experiments than have so far been attempted, especially long-term learning tasks which exploit synaptic plasticity mechanisms (Schemmel et al., 2007).

Except for the kind of systems considered in this thesis, all neuromorphic hardware projects cited above currently work with circuits operating in biological real-time. This allows interfacing real-world devices such as sensors (Serrano-Gotarredona et al., 2006) or motor controls for robotics, as well as setting up hybrid systems with *in vitro* neural networks (Bontorin et al., 2007). In contrast to these real-time systems, the type of neuromorphic hardware in focus of the presented work (Schemmel et al., 2007, 2008) operates at a highly accelerated rate (see Section 3.1.5). This crucial feature even increases the speedup advantages mentioned above by many orders of magnitude and hence opens up new prospects and suggests new experimental paradigms (see Section 3.1.1).

## 1.2.4 Requirements for the Establishment of Neuromorphic Modeling

The computation speed, together with an implementation path towards architectures with low power consumption and very large scale networks (Schemmel et al., 2008; Fieres et al., 2008), makes neuromorphic hardware systems a potentially valuable research tool for the modeling community, where software simulators are more commonplace (see (Brette et al., 2006) for a review of simulation tools). The establishment of a neuromorphic hardware device as a useful component within the neuroscientific modelers' toolbox requires:

• A proof of its biological relevance, i.e. it has to be verified that the implemented neuron and connectivity model can be used to generate biologically realistic structure and

behavior.

- For this purpose, a common concept of experiment description and output data interpretation has to be found which allows a comparison between the hardware domain and a reference system. A very practical choice for such a reference are established software simulators.

- Its operability by non-hardware-experts.

In the following chapters, the fulfillment of these requirements for one specific type of neuromorphic device is documented.

## 1.3 Utilized Neuroscientific Concepts

In the following, a selection of neuroscientific concepts is described that are relevant in the context of this thesis. In case of the synapse modeling, the list does not imply a qualitative superiority of the selected approaches compared to the manifold possible alternatives, but rather reflects the functionality that is implemented in the hardware system utilized in the following chapters (see Section 2.1).

## 1.3.1 High-Conductance States

Membrane dynamics of single neurons play an important role in neural information processing. Activity measurements in the cortex show that the dynamical properties of a membrane are strongly influenced by the total of its synaptically induced conductances (Shu et al., 2003; Destexhe et al., 2003; Boustani et al., 2007; Cossart et al., 2003). In this context, it is useful to distinguish between two states of neuronal activation: *Up* states or *activated* states, where the membrane is depolarized by increased extracellular activity and the embedded cell fires irregularly, and *down* states, where both intra- and extracellular activity follow low-frequency rhythms (Anderson et al., 2000). In the activated state, which is also called the *high-conductance state*, neurons show stochastic firing behavior and an enhanced responsiveness towards input stimuli.

The high-conductance state determines the properties of a single neuron's membrane within an active network. There is experimental evidence for its existence within *in vivo* networks, e.g. in awake and attentive animals (Destexhe et al., 2003; Boustani et al., 2007), or *in vitro* in localized sub-populations (Cossart et al., 2003).

Characteristics of neurons in the high-conductance state are a low input resistance, a depolarized membrane with large membrane potential fluctuations, dominant inhibitory conductances and a stochastical response to stimulation patterns due to fluctuating background activity (Destexhe et al., 2003; Kumar et al., 2008).

In (Wielaard et al., 2001) and in (Shelley et al., 2002), a model is described and analyzed which is based on leaky integrate-and-fire neurons that can exhibit high-conductance states. There, the membrane potential V(t) (see also Equation 2.1) is shown to follow the so-called *effective reversal potential*  $V_{\text{eff}}(t)$  with the membrane time constant  $\tau_{\text{m}}(t)$ .  $V_{\text{eff}}(t)$  is defined as the *difference current*  $I_{\text{D}}(t)$  between excitation and inhibition divided by the total membrane conductance  $g_{\text{T}}(t)$ :

$$V_{\rm eff}(t) \equiv \frac{I_{\rm D}(t)}{g_{\rm T}(t)} = \frac{g_{\rm e}^{\rm tot}(t)E_{\rm e} - g_{\rm i}^{\rm tot}(t)|E_{\rm i}|}{g_{\rm T}(t)} \qquad (1.1)$$

Here,  $g_{\rm e}^{\rm tot}(t)$  and  $g_{\rm i}^{\rm tot}(t)$  denote the total of synaptically induced excitatory and inhibitory conductances, respectively. The membrane time constant  $\tau_{\rm m}(t)$  is determined by the total membrane capacitance  $C_{\rm m}$  and the total conductance  $g_{\rm T}(t) \equiv g_{\rm l} + g_{\rm e}^{\rm tot}(t) + g_{\rm i}^{\rm tot}(t)$ , where  $g_{\rm l}$ models the permanent and constant leakage conductance (see also Equation 2.1):

$$\tau_{\rm m}(t) \equiv \frac{C_{\rm m}}{g_{\rm l} + g_{\rm e}^{\rm tot}(t) + g_{\rm i}^{\rm tot}(t)} \qquad (1.2)$$

This membrane time constant can be understood as the temporal resolution capability of the neuron, because a small  $\tau_{\rm m}(t)$  makes the membrane potential immediately follow the effective reversal potential and therewith follow the synaptic input. Consequently, a neuron with a small  $\tau_{\rm m}(t)$  can perform well as a coincidence detector because it is able to rapidly detect changes in input correlation.

The possibility of neuron membranes to switch between integrating properties and coincidence detector functionality enriches the information processing capabilities of neural networks.

## 1.3.2 Models of Synapse Response Dynamics

In the following, some popular models for the temporal development of synaptic currents or conductances as a response to incoming spikes are listed. In this thesis, they are also referred to as *temporal kernels* or, only in the case of conductance-based synapses, *conductance courses* (CC).

**Delta Function** For current-based models, the synaptic response to a spike arriving at time  $t = t_{sp}$  is sometimes modeled simply as current delta peaks, see e.g. (Brunel, 2000):

$$I_{\rm syn}(t) = I_0 \,\delta(t - t_{\rm sp})$$

. (1.3)

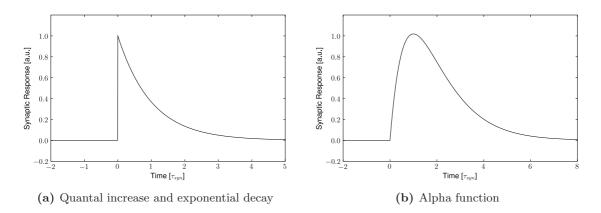

**Quantal Increase and Exponential Decay** A modification which introduces temporal dynamics to the synapse is a quantal increase of the conductance or current by a fixed value  $w_{\text{syn}}$  (usually referred to as the *synaptic weight*), followed by an exponential decay with time constant  $\tau_{\text{syn}}$ , found e.g. in (Sussillo et al., 2007) and (Maass et al., 2004a):

$$\frac{\mathrm{d}g_{\mathrm{syn}}(t)}{\mathrm{d}t} = -\frac{g_{\mathrm{syn}}(t)}{\tau_{\mathrm{syn}}} + w_{\mathrm{syn}}\,\delta(t - t_{\mathrm{sp}}) \qquad . \tag{1.4}$$

See Figure 1.2(a) for an illustration.

**Alpha Function** In order to avoid the quantal increases of currents or conductances and rather have a non-instantaneous rise which smoothly changes into a decrease, alpha or alpha-like functions are commonly used, e.g. in (Kumar et al., 2008) and (Shelley et al., 2002):

$$g_{\rm syn}(t) = g_0 \, \frac{t - t_{\rm sp}}{\tau_{\rm syn}} \exp^{(t_{\rm sp} - t)/\tau_{\rm syn}} H(t - t_{\rm sp}) \qquad,\tag{1.5}$$

where H(t) is the Heaviside step function. See Figure 1.2(b) for an illustration.

Figure 1.2: Two typical examples for the temporal response kernels of modeled synapses. Such kernels are used to shape the conductance or the current course generated when a spike arrives at the synapse. (a) A quantal increase followed by an exponential decay. (b) An alpha function.

## 1.3.3 Synaptic Learning

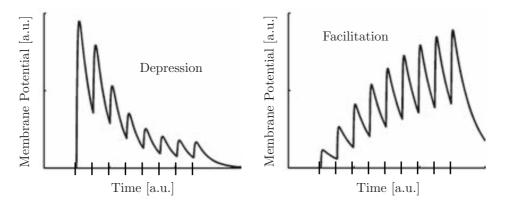

In the following, two important models of synaptic plasticity are introduced: The shortterm mechanisms of synaptic depression and facilitation, and a model of long-term synaptic modification based on the temporal correlation of pre- and post-synaptic spike times. For a review of phenomenological models of synaptic plasticity based on spike timing, see e.g. Morrison et al., 2008.

### Short-Term Synaptic Plasticity

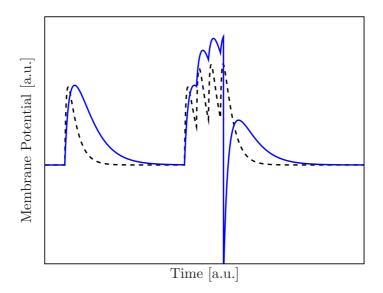

It has been found that the efficacy of biological synapses can be dependent on the history of their pre-synaptic activity (Tsodyks and Markram, 1997; Markram et al., 1998). These changes typically last for a few milliseconds to seconds. The effect is called *depression* if the synapse gets weaker, the opposite effect, i.e. strengthening of the synapse, is referred to as *facilitation*. See Figure 1.3 for a schematic.

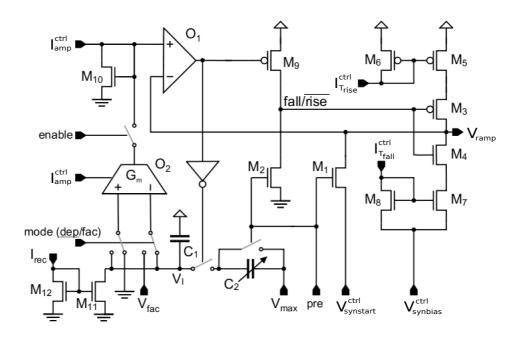

In the FACETS Stage 1 hardware, a slight modification of the short-term plasticity model described in Tsodyks and Markram, 1997 is implemented. It is introduced in Section 2.1.3,

#### Long-Term Synaptic Plasticity

A first important postulation about the mechanisms of self-organization in the brain was made by the psychologist Donald Hebb in 1949, especially notable since it was formulated on purely theoretical grounds (Hebb, 1949). He suggested a dependency of the development of synaptic strengths on correlations between pre- and post-synaptic activity: "When an axon of cell A is near enough to excite cell B or repeatedly or persistently takes part in firing it, some growth process or metabolic change takes place in one or both cells such that A's efficiency, as one of the cells firing B, is increased."

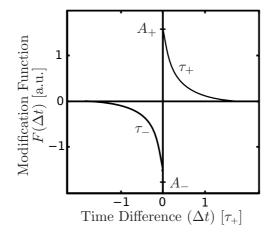

Based on experimental evidence described e.g. in Bi and Poo, 1997 and (Markram et al., 1997), a class of synaptic weight modification models has been developed that is based on the temporal correlation between pre- and post-synaptic firing (Song et al., 2000; Legenstein et al., 2005; Morrison et al., 2007, for a review see Morrison et al., 2008). According to these

**Figure 1.3:** Schematic of a membrane potential that receives sequences of spikes (indicated as vertical markers on the time axis) via an excitatory depressing (left) and via an excitatory facilitating (right) synapse. In the case of depression, the synaptic efficacy decreases due to the successive pre-synaptic input. In the case of facilitation, the synaptic efficacy grows as a consequence of the pre-synaptic stimuli.

so-called *spike-timing-dependent plasticity* (STDP) rules, the weight of a synapse increases by an additive or relative amount, if the temporal correlations between pre- and post-synaptic spikes suggest a causal relationship. In cases of acausal correlations, the weight will decrease. Such correlations are determined in terms of spike pairings or triplets (Pfister and Gerstner, 2006).

For the specific STDP implementation realized in the FACETS Stage 1 hardware system, see Section 2.1.3.

## 1.4 The FACETS Research Project

The FACETS<sup>2</sup> research project (FACETS, 2009) is a collaboration of 16 European partner groups, funded by the European Commission in the framework of the Information Society Technologies (IST, 2009) program. FACETS puts together a multi-disciplinary team of researchers from the fields of biology, mathematics, computer science, physics and electrical engineering. The goal of the project is to experimentally and theoretically investigate brainlike computing principles beyond the Turing paradigm (Turing, 1937; von Neumann, 1945). Computational concepts inherent to biological neural systems, which form the basis for capabilities like the processing of sensory input, memory, self-organization and learning, shall be extracted, understood, generalized and exploited for technological applications.

The research in FACETS follows three major approaches:

- In vivo and in vitro experiments with real neural tissue. The acquired results are collected in data bases and therewith made accessible to other FACETS members.

- The theoretical analysis of the experimental data. Mathematical models of neural systems based on the experimental observations are

<sup>&</sup>lt;sup>2</sup>Fast Analog Computing with Emergent Transient States

extracted. If possible, they are investigated analytically, otherwise they are numerically computed in software simulations.

• The design, implementation and utilization of neuromorphic hardware devices which physically implement the developed neural network models.

The mutually beneficial cooperation of researchers working in these three fields is a major challenge aimed at and strongly supported by FACETS.

**Neuromorphic Hardware in FACETS** Along the line of keeping diversity instead of eliminating it, the project follows two development branches for neuromorphic hardware systems: One approach aims at VLSI models of neurons with a high degree of biological precision. These systems are operating in real-time and provide the opportunity to set up hybrid systems, i.e. networks of biological and hardware neurons which communicate with each other (Bontorin et al., 2007). The second approach tries to exploit the possibilities of CMOS<sup>3</sup> technology in terms of the small realizable time scales, the low power consumption and the possible dense spatial integration of VLSI circuits. The goal is to create a novel, large-scale and massively accelerated neuromorphic hardware device which, among other possible applications (see Section 3.1.1), provides a complementary modeling tool for the computational neuroscience community. It shall helps to overcome some typical limitations of software simulators like speed and scalability (see Section 1.2.3). In Chapter 2, this second type of hardware is introduced and described in detail.

The development of such a device is not a task performed isolatedly by the engineering groups within FACETS. Instead, its successful realization essentially depends on contributions from modeling experts and experimentalists. The implemented neuron and synapse models are the outcome of project-wide discussions, and the communication structure provided by the currently developed large-scale system (see Section 2.2), for example, strongly orients towards the realization of experiment types performed and suggested by FACETS members.

<sup>&</sup>lt;sup>3</sup>Complementary Metal Oxide Semiconductor

## 2 Neuromorphic Substrate

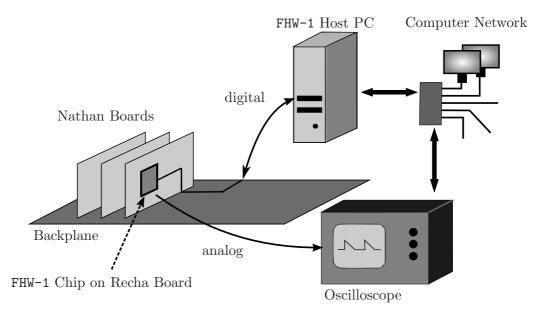

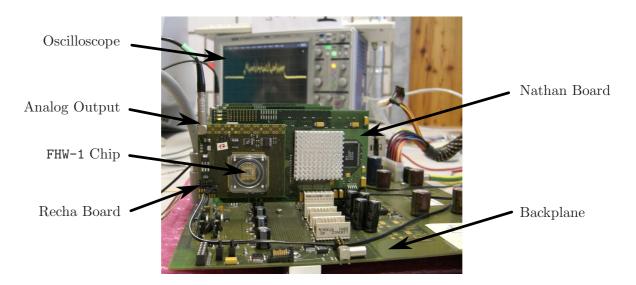

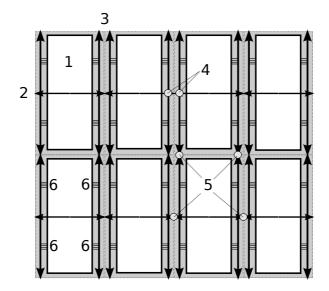

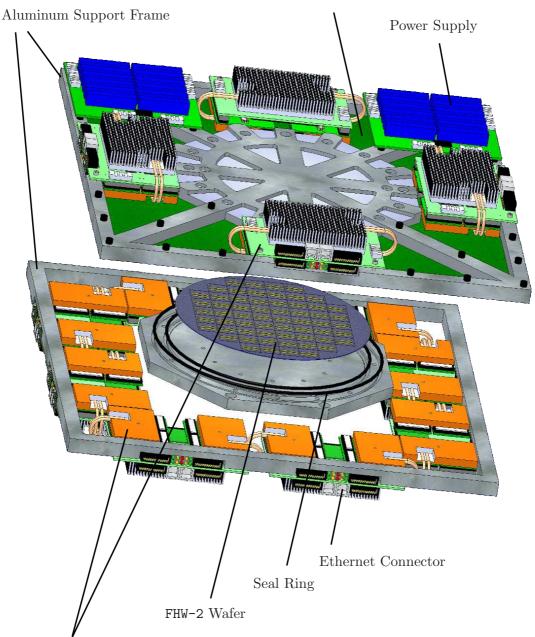

This chapter introduces the two development stages of the accelerated, large-scale hardware approach followed by the FACETS project (see Section 1.4). Section 2.1 provides a detailed description of the chip-based prototype devices, also referred to as FHW-1 systems. These devices have been available for some time already. They have been utilized for all experimental hardware work presented in this thesis. Many of the FHW-1 components and sub-circuits will be used in the target system, which is not based on single chips anymore, but on the creation of a neural substrate on a whole silicon wafer. This *wafer-scale* or FHW-2 system, which is currently under development, is introduced in Section 2.2.

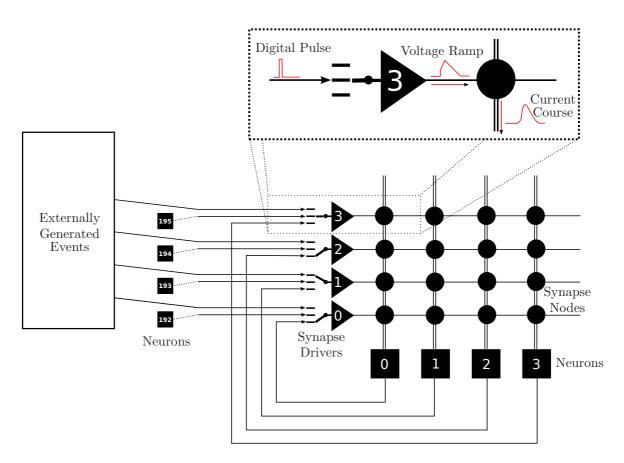

## 2.1 Chip-Based Neural Network Model

The components of the hardware system utilized throughout this thesis have been described in detail in various publications (Schemmel et al., 2004, 2006, 2007; Fieres et al., 2004; Philipp et al., 2007; Grübl, 2007; Philipp, 2008). In the following, basic information about the neural network chip and its support hardware is summarized with respect to the neuroscientific applicability of the system. The implemented neuron and synapse model plus the realizable network topologies are described.

Furthermore, since the correspondence between hardware parameters and their biological counterparts is not always a linear one (see Section 3.1.5), and since multiple process-inherent or design-related hardware mechanisms impose problems on the biologically realistic operation of the device (see Section 4.3), a selection of technical details about sub-circuits, about hardware parameters and about their precise functionality is provided. Later sections will refer to these details.

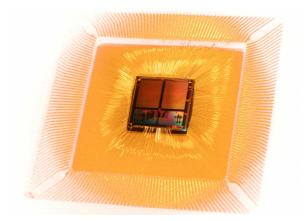

## 2.1.1 Technology and Dimensions

The existing first three versions of the FACETS Stage 1 hardware (FHW-1) system are built using a standard 180 nm CMOS process. 384 neurons are located on one single  $25 \text{ mm}^2$ die. The programmable inter-neuron connectivity is described below in Section 2.1.2. The possibility to inter-connect multiple of the network dies is work in progress (Philipp et al., 2007). The system exhibits an acceleration factor of up to  $10^5$  – see Section 3.1.5 for a detailed explanation of the applied time transformation method. The action potentials generated

## 2 Neuromorphic Substrate

during hardware operation can be recorded with a temporal resolution of approximately 0.3 ns (HTD). The precise value of this depends on the frequency  $f_{chip}$  the chip is clocked with.

Figure 2.1 shows a photograph of an FHW-1.2 chip bonded to a carrier PCB<sup>1</sup>. The two symmetric, homogeneously structured rectangles are the synapse arrays described below in Section 2.1.2. The more heterogeneously structured rectangle below the synapse arrays comprises the neuron circuits described in Section 2.1.2 and various digital control circuitry.

Figure 2.1: Photograph of an FHW-1 chip and the bonding wires connecting it to pads inside a package.

## 2.1.2 Implemented Model

The FHW-1 system implements a leaky integrate-and-fire (I&F) neuron model with conductancebased synapses (Destexhe, 1997; Destexhe and Pare, 1999). It is designed to exhibit a linear correspondence with existing phenomenological conductance-based modeling approaches (Burkitt et al., 2003; Rudolph and Destexhe, 2006). The cell body is modeled as a *point neuron*, i.e. it does not comprise any compartments separated by resistors which are often used to model the temporal dynamics induced by the spatial extension of the cell soma, its dendrites and its axon (Gerstner and Kistler, 2002, Section I.4.4).

In analytical or numerical I&F neuron models, the electrical processes of neural information processing are usually described mathematically by sets of differential equations. In the neuromorphic hardware described here, nearly all electric quantities incorporated in the model are physically represented: A capacitance is modeled by a capacitance, currents are currents and voltages are voltages. Conductances are emulated by voltage controlled current sources, so-called operational transconductance amplifiers. The model is not passively computed by a separate unit, *it computes itself* in continuous time and with continuous variables.

#### What is an Experiment?

An important consequence of the physical nature of the neuromorphic model is the hardwarespecific definition of an *experiment run*: In contrast to pure software simulations, where time

<sup>&</sup>lt;sup>1</sup>Printed Circuit Board

emerges as a sequence of discrete numerical integration steps, the analog part of a neuromorphic hardware model exists and operates continuously in real-time. In software simulations, an experiment run has a starting point in time with well defined initial conditions plus an experiment duration. If not explicitly computed, the model does not exist beyond this scope. In a hardware system connected to its power supply, the membrane potential is permanently existing and evolving and can always be measured.

Hence, an experiment run in hardware is defined as a period  $T_{exp}$  during which

- the system is fully configured with well defined parameter values,

- a sequence of stimuli is applied and

- a set of observables is recorded.

A period  $T_{\text{init}}$  is recommended which immediately precedes  $T_{\text{exp}}$  without stimulation and recording, but with a well defined hardware configuration already applied. This minimizes the influence of the operation history on dynamically evolving observables like the membrane potential or synaptic activation states. Still, due to effects described in Sections 4.2.2 and 4.3.8, two hardware runs with identical settings can never generate precisely the same results.

#### Membrane Potential Dynamics

The neuron circuits are designed such that the temporal development of an emulated membrane potential V(t) is determined by the following differential equation:

$$-C_{\rm m}\frac{dV}{dt} = g_{\rm l}(V - E_{\rm l}) + \sum_{j} p_{j}(t)g_{j}^{\rm amp}(t)(V - E_{\rm e}) + \sum_{k} p_{k}(t)g_{k}^{\rm amp}(t)(V - E_{\rm i}) \qquad .$$

(2.1)

The constant  $C_{\rm m}$  represents the total membrane capacitance. The first term on the righthand side models the sum of all currents via constantly conducting ion channels. Hence, if no transient conductances towards other reversal potentials are active, the membrane potential will develop towards the so-called *leakage reversal potential*  $E_{\rm l}$ . The time constant of this development, an exponential convergence, is determined by the membrane capacitance and the so-called *leakage conductance*  $g_{\rm l}$ :  $\tau_{\rm m} = \frac{C_{\rm m}}{g_{\rm l}}$ .

The transient conductances imposed by synaptic activity have different reversal potentials,  $E_i$  and  $E_e$ , modeling inhibitory and excitatory ion channels. The index j in the first sum of Equation 2.1 runs over all excitatory synapses, while the index k in the second sum covers the inhibitory ones. The conductance course (CC) induced by an individual synapse s is modeled as a product  $p_s(t)g_s^{amp}(t)$ , where  $p_s(t)$  denotes the synaptic open probability (Dayan and Abbott, 2001), and  $g_s^{amp}$  is again a product of the synaptic weight  $\omega_s(t)$  and a maximum conductance  $g_s^{max}(t)$ :

$$g_s^{\rm amp}(t) = \omega_s(t) \, g_s^{\rm max}(t) \qquad (2.2)$$

The shape of a CC is determined by  $p_s(t)$  (see Section 2.1.2), while  $g_s^{\text{amp}}(t)$  defines its amplitude. The weights  $\omega_s(t)$  can be dynamically modified by the implemented so-called *spike-timing dependent plasticity* (STDP, see Section 1.3.3) algorithm which in every synapse detects temporal correlations in the order of tens of milliseconds (BVD, Caporale and Dan, 2008) between pre- and post-synaptic action potentials. See Section 2.1.3 for more detail on that. The maximum conductances  $g_s^{\max}(t)$ , on the other hand, can be affected by plasticity

## 2 Neuromorphic Substrate

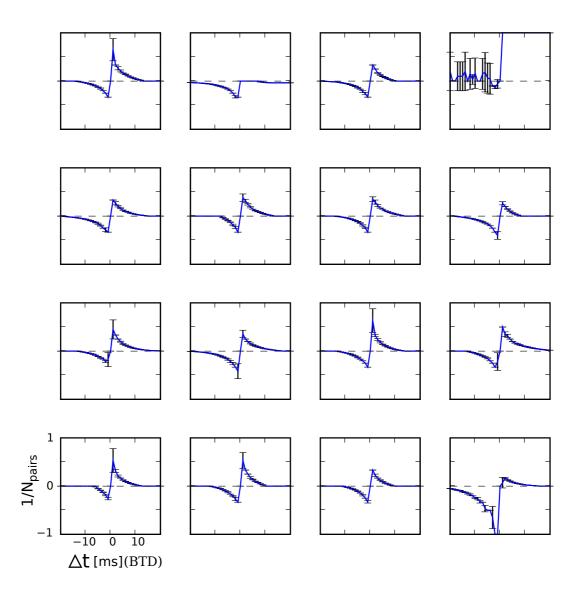

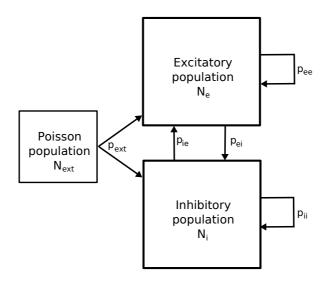

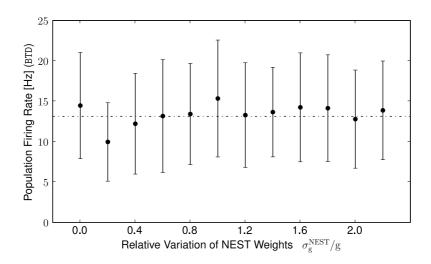

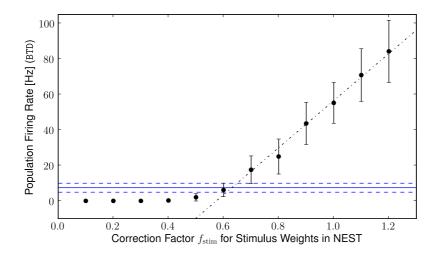

mechanisms called *short-term depression* and *short-term facilitation*, both determined by the pre-synaptic activity only.