# INAUGURAL - DISSERTATION

zur

Erlangung der Doktorwürde

der

Naturwissenschaftlich-Mathematischen Gesamtfakultät

der

Ruprecht – Karls – Universität

Heidelberg

vorgelegt von MSc Deyan Atanasov aus Kubrat, Bulgarien

Tag der mündlichen Prüfung: 21. Dezember 2009

# Design and Implementation of a System for Data Traffic Management in a Real-Time Processing Farm Operated at 1 MHz

Gutachter: Prof. Dr. Volker Lindenstruth

Prof. Dr. Ulrich Brüning

## **Abstract**

Viele der heutigen Hochenergiephysik-Experimente erforschen seltene Phänomene und benötigen daher eine Echtzeitdatenverarbeitung mit hohen Durchsatzraten, um das Rohdatenaufkommen der Detektoren von einigen Terabytes pro Sekunde auf eine Rate zu die und detaillierte Auswertung senken, die für Speicherung geeignet Anwendungsspezifische Trigger-Systeme wählen die für das physikalische Experiment relevanten Ereignisse aus. Häufig werden Datenfragmente, die zu einem Ereignis gehören, aber von mehreren verschiedenen Detektoren produziert werden, an einer Stelle gesammelt, bevor sie verarbeitet werden. Das sich ergebende Kommunikationsmodel kann bei ungesteuerter Datenübertragung zu Verzögerungen und ineffizienter Nutzung von Rechenzeiten führen, da eine Vielzahl von Quellen versuchen, um Netzwerkverbindungen und Rechenkapazitäten zu konkurrieren. Diese Arbeit behandelt die notwendigen Maßnahmen, um einen störungsfreien und lastverteilten Betrieb einer Echtzeittrigger-Farm sicherzustellen, die Paketgrößen von einigen Kilobytes bei einer Taktrate im Megahertz Bereich verarbeitet. Die über mehrere Quellen aufgeteilten Daten müssen dabei innerhalb einiger Millisekunden zusammengefasst und verarbeitet werden. Die Rechnerfarm besteht aus gewöhnlichen PCs, die ringförmig durch ein handelsübliches Hochgeschwindigkeitsnetzwerk mit niedriger Latenz verbunden sind. Es wird ein System zum Datenverkehrsmanagement vorgestellt, basierend auf einer globalen Steuerungseinheit und einem dedizierten Steuerungsnetzwerk. Erstere reserviert verteilte Rechenkapazitäten dynamisch, um Netzwerkstaus zu vermeiden und die Belastung der Systeme aufzuteilen. Letztere versorgt die Datenquellen mit den Steuerungsinformationen, um die überwachte Datenübertragung anzustoßen. Anhand eines Prototypen-Rechnerverbundes mit einer hardwarebasierten Steuerung des Netzwerkverkehrs wird der störungsfreie Betrieb gezeigt. Basierend auf den gemessenen Parametern werden Simulationsergebnisse für große Computerfarmen präsentiert. Prototyp und Simulation zeigen die Fähigkeit des Systems, 128 Byte Blöcke, die über mehreren PCI-Eingangsquellen mit einer Rate von mehr als 2 MHz zur Verfügung gestellt werden, auf einen fernzugreifbaren Speicher (Remote Shared Memory) zu transportieren. Sowohl die Mess- als auch die Simulationsergebnisse demonstrieren, dass es möglich ist, ein hochverfügbares Mehrcomputer-Trigger-System mit geringer Latenz auf handelsüblichen Komponenten aufzubauen. Dafür muss nur der tatsächliche Datentransfer sorgfältig gesteuert werden, um, bei sinnvollem Einsatz der Rechenkapazitäten, effizient Daten zusammen zu führen.

## **Abstract**

The majority of contemporary high-energy physics experiments study rare phenomena, which necessitates real-time high-throughput data processing to reduce the raw detector data rate of several Tbyte/s to a rate which is feasible for storage and detailed analysis. Unique trigger systems select the physical events relevant to the experiment. Typically, data fragments corresponding to the same event and originating from multiple detector data sources need to be assembled in a specific location before being processed further. The resulting communication model can lead to congestions and to inefficient system utilization if data are transferred without supervision since numerous sources are attempting to use common interconnect and computing recourses concurrently. This thesis deals with the measures taken to ensure a congestion-free, load-balanced operation of a real-time trigger farm processing data packets as small as several kbytes at a megahertz rate. The input data are initially split among multiple data feeds and need to be assembled and processed within a few milliseconds. The processing farm is built around commodity PCs which are interconnected with a commercial high-speed low-latency network implementing a torus topology. The thesis presents a system for data traffic management based on a global traffic supervisor and a dedicated control network. The former allocates distributed computing resources dynamically in order to avoid network congestions as well as to balance the load of the system. The latter communicates supervising information to all data feeds in order to initiate a controlled data transfer. A congestion-free system operation is demonstrated in a farm prototype with an integrated hardware-based implementation of the traffic shaping system. Based on parameters measured in the prototype, simulation results of a large-scale processing farm are presented. Both the prototype and the simulation results demonstrate that the system is capable of transferring input data initially split among multiple PCI-based feeding nodes, each one transmitting sub-fragments of 128 bytes, to a specific remote shared memory location at a rate beyond 2 MHz. The obtained results demonstrate the applicability of multicomputer systems based on commodity components for high-rate, low-latency trigger processing if certain care is taken in organizing the actual data transfers. This organization has to ensure efficient event building and appropriate allocation of the available processing resources.

# **CONTENTS**

| I.       | INTRODUCTION                                                     | 1        |

|----------|------------------------------------------------------------------|----------|

| II.      | ARCHITECTURE OF A HIGH-RATE LOW-LATENCY SCALABLE TRIGO           | GER5     |

| A.       | . Initial Motivation                                             | 5        |

|          | 1. The LHCb Trigger System                                       |          |

|          | 2. The LHCb Level-1 and the Requirements for the Level-1 Trigger |          |

| B.       |                                                                  |          |

|          | 1. The Scalable Coherent Interface                               | 13       |

| C.       | · · · · · · · · · · · · · · · · · · ·                            |          |

| D.       | . Data Routing                                                   | 16       |

| E.       | THE SYSTEM PROTOTYPE                                             | 17       |

| F.       | THE NEED FOR TRAFFIC SHAPING                                     | 18       |

| G.       | . TRAFFIC SHAPING IN THE CMS EXPERIMENT                          | 22       |

| Η.       | . TRAFFIC SHAPING IN THE ATLAS EXPERIMENT                        | 26       |

| III.     | DATA FLOW CONTROL SYSTEM ARCHITECTURE                            | 29       |

| A        | . THE CONCEPT                                                    | 29       |

| В.       |                                                                  |          |

| Δ.       | 1. Structure and Operation                                       |          |

|          | 2. Scheduling Discipline                                         |          |

|          | 3. Latency of the Scheduler                                      |          |

|          | 4. Queuing of Destination Addresses                              |          |

|          | 5. Flow Control Network Interface                                |          |

|          | 6. Transfer of Feedback Messages                                 |          |

|          | 7. Implementation                                                |          |

|          | 8. Setting up the Scheduler                                      |          |

|          | 9. Control and Status of the Scheduler                           |          |

| C.       | $\sigma$                                                         |          |

|          | 1. Motivation                                                    |          |

|          | 2. Features                                                      |          |

| D.       |                                                                  | 56       |

| E.       |                                                                  |          |

|          | 1. Structure                                                     |          |

|          | 2. Data Format                                                   |          |

|          | 3. Flow Control Network Interface                                |          |

|          | 4. Implementation                                                |          |

|          | 5. Configuration, Control and Status of the DMA Engine Domain    |          |

| F.       |                                                                  | 68       |

| IV.      | FLOW-CONTROLLED SYSTEM PERFORMANCE                               | 71       |

| Α.       | . Test Set-up                                                    | 71       |

| B.       |                                                                  |          |

| В.<br>С. |                                                                  |          |

| D.       |                                                                  |          |

| Б.<br>Е. |                                                                  |          |

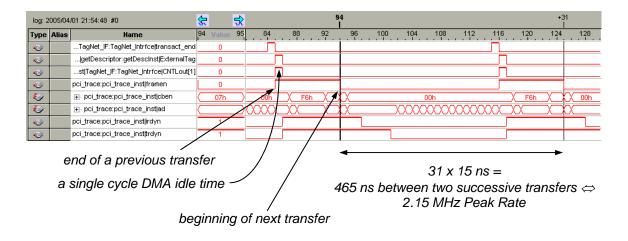

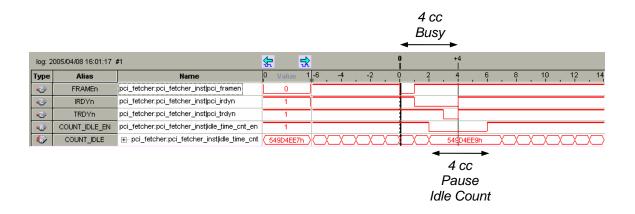

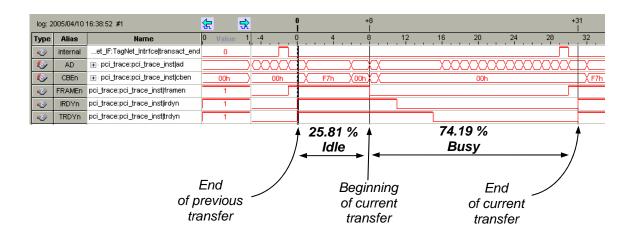

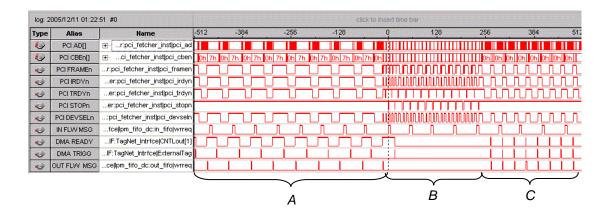

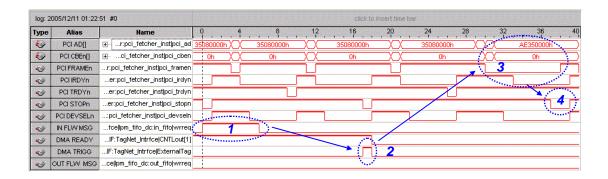

| L.       | 1. PCI Bus Idle Time Analysis                                    |          |

|          | 7 Tayaat Rotry Analysis                                          | 85<br>85 |

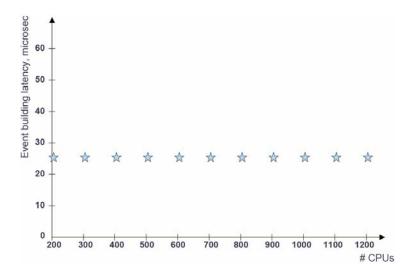

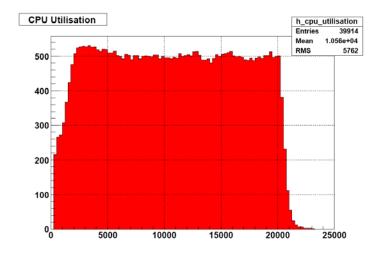

| V. S | SIMULATION OF THE TRIGGER PROCESSING FARM     | 89  |

|------|-----------------------------------------------|-----|

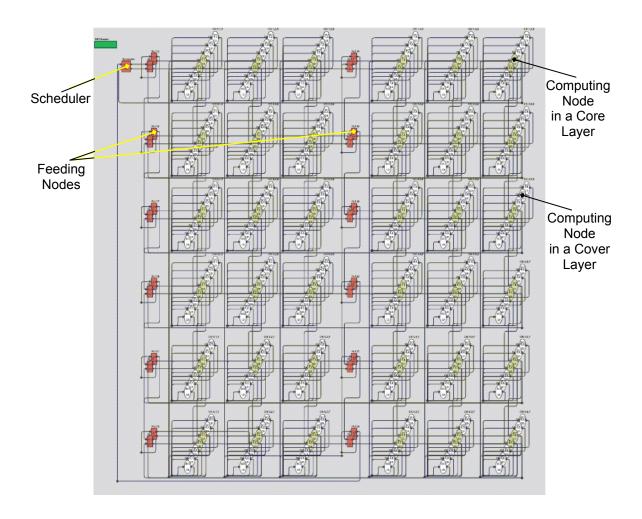

| A.   | SYSTEM ARCHITECTURE                           | 89  |

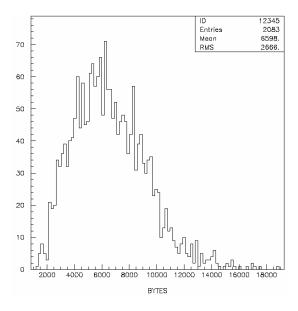

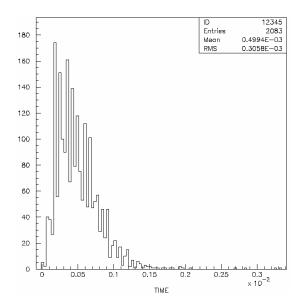

| B.   | INPUT DATA                                    | 90  |

| C.   | System Size                                   | 91  |

| D.   | THE SIMULATION FRAMEWORK                      | 92  |

| E.   | THE SIMULATION MODEL                          | 94  |

| F.   | SIMULATION RESULTS                            | 95  |

| VI.  | CONCLUSION                                    | 101 |

| VII. | APPENDICES                                    | 105 |

| A.   | SETTING UP THE SYSTEM                         | 105 |

| B.   | SCHEDULER DESIGN PARAMETERS                   | 110 |

| C.   | CONTROL AND STATUS REGISTERS OF THE SCHEDULER | 117 |

| D.   | DMA Engine Design Parameters                  | 122 |

| E.   | DMA ENGINE CONTROL AND STATUS REGISTERS       |     |

| F.   | CD-ROM CONTENTS                               | 127 |

| G.   | ACRONYMS AND ABBREVIATIONS                    | 128 |

| BIBL | IOGRAPHY                                      | 133 |

| ACKN | NOWLEDGEMENTS                                 | 141 |

# **LIST OF FIGURES**

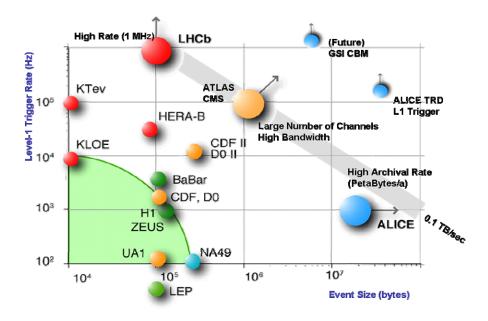

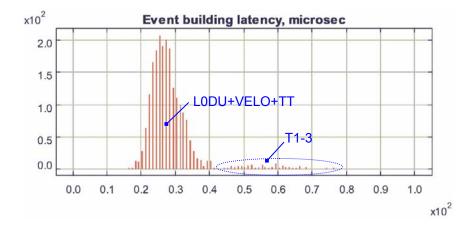

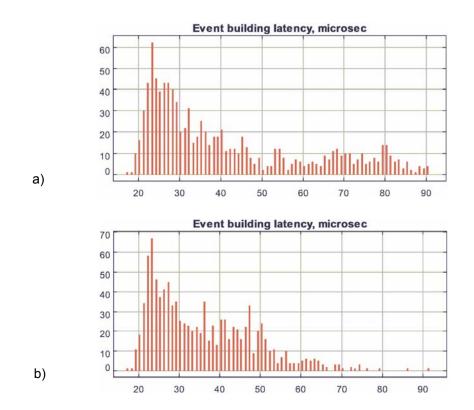

| FIGURE I-1: A SUMMARY OF SOME CURRENT AND FUTURE HIGH-ENERGY PHYSICS EXPERIMENTS.  UPCOMING LHC EXPERIMENTS ARE DEPICTED AS LARGER BALLS. DIFFERENT EXPERIMENTS SET |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIVERSE REQUIREMENTS TO THE TRIGGER AND DATA ACQUISITION SYSTEMS. A PICTURE FROM [5, 6]1                                                                            |

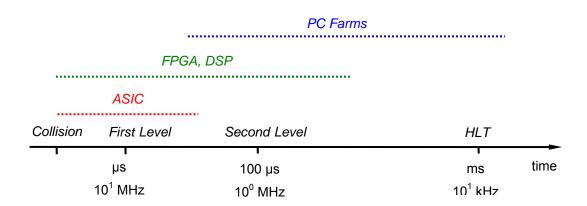

| FIGURE I-2: THE TRIGGER-LAYER LATENCY AND THE PROCESSING RATE ORDERS SET DIFFERENT REQUIREMENTS TO THE TECHNOLOGY CHOICES FOR THE VARIOUS TRIGGER LEVELS            |

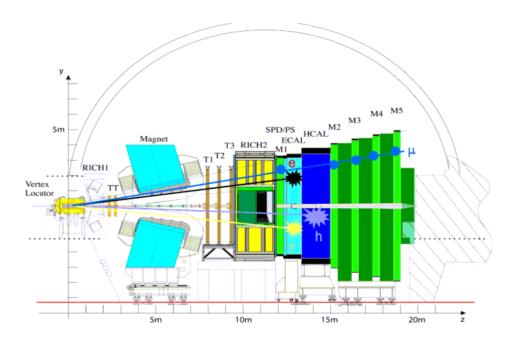

| Figure II-1: Since at high energies both the $b$ - and the $\overline{b}$ -hadrons are predominantly                                                                |

| PRODUCED IN THE SAME FORWARD CONE [10], THE DETECTOR COVERS LOW POLAR ANGLES UP TO                                                                                  |

| 300 MRAD IN ORDER TO ACHIEVE A HIGH PHYSICS PERFORMANCE. THE LHCB DETECTOR COMPRISES                                                                                |

| THE FOLLOWING SUB-DETECTORS: A VERTEX DETECTOR FOR A HIGH-PRECISION RECONSTRUCTION OF                                                                               |

| CHARGED PARTICLES TRACKS NEAR THE INTERACTION POINT; A TRACKING SYSTEM COMPRISING                                                                                   |

| FOUR STATIONS (TT AND T1-T3) FOR TRACK RECONSTRUCTION AND A PRECISE MOMENTUM                                                                                        |

| MEASUREMENT OF CHARGED PARTICLES; RING IMAGING CHERENKOV COUNTERS RICH1 AND                                                                                         |

| RICH2 FOR CHARGED PARTICLE IDENTIFICATION; A CALORIMETER SYSTEM (A SCINTILLATOR PAD                                                                                 |

| DETECTOR (SPD), A PRESHOWER DETECTOR (PS), AN ELECTROMAGNETIC CALORIMETER (ECAL),                                                                                   |

| AND A HADRON CALORIMETER (HCAL)) DEDICATED TO THE IDENTIFICATION OF ELECTRONS AND                                                                                   |

| HADRONS WITH MEASUREMENTS OF POSITION AND ENERGY FOR TRIGGER AND OFFLINE ANALYSIS;                                                                                  |

| FIVE MUON STATIONS (M1-M5) FOR MUON IDENTIFICATION AND LEVEL-0 INFORMATION6                                                                                         |

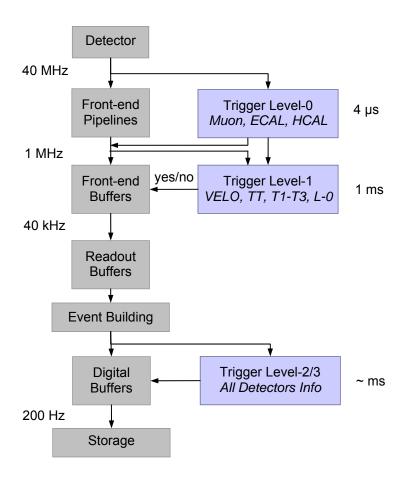

| FIGURE II-2: THE LHCB TRIGGER SYSTEM IN CONJUNCTION WITH SOME DATA ACQUISITION (DAQ)                                                                                |

| System Elements                                                                                                                                                     |

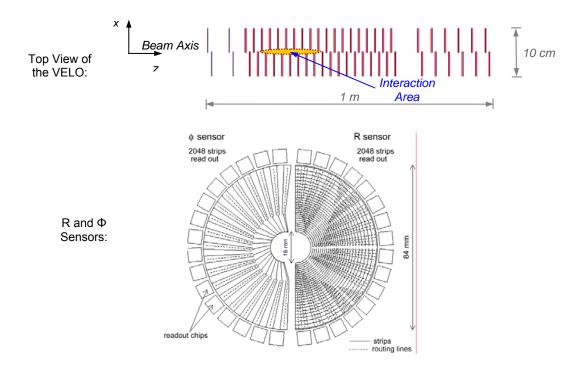

| FIGURE II-3: THE VERTEX LOCATOR [18] COMPRISES A SERIES OF SILICON STATIONS PLACED ALONG THE                                                                        |

| BEAM DIRECTION. EACH STATION CONSISTS OF A LEFT AND A RIGHT DETECTOR MODULE. EACH                                                                                   |

| MODULE, EXCEPT THOSE IN THE FIRST TWO STATIONS, IS COMPOSED OF TWO HALF-CIRCULAR                                                                                    |

| SENSORS MEASURING R AND $\Phi$ respectively. The first two stations are solely R-measuring                                                                          |

| STATIONS AND ARE PART OF THE LEVEL-0 PILE-UP VETO COUNTER. BOTH SENSOR TYPES FEATURE                                                                                |

| FINE STRIPS WHICH ALLOW FOR MEASUREMENTS WITH RESOLUTION IN THE MICROMETER RANGE8                                                                                   |

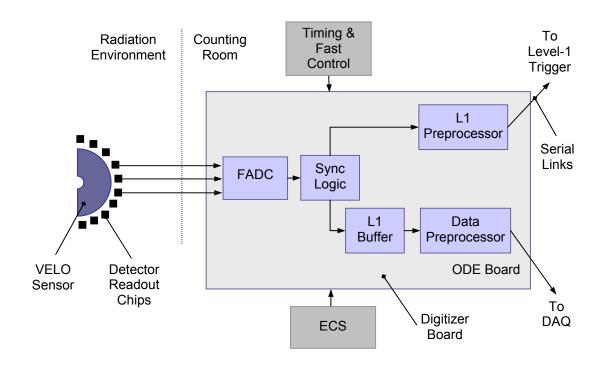

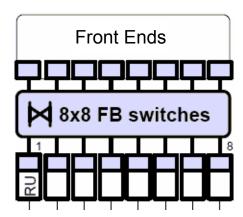

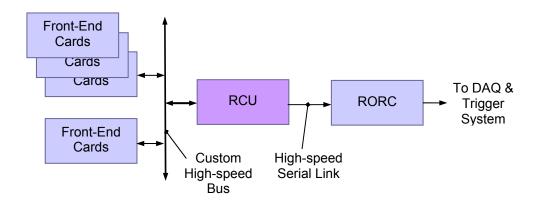

| FIGURE II-4: FRONT-END ELECTRONICS ARCHITECTURE                                                                                                                     |

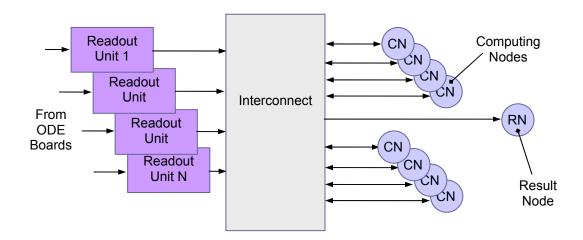

| FIGURE II-5: AN ABSTRACT VIEW OF THE TRIGGER SYSTEM ARCHITECTURE                                                                                                    |

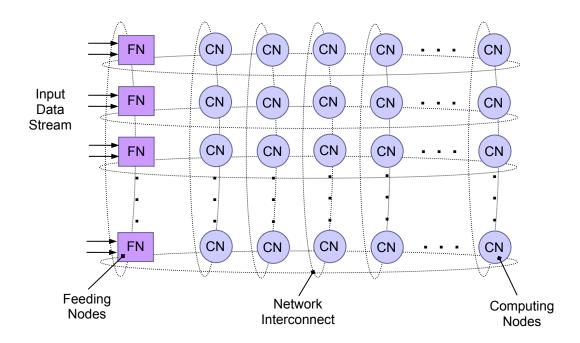

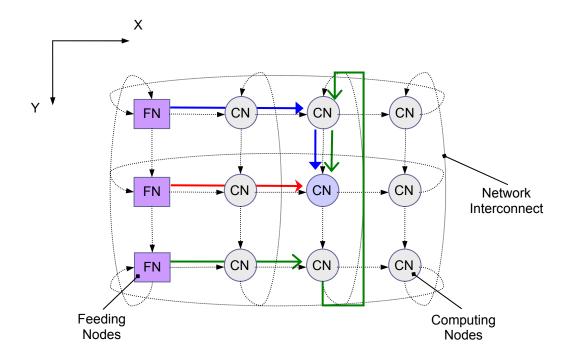

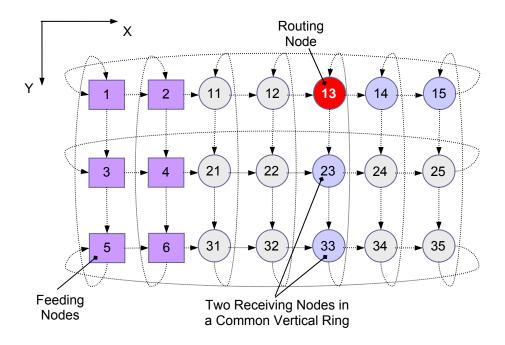

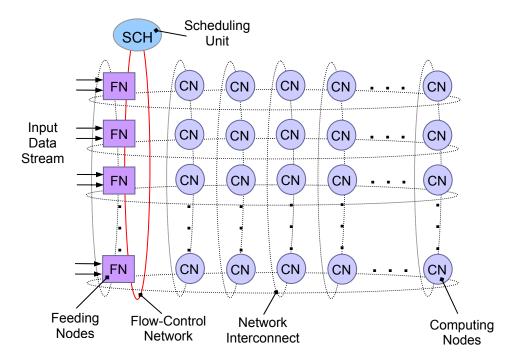

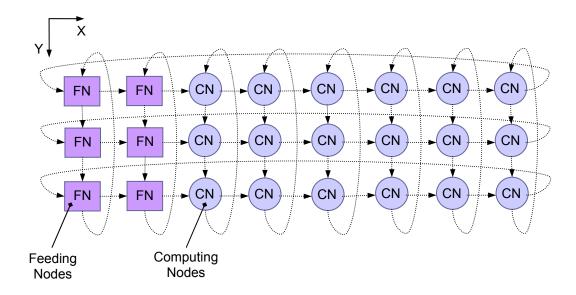

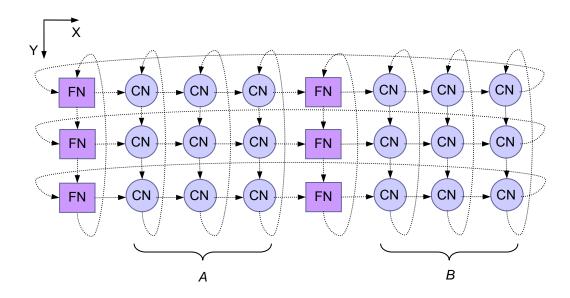

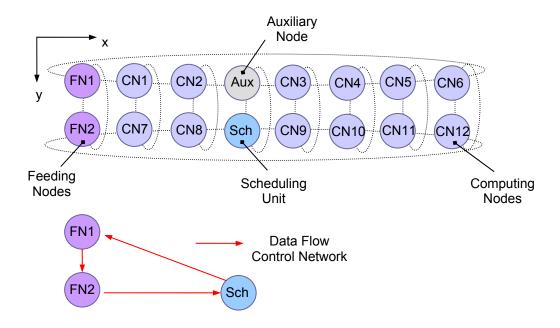

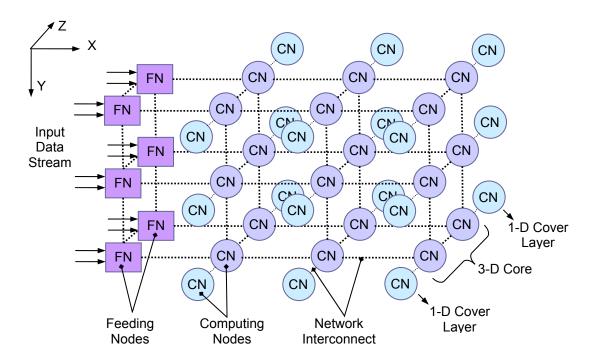

| FIGURE II-6: THE BASIC SYSTEM ARCHITECTURE IS A 2-D TORUS COMPRISING FEEDING NODES (FN) AND                                                                         |

| COMPUTING NODES THAT ARE INTERCONNECTED BY A HIGH-SPEED LOW-LATENCY NETWORK12                                                                                       |

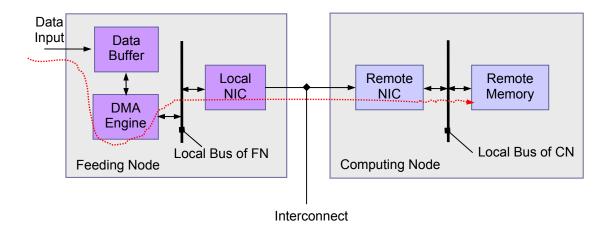

| FIGURE II-7: SUB-EVENT DATA PATH                                                                                                                                    |

| FIGURE II-8: DIMENSIONAL (X-Y) DATA ROUTING IS USED IN THE TORUS. FOR EVERY EVENT, MULTIPLE                                                                         |

| DATA PACKETS, EACH ONE ORIGINATING FROM A DIFFERENT FEEDING NODE, ARE COLLECTED AT A                                                                                |

| PARTICULAR TARGET COMPUTING NODE. THE NETWORK PATHS OF THE DIFFERENT PACKETS ARE                                                                                    |

| SHOWN BY DIFFERENT-COLOURED ARROWS WITH DIFFERENT ARROWHEADS                                                                                                        |

| FIGURE II-9: THE SYSTEM PROTOTYPE AT THE CHAIR OF COMPUTER SCIENCES AT KIP, UNIVERSITY OF                                                                           |

| Heidelberg17                                                                                                                                                        |

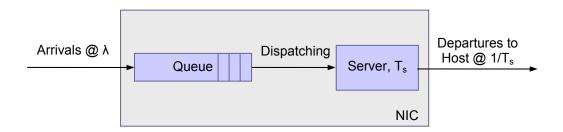

| FIGURE II-10: A NETWORK ADAPTOR PRESENTED AS A QUEUING SYSTEM                                                                                                       |

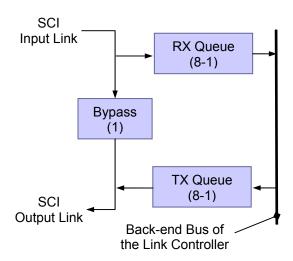

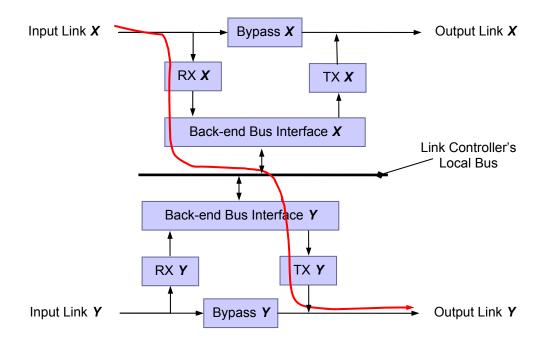

| FIGURE II-11: THE I/O STAGE OF AN SCI NODE PRESENTED AS A NETWORK OF QUEUES: PACKETS THAT                                                                           |

| HAVE TO TAKE OFF THE RING PASS THROUGH THE RECEIVING QUEUE; ALL PACKETS SENT BY THE                                                                                 |

| NODE GO THROUGH THE TRANSMITTING QUEUE; A PACKET WHICH HAS TO BY-PASS THE NODE IS                                                                                   |

| STORED IN THE BYPASS QUEUE IF THE NODE IS CURRENTLY TRANSMITTING ITS OWN PACKET. THE                                                                                |

| ONE-DIMENSIONAL CASE IS DEPICTED. IN CASE OF A TWO-DIMENSIONAL SCI NIC THE PICTURE HAS                                                                              |

| TO BE DUPLICATED: TWO LINK CONTROLLERS, ONE FOR EACH DIMENSION, SHARE A COMMON BACK-                                                                                |

| END BUS                                                                                                                                                             |

| FIGURE II-12: PERFORMANCE LIMITATIONS CAN BE OBSERVED WHEN TWO NODES SHARING A VERTICAL                                                                             |

| RING RECEIVE DATA CONCURRENTLY. THE MAXIMUM DATA TRANSFER RATE IS DETERMINED BY THE                                                                                 |

| PERFORMANCE OF THE LOCAL BUS OF THE LINK CONTROLLER                                                                                                                 |

| FIGURE II-13: RE-ROUTING REQUIRES THAT A PACKET PASSES THROUGH THE LINK CONTROLLER'S LOCAL                                                                          |

| BUS, WHOSE MAXIMUM TRANSFER RATE IN A 2-D TORUS HAS BEEN DETERMINED TO BE 450 MBYTE/S                                                                               |

| [9]                                                                                                                                                                 |

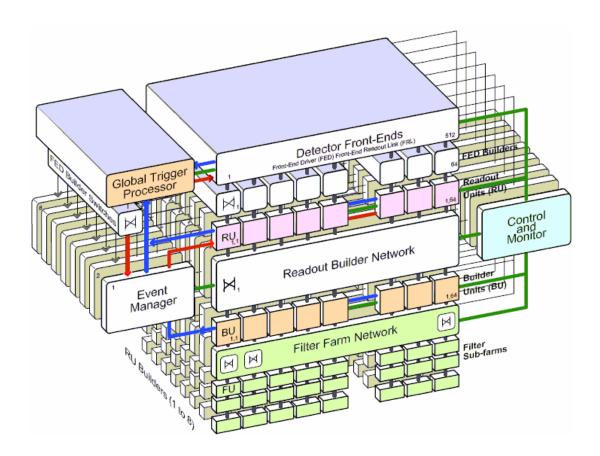

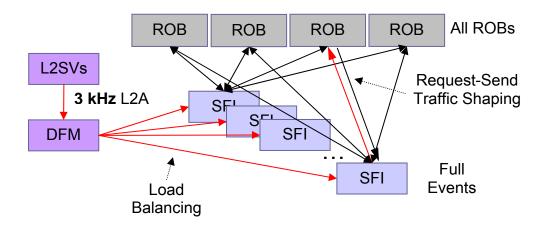

| FIGURE II-14: A 3-D VIEW OF THE CMS EVENT BUILDER [29]                                                                                                              |

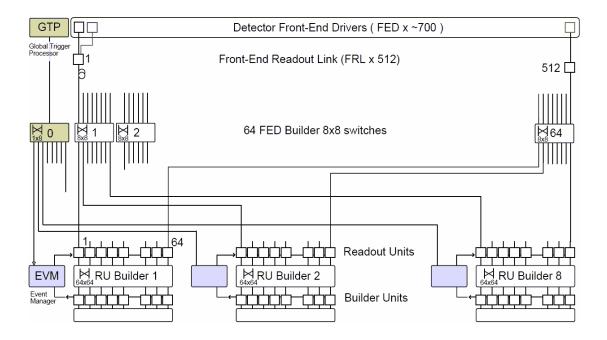

| FIGURE II-15: CONCEPTUAL DESIGN OF THE CMS EVENT BUILDER [29]                                                                                                       |

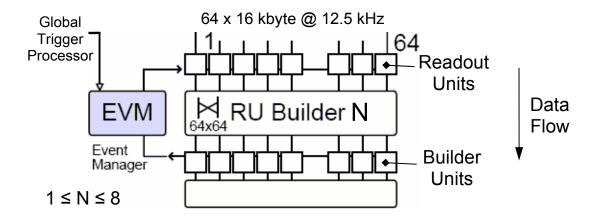

| FIGURE II-16: THE CMS FED BUILDER 24  FIGURE II-17: THE CMS R.I. BUILDER 25                                                                                         |

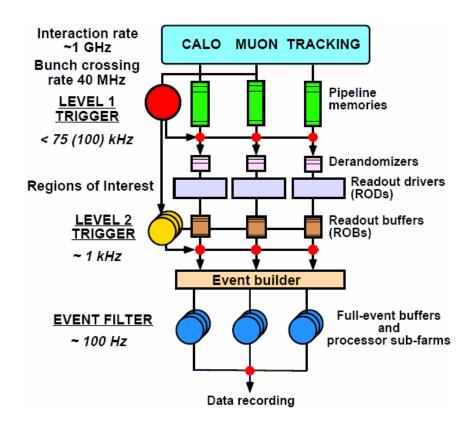

| FIGURE II-18: BLOCK DIAGRAM OF THE ATLAS TRIGGER/DAQ SYSTEM [31]                                                                                                                                                             | .26  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

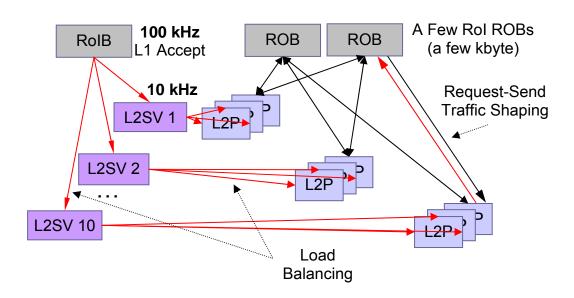

| FIGURE II-19: ROI BUILDING IN THE ATLAS LEVEL-2 TRIGGER                                                                                                                                                                      |      |

| FIGURE II-20: FULL EVENT BUILDING IN THE ATLAS HLT EVENT FILTERS                                                                                                                                                             |      |

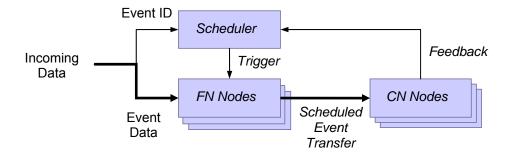

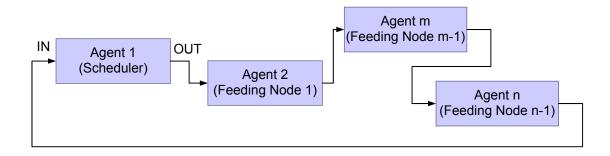

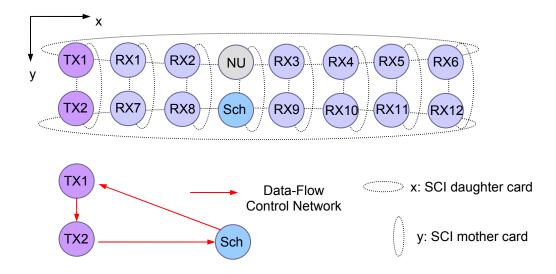

| FIGURE III-1: LOGICAL VIEW OF THE FLOW-CONTROLLED SYSTEM. THE TRANSFER OF EVENT DATA FROM                                                                                                                                    |      |

| THE FEEDING NODES TO THE COMPUTING NODES IS MADE UNDER THE SUPERVISION OF A SCHEDULI                                                                                                                                         |      |

| UNIT. THE SCHEDULER MAINTAINS A LIST OF AVAILABLE COMPUTING NODES AND CHOOSES THE N                                                                                                                                          |      |

| RECEIVING CN IN A WAY THAT PREVENTS CONGESTIONS IN THE SYSTEM                                                                                                                                                                | 29   |

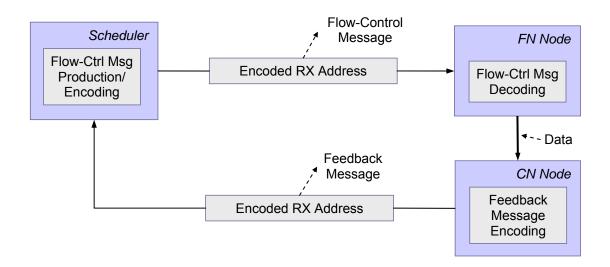

| FIGURE III-2: THE FLOW CONTROL SYSTEM EMPLOYS MAINLY TWO DEVICES, I.E. A CENTRALIZED                                                                                                                                         |      |

| SCHEDULING UNIT AND A CUSTOM SCALABLE POINT-TO-POINT SERIAL NETWORK. THE FORMER                                                                                                                                              |      |

| REALIZES THE DYNAMIC ALLOCATION OF FREE COMPUTING NODES. THE LATTER INTERCONNECTS                                                                                                                                            |      |

| THE SCHEDULER WITH THE FEEDING NODES IN ORDER TO INITIATE THE TRANSFER OF DATA TO A                                                                                                                                          | 20   |

| SPECIFIC COMPUTING NODE AT A SPECIFIC TIME.                                                                                                                                                                                  |      |

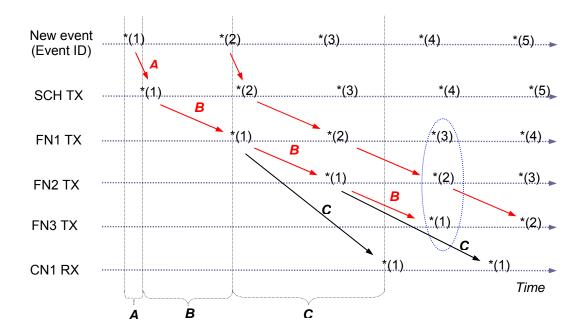

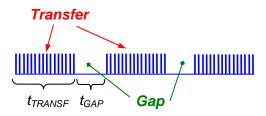

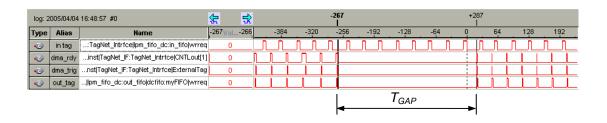

| FIGURE III-3: UPON RECEIVING A NEW EVENT THE SCHEDULER TRANSMITS A FLOW CONTROL MESSAGE TO THE PROPERTY OF T | Ю    |

| THE FIRST FEEDING NODE (FN1) IN THE CHAIN ( $A$ DENOTES THE LATENCY OF THE SCHEDULER).                                                                                                                                       | TOP. |

| AFTER A CERTAIN AMOUNT OF TIME, B, THE MESSAGE ARRIVES AT FN1; FN1 SENDS ITS SUB-EVEN                                                                                                                                        | 1    |

| AND FORWARDS THE CONTROL MESSAGE TO FN2 ( $B$ DENOTES THE LATENCY OF A FLOW CONTROL MESSAGE BETWEEN TWO ADJACENT NODES IN THE FLOW CONTROL CHAIN PLUS THE TIME THE SUB-                                                      |      |

| EVENT TRANSFER FROM THE DMA ENGINE TO THE LOCAL NETWORK ADAPTER (FIGURE II-7) TAKE                                                                                                                                           |      |

| WHEN FN2 SENDS ITS FIRST SUB-EVENT, FN1 TRANSFERS THE NEXT ONE TO ANOTHER NODE. THU                                                                                                                                          |      |

| THE FEEDING NODES NEVER SEND DATA SIMULTANEOUSLY TO THE SAME RECEIVER. THE TIME                                                                                                                                              | 3    |

| INTERVAL C DENOTES THE LATENCY OF THE PACKET THROUGH THE NETWORK, WHICH DIFFERS DU                                                                                                                                           | Œ    |

| TO DIFFERENT NETWORK PATHS.                                                                                                                                                                                                  |      |

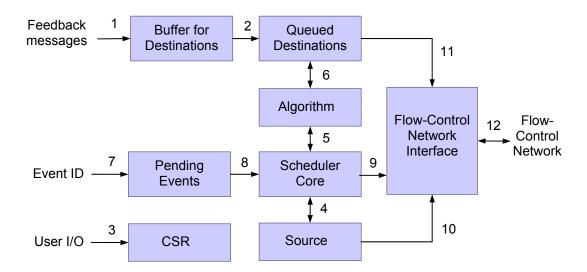

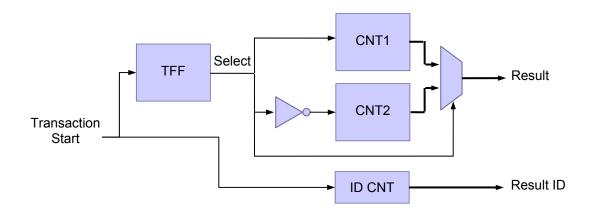

| FIGURE III-4: STRUCTURE OF THE SCHEDULER                                                                                                                                                                                     |      |

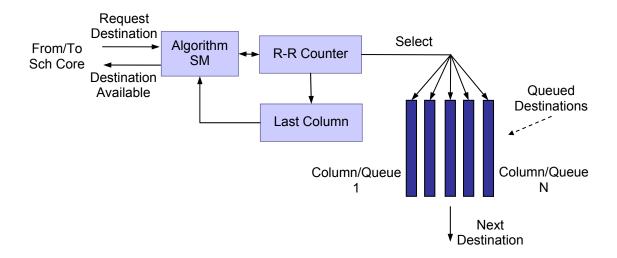

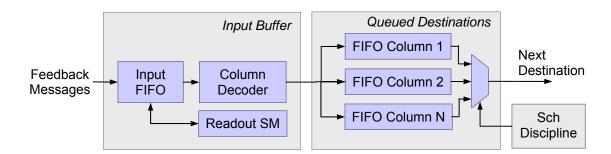

| FIGURE III-5: THE FIGURE SHOWS THE ARCHITECTURE OF THE 'QUEUED DESTINATIONS' UNIT AND THE                                                                                                                                    | .55  |

| 'ALGORITHM' UNIT IN FIGURE III-4.                                                                                                                                                                                            | 35   |

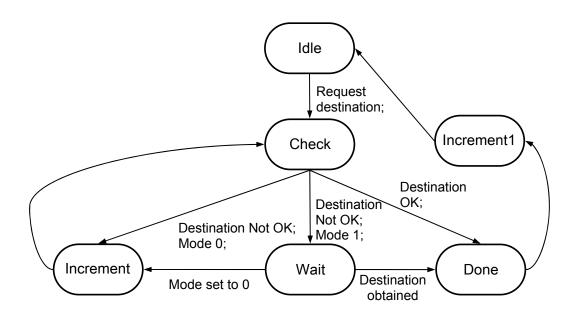

| FIGURE III-6: ALGORITHM STATE-TRANSITION DIAGRAM. WHEN THE CORE OF THE SCHEDULER REQUEST                                                                                                                                     |      |

| DESTINATION, THE STATE MACHINE CHECKS WHETHER THE SELECTED QUEUE CONTAINS AVAILABI                                                                                                                                           | LΕ   |

| DESTINATION ADDRESSES. IF NOT, THE R-R COUNTER IS INCREMENTED. THE LATTER, HOWEVER,                                                                                                                                          |      |

| ONLY HAPPENS IF THE MODE OF OPERATION SET ALLOWS A TORUS COLUMN TO BE SKIPPED (MODE                                                                                                                                          | 0).  |

| THE DESTINATION OBTAINED IS GRANTED TO THE CORE OF THE SCHEDULER ONLY IF IT RESIDES IN                                                                                                                                       |      |

| DIFFERENT COLUMN THAN THE LAST ONE THAT WAS USED.                                                                                                                                                                            | 35   |

| FIGURE III-7: BY-PASS TRAFFIC HAS PRIORITY OVER TRANSMISSION. THEREFORE, ONE OF THE TWO                                                                                                                                      |      |

| FEEDING NODES PER ROW IS UNABLE TO SEND ITS PACKETS FREELY DUE TO HEAVY BY-PASS TRAFF                                                                                                                                        | IC   |

| ORIGINATING FROM THE OTHER ONE. THUS THE ARCHITECTURE SHOWN IN THE FIGURE DOES NOT                                                                                                                                           |      |

| DEMONSTRATE THE EXPECTED DATA RATE.                                                                                                                                                                                          |      |

| FIGURE III-8: THE ARCHITECTURE WITH DISPLACED FEEDING NODES ALLOWS OVERCOMING THE HEAVY                                                                                                                                      |      |

| PASS PROBLEM THAT CHARACTERIZES THE ARCHITECTURE SHOWN IN FIGURE III-7 IF THE SYSTEM                                                                                                                                         |      |

| PROPERLY LOAD-BALANCED                                                                                                                                                                                                       |      |

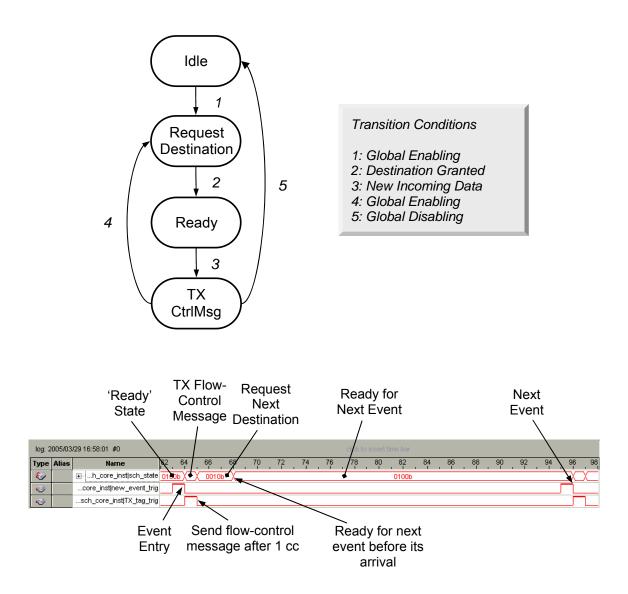

| FIGURE III-9: MAIN STATE MACHINE DIAGRAM. THE SCHEDULER ACCOUNTS FOR A SINGLE CLOCK CYCLI                                                                                                                                    |      |

| LATENCY. THE MEASUREMENTS IN THE FIGURE ARE PERFORMED IN A SYSTEM RUN AT AN INPUT DA                                                                                                                                         |      |

| RATE OF ABOUT 2 MHZ. THE SPEED OF THE CLOCK FED TO THE CORE OF THE SCHEDULER AND TO T<br>PERIPHERAL UNITS RELEVANT TO THE DESTINATION SELECTION IS 70 MHZ. UNDER THESE                                                       | HE   |

| CIRCUMSTANCES THERE ARE ABOUT 30 CLOCK CYCLES FOR THE SCHEDULER CORE TO OBTAIN THE                                                                                                                                           |      |

| NEXT DESTINATION WITHOUT CAUSING UNDESIRABLE LATENCY. THE UTILIZED ALGORITHM AND T                                                                                                                                           |      |

| QUEUING REQUIRE 2 CLOCK CYCLES. THE DESIGN OF THE SCHEDULER FORESEES RUNNING THE                                                                                                                                             | ш    |

| SCHEDULER CORE AT A HIGHER FREQUENCY IN CASE OF A MORE COMPLEX SCHEDULING DISCIPLING                                                                                                                                         | E    |

| SOLEDOEEK COMENT A MODEL A REQUESTO I I WORLD OF A MODEL COME EET GOLEDOEIKO BISCH EIN                                                                                                                                       |      |

| FIGURE III-10: QUEUING OF DESTINATION ADDRESSES. THE ARCHITECTURE WAS DESIGNED TO FIT THE                                                                                                                                    |      |

| CHOSEN SCHEDULING DISCIPLINE AND THE SYSTEM TOPOLOGY. CHOOSING ANOTHER SCHEDULING                                                                                                                                            | i    |

| DISCIPLINE OR MODIFYING THE SYSTEM TOPOLOGY MAY REQUIRE ANOTHER SOLUTION                                                                                                                                                     | 39   |

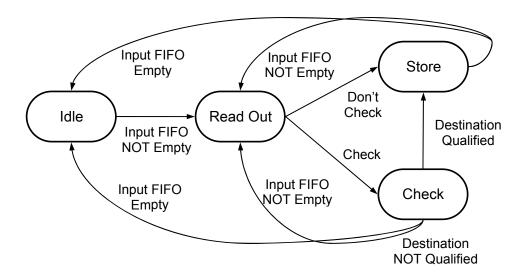

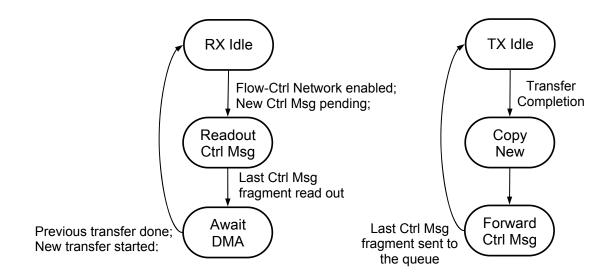

| FIGURE III-11: STATE DIAGRAM OF THE INPUT BUFFER READOUT STATE MACHINE                                                                                                                                                       | .40  |

| FIGURE III-12: ARCHITECTURE OF THE FLOW CONTROL NETWORK INTERFACE IN THE SCHEDULER                                                                                                                                           | .41  |

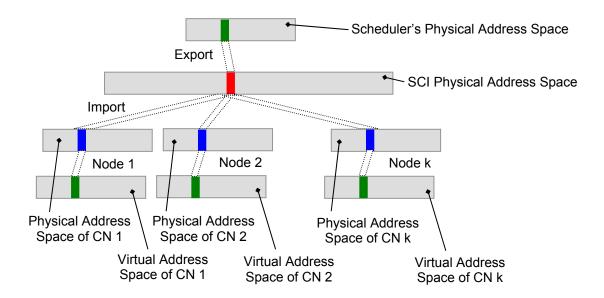

| FIGURE III-13: EVERY COMPUTING NODE IMPORTS A DEDICATED MEMORY REGION THAT IS EXPORTED BY                                                                                                                                    | Ý    |

| THE HOST OF THE SCHEDULER TO ESTABLISH COMMUNICATION CHANNELS FOR THE TRANSFER OF                                                                                                                                            |      |

| FEEDBACK MESSAGES. THE SHARED MEMORY PARADIGM ALLOWS THIS TRANSFER TO BE PERFORM                                                                                                                                             |      |

| BY EXECUTING WRITES TO REMOTE MEMORY, WHICH IS EASILY DONE IN USER SOFTWARE                                                                                                                                                  | .42  |

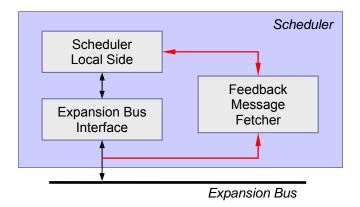

| FIGURE III-14: THE FETCHER LATCHES THE DATA TRANSFERRED VIA THE EXPANSION BUS IF THE                                                                                                                                         |      |

| TRANSACTION IS INITIATED AGAINST AN ADDRESS OF INTEREST THAT IS SPECIFIED IN THE                                                                                                                                             |      |

| INITIALIZATION PHASE. THE ADDRESS OF INTEREST EQUALS THE PHYSICAL ADDRESS OF THE MEMO                                                                                                                                        | )RY  |

| WHEN MAPPING THE MEMORY REGION, A FUNCTION CALLABLE FROM USER SPACE [34] IS USED FOR         |

|----------------------------------------------------------------------------------------------|

| TRANSLATING THE VIRTUAL ADDRESS INTO THE CORRESPONDING PHYSICAL ADDRESS42                    |

| FIGURE III-15: FORMAT OF A FEEDBACK MESSAGE. THE COL_POSITION AND THE ROW_POSITION           |

| FIELDS REPRESENT THE NUMBER OF THE TORUS COLUMN AND THE ROW IN WHICH THE NODE RESIDES.       |

| SINCE THERE IS MORE THAN ONE RECEIVING BUFFER PER COMPUTING NODE, THE BUFF_NUM FIELD         |

| IDENTIFIES THE RECEIVING BUFFER WITHIN A NODE                                                |

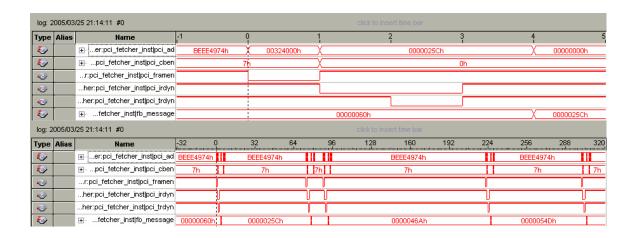

| FIGURE III-16: ASYNCHRONOUS RECEPTION OF FEEDBACK MESSAGES AT THE SCHEDULER. FIVE            |

| TRANSACTIONS CAN BE DISTINGUISHED IN THE LOWER TRACE. EACH ONE REPRESENTS THE TRANSFER       |

| OF A FEEDBACK MESSAGE ORIGINATING FROM A DIFFERENT COMPUTING NODE                            |

|                                                                                              |

| FIGURE III-17: A SKETCH OF THE ALICE TPC READ-OUT CHAIN. ONE RCU READS DATA OUT OF 32        |

| FRONT-END CARDS [35], PERFORMS SUB-EVENT BUILDING, ADDS HEADER INFORMATION, AND              |

| TRANSMITS THE DATA TO THE INPUTS OF THE DAQ AND THE TRIGGER SYSTEM                           |

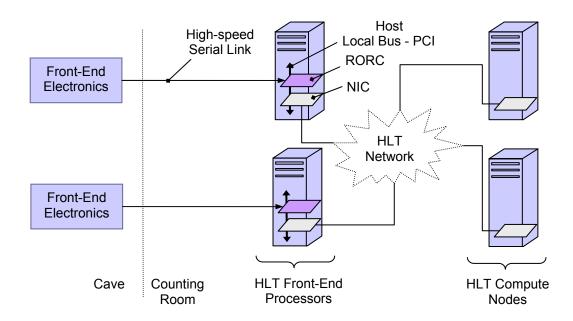

| FIGURE III-18: EACH HLT FRONT-END PROCESSOR NODE IS COMPLEMENTED BY A PCI EXPANSION CARD     |

| BASED ON RECONFIGURABLE HARDWARE UNITS. THE CARD RECEIVES DATA COMING FROM ALL               |

| MAJOR ALICE DETECTOR FRONT-END ELECTRONICS. SUBSEQUENTLY, IT PUSHES THE DATA                 |

| THROUGH THE LOCAL EXPANSION BUS TO THE HOST MAIN MEMORY, WHERE THEY ARE ACCESSIBLE           |

| TO THE HOST CPU. BEFORE TRANSFERRING THE DATA TO THE MAIN MEMORY, HOWEVER, THE RORC          |

| CARD PERFORMS DATA PRE-PROCESSING IN HARDWARE TO ASSIST THE CPU. THIS WAY IT                 |

| ACCELERATES THE TRIGGER ALGORITHM                                                            |

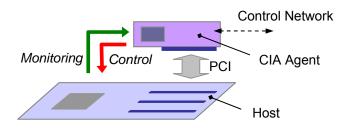

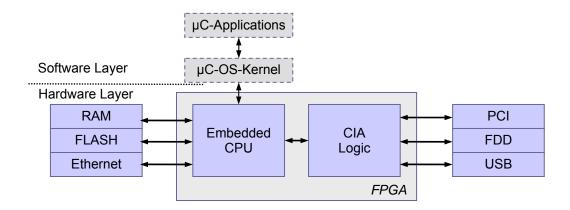

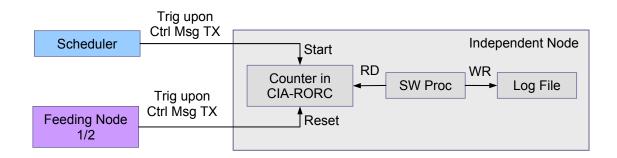

| FIGURE III-19: THE INDEPENDENT CIA AGENT CAN MONITOR THE STATUS OF THE INSTALLED PCI DEVICES |

| BY ACCESSING THEM THROUGH THE HOST PCI BUS. ON THE OTHER HAND, THE CARD CAN ALSO             |

| ACTIVELY CONTROL THE HOST BY EMULATING CERTAIN I/O DEVICES AND PASSING CONTROL               |

| COMMANDS THROUGH THE PCI BUS TO THE HOST                                                     |

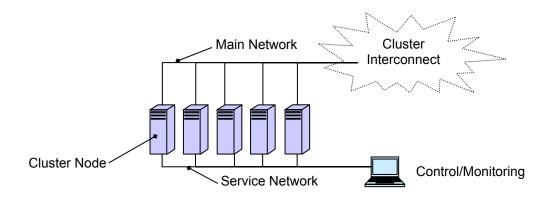

| FIGURE III-20: AUTOMATED CLUSTER CONTROL AND MONITORING ARE REALIZED REMOTELY VIA AN         |

| INDEPENDENT SERVICE NETWORK WHICH INTERCONNECTS THE DEDICATED AUTONOMOUS CIA                 |

| AGENTS INSTALLED IN EVERY NODE                                                               |

| FIGURE III-21: THE CIA AGENT REQUIRES A COST-EFFECTIVE, RELIABLE, FLEXIBLE, REDUCED-POWER    |

| SOLUTION THAT IS EASY TO MAINTAIN, IN ORDER TO IMPLEMENT SPECIAL FUNCTIONALITIES.            |

| CONSEQUENTLY, AN EMBEDDED SYSTEM RUNNING AN OPEN MODULAR EMBEDDED OPERATING                  |

|                                                                                              |

| SYSTEM WAS CHOSEN. THE CIA-RORC CARD WAS DESIGNED TO PROVIDE A HARDWARE PLATFORM             |

| (FIGURE III-22, FIGURE III-23) THAT ALLOWS THE EMBEDDED SYSTEM TO BE PORTED TO IT            |

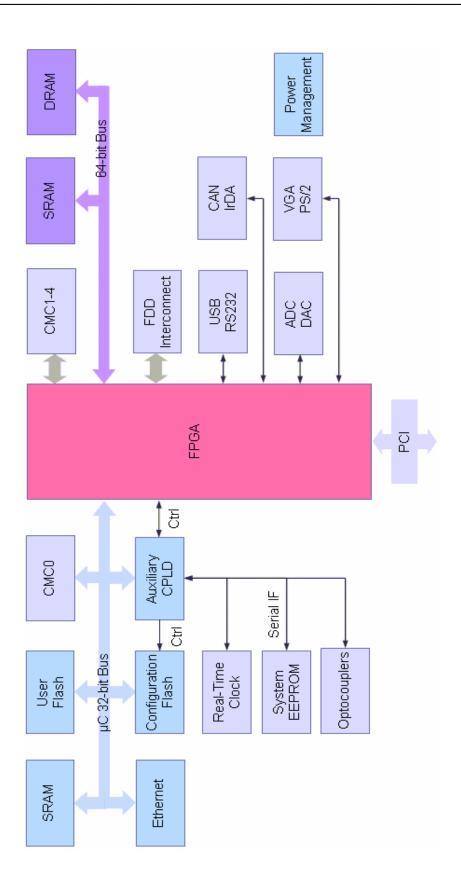

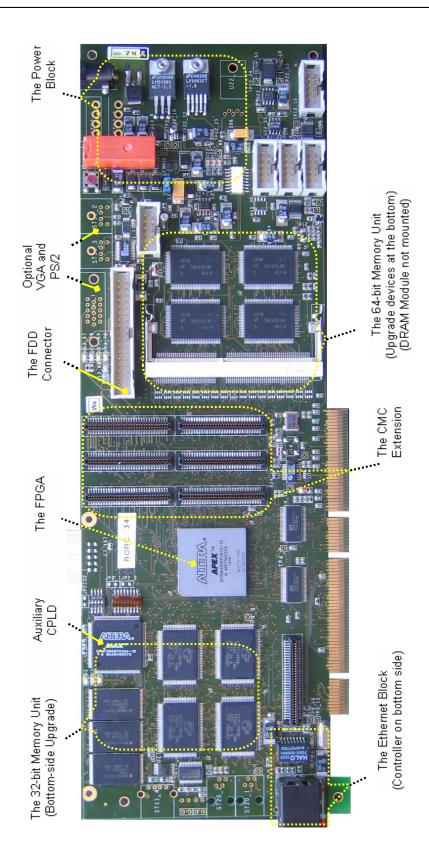

| FIGURE III-22: THE CIA-RORC BOARD: A SIMPLIFIED BLOCK DIAGRAM                                |

| FIGURE III-23: THE CIA-RORC BOARD. THE DATA PROVIDED IN [43 - 56] ARE USED FOR THE           |

| DEVELOPMENT OF THE BOARD                                                                     |

| FIGURE III-24: THE FLOW CONTROL SYSTEM NETWORK IMPLEMENTS A RING, WHERE DATA FLOW ONLY IN    |

| ONE DIRECTION. THE TERMS IN BRACKETS IDENTIFY THE AGENTS IN THE ACTUAL SET-UP. THE           |

| SCHEDULER FEEDS THE NETWORK WITH FLOW CONTROL MESSAGES. UPON RECEPTION OF SUCH A             |

| MESSAGE THE FLOW CONTROL INTERFACE UNIT PERFORMS A BASIC ERROR CHECK, DECODES THE            |

| MESSAGE, TRIGGERS THE DMA ENGINE TO INITIATE THE DATA TRANSFER, AND FORWARDS THE             |

| MESSAGE TO THE NEXT AGENT. ALL MESSAGES ARRIVE BACK AT THE SCHEDULER AFTER A CERTAIN         |

| AMOUNT OF TIME, WHERE A DATA INTEGRITY CHECK IS PERFORMED. DEPENDING ON THE MODE OF          |

| OPERATION, A FEEDING NODE MAY OR MAY NOT MODIFY THE MESSAGES OR TRANSMIT SELF-               |

| GENERATED MESSAGES TO THE FLOW CONTROL NETWORK                                               |

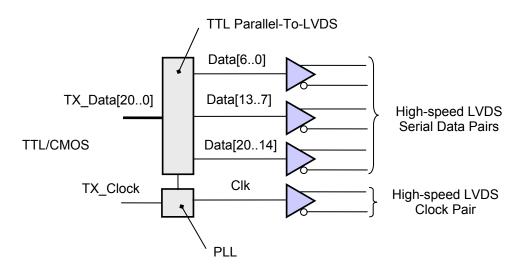

| FIGURE III-25: THE FLOW CONTROL NETWORK INTERFACE CARD DEPLOYS A 21-BIT CHIPSET WITH THE     |

| FOLLOWING POSSIBLE USER CONFIGURATION: TWO PAYLOAD BYTES, THREE CONTROL BITS, AND TWO        |

| PARITY BITS. ALL BITS ARE TRANSFERRED OVER THREE DIFFERENTIAL DATA PAIRS, WHERE EACH         |

| DIFFERENTIAL PAIR IS USED FOR TRANSFERRING SEVEN OF THE TWENTY-ONE PARALLEL DATA BITS.       |

| ONE EXTRA DIFFERENTIAL PAIR IS USED FOR TRANSFERRING THE CLOCK. THIS HIGH-SPEED CLOCK IS     |

| MANAGED BY PHASE-LOCKED LOOPS (PLL) IN THE TRANSCEIVERS                                      |

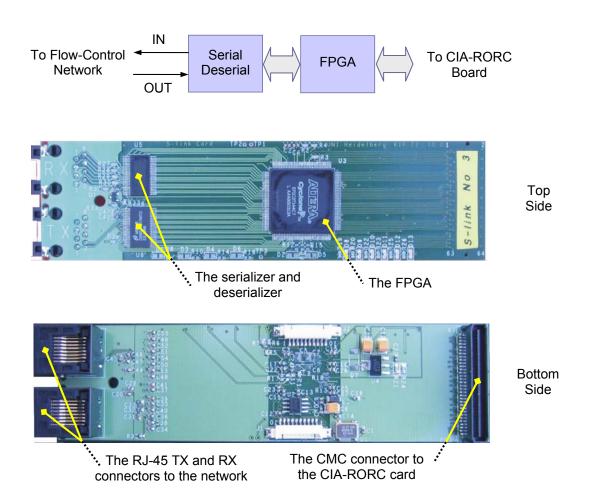

| FIGURE III-26: THE FLOW CONTROL NETWORK INTERFACE CARD WAS DESIGNED AS A SMALL-FACTOR CMC    |

|                                                                                              |

| CARD WHICH CAN BE PLUGGED INTO THE CIA-RORC BOARD. THE MAXIMUM INPUT TRANSMISSION            |

| CLOCK SUPPORTED BY THE CHOSEN CHIPSET IS 85 MHZ, WHICH CORRESPONDS TO A DATA RATE OF         |

| 1.785 GBPS. THE MAXIMUM SPEED ACHIEVABLE DEPENDS ALSO ON OTHER FACTORS LIKE UTILIZED         |

| CONNECTORS, PCB MATERIAL, AND TYPE AND LENGTH OF THE INTERCONNECT MEDIA BETWEEN THE          |

| TRANSMITTER AND THE RECEIVER. THE DEVELOPED CARD DEPLOYS LOW-COST CAT5E RJ-45                |

| CONNECTORS. THE FEEDING NODES ARE INTERCONNECTED THROUGH STANDARD CAT6 STP                   |

| (SHIELDED TWISTED PAIR) CABLES WHICH ARE 2 METERS LONG. THE LINK IS OPERATED AT A DATA       |

| RATE OF 630 MBPS (480 MBPS DATA PAYLOAD).                                                    |

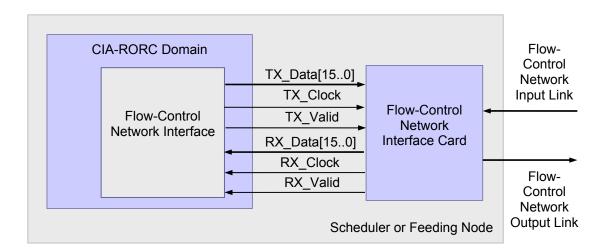

| FIGURE III-27: THE CONNECTION BETWEEN THE HOST CIA-RORC BOARD AND THE ASSOCIATED             |

| INTERFACE CARD IS FULL-DUPLEX. EACH DIRECTION COMPRISES 16 DATA SIGNALS                      |

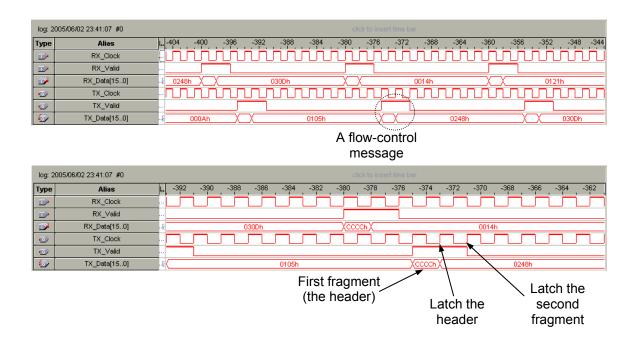

| (TX_DATA/RX_DATA), A FLAG BIT (TX_VALID/RX_VALID) USED TO MARK EACH 16-BIT WORD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AS    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| VALID OR INVALID, AND A STROBE SIGNAL (TX_CLOCK/RX_CLOCK) FOR LATCHING THE INCOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| DATA. SIXTEEN BITS OF DATA ARE TRANSFERRED ON EVERY RISING EDGE OF THE STROBE SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| THE RATE OF THE STROBE SIGNAL IS ADJUSTABLE, IT IS SET TO 30 MHZ IN THE SET-UP. THE CLO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| FREQUENCY OF THE HIGH-SPEED LVDS LINK (FIGURE III-25) IS 7 TIMES HIGHER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 59    |

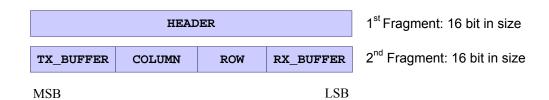

| FIGURE III-28: FORMAT OF A FLOW CONTROL MESSAGE TRANSFERRED THROUGH THE FLOW CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |

| NETWORK. THE FIRST FRAGMENT IS A HEADER THAT IDENTIFIES THE TYPE OF MESSAGE. THE HEADER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ADER  |

| STRING IS DESIGNED TO BE MODIFIABLE (SECTION VII.B). IN THIS WORK, ONLY MESSAGES THAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| INITIATE DATA TRANSFER WERE USED. THE DESTINATION ADDRESS IS ENCODED BY THE FIELDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| COLUMN, ROW AND RX_BUFFER. THE FIELDS COLUMN AND ROW GIVE THE X AND Y COORDINA'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TES   |

| OF THE DESTINATION NODE IN THE 2-D TORUS CORRESPONDINGLY. THE FIELD RX BUFFER IS T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| RECEIVING BUFFER OFFSET (SEE ALSO SECTION III.F). THE FIELD TX_BUFFER SPECIFIES THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| ADDRESS OF THE SUB-EVENT IN THE FEEDING NODE SINCE THE LATTER CAN BUFFER SEVERAL SU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | R.    |

| EVENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

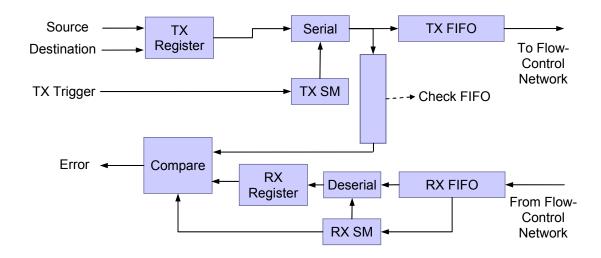

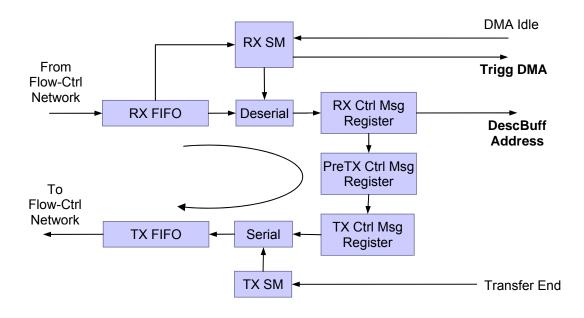

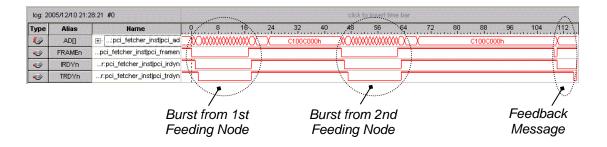

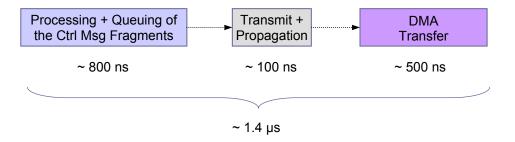

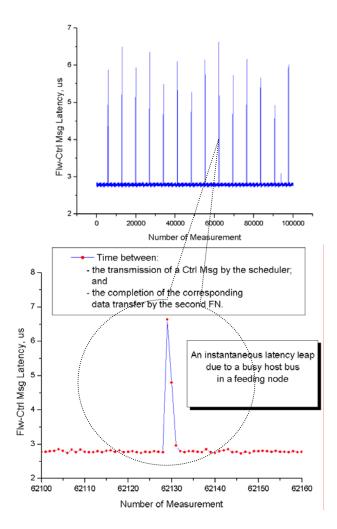

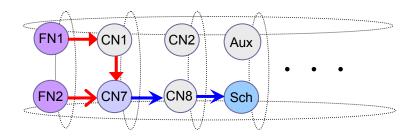

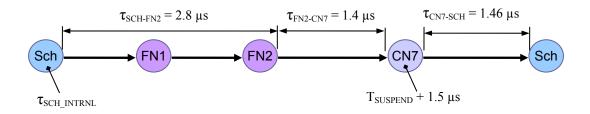

| FIGURE III-29: Transfer of a Flow Control Message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

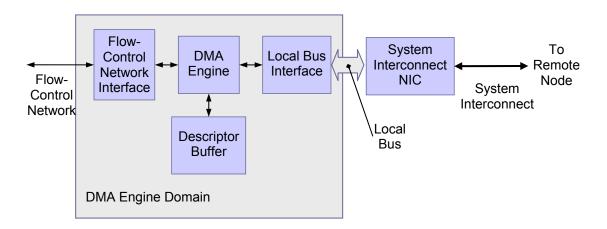

| FIGURE III-30: STRUCTURE AND INTERFACE OF THE DMA DOMAIN IN THE FEEDING NODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |

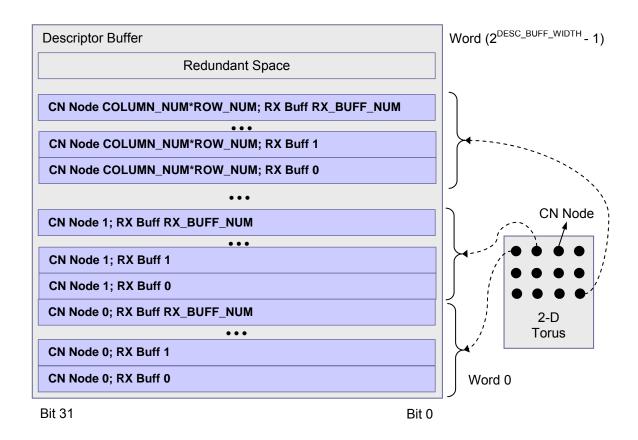

| FIGURE III-31: THE DESCRIPTOR BUFFER FORMAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| FIGURE III-32: FORMAT OF A MOCK-UP DATA WORD TRANSFERRED BY THE FEEDING NODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 63    |