### **DISSERTATION**

submitted

to the

Combined Faculty for the Natural Sciences and Mathematics

of

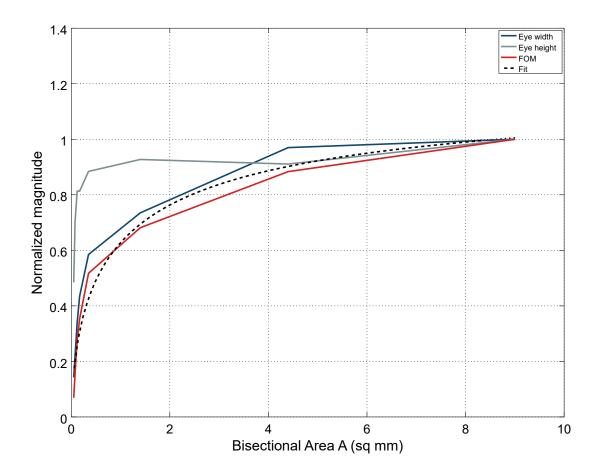

Heidelberg University, Germany for the degree of Doctor of Natural Sciences

## Put forward by

| Dipl.Phys. Dipl.Inf. Maximilian Thürmer |  |

|-----------------------------------------|--|

| Born in Heidelberg on August 31st, 1983 |  |

| Date of oral examination:               |  |

Modelling and performance analysis of multigigabit serial interconnects using real number based analog verification methods

Advisor: Prof. Dr. Ulrich Brüning

# Danksagungen

Wissenschaftlich gesehen mögen wir alle auf den Schultern von Giganten stehen, doch selbst dieser aufrechte Stand ist uns nur möglich, dank der uns liebenden Menschen, die sich um uns sorgen und Worte der Empathie für uns in den Phasen finden, in denen wir sie am nötigsten haben.

Daher danke ich meiner Familie aus vollem Herzen für all ihre Unterstützung, besonders während der fordernden letzten Monate. Dies gilt im höchsten Maße meiner Frau und meiner Tochter, die mich für diese Zeit so oft haben entbehren müssen und ohne deren liebevolle Fürsorge und Aufmunterungen diese Arbeit schlicht nicht möglich gewesen wäre. Dank gilt auch meinen Eltern und deren Partner, meiner Schwester und deren Familie sowie meiner Schwiegermutter für die zahllosen guten Gespräche und Aufmunterungen sowie deren fortwährendes Interesse am Fortschritt meiner Arbeit.

Ebenso danke ich meinen Kollegen, inmitten und mit Hilfe derer diese Arbeit entstanden ist. Dies gilt besonders für die enge Zusammenarbeit mit Markus Müller, aber ebenso für die anderen Mitglieder unseres kleinen, aber sehr engagierten Teams, in dem die zahllosen Diskussionen, die zu führen waren, stets zu produktiven und kreativen Ideen inspirierten.

Abschließend gilt mein Dank Herrn Prof. Dr. Brüning für die Möglichkeit, diese Arbeit anzufertigen sowie für sein stets offenes Ohr und die anregenden, fachlichen Diskussionen.

# Contents

| ı | intro | auction    |                                                         |    |

|---|-------|------------|---------------------------------------------------------|----|

|   | 1.1   | Challe     | enges in contemporary design and analysis methodologies | 4  |

|   | 1.2   | Structi    | ure of this work                                        | 7  |

| 2 | Elec  | trical se  | erializer based multi-gigabit communication links       | ç  |

|   | 2.1   | Mathe      | matical definitions and relations                       | Ò  |

|   | 2.2   | Link s     | ystem overview and nomenclature                         | 12 |

|   |       | 2.2.1      | The bit error rate                                      | 13 |

|   |       | 2.2.2      | Interaction with higher communication layers            | 17 |

|   |       | 2.2.3      | Power distribution                                      | 21 |

|   |       | 2.2.4      | Phase locked loop                                       | 24 |

|   |       | 2.2.5      | Transmitter                                             | 31 |

|   |       | 2.2.6      | Receiver                                                | 34 |

|   |       |            | 2.2.6.1 Clock data recovery circuit                     | 35 |

| 3 | Elec  | trical tra | ansmission channels and equalization                    | 41 |

|   | 3.1   | The bi     | trate capacity                                          | 44 |

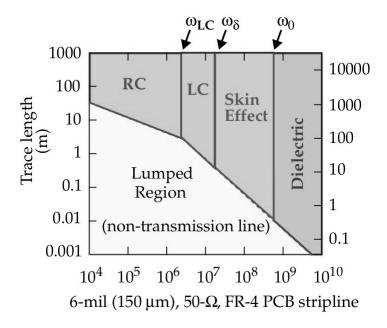

|   | 3.2   | Perfor     | mance regions and the Johnson Signal Model              | 46 |

|   |       | 3.2.1      | Lumped Element Region                                   | 48 |

|   |       | 3.2.2      | RC Region                                               | 49 |

|   |       | 3.2.3      | LC Region                                               | 50 |

|   |       | 3.2.4      | Skin-effect Region                                      | 50 |

|   |       | 3.2.5      | Dielectric loss Region                                  | 51 |

|   |       | 3.2.6      | Waveguide dispersion region                             | 52 |

|   |       | 3.2.7      | Johnson Signal Model for a coaxial transmission line    | 52 |

|   | 3.3   | Equali     | zation techniques                                       | 65 |

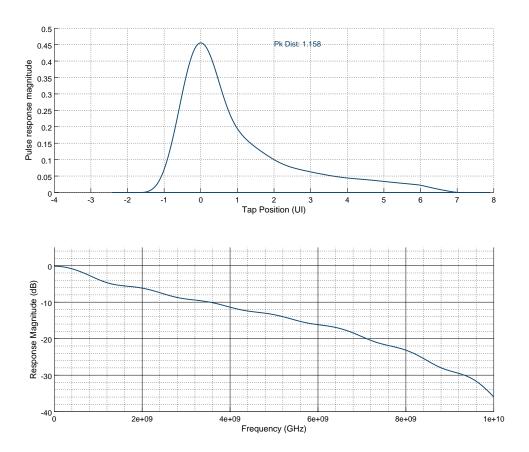

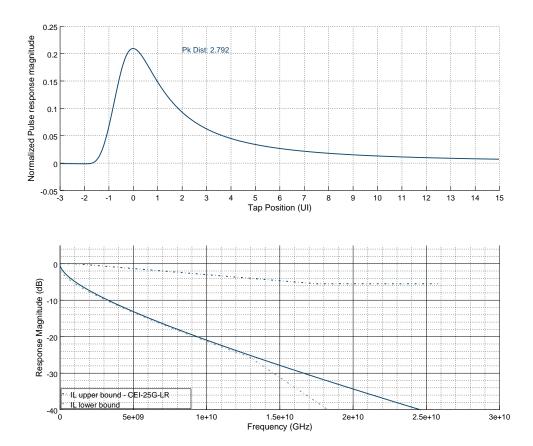

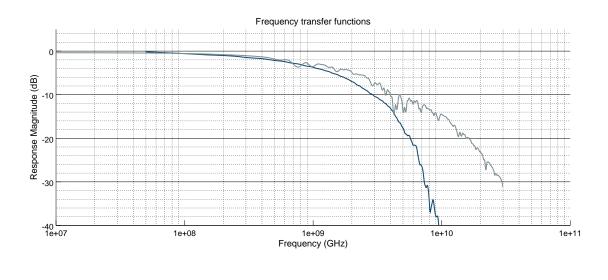

|   |       | 3.3.1      | Finite impulse response filter                          | 65 |

|   |       | 3.3.2      | Continuous time linear equalizer                        | 68 |

|   |       | 3.3.3      | Decision feedback equalization                          | 70 |

|   |       | 3.3.4      | Equalizer adaption                                      | 73 |

|   | 3 4   | I ine C    | oding and nower spectral density                        | 76 |

viii Contents

| 4 | Seri | alizer s                               | ystem component modelling                                     | 81  |  |

|---|------|----------------------------------------|---------------------------------------------------------------|-----|--|

|   | 4.1  | Gener                                  | al Real Number Modelling Considerations                       | 85  |  |

|   | 4.2  | The op                                 | penMGT framework                                              | 91  |  |

|   |      | 4.2.1                                  | Leaf cells                                                    | 92  |  |

|   |      | 4.2.2                                  | Testbenches                                                   | 95  |  |

|   | 4.3  | The op                                 | penMGT C and Octave modelling extension (OCM)                 | 95  |  |

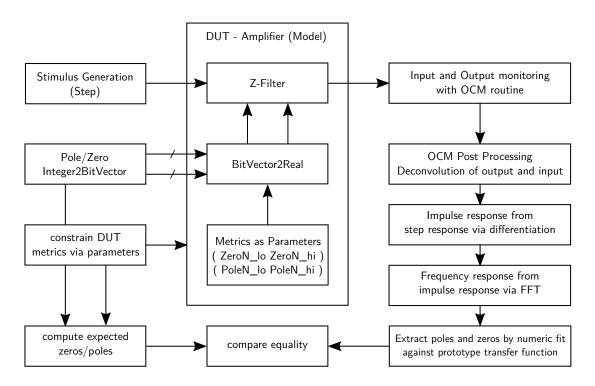

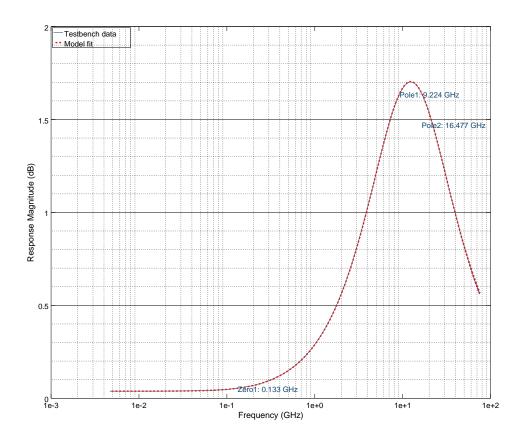

|   |      | 4.3.1                                  | General architecture                                          | 96  |  |

|   |      | 4.3.2                                  | Self consistency of testbench and model                       | 99  |  |

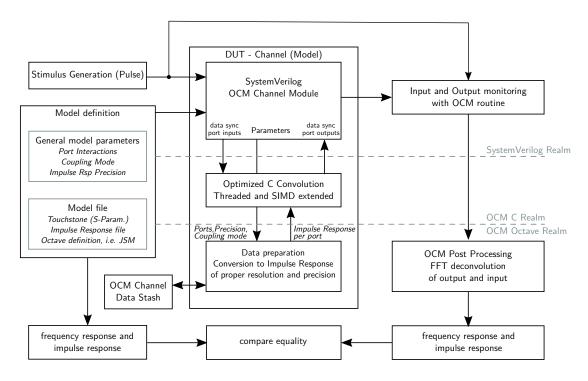

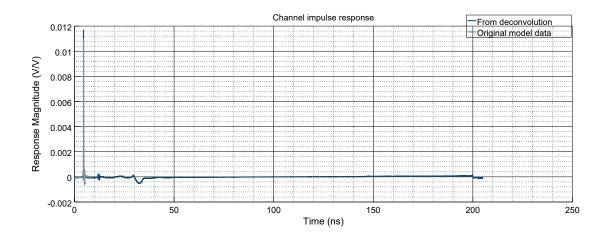

|   | 4.4  | Chann                                  | nel modelling process                                         | 101 |  |

|   |      | 4.4.1                                  | OCM data preparation                                          | 103 |  |

|   |      | 4.4.2                                  | Optimized C convolution routine                               | 105 |  |

|   |      | 4.4.3                                  | SystemVerilog considerations                                  | 106 |  |

|   |      | 4.4.4                                  | Testbench and performance comparison                          | 109 |  |

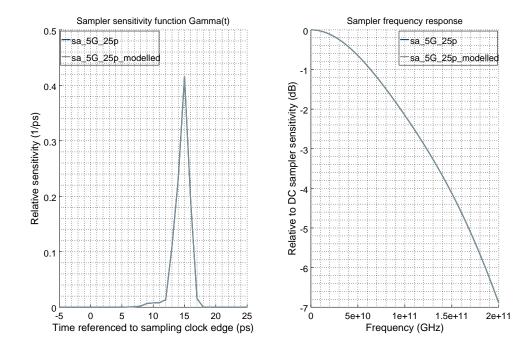

|   | 4.5  | Sampl                                  | er modelling process                                          | 117 |  |

|   |      | 4.5.1                                  | Model theory                                                  | 120 |  |

|   |      | 4.5.2                                  | Models / OCM Data Sources                                     | 132 |  |

|   |      | 4.5.3                                  | SystemVerilog considerations                                  | 134 |  |

|   |      | 4.5.4                                  | Optimized C modelling routine                                 | 135 |  |

|   |      | 4.5.5                                  | Testbench and performance analysis                            | 135 |  |

| 5 | Link | budget                                 | ting                                                          | 137 |  |

|   | 5.1  | Histor                                 | y and state of the art                                        | 138 |  |

|   | 5.2  | The Peak distortion analysis algorithm |                                                               |     |  |

|   | 5.3  | The OCM link budgeting algorithm       |                                                               |     |  |

|   |      | 5.3.1                                  | Power distribution                                            | 156 |  |

|   |      | 5.3.2                                  | PLL phase noise spectral density for transmitter and receiver | 156 |  |

|   |      | 5.3.3                                  | Peak distortion analysis                                      | 157 |  |

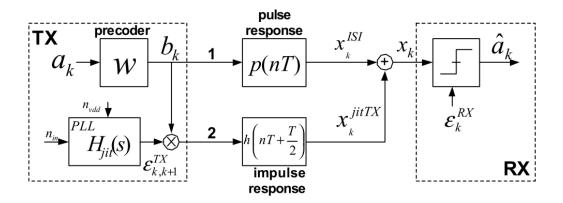

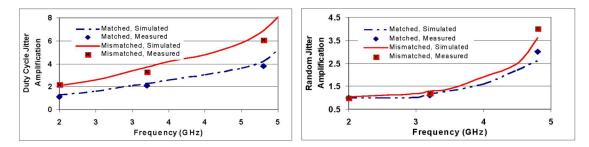

|   |      | 5.3.4                                  | System channel and jitter amplification in CDR based systems  | 158 |  |

|   |      | 5.3.5                                  | System voltage noise estimation                               | 165 |  |

|   |      | 5.3.6                                  | Clock data recovery and sampler phase noise estimation        | 167 |  |

|   |      | 5.3.7                                  | Final statistical eye compilation and metric extraction       | 176 |  |

| 6 | Des  | ign eval                               | luation                                                       | 179 |  |

|   | 6.1  | A qua                                  | rter rate serializer design                                   | 179 |  |

|   | 6.2  |                                        | sis of 10 Gigabit operation                                   | 182 |  |

|   | 6.3  | •                                      | sis of 20 Gbps operation                                      | 188 |  |

|   | 6.4  | _                                      | nce of the sampler ISF                                        | 191 |  |

|   | 6.5  |                                        | g channel geometry with the Johnson Signal Model              | 193 |  |

| 7 | Con  | clusion                                | and Outlook                                                   | 197 |  |

| ix |

|----|

|    |

| List of Figures | 201 |

|-----------------|-----|

| List of Tables  | 209 |

| AppendixA       | 214 |

| AppendixB       | 217 |

# Acronyms

**ACF** autocorrelation function

**API** application programming interface

**AWG** American Wire Gauge

**BER** bit error rate

**CAD** computer aided design

**CDF** cumulative density function

**CDR** clock data recovery

**CEI** common electrical I/O

**CML** current mode logic

**CMOS** complementary metal oxide semiconductor

**CPU** central processing unit

**CTLE** continuous time linear equalizer

**DAC** digital to analog converter

**DCD** duty cycle distortion

**DFE** decision feedback equalizer

**DFT** discrete fourier transform

**DPI** direct programming interface

**ECAD** electronic computer aided design

**ESD** electrostatic discharge protection

**ESL** equivalent series inductance

**ESR** equivalent series resistance

**xii** Contents

**EVN** equivalent voltage noise

**FIR** finite impulse response

**HPC** high performance computing

**IC** integrated circuit

**ISF** impulse sensitivity function

**ISI** intersymbol interference

**LTI** linear time invariant

**NIC** network interface controller

**NRZ** non return to zero

**OCM** openMGT modeling framework

**OCD** openMGT OCM data analysis and post processing backend

**OIF** Optical Internetworking Forum

**PAM** pulse amplitude modulation

**PCB** printed circuit board

**PDA** peak distortion analysis

**PDF** probability density function

**PDK** physical design kit

**PDN** power distribution network

PLL phase locked loop

**PRBS** pseudo random bit sequence

**PSD** power spectral density

**PSRR** power supply rejection ratio

**RF** radio frequency

**RMS** root-mean-square

**RNM** real number model

**SBR** single bit response

Contents

**SNR** signal to noise ratio

**SOC** system on chip

VCO voltage controlled oscillator

**VGA** variable gain amplifier

**VRM** voltage regulator module

## 1 Introduction

Over the past decade there has been a strong trend towards serializer based multigigabit communication interfaces. While network interfaces between compute nodes have been using multigigabit transmission for a long period of time already (10G Ethernet, Infiniband) and system interconnects between central processing unit (CPU) and peripheral (I/O) devices have entered the gigahertz region for quite a while, too (Hypertransport, QPI, PCI-E, S-ATA), the CPU to memory interconnects are the next domain to follow suit (HBM, HMC). This is also true for memory interfaces in the mobile processor segment[26] as well as for peripheral standards such as USB 3.0 or HDMI.

A serializer, also called *transceiver* or *SERDES*, is an electronic subsystem within an integrated circuit (IC). It consists of a transmitting and a receiving part. The transmitter acts as a multiplexer (serializer) with an output driver for the transmission channel while the receiver implements a demultiplexer (deserializer) with analog input to digital output conversion. Data is therefore modulated onto the channel or decoded from it at a higher frequency than it is accepted from or presented to the parallel side interfacing with the chip fabric.

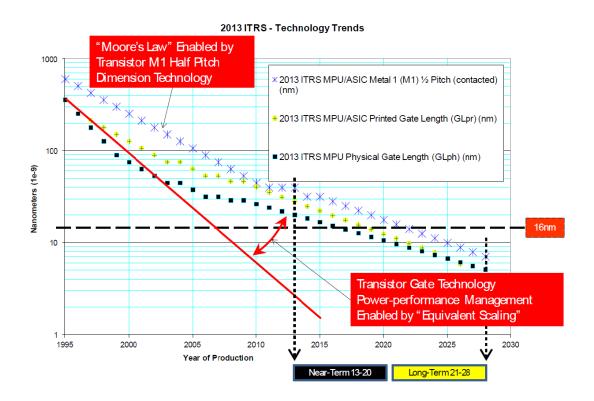

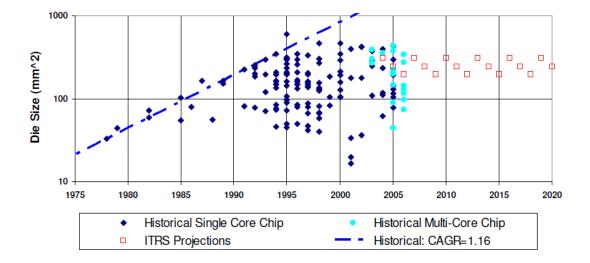

There are two main constraints which drive the development towards ever higher data rates on the physical transmission channel between transmitter and receiver: The increase in data processing throughput of the integrated systems and the pin count limitation of chip die and package. While the first constraint is a consequence of rising internal clock rates and technology shrinks (see figure 1.1), the latter results from mechanical and thermal constraints (see figure 1.2). The continuous increase in integrated circuit performance and therefore data throughput can only be realized by providing the corresponding I/O data rate demands with modern serializer technology. An integrated system must maintain an application defined ratio between internal processing throughput and its total I/O bandwidth such that communication will produce as little of a bottleneck as possible to overall system performance. Technology shrinks not only allow to safe power and achieve more performance with the same battery lifetime but also foster a trend towards an ever growing level of integration (leading to so called systems on chip) whose internal processing throughput may quickly saturate the available I/O capacity. It is for this reason that multigigabit serializer technology will grow even more important in the future. This is true for all electronic systems ranging from tiny devices for the *internet of things* to mobile hand held devices all the way up to high end processors, network interface cards and the

2 1 Introduction

various communication channels in high performance computing (HPC) systems.

Figure 1.1: The ITRS technology projection of 2013 for feature size scaling [21]

**Figure 1.2:** ITRS projection of total die size from 2008 [29] already revealing the fundamental thermal and mechanical constraints

As previously noted, the frequency at which data is modulated onto the transmission channel or extracted from it is related to the chip internal clock frequency via the (de)muxing ratio. This is unless more sophisticated data modulation schemes than standard non-return to zero single data rate signalling are used. Serializer circuits are usually employed to transfer information across distances far greater than that of the integrated circuit itself. Especially in high performance computing applications, there is a great variety of transmission channels. The most challenging specimen realize intercabinet or internode connections by using long copper cabling or backplane traces. Due to their high dielectric and conductor losses and the unavoidable signal degradation at every connector, all of which become worse as frequency increases, the transmitters and receivers have to compensate these effects as much as possible. Output driver and analog receiver frontend will therefore substantially grow in complexity and inevitably consume more power.

Equally challenging are chip to chip interconnects within a single node (compute system), These interconnects can either be between different CPUs, between CPUs and peripheral devices or simply from CPU to main memory. The quality of copper cables is high compared to printed circuit board (PCB) traces and its dielectric and conductor losses comparably low. Therefore, even though these node internal connections do not span as much of a distance, their malicious impact on signal quality is very significant even at shorter distances.

Another trend of past years has been to progress system integration whereever possible. This ranges from multi-die packages which may for instance combine processor and memory modules [20, 43] to chip on chip packaging with through silicon vias [65]. Despite these small distances, with the steady increase in signal frequencies to the high Gigahertz range the resulting electromagnetic wavelenghts are still comparable or below the transmission line extents. The transmission channel will therefore have to be treated and analyzed with microwave engineering approaches. Depending on operating frequency, this may be true for on-package interconnects - it certainly cannot be avoided for longer communication channels of complex topology.

Regardless of application scope, a serializer system requires a broad span of analysis and implementation tools from various disciplines. Microwave engineering techniques are required for channel and power distribution analysis alike. The output driver of the transmitter and the signal preconditioning stages of the receiver are very broadband all-analog integrated building blocks. Also, the clocking sources and clock distribution scheme are to the largest degree an analog design effort. The multiplexing and demultiplexing stages on the other hand could be approached with either analog or semicustom, digital design methods. As technologies continue to shrink, however, favouring the mostly automated semicustom digital implementation flow over manual analog design becomes increasingly appealing. Due to the smaller feature sizes of advanced submicron technology nodes, the variation in transistor properties increases and makes it difficult to meet design

4 1 Introduction

specifications for analog subcomponents without additional calibration mechanisms. These mechanisms in turn rely on tunable digital to analog converters and thus digital tuning logic as do the equalization adjustment mechanisms of the all-analog stages. As a consequence, modern serializers have to be conceived as so-called *mixed signal mode* designs.

#### 1.1 Challenges in contemporary design and analysis methodologies

One of the key challenges to the application of a serializer based communication scheme lies in the interaction of higher level protocols with the underlying, physical serializer implementation and its associated performance limits. Serializers are located at the lowest level of the communication stack, the physical layer (see figure 2.3 in section 2.2.2). Their interaction with the so-called link layer and medium access layer is very involved. Communication protocols, however, must be viewed on a larger time scale than the underlying serializer technology. While the temporal extent of a symbol on the transmission line will be in the range of a few tens of picoseconds with multigigabit signalling, the communication protocol interactions are to be analyzed in the regime of tens to hundreds of microseconds. These may include the initialization of the communication link (i.e. powering up the serializer system, synchronization of multiple serializers forming the link), the exchange of equalization presets or even link layer protocol mediated equalization adaption procedures as well as the indication of start and end of power saving or sleep modes of the link.

The design and analysis of these interactions require the availability of fast yet accurate simulation models which include information about the power state, the transistion times, frequency responses or other analog properties of individual subcomponents of the link. The challenge grows even further once tight performance or power constraints need to be met. These constraints always implicate a power and performance tradeoff at a particular point in the system. The goal is to find the right aspects where power is saved or performance increased most easily or efficiently - a process which is called *budgeting* and which only becomes possible with reasonable simulation run times and therefore very good and careful model abstraction versus performance tradeoffs.

While the modelling effort can be considered complete for those building blocks of the system which are of semicustom (all digital) nature and the respective work flows are well established in the industry, full analog elements or elements where digital and analog signals interface still have no entirely canonical work flow. For the most part, this is due to the versatility of analog components. Another reason lies in the different traditions among digital and analog electrical engineering communities. Digital designs are, to the most part, top down and text driven, while analog engineers prefer a bottom up, schematic based approach. For the specification and performance analysis of modern high speed serializers, a special level of abstraction is therefore required. On the one hand, it must

allow the definition of small, electrical subcomponents along with their required metrics, on the other hand, these subcomponents have to be embeddable into a complex system of subcomponents to form the final serializer and even further: the final link system. Within such a system, design tradeoffs, subcomponent analysis and design space exploration can be done early in the design process without the availability of more detailed models such as actual schematic implementations. This new abstraction layer should deliver hints at overconstrained (and therefore power inefficient) subsystems and should help relax specification items wherever they have a severe impact on overall efficiency or feasability. Protocol engineers are then enabled to test ideas and their impact on power savings at a very early stage and can themselves deliver valuable input to software engineers and system architects who may analyze for further repercussions on overall communication performance or efficiency. In addition to this, the tight integration requirements of modern system on chip (SOC) implementations produced and necessitate a trend towards more sophisticated hardware verification paradigms. Functional verification of digital hardware has a long lasting tradition already. The mixed mode and especially the analog sphere are catching up with this process. A serializer subsystem which may be central to almost any new high speed communication scheme can make no exception to this trend.

With the availability of suitable models for different scopes of interest, the problem of consistency between the models, the final implementation and their testbenches arises. A robust design and verification flow must ensure consistency between the various views of a component and its testbench in order to garantuee subsystem models will actually reflect the intended properties of a final implementation.

In addition to the spread in characteristic event times between the serializer subsystems and the higher level link entities, the analog properties of the serializer present further complications to system analysis. As data rates grow (and IC technologies continue to shrink), the voltage swing seen at the receiver input becomes comparable to the cumulative voltage noise magnitudes in the system itself. Also, the duration of a single bit on the transmission line becomes smaller compared to the inevitable timing uncertainties (jitter) of the clocks driving the design. Analysis of these effects require small time steps in transient simulation runs and broadband noise sources which again increases the amount of necessary computation points in classical analog simulators. Transient analysis under consideration of all noise effects will therefore quickly lead to unacceptable simulation run times and is thus unsuitable for design space exploration.

The statistical nature of noise in conjunction with the naturally uncorrelated deterministic effects make this problem even more drastic once serializer design constraints are defined such that there may only be a very small number of erroneous bits per unit time - which is typically one of the prime design targets. The probability of actually capturing a specific, malicious event is small by definition - as a consequence, the simulation time would need to be increased drastically in order to observe it. This also makes transient simulations

6 1 Introduction

an ill equipped tool to analyze statistical processes in the context of transient simulations for multigigabit designs. A technique is required which ammends the standard set of operating point, transfer function, transient analysis and small signal noise analysis with a post processing environment bringing together these very different views. Additionally, some serializer subsystems require more abstract modelling views outside the classical time or frequency domain. These abstract models may also rely on information of other simulations or subsystem parameters such as the total voltage noise or timing noise and must therefore be part of the abovementioned *budgeting* and design analysis procedure.

As previously mentioned, one of the major constraints to serializer requirements is the range of physical channels that are to be supported by the given design. Transmission channels are usually described with a set of frequency dependent reflection and transmission coefficients - so called S-Parameters. They either result from direct laboratory measurement or can be constructed by elaborated, numerical models for a large spectrum of topologies by using modern microwave electronic computer aided design (ECAD) tools. At the same time, these microwave tools are not designed to implement large and complex mixed signal designs. There are, of course, data import and export functionalities provided by the various vendors which allows to use the most appropriate tool for each task at hand. Interoperation and data consistency between the tools then again becomes an emerging issue and mechanisms to seamlessly provide parameterizable (channel) models are, to the best of the authors knowledge, not included. From a design space exploration point of view, this forces the user to generate model files for every change in physical channel parameters - a task that can hardly be automated. Furthermore, for transient simulations, the frequency domain model needs to be converted to a suitable representation. Especially for analog, multigigabit simulations, the usual approach is to perform a Fourier transformation of the model data and deploy a continuous time convolution approach. Quite generally, this makes the channel model one of the computationally most intense components in the design with a severe impact on simulation time.

A way needs to be found which allows to leverage the ideas of analog verification and modelling of the past years [8] to speed up simulation processes and seamlessly ammend them with a powerful numerical post processing backend for advanced statistical analysis. This post processing scheme must take into account the various modelling views and subcomponent interactions. There have been many publications on these so-called *hybrid* statistical analyses of serializer systems [60, 61, 16, 45, 33, 63, 44] some of which lend themselves better to SystemVerilog and numerical backend integration than others. Additionally, they all focus on different subcomponent subsets which is why a concise overview is needed to devise an appropriate design space exploration and budgeting procedure for this demanding mixed signal mode design.

The work presented here aims at solving the challenges described thus far by using modern analog verification procedures as leveraged by the SystemVerilog [18] and Ver-

1.2 Structure of this work 7

ilog/A/MS [2] language standards. Their flexibility in describing and testing mixed mode integrated circuits by using *real number* and mixed signal modelling is extended by the integration of the open source numeric software package *Octave* [12] to develop a versatile system for performance analysis, modelling, design space exploration and budgeting of mutligigabit serializer designs.

#### 1.2 Structure of this work

This text will begin with an overview of the various subcomponents and their metrics comprising a multigigabit serializer in chapter 2. Each subcomponent and its function will be shortly introduced and contextualised with related publications. Also, the nomenclature used throughout this text, technical as well as mathematical, will be defined for later chapters and shall serve as a reference to the reader.

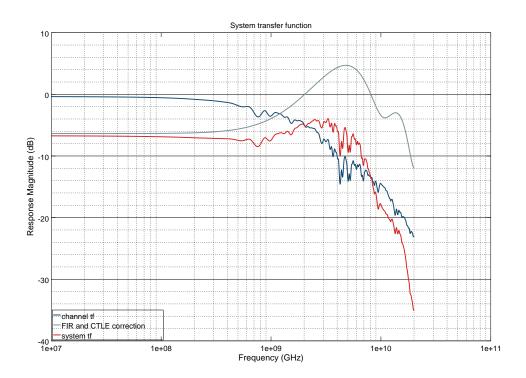

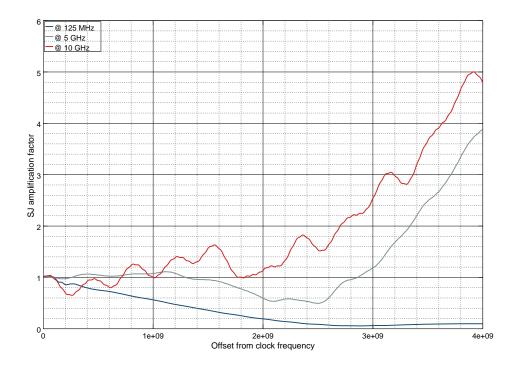

With the most central aspect of a serializer system being the channel, it deserves to be treated separetely in chapter 3. Its properties and the various views on signal degradation are discussed thereby highlighting the difficulties in modelling them numerically. This challenge is also expressed in the context of the so-called *bit rate capacity*, a performance metric which is still being used in HPC exascale projections. The shortcomings of this metric will be highlighted and an alternative, numerical modelling approach be presented. The resulting channel model will then be used for first, serializer implementation agnostic performance and scaling trends with respect to channel parameters. This ammends the analysis of previous work and gives valuable insight for future HPC technology projections. Also, the mechanisms of equalization in serializer systems will be introduced together with a convergence algorithm for automatic equalization adaption. In anticipation of the serializer design and analysis framework presented here, the chapter will already show some of the results to give insight into the mechanisms of equalization and estimate the time spans required by the convergence procedures.

The serializer system is built on the foundation of a framework which was jointly developed with this work and also partly published in [38]. A brief description of the framework named openMGT can be found in chapter 4. Following its introduction, it will be further extended in section 4.3 to allow for the accommodation of more compute intense system subcomponents such as the transmission channel and the receiver samplers in the context of real number based simulations. Also, a simulation performance comparison will be presented to demonstrate the benefit of the implementation presented here. In light of the growing importance of verification processes during system design, the models and testbenches developed for channel and samplers will be shown to be self-consistent.

Chapter 5 will introduce the central concepts of hybrid statistical link analysis as required to accurately verify a complete serializer system. Due to the time domain centered approaches usually taken by publications in this context, especially with regard to jitter

1 Introduction

analysis, some of the concepts are not suitable for integration with the framework presented here. Therefore, an alternative approach is developed in section 5.3 which is based on a well established, statistical algorithm for the assessment of worst case channel properties. This algorithm is presented in section 5.2 preceding the actual openMGT/OCM budgeting procedure.

Finally, chapter 6 presents the application of the framework and budgeting procedure to an adjustable 2.5-20 Gbps serializer link architecture which was codeveloped in a team effort during the conception of this thesis.

# 2 Electrical serializer based multi-gigabit communication links

In the ecosystem of high performance computers, many different serializer based communication standards have been established over time. They quite often share a substantial common basis or have relaxed requirements when it comes to certain specification items. Yet, due to their very specific application ranges, some of the differences which may seem subtle at first, prohibit a particular serializer implementation to be used in another environment. This text deals with serializers that are to be used in the domain of chipto-chip and node-to-node communication across backplanes, connectors and high quality cables. Some of the results may be useful for or extendable to other contexts such as on-chip communication or electro-optical systems as well. The framework developed throughout the next chapters will be designed with extensibility in mind. However, the system overview and nomenclature as well as the background on electrical transmission lines and equalization presented here puts its emphasis on the first mentioned use case.

#### 2.1 Mathematical definitions and relations

This section presents a clarification of the mathematical conventions and the nomenclature used throughout this text. Especially the radio frequency (RF) and microwave community tend to use very different notations which is why an attempt is being made to unify the approaches as much as possible. Whenever formulas from papers are used and cited, their notation will be given in the form presented here.

- The complex conjugate to a variable  $a \in \mathbb{C}$  is  $a^*$

- Vectors v are written boldface and are lowercase

- Matrices  $\overline{M}$  are written boldface with a bar over them and are uppercase

- Metrics and parameters of the OCM link budgeting procedure  $b_{\text{item}}^{\ddagger}$  are written boldface italic throughout this text irrespective of their actual dimensionality or nature. This serves as a reference for Appendix A where the parameters used for the

link budgeting procedure developed throughout this text and specifically in chapter 5 are again listed as an overview.

- A function f which is continuous with respect to its argument x is written as f(x)

- A function f which is discrete with respect to its argument x is compactly written as vector f while specific values of the function are denoted by  $f_x$

- A Fourier transform pair is short handedly written as  $f(x) \hookrightarrow F(p)$ .

- The Fourier transformation of a function · is denoted by F{·} and the inverse Fourier transformation by F<sup>-1</sup>{·}

- The convolution h(x) of two functions f(x) and g(x) is described and defined as

$$h(x) = f(x) * g(x) \equiv \int_{-\infty}^{\infty} f(x)^* g(x - x') dx'$$

(2.1)

If f is a continuously valued function of a continuous variable x the transformation set is given by

$$\mathscr{F}\left\{f(x)\right\} = \frac{1}{\sqrt{2\pi}} \int_{-\infty}^{\infty} f(x)e^{-jpx} dx = F(p)$$

$$\mathscr{F}^{-1}\left\{F(p)\right\} = \frac{1}{\sqrt{2\pi}} \int_{-\infty}^{\infty} F(p)e^{jpx}dp = f(x)$$

where the continuous function F will then of course depend on a continuous argument p. In the context of real number modeling and numerical statistical analysis, however, all function arguments will necessarily be of discrete nature. In this case the function f and F are represented by vectors  $\mathbf{f} = (f_0, ... f_{N-1}) \in \mathbb{C}^N$  and  $\mathbf{F} = (F_0, ... F_{N-1}) \in \mathbb{C}^N$  where  $f_n = f(x_n)$  and  $F_n = F(j\omega_n)$ .

The discrete fourier transform (DFT) and its inverse can be calculated according to

$$F_n = \sum_{k=0}^{N-1} f_k \cdot e^{-\frac{2\pi j \cdot kn}{N}}$$

$$f_n = \sum_{k=0}^{N-1} F_k \cdot e^{\frac{2\pi j \cdot kn}{N}}$$

respectively. Wherever it is beneficial to a more comprehensible discussion, the text will

use the continuous description and deviate from this path only to highlight important aspects of a particular implementation. The two vectors f and F are associated with their argument vectors x and  $\omega$ . The following relations hold for every function argument vector pair  $(x/\omega)$ :

$$x_0 = dx = (x_{n+1} - x_n) = \frac{2\pi}{\omega_{N-1}}$$

and  $x_{N-1} = \frac{2\pi}{\omega_0}$  (2.2)

and conversely

$$\omega_0 = d\omega = (\omega_{n+1} - \omega_n) = \frac{2\pi}{x_{N-1}}$$

and  $\omega_{N-1} = \frac{2\pi}{x_0}$  (2.3)

Furthermore, the following functions are defined:

• The power spectral density (PSD) of a function f(x) is denoted by  $S_{ff}(j\omega)$  and equates to

$$S_{ff}(j\omega) = \mathscr{F}\{|f(x)|^2\}$$

• The autocorrelation function (ACF) of a function f(x) is denoted by  $r_{ff}(x)$  and is defined as

$$r_{ff}(x) = \lim_{X \to \infty} \frac{1}{2X} \int_{-X}^{X} f(x)^* f(x - x') dx'$$

(2.4)

$$r_n = \lim_{N \to \infty} \sum_{k=1}^{N-1} f_k^* f_{k+n}$$

(2.5)

in the continuous and discrete case. The ACF is a measure for the resemblance of a function with itself.

• In this text the Gaussian probability density function (PDF) is used in the following form:

$$p(x) = \frac{1}{\sigma \sqrt{2\pi}} e^{-\frac{1}{2} \left(\frac{x-\mu}{\sigma}\right)^2}$$

(2.6)

with the standard deviation  $\sigma$  and the mean value  $\mu$ .

Whenever there is a parameter  $\sigma_x$  it signifies that the underlying values of the statistical function x exhibit a Gaussian distribution whose standard deviation (or equivalently the root-mean-square (RMS) value of x) is given by its value. The error function and

complementary error function are defined as

$$\operatorname{erf}(x) = \frac{2}{\sqrt{\pi}} \int_{-\infty}^{x} e^{-t^2} dt$$

$$\operatorname{erfc}(x) = 1 - \operatorname{erf}(x)$$

which are the integrals of a Gaussian distribution with unity standard deviation up to and starting from a given point *x* respectively and thus represent cumulative probabilities such as required when defining the bit error rate (see below).

Oftentimes, conversions of power spectral densities from frequency to phase space will be required. A conversion between phase and frequency domain can be made with respect to a center frequency  $f_0$  due to

$$\Delta \varepsilon(t) = \varepsilon(t) - f_0 = \frac{1}{2\pi} \frac{d\phi(t)}{dt}$$

and therefore

$$S_{\varepsilon\varepsilon}(f) = \frac{1}{f_0^2} S_{\Delta\varepsilon\Delta\varepsilon} = \frac{f^2}{f_0^2} S_{\phi\phi}(f)$$

Phase noise is usually given as a single sided spectral function (meaning from 0 to  $\infty$ ). For oscillators the definition of the phase noise power spectral density as  $\mathcal{L}(f) = \frac{S_{\phi\phi}(f)}{2}$  is also common. In figures, its magnitude is always given relative to the power at the central carrier ( $\frac{\text{dbC}}{\text{Hz}}$ ). IEEE calls  $S_{\phi\phi}(f)$  the phase instability and  $\mathcal{L}(f)$  the phase noise. We will make no semantic distinction here.

## 2.2 Link system overview and nomenclature

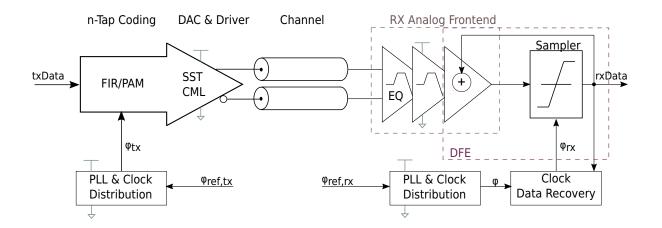

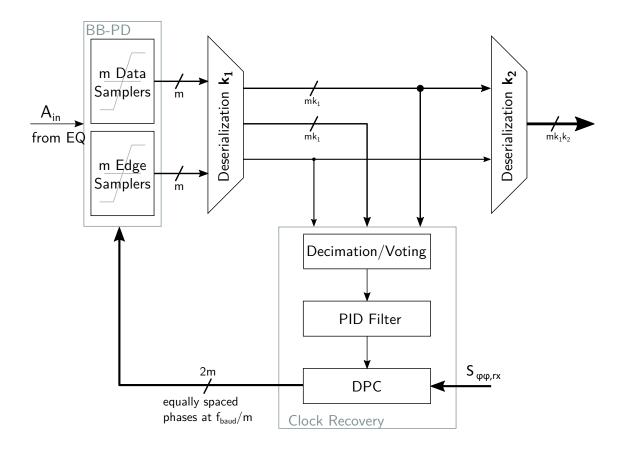

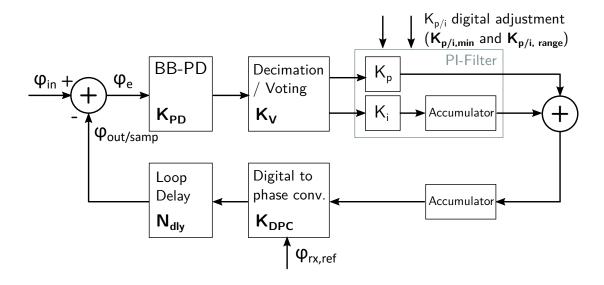

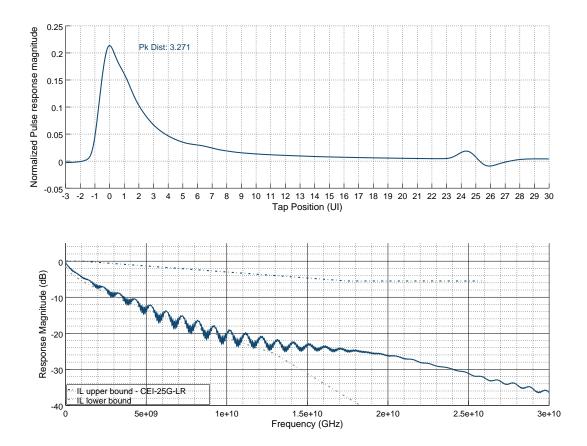

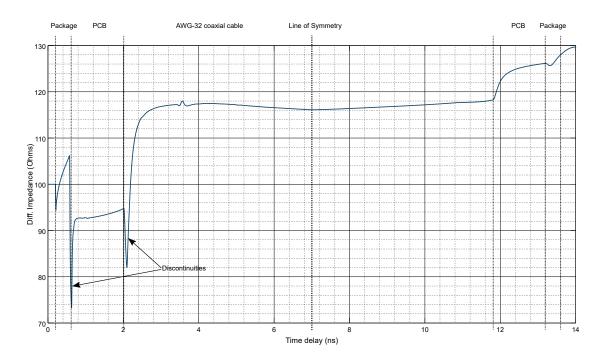

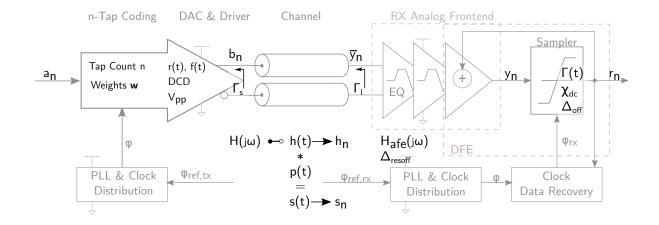

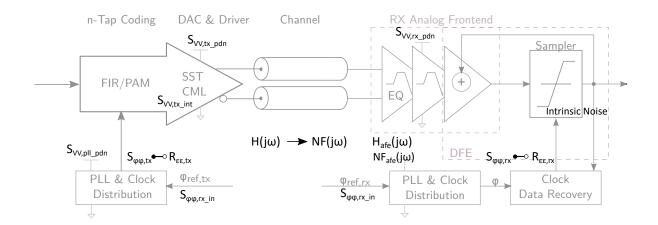

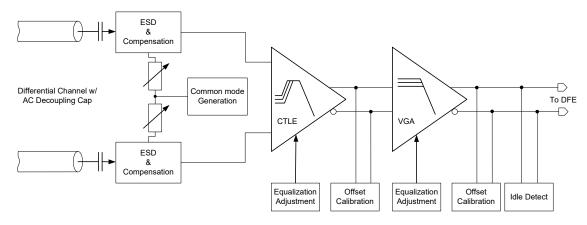

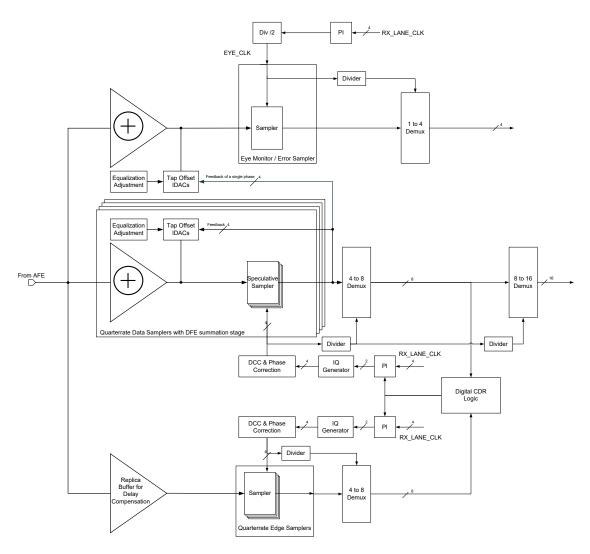

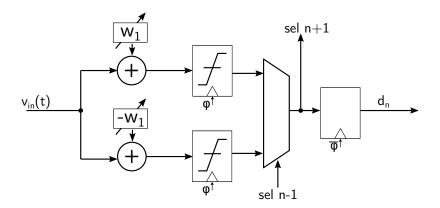

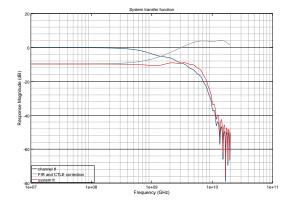

Figure 2.1 presents a condensed block diagram of the communication system as it is being investigated throughout this text. This section will give an overview of the subcomponents, their function and their most central performance metrics. In the context of link budgeting, this will provide the orientation needed when combining the various subcomponent interactions to derive a final metric for overall system performance. This final metric is called the bit error rate (BER) of the communication system. It comprises all deterministic and random influences on information propagation from transmitting to receiving side. As such, it is a statistical quantity and defines the probability of detecting an erroneous bit at the receiver output. It also marks the starting point of the subcomponent and metric discussion in this section.

**Figure 2.1:** The system components of a multi-gigabit serial link as they will be used, described and modeled throughout this text

#### 2.2.1 The bit error rate

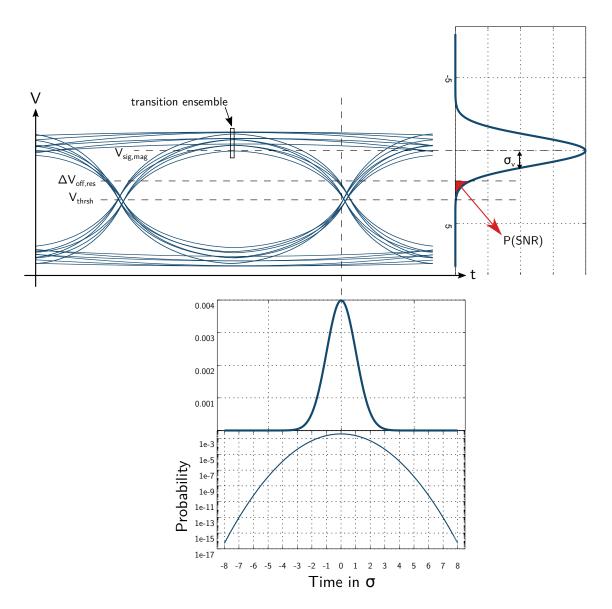

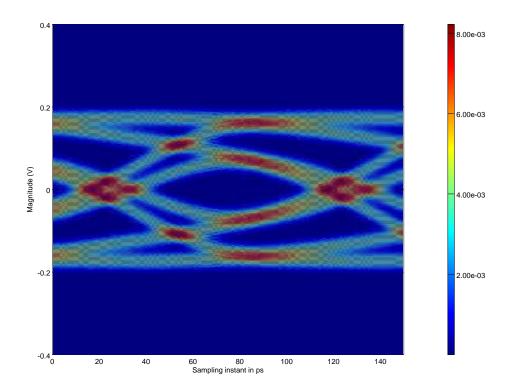

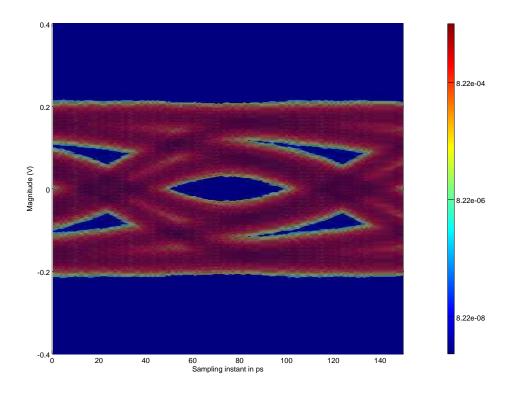

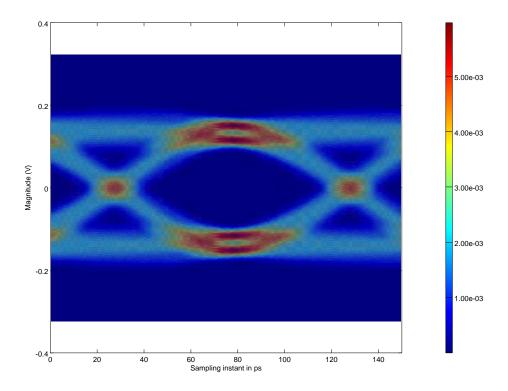

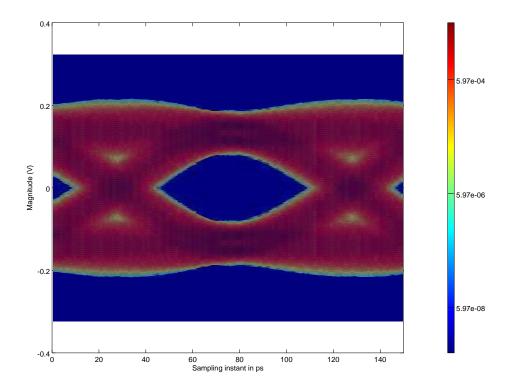

Figure 2.2 shows an idealistic and *deterministic* eye diagram as it may result from overlaying a few of the worst case patterns (sequences of logic ones and zeros) seen at the analog input of the receiver samplers after passing through the system. We will call the path from transmitter (TX) output to receiver (RX) sampler input the *system channel*. It comprises the actual physical transmission medium and all signal equalization stages. The eye diagram is assumed to have been obtained either by a noiseless transient simulation or by statistical methods (see section 5.2). In this particular example, the line coding (see subsection 2.2.2) is chosen to be non return to zero (NRZ) for simplicity. However, the arguments below remain valid even for more complex coding schemes:

All deterministic effects are bounded which makes it possible to generally calculate the probability of seeing a particular voltage level at a specific point in time. Quite actually, the single colored eye diagram of figure 2.2 is a three dimensional map with the third dimension specifying the probability of seeing the given voltage at the specific time instant. Oscilloscopes, papers and statistical channel analysis in this text therefore use a color scheme to highlight this aspect of the eye diagram which is left out in the figure above only for simplicity. Without random noise sources, the deterministic worst case eye of the channel equalized by the transmitter and receiver filters and impeded by residual offsets and duty cycle distortion would be the final metric. The goal would then be to design a system which exhibits an eye diagram of smallest height and width for the required transmission channels (assuming a perfect receiver sampler, see section 4.5). In such a case, the efforts of equalization and therefore power consumption would be kept at a minimum while it was garantueed to never receive a single bit in error.

The unavoidable presence of random noise sources in the system, however, makes

**Figure 2.2:** An idealistic, reduced representation of a *deterministic* eye diagram as captured at a sampler input along with the Gaussian distributions of voltage and timing noise in linear and logarithmic scale normalized to their standard deviation.

analysis much more complicated. Random noise sources are unbound and in the context of this text are all based on underlying physical processes that are wide-sense stationary and ergodic. The first restriction ensures consistent process behavior independent of the initial value and point in time of the noise source state. The latter garantuees that the process will eventually assume all possible internal states which ensures that by observing the process over time, its *PDF* can be derived. The combination of all unbound statistical processes within the system, such as thermal noise, shot noise or flicker noise (which do themselves not adhere to a Gaussian distribution except for thermal noise) will eventually result in a Gaussian distribution of timing and voltage noise due to the central limit theorem of statistics. System internal and external noise sources affect the sampler input signal voltage seen at a particular point in time. Depending on the view, this can either be considered a voltage noise or a timing noise (jitter). The slew rate of the signal translates one into the other and it depends on the subsystem being analyzed which of the views is more convenient. The presence and interaction of both types of perturbation to the eye diagram is indicated by the two Gaussian probability density functions in figure 2.2. In addition to the linear scale of the PDF which is normalized to the standard deviation  $\sigma$  of the process, its logarithmic representation is also shown. It highlights the unbound nature of the process and shows that extreme noise contributions both in voltage and time dimension are possible albeit at very low probabilities. For better visibility, a large  $\sigma$  compared to deterministic eye width and height was chosen here.

For a noiseless system, the performance metric is straight forward to define, the eye width at the decision threshold (usually chosen to be at 0) and its height for a specific instant in time can be derived with ease. The system would be said to achieve the given eye opening at a randomly low error level. With unbound noise sources on the other hand, the eye diagram is closed by definition. It is therefore necessary to define beforehand which probability of receiving a bit in error is acceptable - the so called BER. An on-die transmission system between higher level cache and processor instruction prefetch stage for instance has only little signal distortion and comparably high transmission levels. It is therefore rather easy to achieve BER levels much lower than  $10^{-30}$  which makes it unlikely to even receive a bit in error during the lifetime of the processor itself.

As transmission line properties decrease signal voltage levels to magnitudes comparable to those of the noise sources in the system (thus decreasing the so-called signal to noise ratio (SNR)), more realistic target BERs need to be chosen. In fact, knowing the achievable SNR at the receiver sampler (which is also directly related to the power consumption of the transmission system), directly determines the achievable BER level. It is the particular serializer application along with the constraints at higher OSI layers (see section 2.2.2) that call for a specific lower BER bound. For instance a serial link with a transmission rate of 10 Gb/s shall on average only produce a single maldetected bit per minute such that the network protocol retransmission procedure does not have a severe impact on total link

performance. This is equivalent to a bit error rate of approximately  $1.7 \cdot 10^{-12}$ .

From figure 2.2 it can be seen that it is the integral of the portion of the Gaussian process reaching below the decision threshold which gives the cumulative probability of actually receiving a bit in error. The connection between SNR and BER can therefore be derived to

$$BER = P(SNR) = \frac{1}{\sigma_{\rm V} \sqrt{2\pi}} \int_{-\infty}^{SNR \cdot \sigma_{\rm V}} e^{-\frac{1}{2} \left(\frac{x - V_{\rm sig,mag}}{\sigma_{\rm V}}\right)^2} dx = 0.5 \, \text{erfc} \left(\frac{SNR}{\sqrt{2}}\right)$$

(2.7)

The signal to noise ratio in figure 2.2 can pessimistically be given by

$$SNR = \frac{V_{\text{sig,mag}} - V_{\text{thrsh}} + \Delta V_{\text{off}}}{\sigma_{\text{V}}}$$

In the example of the  $10 \,\mathrm{Gb/s}$  link above, an SNR of about 7 would need to be achieved at the sampler. This is pessimistic in the sense that here we assumed convolution of the Gaussian distribution with the worst case transition alone. However, this convolution would need to be performed with the ensemble of all transitions passing through the sampling time instant  $t_s$  in the figure (highlighted by the black box) which would of course reduce the relative impact of the worst case transition in accordance to its probability of actually occuring in a given bit pattern (see chapter 5 for more information on this process). Note also, that the probabilites of the Gaussian plots in figure 2.2 are neither scaled with the probability of the worst case transition nor can the probability of receiving a bit in error directly be read from the graphs. This would additionally involve the abovementioned integration over the ensemble of all noise source magnitudes which could potentially push the voltage level below the decision threshold.

While it is straight forward to analyze the eye diagram in terms of voltage noise (and therefore uncertainty in voltage amplitude, hence voltage error), uncertainty with respect to instants in time (timing errors) need to be defined and treated more carefully:

There are mainly three different descriptions of timing error which are all interrelated. They are the so-called *phase jitter*, the *period jitter* and the *cycle to cycle jitter*. The latter two are important when analyzing autonomously oscillating systems or parallel bus systems where a known timing between serveral lanes is important due to common retiming on the receiving side. With serial links as discussed here, each lane is considered a separate system. Retiming can and will be delegated to other layers of the communication stack such as the medium access layer (see section 2.2.2). The serial link transmits symbols in well defined time intervals called bit period T or sometimes unit interval UI. The existence of T is an idealized assumption and helps to quantify the time interval error (TIE) which is due to residual equalization errors, residual offset errors or phase noise of the clock sources driving the gating structures responsible for creating the potential differences on the transmission line that ultimately represent the information (bits). It is in this sense that

we can define the phase jitter  $\phi_n = t_n - nT$  where  $n \in \mathbb{N}$ . While nT would be the moment in time where the ideal signal crossing would occur if the information modulated onto the transmission line were actually changing,  $t_n$  is the actual point in time observed for the transition through the reference level. From a known phase noise PSD  $S_{\phi\phi}(\omega)$  or its dual autocorrelation function, the RMS time interval error (jitter) can be derived to

$$\sigma_{\phi}^{2} = \frac{4}{\omega_{0}^{2}} \int_{0}^{\infty} S_{\phi\phi}(\omega) d\omega = \frac{2}{\omega_{0}^{2}} R_{\phi\phi}(0)$$

(2.8)

where  $\omega_0 = \frac{2\pi}{T}$ .

The SNR is a voltage domain quantity. For jitter, however, the same derivation can be made with respect to the time domain. This is indicated by the Gaussian distribution below the eye diagram. The decision threshold in this case is the (ideal) sampling instant usually located at the center of the eye. The Gaussian tails to be integrated give the probability of sampling a bit pre- or succeeding the actual bit to be sampled. It is for this reason, that there must always be a triplet of information given to describe the performance of the overall system: the resulting eye width  $e_{\rm w}^{\ddagger}$ , the eye height  $e_{\rm h}^{\ddagger}$  and the  $BER^{\ddagger}$  level at which the prior two values were obtained. As the processor example above indicates, a BER for a serial transmission system should always be given with respect to channel attenuation at the Nyquist frequency (and hence serializer data rate) and the system testing pattern used (a PRBS sequence for instance) in cases where a non-statistical analysis is made. Oftentimes, even more information like channel reflections are given too, to highlight the importance and effectiveness of more involved equalization schemes such as the DFE (see section 3.3).

#### 2.2.2 Interaction with higher communication layers

Figure 2.3 depicts the lowest three layers of the *open systems interconnection (OSI) model* which are called *physical layer*, *data link layer* and the *network layer* respectively and define the constraints for the serializer system. The bulk of digital hardware components which need to implement certain aspects of these layers are omitted in figure 2.1. These include the muxing and demuxing structure to adapt to on-chip data width and rate, the buffering structures, power down, idle modes as well as offset and equalization calibration logic. They are all not shown as they are handled by the well established digital description and implementation work flow which is ammended by the real number modelling framework (see section 4.2 of chapter 4 for details). Also, these aspects, albeit integral part of the serializer itself, can conceptually be attributed to the higher layers as well. The specification items listed in the diagram focus on those aspects of the higher two layers which conversely exhibit an interaction with the serializer performance at the lowest level. The

| Network Layer    | Packet definitions             | Test patterns, NOP/Skip, Data/Control                                                                            |

|------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------|

| rectwork Eager   | Packet error correction        | Retransmission, Buffering                                                                                        |

|                  | Data coding                    | XB/YB, Scrambling, DBI                                                                                           |

| Link (MAC) Layer | Link maintenance               | Presence detection, calibration phase, equalization, data rate negotiation, power down and sleep modes, recovery |

|                  | Error correction               | CRC, FEC, fault tolerance                                                                                        |

|                  | Line coding &<br>Signal levels | NRZ (PAM-2), Duobinary, PAM-4                                                                                    |

| Physical layer   | Impedance                      | 40/80 to 60/120 Ohms                                                                                             |

|                  | Channel type                   | Single-ended, Differential, Termination, Coupling (AC/DC)                                                        |

**Figure 2.3:** A selection of specification items and the OSI layers they are associated with. The items of the higher two layers in the diagram show interaction with the lowest layer. Higher layer analysis and design space exploration therefore requires an understanding of their influence on serializer performance.

most substantial interdependences are of course located at the data link layer which defines the low level link protocol but even at the network layer, there are design decisions to be made that have a direct impact on serializer implementation and performance evaluation.

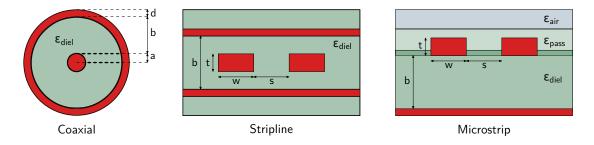

The design choices at the physical layer do not all directly mirror in the rather abstract view of figure 2.1. Most importantly, the *channel types* to be supported need to be well specified. This quite generally includes whether data is transmitted electrically or optically, whether transmission is wireline based or over-the-air and whether a bandlimited modulation technique or broadband communication is being used. In the context of wireline, broadband electrical communication as discussed here, one of the most central aspects is the *impedance domain* in which communication occurs (see also chapter 3). While for on-chip communication, this domain may be rather high impedance, long transmission channels across backplane and cabling generally use industry standard values in the range of 40 to  $80 \Omega$ . The impedance domain is also very important with respect to the coupling and termination scheme. While signal coupling can electrically either be done directly, capacitively or inductively, the termination schemes have a far greater variety (as evident from the vast number of different signaling schemes supported by modern FPGA IO cells for instance). For on chip communication, single ended capacitively coupled schemes without explicit termination have become popular [41] while for long-haul backplane communication as discussed here, differential signaling with termination at both ends of the channel is widely used. This is primarily due to the superior noise immunity and independence of any reference level between transmitter and receiver resulting from this scheme. AC coupling is primarily used once the transmission channel crosses connectors or

even systems (compute nodes for instance) while DC connections are preferred whenever tight control of the entire system to be implemented is possible. An example for this would be a memory module (such as HMC) connected to a CPU on the same board or even package where the power as well as the reference clock distribution are part of the systems design space.

In addition to impedance the *line coding and signal levels* for data transmission and reception need to be defined. The line coding is specified in the physical layer and one of the earliest design decisions of all. In this text, the focus solely lies on NRZ coding. This is, for the most part, due to its wide popularity and the interoperability requirements of the serializer whose development was assisted by this work. Another more complex choice for line coding may have been a duobinary or ternary coding scheme. Essentially, these codes exhibit a vastly different power spectral density (see section 3.4) with a redistribution of signal alphabet power in favor of lower frequency. Especially in high loss, long haul channels, this can substantially facilitate equalization efforts or the feasibility of power constraints. A much more involved choice offers a scheme such as a PAM-N code, where PAM stands for pulse amplitude modulation (PAM). A transceiver which utilizes NRZ line coding is also said to be using a PAM-2 scheme. There have been publications on PAM-4 systems [4, 32, 28, 13] which, with the advent of 100G Ethernet finally arrive at a commercial level as well. There is a substantial increase in design complexity associated with PAM-4, especially at the receiver (refer to caption of figure 2.12). Not only does the number of samplers and clocking resources increase. Also, equalization schemes and clock data recovery analysis are much more involved. The benefit ultimately lies in the relaxed equalization requirements compared to a PAM-2 system with the same baud rate. The baud rate is the number of symbols transmitted per second. An NRZ code encodes a single bit per bittime with its two voltage levels. A PAM-4 code on the other hand transmits two symbols per bit time with its four defined voltage levels.

At the link layer, one of the most influential decisions with respect to serializer performance and constraining is the *data coding*. Popular coding schemes are XB/YB schemes in which words of data to be transmitted are translated from X to Y bits with Y being greater than X. Concepts of how this transformation is carried out differ substantially for the various choices of X. In the past, one of the most popular choices has been 8B/10B coding [64] which used a predefined translation table under omission of some of the 10 Bit codes to guarantee a DC balance in the signal over a well defined run length. The DC balance constraint was meant to avoid a shift of the common mode voltage at the receiving samplers which would result in a reduction of the effective signal to noise ratio. At the same time, there is a guaranteed number of transitions per unit time so that AC coupled transmission lines may be used. Also, the clock recovery mechanisms all rely on tracking signal transitions and will therefore leave the ideal sampling instant (i.e. loose lock) when a specific lower bound for the transition density can not be upheld. When designing the

clock recovery circuit of a receiver, this is a very central aspect which requires thorough analysis. 8B/10B coding with its high transition density is a rather conservative choice in this regard and comes at a pretty substantial cost: only 80 percent of all bits transmitted actually convey user information. This is why in recent years, other combinations of X and Y have become more popular. The two most prominent are 64B/66B (10 Gigabit Ethernet / Fibre Channel) as well as 128B/130B (PCI-E 3.0). In both cases, there is no explicit transformation table. To ensure a statistical DC balance, the transmitter *scrambles* the data with a linear feedback shift register of a predefined polynomial while the receiving side inverts this process to recapture the original data. Theoretically, it is possible to force a scrambler into producing an indefinitely long sequence of static bits with a well chosen succession of input data. Usually, user data exhibits a good level of variability which the scrambling in turn will convert to a well randomized output bit stream (and therefore to a spectrally white frequency distribution). This may also be important for equalization training algorithms, especially the widely popular SS-LMS algorithm (see section 3.3) which rely on an equal symbol probability distribution.

Link initialization and management are also vital aspects of the link layer. In this context, the procedures in which a link is powered up or down, calibrated (to compensate circuit mismatches) or even set up with respect to its data rate and equalization need to be defined. If automatic adaption schemes are to be implemented in hardware, one of the key aspects to investigate is how to perform digital loop based equalization procedures and how these calibration loops respond to an elevated, initial bit error level. Another important aspect in this context is the definition of *link operability*. Usually, a link is said to be operable once it reaches the predefined bit error rate (see next subsection). The bit error rate cannot achieve low levels of statistical insignificance in all transmission domains, especially not within the domain primarily described in this text. The link layer therefore also needs to implement an error detection and recovery mechanism if the overall communication stack specification aims to avoid severe latency penalties as would be incurred if retransmissions of faulty data were delegated to higher OSI layers. Error detection and correction schemes can for instance be realized by forward error correction (FEC) or by cyclic redundancy checks (CRC). Fault recovery when failing to correct the received data may include the retransmission of the faulty packet. A thorough analysis of which error levels still allow to maintain an operable link within given performance specifications may allow to tweak overall power consumption and aid in the development of robust link transmission protocols. This again requires a serializer model which is closely tied to its physical implementation but simulates magnitudes faster.

The *network layer* may also benefit from a concise transceiver model. When defining test patterns and the overall package structure of the network, a thorough analysis may help to increase the overall power efficiency of the system and may expose new ways of implementing network power states and utilization awareness. This in turn helps to avoid

overconstraining the metrics for the serializer itself.

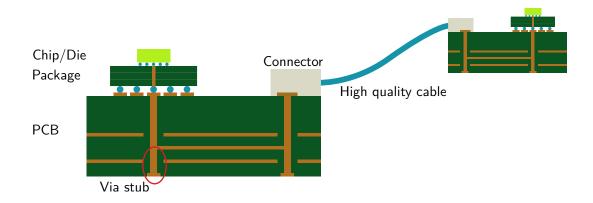

Figure 2.4: Physical system topology

#### 2.2.3 Power distribution

Figure 2.1 hints at the various power distribution networks (PDNs) of the subsystems. The PDN may have a strong impact on system performance, especially in highly integrated SOC environments. Whenever the small-signal properties of a circuit are of importance or in cases where the signal to noise ratio is of concern the influence of the power supply cannot be safely ignored. This usually excludes digital logic as long as excessive switching noise or supply voltage drops due to a lack of proper decoupling or series resistance (IR) analysis does not pose a problem.

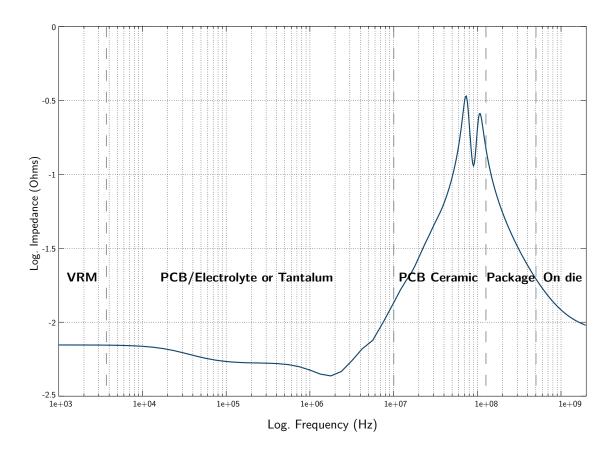

Figure 2.5 shows a typical impedance versus frequency function and the domains which dominate the response in the various regions of the plot as it would be expected from a mechanical arrangement such as the one shown in figure 2.4. The example is taken from an analog supply voltage rail of a custom built hybrid memory cube (HMC) test board. The electromagnetic extraction of the PCB board was performed in conjunction with an ECAD vendor supplied capacitor model database while the chip vendor supplied the combined die and package input impedance.

At lowest frequencies, the output impedance of the voltage regulator module (VRM) sets the lower bound of the power distribution network impedance  $Z_{PDN}$ . The output of the VRM is decoupled with very large capacitances (usually electrolyte or tantalum capacitors) which typically have a fair amount of equivalent series inductance (ESL) due to their mechanical size but are required to have very low equivalent series resistance (ESR) in order to maintain the good output impedance characteristics of  $Z_{PDN}$  at the lowest frequencies. The elevated level of ESL, of course, quickly forces their impedance to grow as frequencies increase. Therefore, small size ceramic capacitors on the PCB and in close

Figure 2.5: A typical power distribution network impedance characteristic

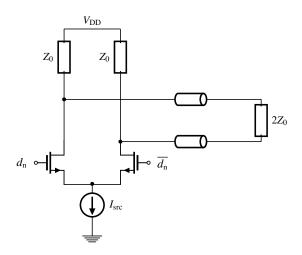

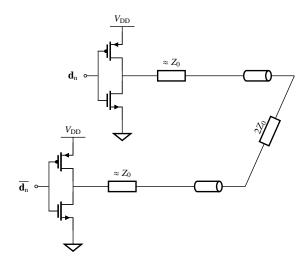

proximity to the current sinks are used to decrease  $Z_{PDN}$  at higher frequencies. If the number of capacitors on the PCB are to be kept small, there is usually an impedance peak in the region around (low) hundreds of MHz. This peak arises from the interaction of chip package inductance and PCB capacitance. Low ESL capacitances of small footprint and in close proximity to the chip package can be used to dampen the peak. Also, on-package capacitances may be used to attempt the same. However, oftentimes onboard capacitances suffer from additional ESL due to vias, especially on thick multilayered boards while onpackage capacitances are rather small due to limitations to their mechanical size. Therefore, on-board capacitances are often effective in the tens of MHz region, while on-package capacitances take an effect in the region of hundreds of MHz and slightly beyond. The impedance at very high frequencies is dominated by the actual chip (die) power distribution and decoupling network. On-die capacitances have virtually no equivalent inductance but may suffer from increased series resistance if not carefully tied to the supply network with large metal strips and sizable via count. It is the averaged ESR of the chip which dominates the high frequency behavior of  $Z_{PDN}$ . It has become custom practice to separate the power supplies of the PLL from the rest of the system. Transmitter and receiver are

usually tied together in a common domain. In order to minimize interactions between the digital, complementary metal oxide semiconductor (CMOS) and therefore switching noise dominated part and the analog, often current mode logic (CML) dominated and noise sensitive part of the design, a separation of digital and analog supplies on the level of chip and package has also been used. Additionally, with a shrink in technology feature sizes, the core voltage decreases, too, due to smaller gate oxide thicknesses. While 65 nm nodes can still be operated with up to 1.2 Volts, the 22 nm node forces designers to work with supplies as low as 0.7 Volts. This quickly becomes a problem for all I/O standards and specifically to serializers (see also subsection 2.2.5). The alternative of using thick-oxide transistors when designing for smaller technology nodes necessitates a further supply and PDN which leads to design challenges especially on the packaging level but may have a favourable impact on the supply noise characteristics in conjuction with other specific design choices (see again subsection 2.2.5). As can be seen from this discussion, there is a lot of information required to obtain a meaningful Z<sub>PDN</sub>. In addition to the vendor supplied characteristics of capacitors and VRM, at least a 2.5D field solver based extraction of the power distribtion network (PCB and package) is required. Also, a good estimate of the total die capacitance and ESR is needed as well. Typically this kind of information is only available very late in the design phase. Therefore, it is common practice to model the PDN as a bandwidth limited thermal noise source with a power spectral density of either

$$S_{\text{VV, LP}}(\omega) = \frac{\sqrt{\pi}(1+\sqrt{2})\sigma_{\text{vn,pdn}}^2}{\omega_{3\text{db,pdn}}} \cdot \frac{1}{1+\left(\frac{\omega}{\omega_{3\text{db,pdn}}}\right)^2}$$

(2.9)

or (much more unphysical and even discontinuous)

$$S_{\text{VV, Box}}(\omega) = \begin{cases} \frac{\sigma_{\text{vn,pdn}}^2}{\omega_{\text{3db,pdn}}} &, 0 \le \omega < \omega_{\text{3db,pdn}} \\ 0 &, \text{else} \end{cases}$$

where in both cases  $\sigma_{vn,pdn}^{\ddagger}$  is the actual in-band RMS voltage noise and  $\omega_{3db,pdn}^{\ddagger}$  the PDN bandwidth. The additional factor for the lowpass filter type is chosen such that in both cases we obtain

$$\int_{0}^{\omega_{3\text{dh,pdn}}} S_{\text{VV}}(\omega) d\omega = \sigma_{\text{pdn}}^{2}$$

and thereby ensure that the noise power contribution made by the PDN to the system is well defined by the parameter  $\sigma_{\text{vn,pdn}}$ . Note that here, we drop the notion of the PDN having an impedance alltogether and think of it plainly as a source of noise power. This noise power would normally originate from the interaction of the systems current consumption  $S_{\text{I}}(\omega)$

(given in its spectral form) with the PDN impedance which is also a complex quantitiy. The voltage spectral density seen at the power supply would then be given by

$$S_{\rm V}(\omega) = S_{\rm I}(\omega) \cdot Z_{\rm PDN}(\omega)$$

and its equivalent voltage noise can be determined from the resulting PSD as  $S_{VV}(\omega) = |S_V(\omega)|^2$ . As mentioned above, a good estimate of both  $S_I(\omega)^{\ddagger}$  and  $Z_{PDN}(\omega)^{\ddagger}$  can generally be obtained with substantial effort and can potentially be included in budgeting procedures. Conversely, it is possible to use budgeting approaches to produce meaningful constraints to  $Z_{PDN}(\omega)$  as board and package implementation design input. Care must be taken, however, to not delegate too much of the noise reduction efforts to system designers as their design space is much more limited compared to the IC design itself. The equivalent noise source approach of course assumes that the noise seen at the power supply is completely uncorrelated with serializer events. Evidently, this is especially untrue for CMOS type logic of which an increasing amount will be found in the serializers of the nodes and years to come. While for the initial system design phase, the simple model serves its purpose, the final design verification and sign-off should rely on more elaborate methods. An intermediate solution to the problem is the definition of an impedance mask and the deduction of approximate time resolved current consumption as part of the modeling process.

#### 2.2.4 Phase locked loop

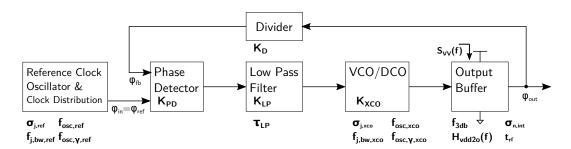

**Figure 2.6:** A simplified block diagram of a phase locked loop (after [34]) with the subcomponent metrics as used for link budgeting in this text

As depicted in figure 2.4, a transmitter and receiver pair which form the active part of a communication channel are surely located on different dies. In some applications such as in system area networks (PCI-e, QPI) and backplane interconnects, their PLLs may share a common reference clock  $\phi_{ref}$ . However, even in these cases, the clock distribution channels from the common reference oscillator to the respective dies usually are not identical. The reference clock channel jitter amplification properties may therefore differ, too ( see

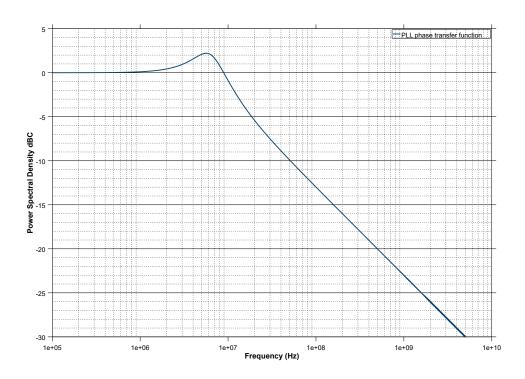

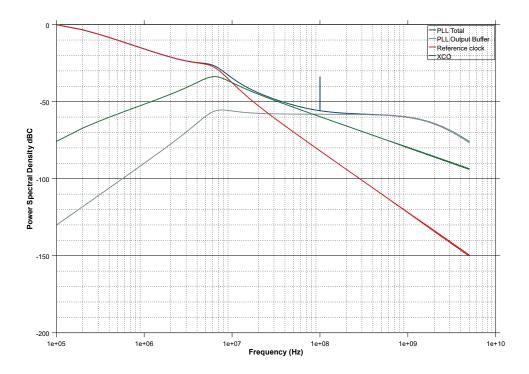

section 5.3.4) which may in turn lead to differing characteristics for the two PLLs. In HPC networking applications, the reference oscillators are certainly not identical whereas the clock distribution channel usually is (if a reference oscillator is located on the network interface controller (NIC) PCB). In this case, a single PLL model for both sides is sufficient. The reference oscillator together with its clock distribution channel is not shown in figure 2.1 as it is a part of the phase locked loop (PLL) model here. The task of a PLL is to generate a high frequency, low jitter reference clock for the transmitter and receiver clock dividers, its (de-)mux stages, the transmitter output driver and the receiver samplers. It is distributed to transmitter and receiver via the on-chip clock tree. The effect of on-die clock distribution is logically assigned to transmitter and receiver domains and will be discussed below. The effect of clock distribution from the high precision reference oscillator (usually a quartz with an oscillation frequency of a few MHz) can potentially be integrated with its model representation directly. Figure 2.6 shows a typical PLL block diagram together with the metric symbols used for budgeting. The design space of these subcomponents is quite large and well beyond the scope of this text. Fortunately, irrespective of the exact implementation, it is usually possible to model a PLL as a second order transfer function in phase space. Ultimately, for the system presented here, the relevant high level metric of the PLL is the phase noise power spectral density  $S_{\phi\phi}(\omega)^{\ddagger}$  including the effects of the PLL power supply. If it is known beforehand and the PLL is no part of the design budgeting process, it is the single piece of information required for deriving constraints for other subcomponents. If the PLL design effort shall be part of the constraining efforts, however, a good or at least rough approximate shape of the phase noise PSD is of importance. It is the spectral content of this jitter that will impede the transmitter output, be potentially amplified by the channel and be finally processed by the clock data recovery circuit of the receiver. Therefore, it will have a significant impact on the system performance (see section 2.2.6). In a final implementation  $S_{\phi\phi}(\omega)$  will be obtained by a periodic steady state and periodic noise simulation as offered by modern RF Spice simulators. The sensitivity of the PLL to noise on the power supply can also be obtained in this way - the necessary analysis is called the periodic transfer function (PXF) simulation and is also beyond the scope of this text. As is the case with detailed PDN metrics, these simulations can only be obtained fairly late in the design phase. For design space analysis and budgeting purposes, the condensed second order model as suggested by Mansuri and Kang [34] and as also used by the PCI Express Jitter modelling specification [47] will be used: The prototypical second order phase transfer function of a PLL in phase space is given as [34]

$$H_{\rm PLL}(s) = \frac{\phi_{\rm out}}{\phi_{\rm in}} = \frac{2\zeta\omega_{\rm n}s + \omega_{\rm n}^2}{s^2 + 2\zeta\omega_{\rm n}s + \omega_{\rm n}^2}$$

(2.10)

where  $\omega_n$  is the PLL natural frequency and  $\zeta$  the damping factor of the closed loop system. The relation between natural frequency and the 3 dB cutoff frequency of the PLL equates

to  $\omega_{3dB} = \omega_n \sqrt{1 + 2\zeta^2 + \sqrt{(1 + 2\zeta^2)^2 + 1}}$ . On the one hand, we do not particularly care about the exact interdependences of a detailed PLL design here. On the other hand, we would like to use the link budgeting procedure and framework to derive general target specification values for the subcomponents of the PLL and weigh their impact against other subdesign choices. Therefore, we will go a step further than the two bare performance parameters mentioned above and discuss the PLL design in some more detail (see again figure 2.6). This is also necessary to arrive at the ultimate goal of obtaining a phase noise PSD for the PLL output - the various noise sources and their contribution to the noise seen at the output need to be taken into account in this case.

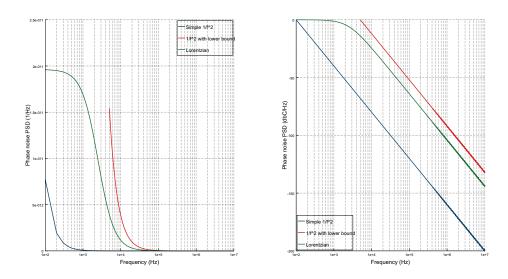

Figure 2.7: Phase noise power spectral densities of the three oscillator models presented in this text.

A PLL takes the reference clock of a quartz oscillator as its input and generates an output clock at a potentially higher frequency which is phase locked to the reference. The reference clock itself already exhibits jitter and therefore has a phase noise PSD associated with it. It is common to approximate the phase noise with

$$\mathcal{L}(f) = \frac{\sigma_{\rm n,ref}^2 f_{\rm ref}^3}{f^2}$$

where  $\sigma_{n,ref}$  is the total RMS cycle jitter both produced (by voltage noise of internal devices) and induced (via supply) in the oscillator. This does not take 1/f noise into account. However, this noise contribution is only relevant at very low frequencies and does not much affect the performance of the serializer system as can be seen at a later point (see subsection 5.3.6). Quartz vendors do not directly provide information on  $\sigma_{n,ref}$

in their datasheets. Fortunately, this is not necessary as the usual information on the total RMS output jitter of the quartz  $\sigma_{j,ref}^{\ddagger}$  along with its center frequency of oscillation  $f_{ref}^{\ddagger}$  are enough for the most simple model. Due to equation 2.8 the following relation for the given parameters hold:

$$\sigma_{\rm j,ref} = \frac{4}{(2\pi f_{\rm ref})^2} \int_{1}^{f_{\rm j,BW}} 2\mathcal{L}(f)df \qquad \rightarrow \qquad \sigma_{\rm n,ref} = \frac{\pi \sigma_{\rm j,ref}}{\sqrt{2f_{\rm ref}}}$$

Along with the total output jitter, vendors usually supply the frequency bandwidth  $f_{j,BW}^{\ddagger}$  across which the measurement was made. For the simple  $1/f^2$  model given here, this information, albeit used during the integration of the phase noise PSD, does not affect the model value  $\sigma_{n,ref}$ . This is due to the divergent nature of the phase noise function for  $f \to 0$  which is also the reason for restricting the integration above towards the lower bound to 1 Hz. This restriction of the integration interval essentially states that the bulk of noise power as given by  $\sigma_{n,ref}$  concentrates within 2 Hz around the carrier. This frequency precision cannot even be achieved with the best devices on the market. Some *spectral broadening* around the central carrier frequency can always be observed. If this broadening is described with the parameter  $f_{osc,\gamma}^{\ddagger}$  the integration above gives

$$\sigma_{\text{n,ref}} = \frac{\pi \sigma_{\text{j,ref}}}{\sqrt{2 f_{\text{ref}}}} \left( \frac{f_{\text{j,BW}} f_{\text{osc,}\gamma}}{f_{\text{j,BW}} - f_{\text{osc,}\gamma}} \right)$$

The rather unrealistic notion that frequencies below  $f_{\rm osc,\gamma}$  do not contribute to overall phase noise power puts more energy into higher frequency bands. This overestimation, however, may lead to more conservative overall designs. The error made by approximating the reference oscillator phase noise by almost Dirac like functions can be resolved by using a Lorentzian model. It has been shown that oscillators, much like many other resonating physical systems, exhibit a spectral phase noise power distribution that adheres to this form[49]:

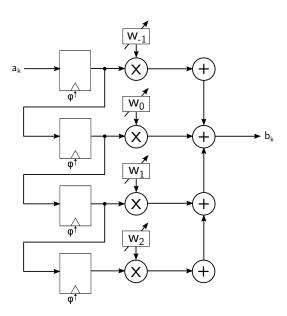

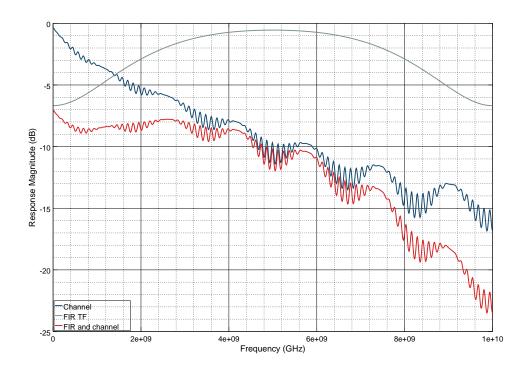

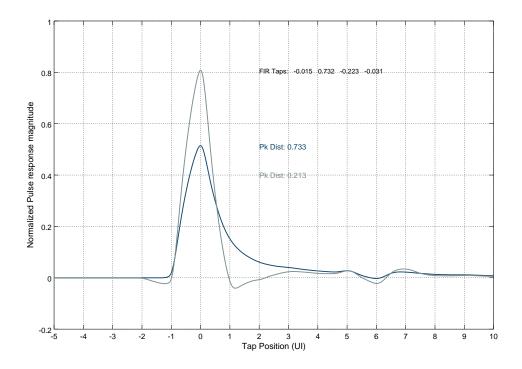

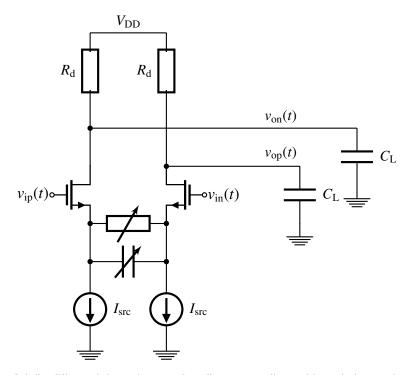

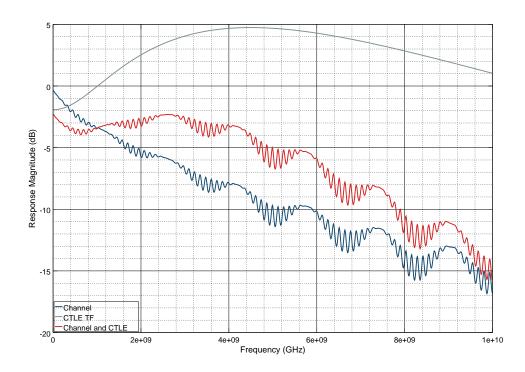

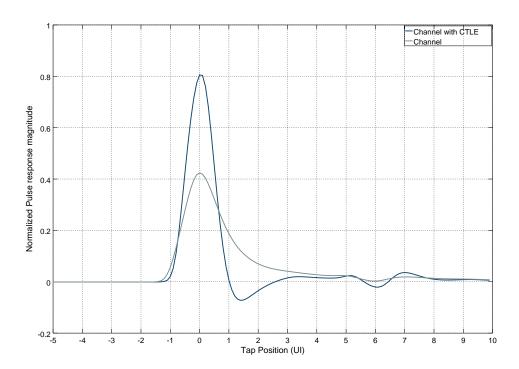

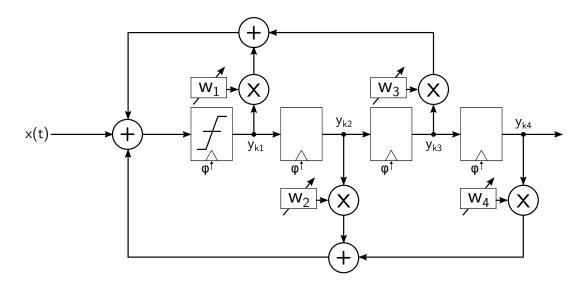

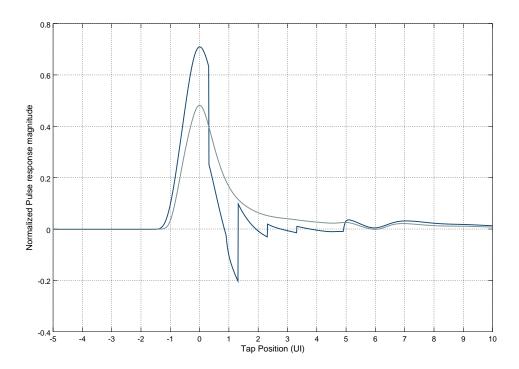

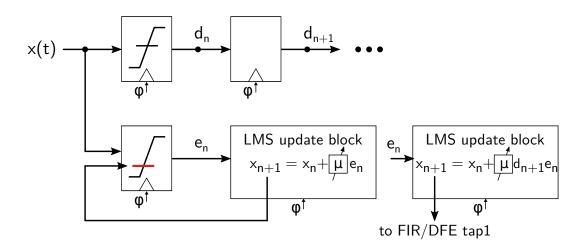

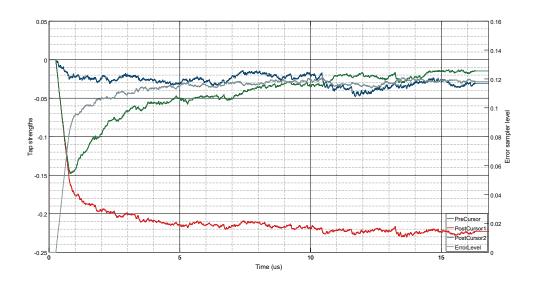

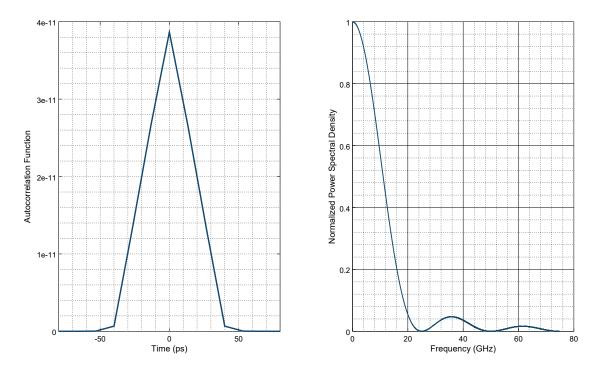

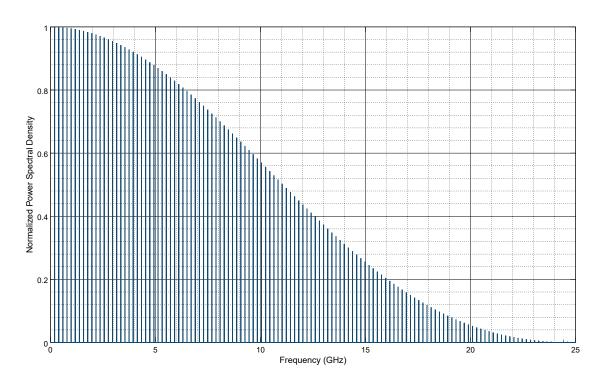

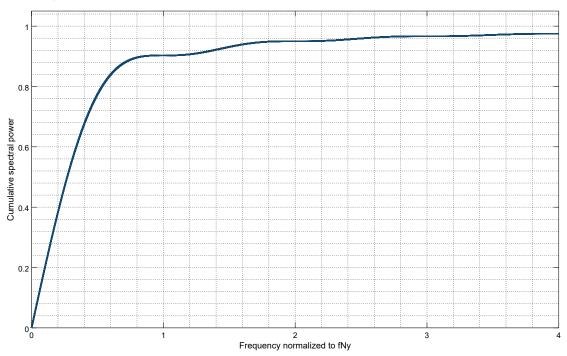

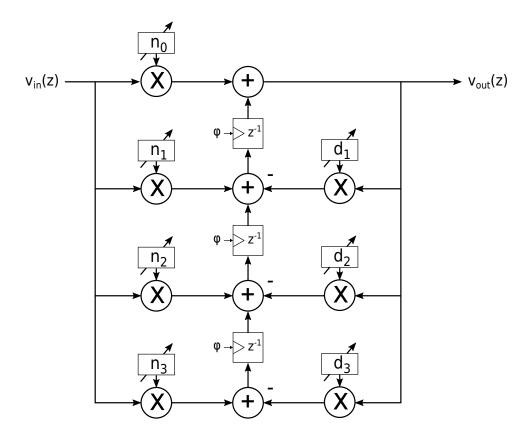

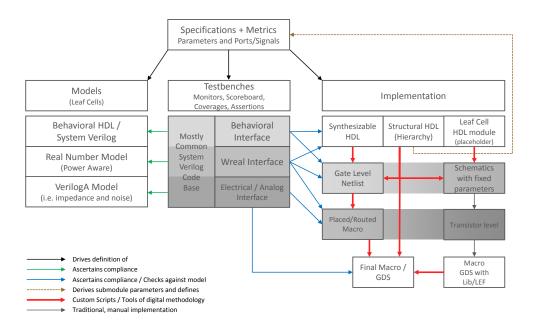

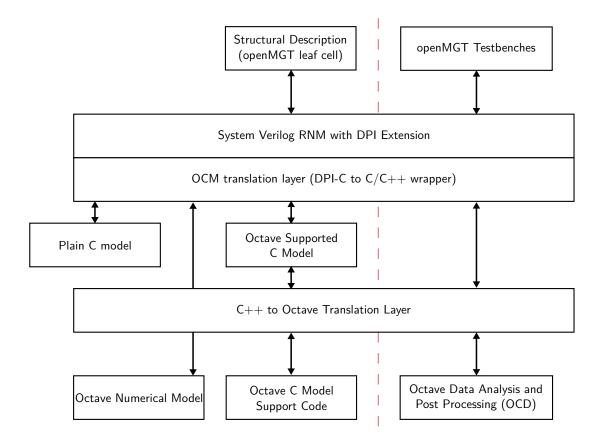

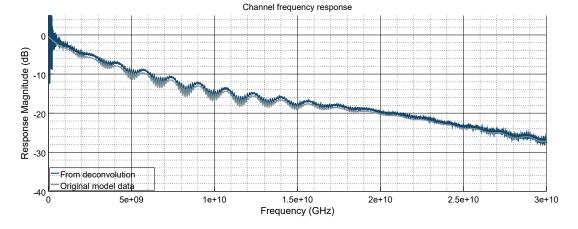

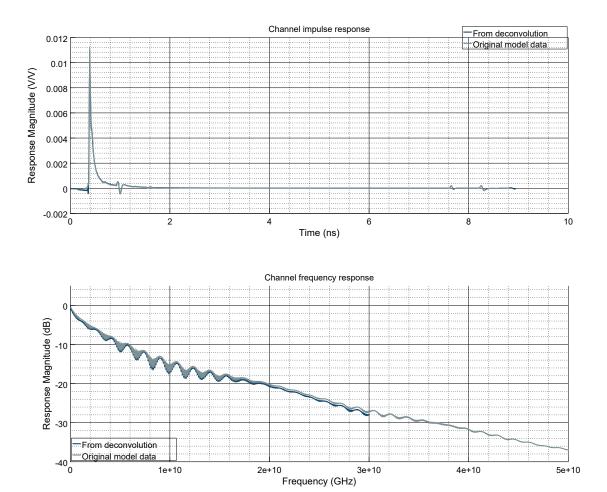

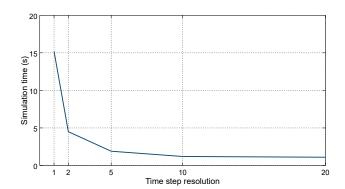

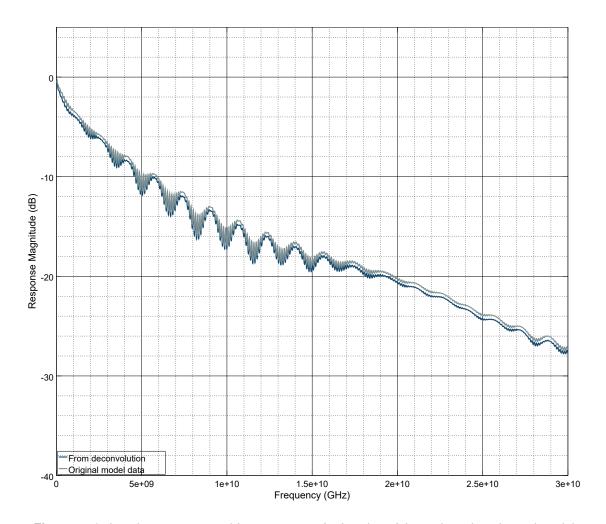

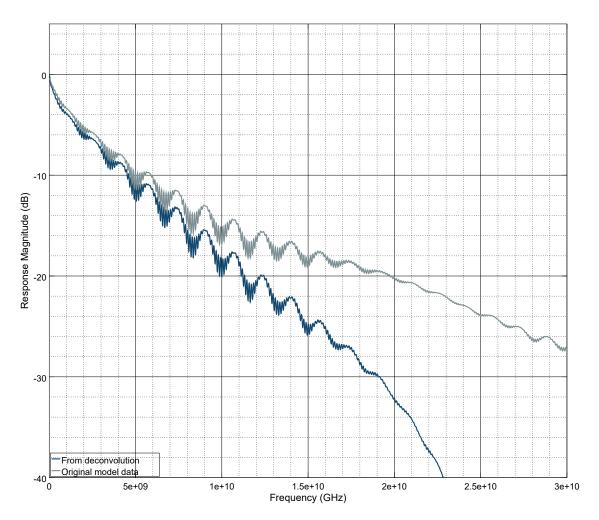

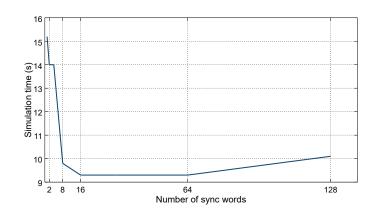

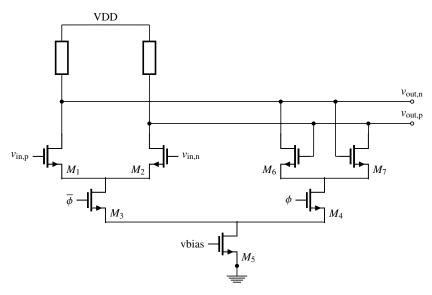

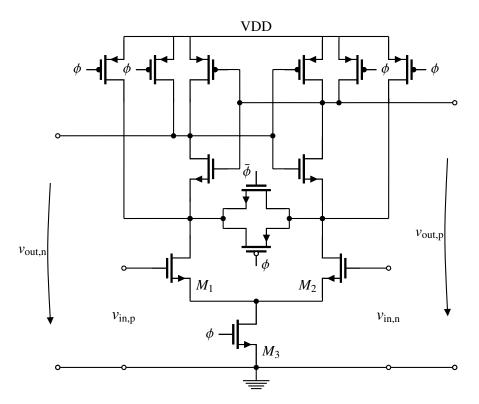

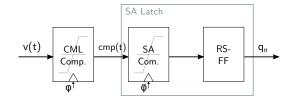

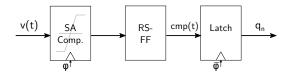

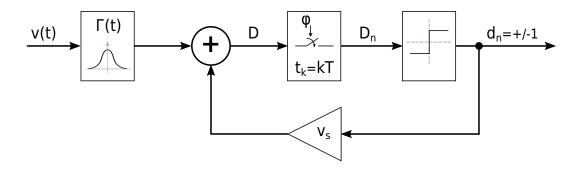

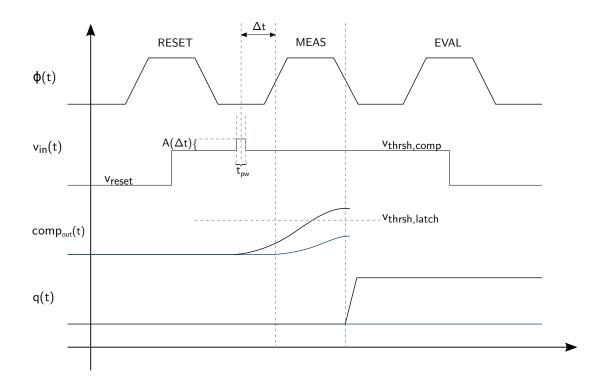

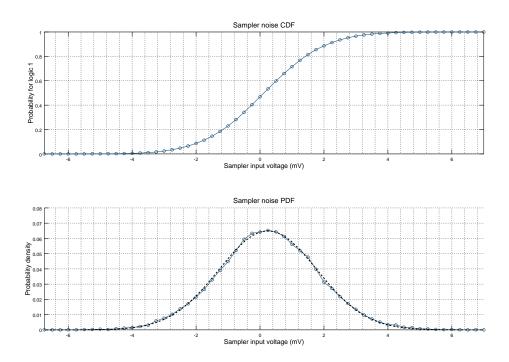

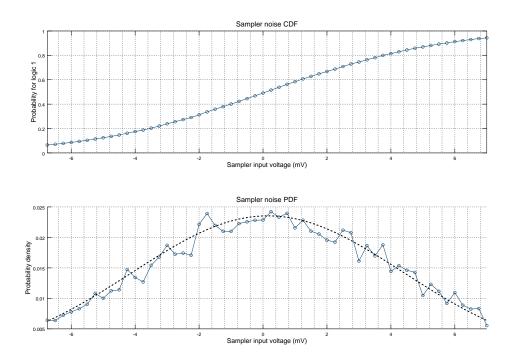

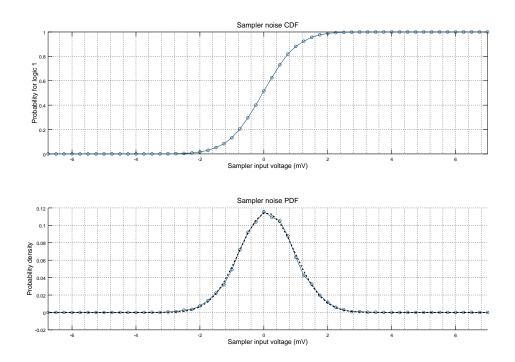

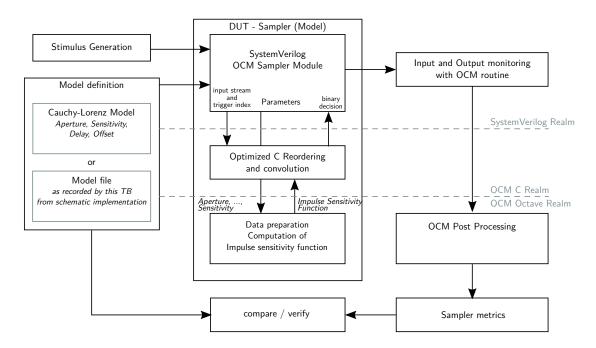

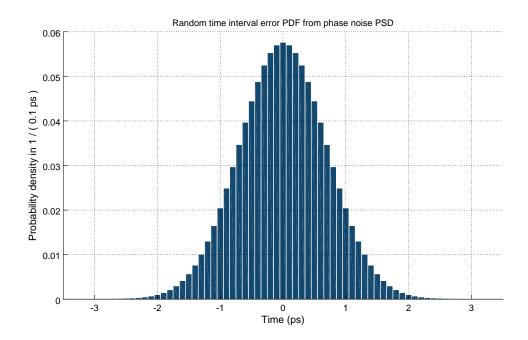

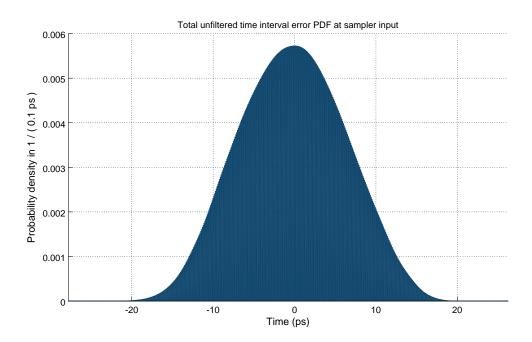

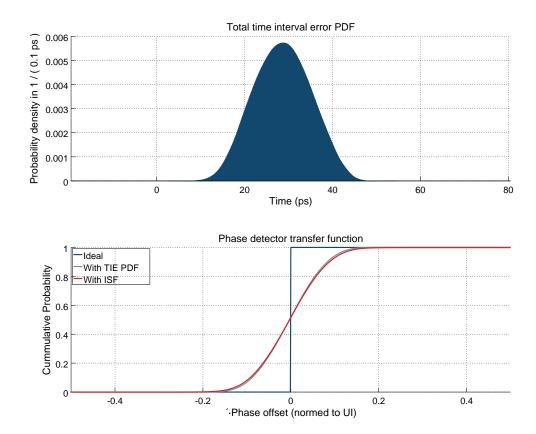

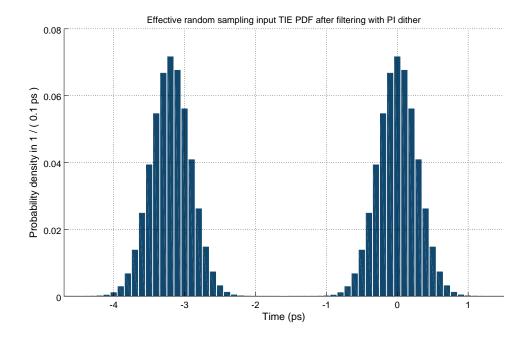

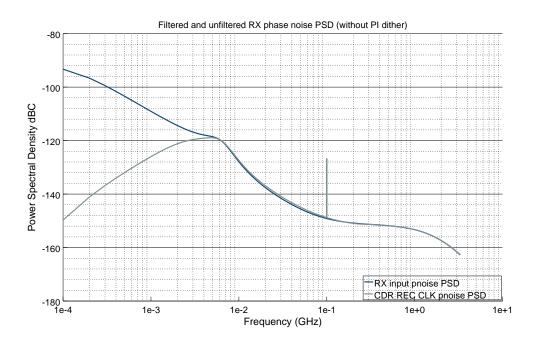

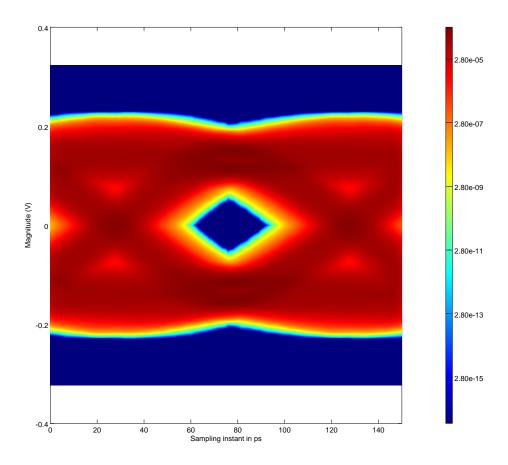

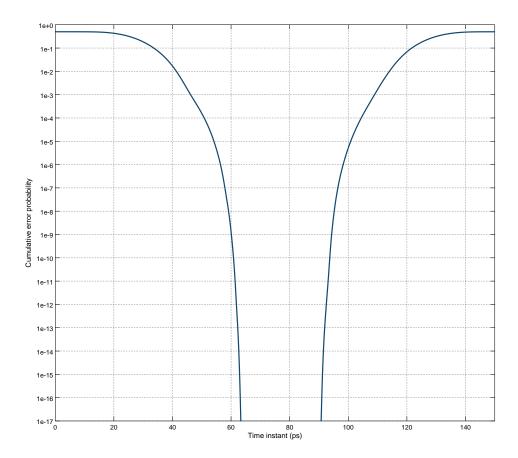

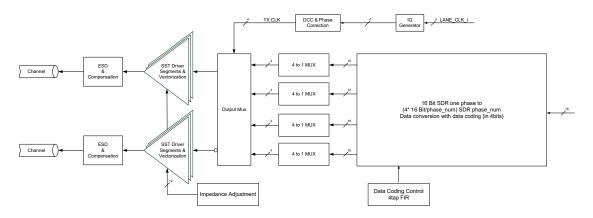

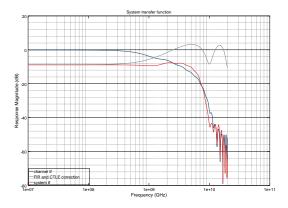

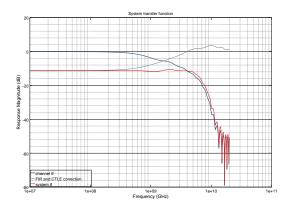

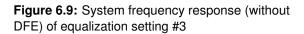

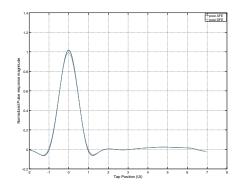

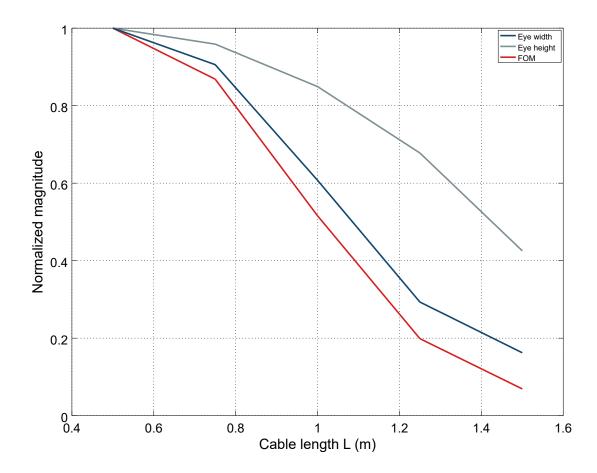

$$\mathcal{L}(f) = \frac{cf_{\text{osc}}^2 \sigma_{\text{n,ref}}^2}{(\pi f_{\text{osc}}^2 c)^2 + f^2} \quad \text{where} \quad c = \frac{f_{\text{osc},\gamma}}{2\pi f_{\text{osc}}^2}$$