# Fakultät für Physik und Astronomie Ruprecht-Karls-Universität Heidelberg

**Diplomarbeit**im Studiengang **Physik**

vorgelegt von

Kai König

aus Heidelberg

Mai 2005

# Entwicklung eines ASICs in Hochspannungstechnologie zur kombinatorischen Microarray – Peptidsynthese

Diese Diplomarbeit wurde von Kai König ausgeführt am Kirchhoff-Institut für Physik

unter der Betreuung von

Herrn Prof. Dr. Volker Lindenstruth

sowie von

Herrn Priv.-Doz. Dr. Ralf Bischoff

Deutsches Krebsforschungszentrum Heidelberg

# Entwicklung eines ASICs in Hochspannungstechnologie zur kombinatorischen Microarray – Peptidsynthese

Arraytechnologien gewinnen zunehmend an Bedeutung in der aktuellen biologischen, medizinischen und pharmazeutischen Forschung. Das "Peptidchip"-Gemeinschaftsprojekt zwischen dem Deutschen Krebsforschungszentrum (DKFZ) und dem Kirchhoff-Institut für Physik der Universität Heidelberg (KIP) hat zum Ziel, Arrays hoher Dichte zu entwickeln, die insbesondere für kombinatorische Peptidsynthese und die zugehörigen Bindungsexperimente geeignet sind.

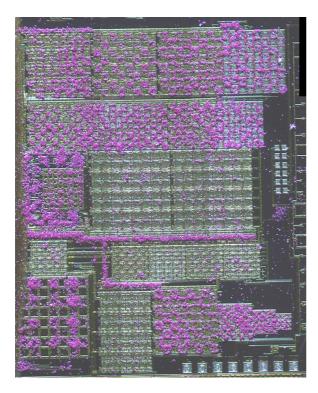

Im Rahmen dieses Projekts durchgeführt, beschreibt diese Arbeit die Entwicklung eines ASICs in Hochspannungs-CMOS-Technologie, der als Träger für ein solches Peptid-Microarray nutzbar ist. Geladene Partikel, die Aminosäuren oder andere Monomere enthalten können, werden im vom Chip erzeugten elektrischen Feld ortsselektiv auf der modifizierten Oberfläche des Chips abgelagert. Dies erlaubt die parallele Synthese mehrerer Oligomere auf dem Chip. Strukturen mit Spotabständen zwischen 100 µm und 45 µm und schaltbare Potentiale von bis zu 100V wurden implementiert und getestet. Ein I<sup>2</sup>C-Interface wird benutzt, um den Chip mit Partikelablagerungsmustern zu programmieren. Der Chip ermöglicht auch die Untersuchung optischer Methoden zur Bindungsereignissen unter Verwendung von integrierten CMOS-Photodioden. Architektur, Design und Simulation des Chips werden in dieser Arbeit beschrieben, ebenso wie experimentelle Ergebnisse des ortsselektiven Transfers von Partikeln auf den Chip.

# Development of an ASIC using high-voltage technology for combinatorial microarray peptide synthesis

Array technology is becoming increasingly important in current biological, medical and pharmaceutical research. The "Peptide Chip" joint project between Deutsches Krebsforschungszentrum (DKFZ) and Kirchhoff-Institut für Physik, Universität Heidelberg (KIP) aims at developing high-density arrays especially suited for combinatorial peptide synthesis and corresponding binding experiments.

Conducted in the framework of this project, this thesis describes the development of an ASIC in High-Voltage CMOS technology to be used as a carrier for such a peptide microarray. Charged particles, that can contain amino acids, are selectively deposited onto the modified chip surface using an electrical field generated by the chip. This allows the synthesis of numerous different oligomers on the chip in parallel. Structures covering spot pitches between 100µm and 45µm and switchable potentials of up to 100V have been implemented and tested. An I<sup>2</sup>C interface is used to program particle deposition patterns into the chip. The chip also allows the investigation of optical methods to detect binding events using integrated CMOS photodiodes. Architecture, design and simulation of the chip are described in this thesis, as are experimental results on spatially selective particle transfer onto the chip.

### Inhaltsverzeichnis

| Ei | nführ | ung .    |                                        | •  | •  | •   | •    | •    | •   | •   | •   | •   | • | • | 1  |

|----|-------|----------|----------------------------------------|----|----|-----|------|------|-----|-----|-----|-----|---|---|----|

| TE | al I  | GRUNDL   | AGEN UND METHODEN                      |    |    |     |      |      |     |     |     |     |   |   |    |

| 1  | Biol  | ogie der | Aminosäuren, Bioarrays, Biochips       |    |    | •   | •    |      |     |     | •   | •   | • |   | 7  |

|    | 1.1.  | Amino    | säuren, Peptide, Proteine              |    |    |     |      |      |     |     |     |     |   |   | 7  |

|    |       | 1.1.1.   | Biochemische Einordnung                |    |    |     |      |      |     |     |     |     |   |   | 7  |

|    |       | 1.1.2.   | Aminosäuren und die Peptidbindung      |    |    |     |      |      |     |     |     |     |   |   | 7  |

|    |       | 1.1.3.   | Von der Peptidbindung zum Protein.     |    |    |     |      |      |     |     |     |     |   |   | 8  |

|    |       | 1.1.4.   | Peptidsynthese im Labor                |    |    |     |      |      |     |     |     |     |   |   | 9  |

|    | 1.2.  | Bioarra  | ays und Biochips                       |    |    |     |      |      |     |     |     |     |   |   | 11 |

|    |       | 1.2.1.   | Einleitung                             |    |    |     |      |      |     |     |     |     |   |   | 11 |

|    |       |          | Anwendungen von Peptidarrays           |    |    |     |      |      |     |     |     |     |   |   | 12 |

|    |       |          | Erzeugung von Peptidarrays und Stand   |    |    |     |      |      |     |     |     |     |   |   | 13 |

|    |       |          |                                        |    |    |     |      |      |     |     |     |     |   |   |    |

| 2  | Anv   | vendung  | gsspezifische integrierte Schaltungen  |    |    |     |      |      |     | •   |     |     |   |   | 15 |

|    |       |          | onische Schaltungen im CMOS-Prozess    |    |    |     |      |      |     |     |     |     |   |   | 15 |

|    |       | 2.1.1.   | Einleitung                             |    |    |     |      |      |     |     |     |     |   |   | 15 |

|    |       | 2.1.2.   | Der MOSFET: Aufbau und Verhalten       |    |    |     |      |      |     |     |     |     |   |   | 16 |

|    | 2.2.  | CMOS     | und hohe Spannungen                    |    |    |     |      |      |     |     |     |     |   |   | 19 |

|    |       | 2.2.1.   | Einleitung                             |    |    |     |      |      |     |     |     |     |   |   | 19 |

|    |       | 2.2.2.   | Physikalische Grenzen                  |    |    |     |      |      |     |     |     |     |   |   | 20 |

|    |       | 2.2.3.   | Elektronik                             |    |    |     |      |      |     |     |     |     |   |   | 22 |

|    | 2.3.  | Optiscl  | he Eigenschaften von CMOS – Bauteile   | n  |    |     |      |      |     |     |     |     |   |   | 30 |

|    |       | 2.3.1.   | Einleitung                             |    |    |     |      |      |     |     |     |     |   |   | 30 |

|    |       | 2.3.2.   | Einleitung                             |    |    |     |      |      |     |     |     |     |   |   | 31 |

|    |       | 2.3.3.   | Dedizierte Photodioden                 |    |    |     |      |      | _   |     | _   |     |   |   | 31 |

|    |       |          |                                        |    |    |     |      |      |     |     |     |     |   |   |    |

| 3  | Übe   | rtrag vo | on geladenen Partikeln auf aktive Trä  | ge | rι | ınd | l da | as l | Per | tic | lch | ip- |   |   |    |

|    |       | _        |                                        | _  |    |     |      |      | -   |     |     | -   |   |   | 35 |

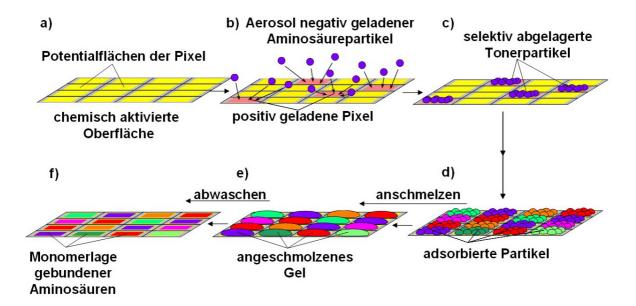

|    | 3.1.  | Grundi   | ideen der chipbasierten Peptidsynthese |    |    |     |      |      |     |     |     |     |   |   | 35 |

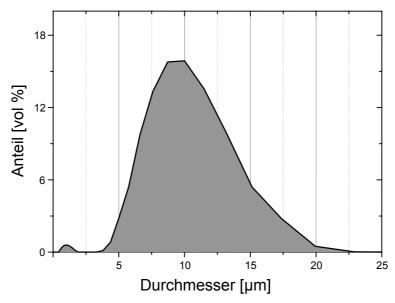

|    | 3.2.  | Tonerü   | ibertrag im Aerosol                    |    |    |     |      |      |     |     |     |     |   |   | 36 |

|    |       | 3.2.1.   | ibertrag im Aerosol                    |    |    |     |      |      |     |     |     |     |   |   | 36 |

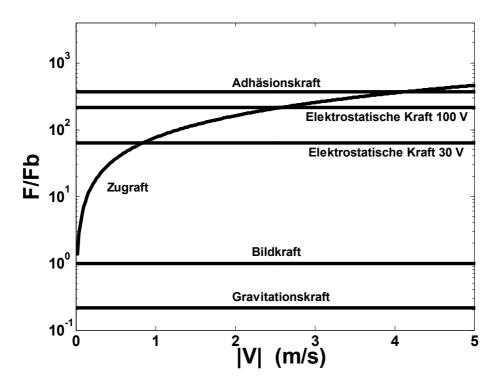

|    |       | 3.2.2.   | Wirkende Kräfte                        |    |    |     |      |      | _   |     | _   |     |   |   | 37 |

|    |       | 3.2.3.   | Bewertung der Beschichtungsqualität    |    |    |     |      |      |     |     |     |     |   |   | 39 |

|    |       | 3.2.4.   | Multipolpixel                          |    |    |     |      |      |     |     | -   |     |   |   | 40 |

|    | 3.3.  | Nachw    | reis von Bindungsereignissen           |    |    |     |      |      |     |     | -   |     |   |   | 41 |

|    | 3.4.  | Das Pe   | eptidchip-Gesamtsystem                 |    |    |     |      |      |     |     |     |     |   |   | 41 |

ii Inhaltsverzeichnis

| 4  | Vorv       | zersuche ui | nd bisherige A     | Arbeiten           | am            | Pept       | idcl | nip. | -Pro | ojek | t. | • | • | • | • | • | • | 43       |

|----|------------|-------------|--------------------|--------------------|---------------|------------|------|------|------|------|----|---|---|---|---|---|---|----------|

|    | 4.1.       | Vorversuc   | he                 |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 43       |

|    |            |             | n Peptidchip 2     |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 43       |

|    |            |             | ele                |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 43       |

|    |            | 4.2.2. Pro  | ozesswahl .        |                    | _             |            |      | _    |      | _    |    |   |   |   |   |   | _ | 43       |

|    | 4 3        | Design un   | d Layout Pepti     | dchin 2            |               |            |      |      |      |      |    |   |   |   |   |   |   | 44       |

|    |            |             | u Peptidchip 2     |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 47       |

|    | 4.5        | Fraehnisse  | e Peptidchip 2     |                    | •             |            | •    | •    |      | •    | •  | • | • | • | • | • | • | 48       |

|    | т.Э.       | 4.5.1 F1    | ektronische Te     | ete                | •             |            | •    | •    |      | •    | •  | • | • | • | • | • | • | 48       |

|    |            | 4.5.1. ER   | ersuche zum To     | oio<br>mariihar    | tro a         |            | •    | •    |      | •    | •  | • | • | • | • | • | • | 50       |

|    |            | 4.3.2. VC   | risuciie zuiii 10  | oner uber          | uag           |            | •    | •    |      | •    | •  | • | • | • | • | • | • | 30       |

| TE | ль II      | Durchfüh    | IRUNG              |                    |               |            |      |      |      |      |    |   |   |   |   |   |   |          |

| 5  | Kon        | zention Pe  | ptidchip 3 .       |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 55       |

| -  |            |             | Anforderungen      |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 55       |

|    |            |             | hl                 |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 56       |

|    | 5.2.       | Konzentio   | n der Teilkom      | nonentei           | n .           |            | •    | •    |      | •    | ٠  | • | • | • | • | • | • | 57       |

|    | 5.5.       | 5 3 1 Di    | e Hochspannu       | ngs_Pive           | ıı .<br>Afeld | <br>er     | •    | •    |      | •    | •  | • | • | • | • | • | • | 57       |

|    |            | 5.3.1. Dr   | er Versorgungs     | ngs-i inc<br>tail  | iicia         | C1 .       | •    | •    |      | •    | •  | • | • | • | • | • | • | 58       |

|    |            | 5.3.2. Di   | a Tagtatrulsture   | m .                | •             |            | •    | •    |      | •    | •  | • | • | • | • | • | • | 59       |

|    |            |             | e Teststrukture    |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 59<br>59 |

|    |            | 5.3.4. W    | asserstoffdetek    | tion .             | •             |            | ٠    | •    |      | •    | ٠  | ٠ | • | • | • | • | • | 39       |

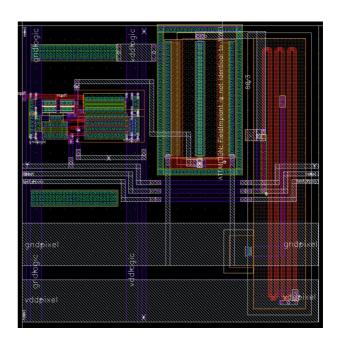

| 6  | Desi       | gn und Lay  | yout Peptidch      | ip 3               |               |            |      |      |      |      |    |   |   | • |   |   |   | 61       |

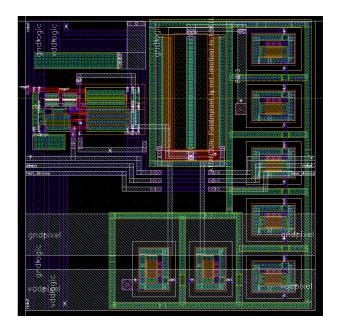

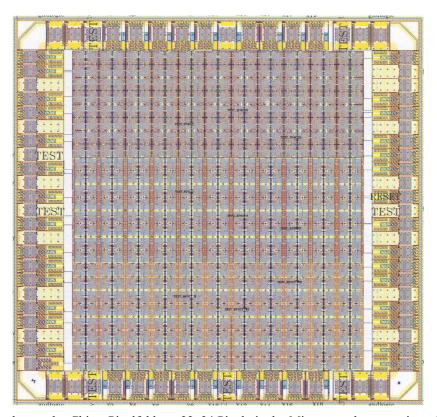

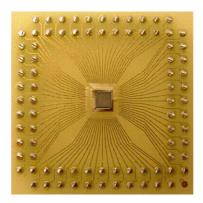

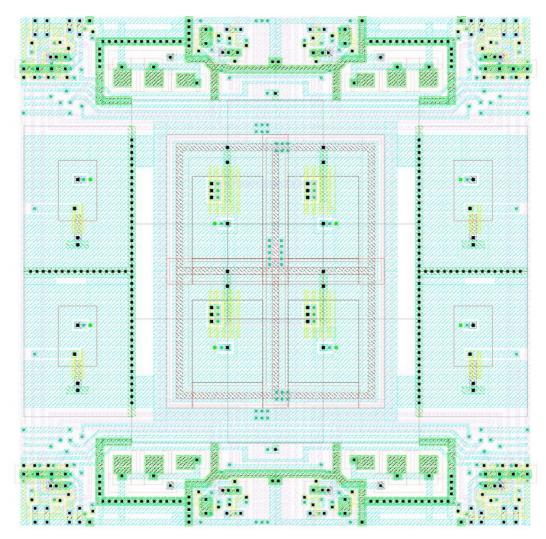

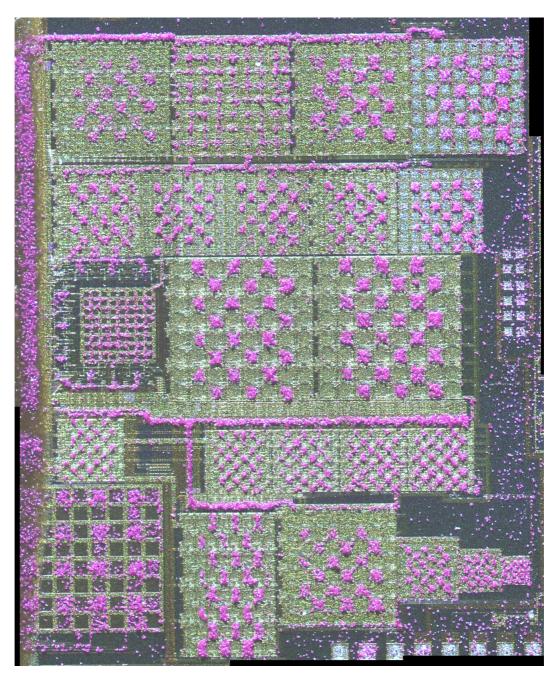

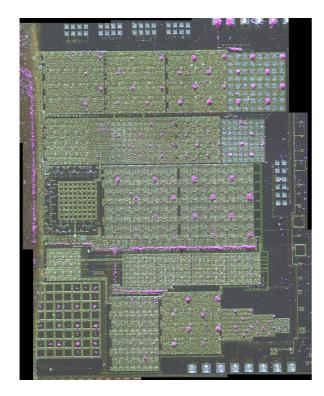

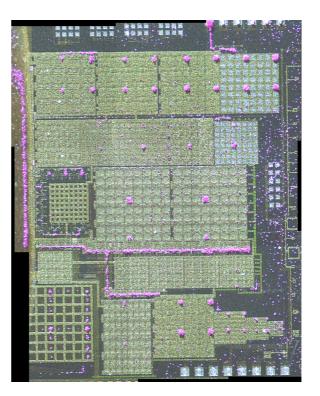

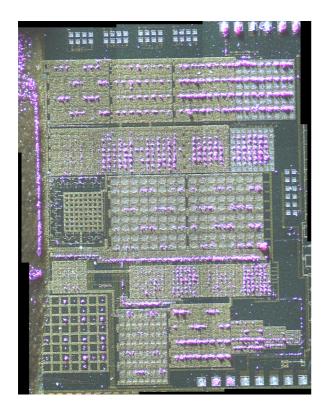

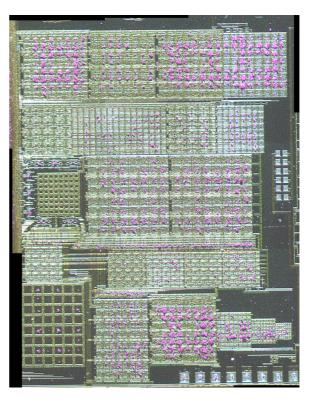

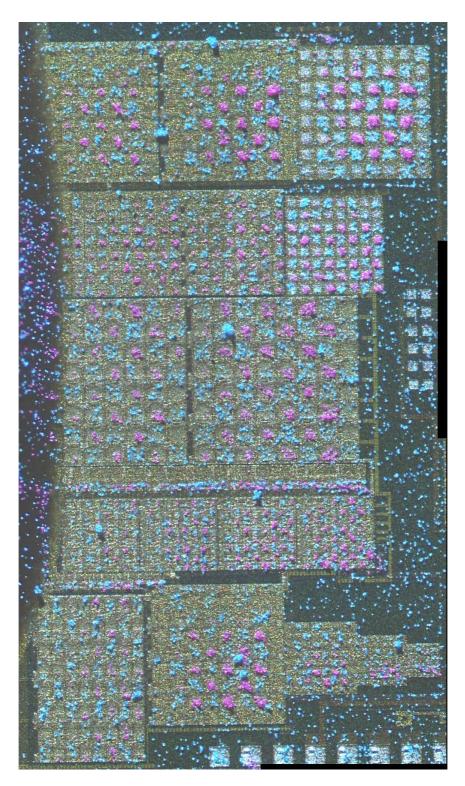

|    | 6.1.       | Überblick   |                    |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 61       |

|    | 6.2.       | Die Pixelf  | elder              |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 62       |

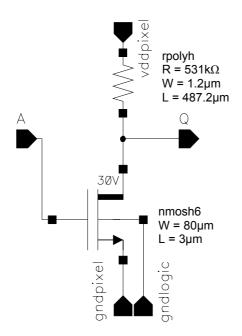

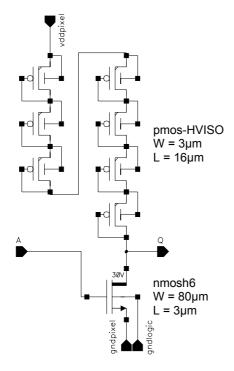

|    |            | 6.2.1. Sc   | haltpixel          |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 62       |

|    |            | 6.2.2. Mu   | ultipolpixel .     |                    | _             |            |      | _    |      | _    |    |   |   |   |   |   | _ | 72       |

|    |            | 6.2.3. Ph   | otopixel           |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 72       |

|    |            | 6.2.4 Ar    | ıfzählung der r    | ealisiert          | en Pi         | <br>xeltv  | nen  | •    |      | •    | ·  | • | • | • | • | • | • | 75       |

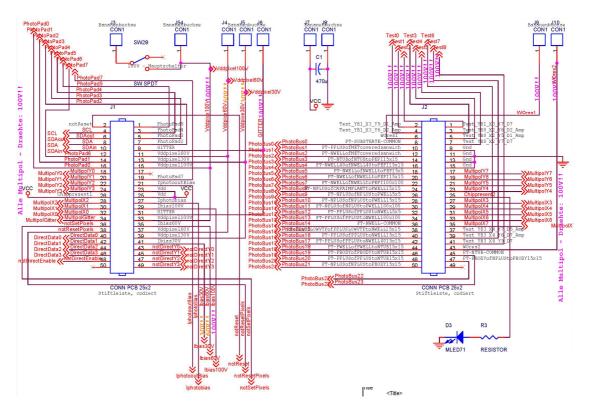

|    | 6.3.       | Der Verso   | rgungs- und A      | nstenern           | inoste        | ril<br>Pil | pen  | •    |      | •    | ٠  | • | • | • | • | • | • | 78       |

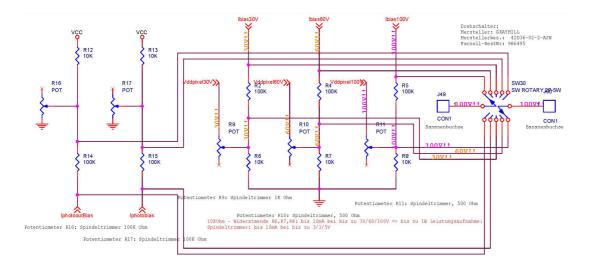

|    | 0.5.       | 631 Re      | ferenzspannun      | insteuer t<br>igen | mgsu          |            | •    | •    |      | •    | •  | • | • | • | • | • | • | 78       |

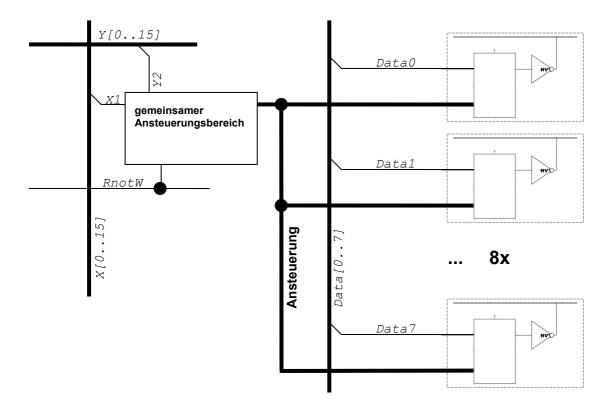

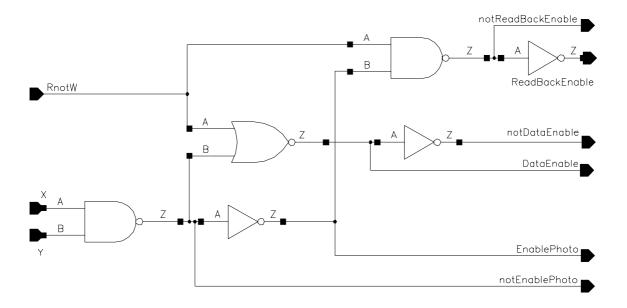

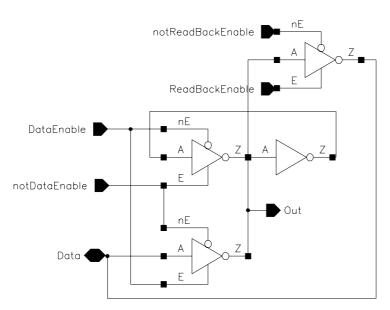

|    |            | 6.3.1. RC   | isteuerung der     | Divolfol           | dor           |            | •    | •    |      | •    | •  | • | • | • | • | • | • | 80       |

|    |            | 6.3.2. Al   | eteengaanaar       | ratärkar           | uei           | • •        | ٠    | •    |      | •    | ٠  | • | • | • | • | • | • | 85       |

|    |            |             | otoausgangsve      |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 85       |

|    | <i>C</i> 1 |             | ondpads            |                    |               |            |      |      |      |      |    |   |   |   |   |   |   |          |

|    | 6.4.       | Teststrukti |                    |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 86       |

|    |            |             | chspannungsti      |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 86       |

|    |            |             | st-Photodioder     |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 86       |

|    |            | 6.4.3. Wa   | asserstoffdetek    | tor                | ٠             |            | •    | •    |      | ٠    | ٠  | ٠ | • | • | • | • | • | 86       |

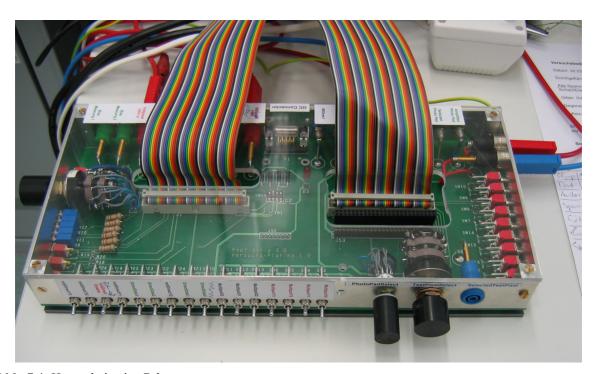

| 7  | Mes        | saufbauten  | Peptidchip 3       |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 87       |

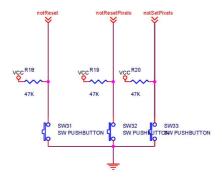

|    | 7.1.       |             | :                  |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 87       |

|    | 7.2.       |             |                    |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 90       |

|    | 7.2.       |             | ertrag             |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 91       |

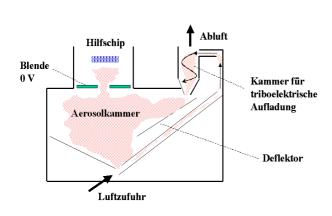

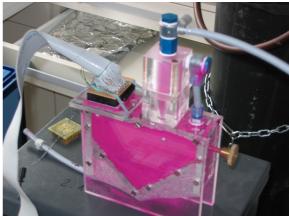

|    | 1.5.       |             | eruag erosolkammer |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 91       |

|    |            |             |                    |                    |               |            |      |      |      |      |    |   |   |   |   |   |   |          |

|    | 7 4        |             | esorption im Lu    |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 91       |

|    | 7.4.       |             | hotodioden un      |                    |               |            | •    | _    |      |      |    |   |   |   |   |   |   | 91       |

|    | 7.5.       | Wassersto   | ffdetektion .      |                    |               |            |      |      |      |      |    |   |   |   |   |   |   | 92       |

| TE | EIL III | ERGE     | BNISSE  | UND D               | ISKUS   | SION  |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   |     |

|----|---------|----------|---------|---------------------|---------|-------|--------|-------|------|------|------|------|-----|------|-----|-----|----|---|---|---|---|-----|

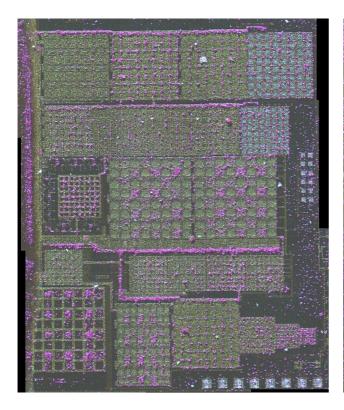

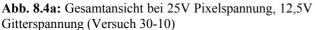

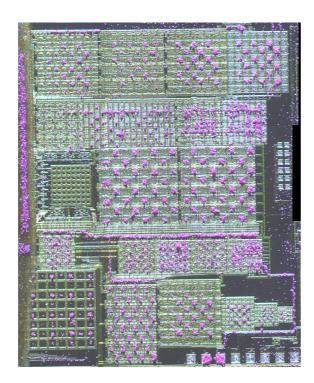

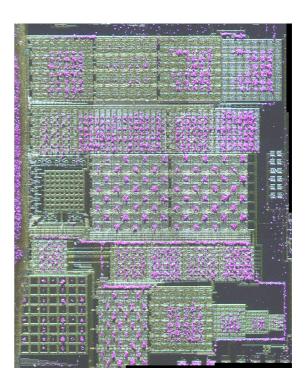

| 8  | Vers    | suche u  | nd Me   | ssunge              | n mit   | dem   | Pept   | idel  | hip  | 3    | •    |      |     |      |     |     |    |   |   |   |   | 9   |

|    | 8.1.    |          | onische | e Tests             |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 9:  |

|    |         | 8.1.1.   | Direk   | te Anst             | eueru   | ng ur | nd Te  | stpiz | xel  |      |      |      |     |      |     |     |    |   |   |   |   | 9:  |

|    |         | 8.1.2.   | Beob    | achtung             | gen zu  | Ausl  | beute  | und   | lΖι  | ıveı | rläs | ssi  | gke | it.  |     |     |    |   |   |   |   | 90  |

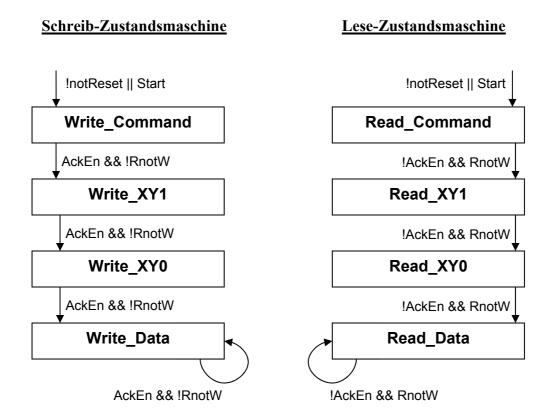

|    |         | 8.1.3.   | Das I   | <sup>2</sup> C-Inte | rface   |       |        |       |      |      |      | . `  |     |      |     |     |    |   |   |   |   | 9′  |

|    |         |          |         | der Hoo             |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 9′  |

|    |         |          |         | oarasitä            |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 9′  |

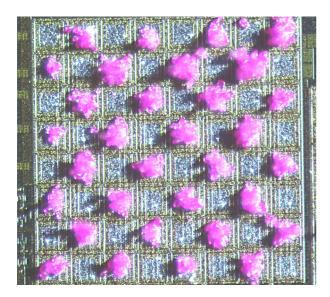

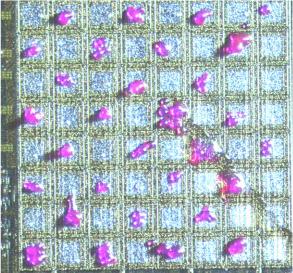

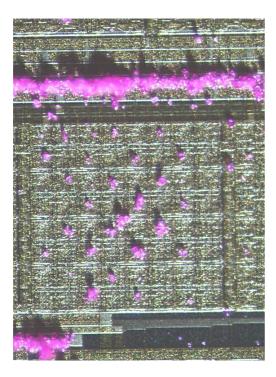

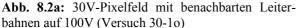

|    | 8.2.    | Unters   | uchung  | des Pa              | artikel | übert | rags   |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 9′  |

|    |         | 8.2.1.   | Einle   | itung               |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 9′  |

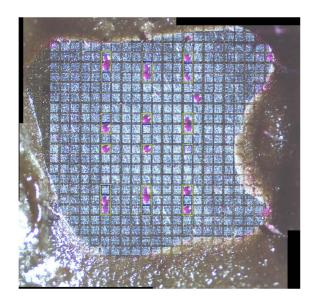

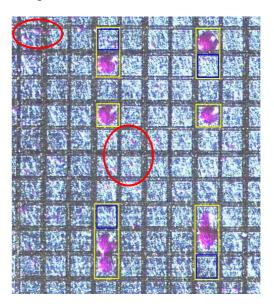

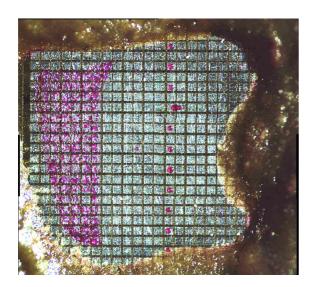

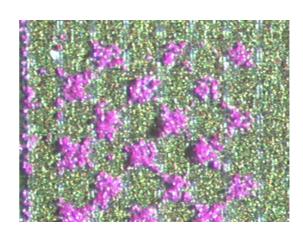

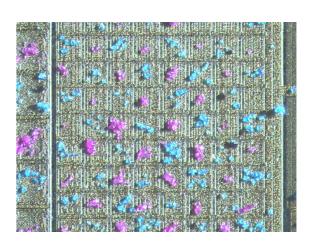

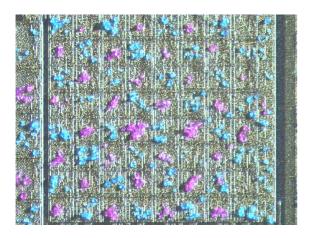

|    |         | 8.2.2.   | Allge   | itung<br>meine      | Festste | ellun | gen .  |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 98  |

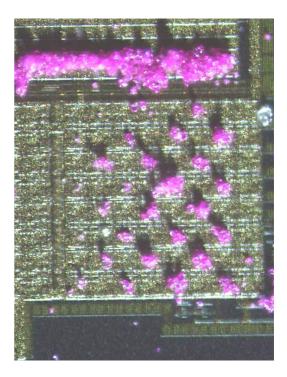

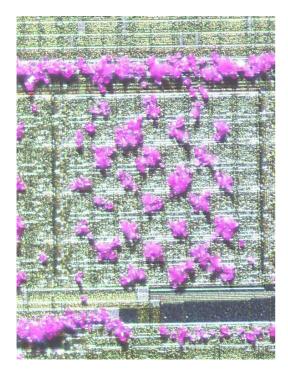

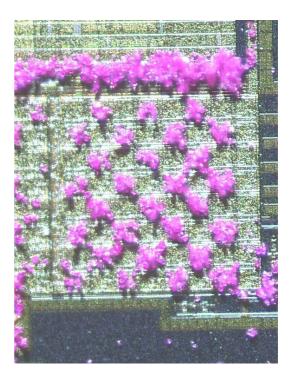

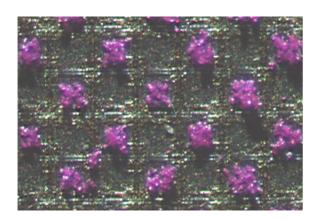

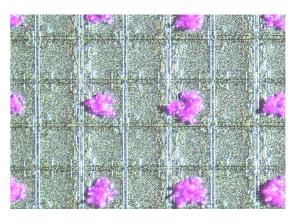

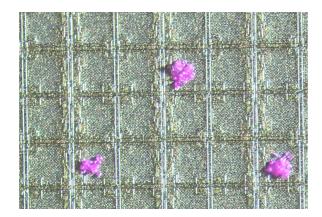

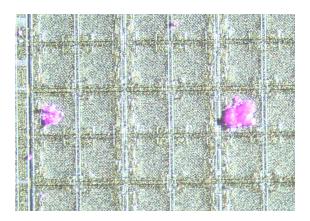

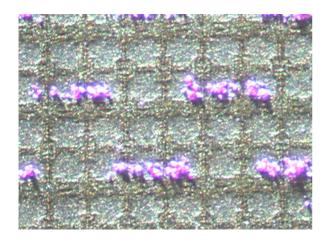

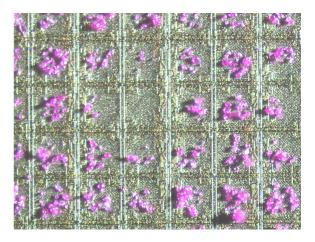

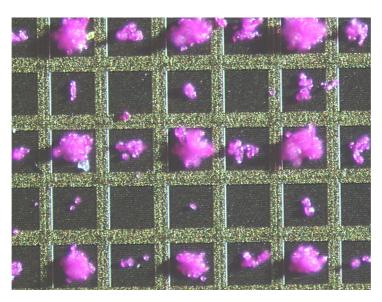

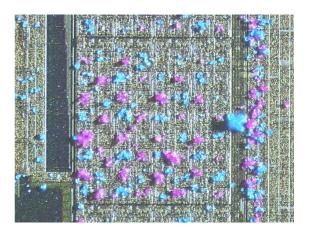

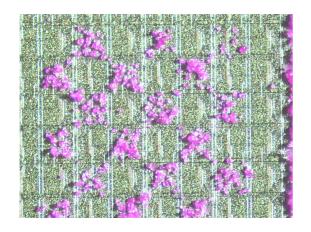

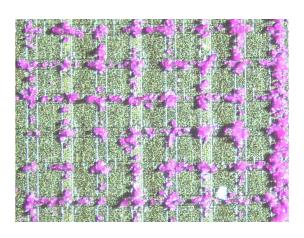

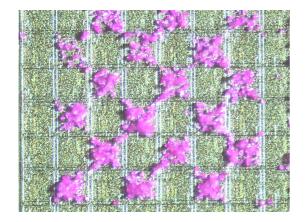

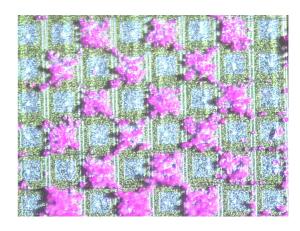

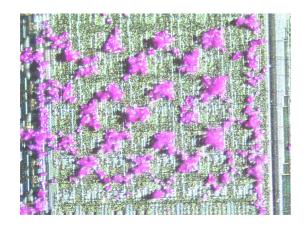

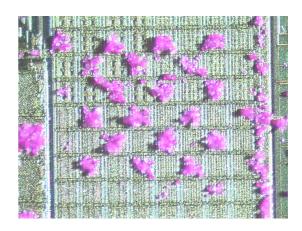

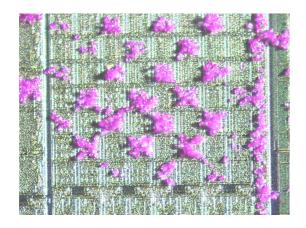

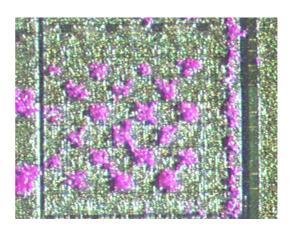

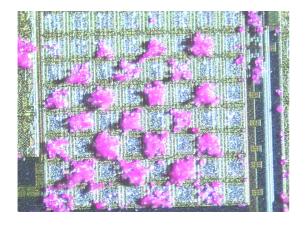

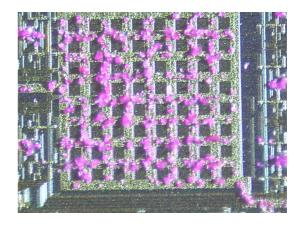

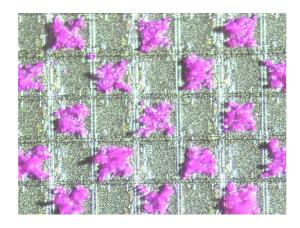

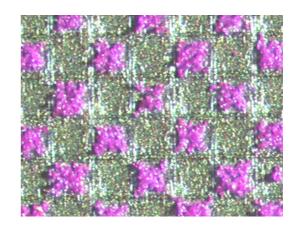

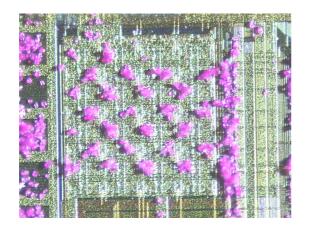

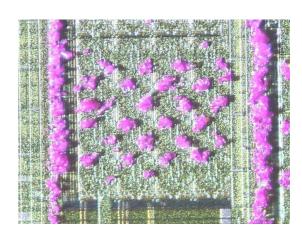

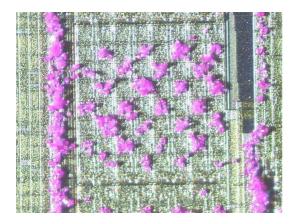

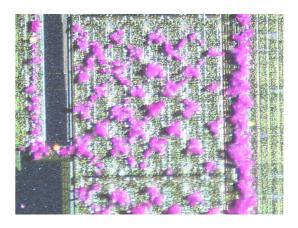

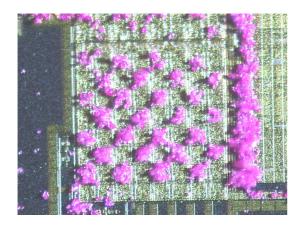

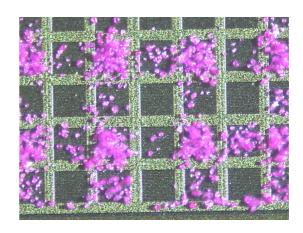

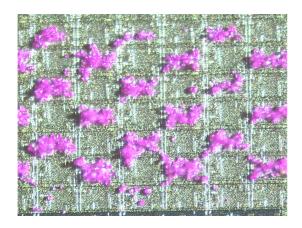

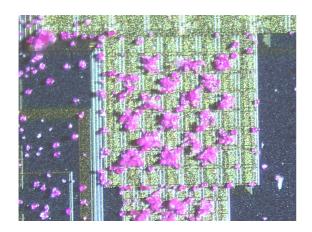

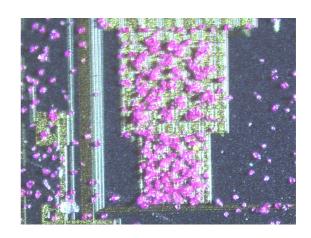

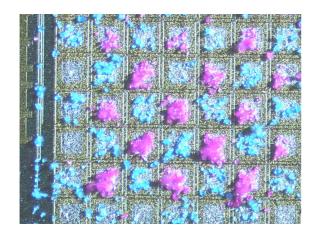

|    |         | 8.2.3.   | Einflu  | ıss von             | Pixels  | größe | e, For | m, S  | Stru | ktu  | r u  | nd   | Gi  | itte | rbr | eit | e. |   |   |   |   | 100 |

|    |         | 8.2.4.   | Einflu  | ıss der             | Pixel-  | und   | Gitte  | rspa  | ınnı | เทช  | _    |      |     |      |     |     |    |   | _ |   |   | 102 |

|    |         | 8.2.5.   | Gitter  | inversi             | on un   | d Bes | schick | ıtun  | gsa  | nor  | nal  | lier | 1   |      |     |     |    |   |   |   |   | 103 |

|    |         |          |         | ıss des             |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 10: |

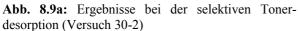

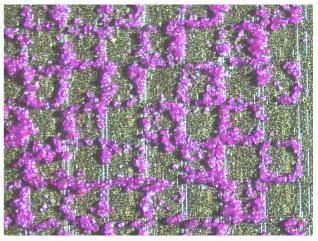

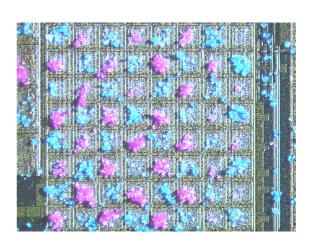

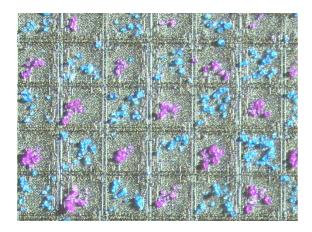

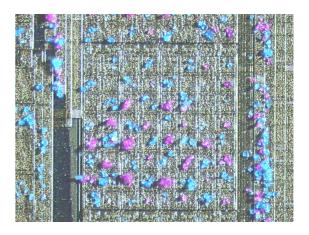

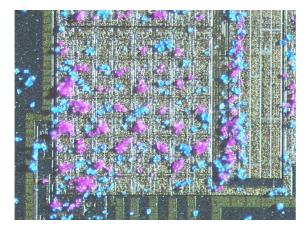

|    |         |          |         | nisse d             |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 108 |

|    |         |          |         | eich zv             |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 109 |

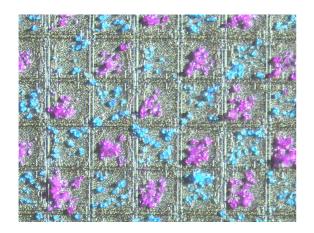

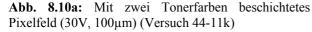

|    |         |          |         | elüberi             |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 110 |

|    |         |          |         |                     | C       |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   |     |

| 9  |         | amment   |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 11. |

|    | 9.1.    | Zusam    | menfa   | ssung d             | ler Erg | gebni | sse .  |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 11  |

|    | 9.2.    | Weiter   | e Arbe  | iten mi             | t dem   | Pept  | idchi  | p 3   |      |      |      |      |     |      |     |     |    |   |   |   |   | 112 |

|    | 9.3.    | Von Po   | eptidch | ip 3 zu             | Pepti   | dchip | 4.     |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 113 |

|    |         |          |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   |     |

| Li | teratı  | ırverzei | ichnis  | • •                 |         |       |        | •     | •    |      | •    | •    | •   | •    | •   | •   | •  | • | • | • | • | 115 |

|    |         |          |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   |     |

| Da | nksa    | gung .   |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 119 |

|    |         | 8****B * | •       |                     |         |       | •      | ·     | •    |      | •    | •    | •   | •    | •   | •   | •  | • | • | • | • |     |

| ۸. | NHÄNO   | O.E.     |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   |     |

|    |         |          |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   |     |

| A1 |         | renzung  |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   |     |

|    |         | roelektr |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 123 |

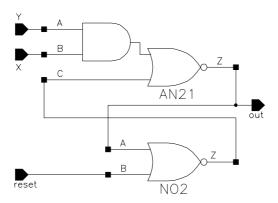

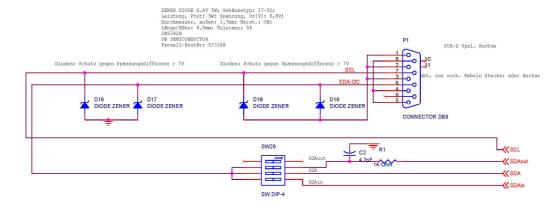

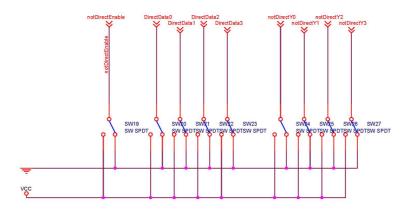

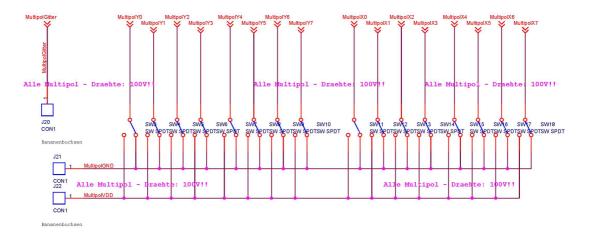

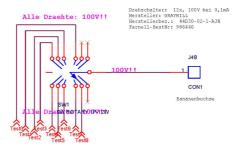

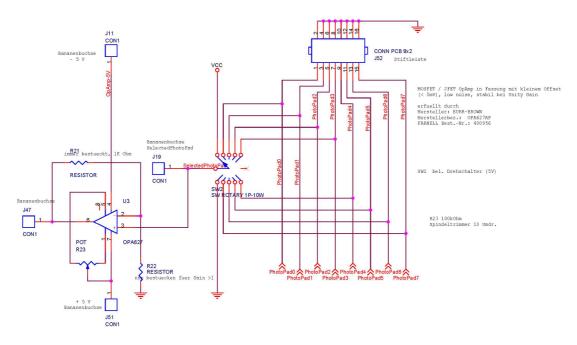

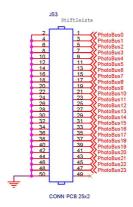

|    |         | altpläne |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 125 |

| A3 |         | ätzliche |         |                     |         |       |        |       |      |      |      |      |     |      |     |     |    |   |   |   |   | 129 |

|    | A3.1    | Zusätz   | liche E | Bilder z            | um To   | nerü  | bertra | ag b  | ei e | inh  | eit  | lic  | her | Sp   | oan | nu  | ng |   |   |   |   | 129 |

|    | A3.2    | 2 Bilder | zum z   | weifarb             | igen T  | one   | übert  | rag   |      |      |      |      |     |      |     |     |    |   |   |   |   | 133 |

#### Einführung

Neben ihrer klassischen Aufgabe als Naturwissenschaft, das menschliche Wissen über die Welt zu mehren, hat die Physik auch schon lange die Aufgabe übernommen, anderen wissenschaftlich-technischen Disziplinen Werkzeuge zur Verfügung zu stellen. Diese dienen sowohl der Gewinnung von Erkenntnis in diesen Disziplinen als auch zum direkten Nutzen für den Menschen.

Gerade in der Medizin und in den Biowissenschaften finden wir zahlreiche Beispiele für Methoden und Geräte, die von der physikalischen Forschung den Weg in die alltägliche Anwendung gefunden haben. Ein inzwischen klassisches Beispiel von vielen ist das physikalische Phänomen der Kernmagnetresonanz, inzwischen routinemäßig eingesetzt in der Medizin als bildgebendes Verfahren im Magnetresonanztomograph (MRT) und in der Biologie zur Strukturbestimmung von Molekülen, besonders bei Proteinen.

Ein anderes Beispiel ist die CMOS-Technologie, durch deren Entwicklung aus der Festkörperphysik die *integrierte Schaltung* (integrated circuit, IC) und damit die Informatik, wie wir sie heute kennen, ermöglicht wurde.

Die CMOS-Technologie wurde seit ihrem Entstehen insbesondere im Hinblick auf ihre Hauptanwendung, schnelle digitale Datenverarbeitung, beständig weiterentwickelt [GEL89]. Zudem wurden neue Anwendungsgebiete durch Erweiterung der Technologie erschlossen:

- die Möglichkeit zu präzisen analogen oder gemischten analog-digitalen Schaltungen (so genannte Mixed-Signal-Schaltungen)

- die Erhöhung der maximal schaltbaren Spannung für Steueranwendungen [BAL99]

- der Einbau von mechanischen Sensoren und Aktuatoren in mikroelektromechanischen Systemen (MEMS), die sich inzwischen zu einer eigenständigen Technologie mit vielen Anwendungen entwickelt haben [MEM04]

Ein zentrales Thema in der biologischen Forschung der vergangenen Jahre war die Entschlüsselung des menschlichen Genoms. Dass dieses Ziel inzwischen weitgehend erreicht ist, verdanken wir aufgrund der großen Menge an zu bearbeitendem Material massiver Automatisierung und Parallelisierung [MÜL04], auch mit Hilfe so genannter "Genchips".

Unser Wissen über biologische Organismen ist damit aber noch lange nicht vollständig: Wir kennen den vollständigen genetischen Text, aber verstehen derzeit nur wenige Bruchteile des Inhalts. Um zum Beispiel den Unterschied zwischen einer Raupe und dem genetisch identischen Schmetterling erklären zu können, muss die Expression der Gene, und damit die von ihnen codierten Proteine betrachtet werden. Aufgrund der Vielzahl der Gene und der Tatsache, dass ein Gen auch mehrere Proteine codieren kann sowie vieler weiterer Effekte,

2 EINFÜHRUNG

werden für die Proteomforschung in gleichem Maße wie für die Genomforschung Werkzeuge benötigt, die für massiv parallele Untersuchungen ausgelegt sind.

Diese Werkzeuge können auch für medizinische Anwendungen eingesetzt werden, besonders für den Nachweis von Antikörpern zur medizinischen Diagnostik, die Suche nach möglichen Wirkstoffen für Medikamente und zur Forschung an Stoffwechselkrankheiten.

Ein Mittel, um solche hohe Parallelität und damit hohen Durchsatz zu erzielen, sind Microarrays, d.h. Träger, auf denen ein regelmäßiges Feld verschiedener Reaktionspartner auf jeweils sehr kleinem, definierten Raum (im µm-Bereich) angeboten werden. DNA-Microarrays verschiedener Techniken sind bereits essenziell für den schnellen und bezahlbaren Vergleich der Genaktivitäten vieler verschiedener Gene. Protein-Mikroarrays stehen trotz kommerzieller Verfügbarkeit einiger erster Produkte noch nicht in dem von der medizinischen und biologischen Forschung gewünschten Maß zur Verfügung.

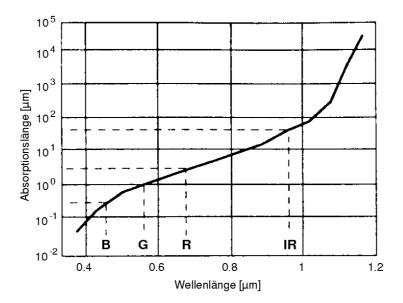

CMOS-Technologie kann Parallelität auf kleinstem Raum ermöglichen. Kleine Strukturgrößen (von wenigen Mikro- bis einigen hundert Nanometern), eine definierte Oberfläche, sowie die Möglichkeit, über elektrische Felder auf geladene Partikel einzuwirken, lassen CMOS-Chips als ideale Grundlage für bestimmte Biochips erscheinen. Zudem könnten Photodioden an den Halbleiterübergängen zur Detektion von optisch markierten Molekülen benutzt werden.

Um einen Biochip auf CMOS-Basis zu entwickeln, sind Kenntnisse in vielen verschiedenen Bereichen erforderlich. Im Falle des Peptidchip-Projekts, in dessen Rahmen die vorliegende Arbeit entstanden ist, verfügt das Deutsche Krebsforschungszentrum (DKFZ), Abteilung Chipbasierte Peptidbibliotheken, (in Kooperation mit dem Institut für Physikalische Chemie, Universität Heidelberg) über die benötigten Kenntnisse und Ressourcen im Bereich der Biochemie und Oberflächenchemie. Das Kirchhoff-Institut für Physik, Lehrstuhl für Technische Informatik und das ASIC-Labor der Universität Heidelberg bringen die nötigen Kenntnisse und Ressourcen für den Entwurf mikroelektronischer Schaltungen und in der Nutzung von CMOS-Technologie sowie physikalische Kenntnisse ein. Insbesondere die Physik des Übertrags von Partikeln auf CMOS-Chips als aktive Träger erweist sich als überaus anspruchsvoll, so dass dieser Bereich als eines der Hauptthemen einer eigenständigen physikalischen Promotionsarbeit behandelt wird [NES04].

Diese Diplomarbeit konzentriert sich auf die mikroelektronischen Herausforderungen des Peptidchip-Projekts und behandelt in diesem Rahmen folgende Themen:

- Konzeption und Entwurf eines ASICs zur Untersuchung der ortsgenauen Ablagerung von Partikeln im elektrischen Feld

- Implementierung von Strukturen zur Erforschung von Möglichkeiten zum optischen Nachweis markierter Biomoleküle auf demselben ASIC

- Entwicklung einer Schnittstelle für die Programmierung und Auslese des Chips. Diese Schnittstelle soll bereits dafür ausgelegt sein, mit nur geringen Modifikationen auch spätere Peptidchips mit einer viel größeren Anzahl Pixel anzusteuern

- Testaufbauten und erste Test des Chips, insbesondere:

- Vermessung der Qualität der Tonerablagerung in Abhängigkeit von den Pixeleigenschaften

- Entwicklung von Messaufbauten, die im Rahmen zukünftiger Arbeiten zur Charakterisierung der elektrischen und optischen Eigenschaften des verwendeten Hochspannungs-CMOS-Prozesses eingesetzt werden

Entsprechend wurde ein Testchip entwickelt, mit dem die wesentlichen Parameter eines Peptidarray-Synthesechips mit Nachweismöglichkeit für bindende Biomoleküle systematisch erforscht werden können. Dieser Chip ermöglicht es, ein Optimum dieser Parameter für einen zukünftigen, anwendungsreifen Peptidchip zu bestimmen.

Erste Versuche, insbesondere zur Beschichtung mit geladenen Partikeln, wurden an diesem Chip bereits im Rahmen der vorliegenden Arbeit durchgeführt. Eine vollständige Vermessung aller Teststrukturen dieses Chips wird zusammen mit der Entwicklung des produktiven Nachfolgechips einer zukünftigen Arbeit vorbehalten bleiben.

# TEIL I METHODEN UND GRUNDLAGEN

#### 1. Biologie der Aminosäuren, Bioarrays, Biochips

#### 1.1 Aminosäuren, Peptide, Proteine

#### 1.1.1 Biochemische Einordnung

*Proteine* sind neben Nukleinsäuren, Lipiden und Polysacchariden eine der wichtigsten Gruppen der in Lebewesen vorkommenden Biopolymere. Von diesen vier Gruppen sind die Proteine nach heutiger Lehrmeinung am vielseitigsten.

Proteine haben unter anderem folgende Funktionen [ALB99-1]:

- Enzyme katalysieren und regulieren chemische Reaktionen.

- Sensorproteine (z.B. Rhodopsin) wandeln Reize um.

- Strukturproteine (z.B. Actin, Tubulin, Keratin) geben Form.

- Transportproteine erlauben den Transfer von Molekülen durch Zellmembranen (z.B. Poren und Kanäle).

- Motorproteine (z.B. Myosin, Kinesin) ermöglichen Bewegung.

- Fluoreszente Proteine (z.B. Green Fluorescent Protein) strahlen Fluoreszenzlicht aus.

Proteine interagieren selektiv mit anderen Molekülen. Zudem können sie ihren räumlichen Aufbau (Konformation) ändern, was wiederum die Möglichkeiten ihrer Interaktion mit anderen Molekülen verändern oder auch eine Kraft auf andere gebundene Moleküle ausüben kann.

#### 1.1.2 Aminosäuren und die Peptidbindung

Um die enorme Vielfalt an Funktion der Proteine ansatzweise erklären zu können, empfiehlt es sich, die Struktur und den chemischen Aufbau dieser Polymere näher zu betrachten.

Bei Proteinen handelt es sich um lineare *Heteropolymere*<sup>1</sup> oder um Komplexe aus mehreren identischen oder unterschiedlichen linearen Heteropolymeren mit anderen Molekülen oder Ionen. Die Monomere dieser Heteropolymere sind die *Aminosäuren*. Sie verfügen alle über eine Aminogruppe (mit Ausnahme von Prolin, das stattdessen über eine Iminogruppe verfügt) und eine Karbonsäuregruppe. Diese beiden chemischen Gruppen sind über ein Kohlenstoffatom verbunden, an dem auch eine so genannte Seitenkette, auch Rest genannt, mit weiteren chemischen Gruppen gebunden ist (Abb. 1.1).

<sup>&</sup>lt;sup>1</sup> Heteropolymere sind Polymere, die aus verschiedenen Monomeren zusammengesetzt sind.

$$\begin{array}{c|cccc}

H & R & & \bigcirc \\

& | & | & | & \bigcirc \\

H & N - C - C & \bigcirc \\

& | & | & | & \bigcirc \\

H & H & H

\end{array}$$

**Abb. 1.1:** Chemische Grundstruktur der Aminosäuren (bei pH 7): Aminogruppe links, Karbonsäuregruppe rechts, Seitenkette in der Mitte (R)

Proteine werden in der Natur fast ausschließlich aus den zwanzig *biogenen Aminosäuren* aufgebaut. Die biogenen Aminosäuren werden nach den chemischen Eigenschaften ihrer Seitenketten in vier Familien unterteilt:

- saure Aminosäuren

- basische Aminosäuren

- ungeladen polare Aminosäuren

- unpolare Aminosäuren

Weiterhin unterscheiden sich die Seitenketten in ihrer Länge, im Verzweigungsgrad und in den vorhandenen funktionalen Gruppen. Die chemischen Eigenschaften der Seitenketten decken also ein weites Spektrum ab, was zu der enormen Vielseitigkeit der Proteine beiträgt.

Zur Polymerisierung von Aminosäuren kommt es bei der chemischen Reaktion unter Abspaltung von Wasser zwischen der Aminogruppe und der Karbonsäuregruppe zweier Aminosäuren. Die entstehende Bindung wird Peptidbindung genannt, das entstehende Molekül wird als Peptid bezeichnet. Es verfügt über eine freie Aminogruppe an einem Ende der Kette (dem N-Terminus) und einer Karbonsäuregruppe am anderen Ende (dem C-Terminus). In lebenden Organismen katalysieren spezielle Molekülkomplexe, die *Ribosomen*, die Reaktionen der Peptidsynthese. Dabei wird die genaue Abfolge der verschiedenen Aminosäuren von einem weiteren Biopolymer, der *mRNA*<sup>1</sup>, bestimmt. Diese bildet mit dem Ribosom und dem entstehenden Peptid vorübergehend eine Einheit<sup>2</sup>. Die mRNA wiederum wird speziell aus der DNA erzeugt, um als Beschreibung oder Blaupause für die Biosynthese eines Proteins zu dienen, sozusagen als "Arbeitskopie" eines Gens.

#### 1.1.3 Von der Peptidbindung zum Protein

Die typische Länge der Polypeptidkette eines Proteins beträgt etwa 300 Aminosäuren, aber dieser Wert kann für spezielle Proteine auch stark abweichen. Die Abfolge der Aminosäuren in dieser Polypeptidkette wird als *Primärstruktur* des Proteins bezeichnet.

<sup>&</sup>lt;sup>1</sup> Messenger Ribonucleic Acid oder Boten-Ribonukleinsäure

<sup>&</sup>lt;sup>2</sup> Tatsächlich können auch mehrere Ribosomen gleichzeitig eine mRNA – jeweils an verschiedenen Stellen – ablesen.

Abhängig von der genauen Sequenz können Teilbereiche eines Proteins die Eigenschaft haben, dass sich dort die Aminosäuren in einer  $\alpha$ -Helix<sup>1</sup>, einem  $\beta$ -Faltblatt<sup>2</sup> oder anderen wiederkehrenden Strukturen anordnen. Diese Elemente bilden die Sekundärstruktur des Proteins.

Als *Tertiärstruktur* bezeichnet man die stabile Konformation, in die die Aminosäurekette sich schließlich faltet. Diese liegt an einem Energieminimum im Raum aller möglichen räumlichen Anordnungen der Aminosäurekette. Eine treibende Kraft sind hierbei die hydrophoben Wechselwirkungen zwischen den unpolaren Seitenketten, die im wässrigen Medium der Zelle dann meist im Inneren des Proteins enden. Verschiedene Proteine unterstützen diesen Faltungsvorgang. Mit Ausnahme von Disulfidbrücken wird die Struktur eines Proteins fast ausschließlich über nicht kovalente Bindungen wie hydrophobe Wechselwirkung, Ionenbindung, Wasserstoffbrücken und Van-Der-Waals-Wechselwirkungen vermittelt.

Jeder Teilbereich eines Proteins, dessen Aminosäurekette sich unabhängig vom Rest der Aminosäurekette in eine solche stabile Konformation faltet, wird als *Domäne* bezeichnet. Eine Proteindomäne besteht üblicherweise aus zwischen 50 und 350 Aminosäuren.

Besteht ein Protein aus mehreren Aminosäureketten und/oder anderen Bestandteilen, so bezeichnet man die räumliche Anordnung dieser Bestandteile zueinander als *Quartärstruktur*.

Besondere Bedeutung kommt bei fast allen Proteinen den Aminosäuren auf der Oberfläche zu, da diese mit anderen Molekülen interagieren und insbesondere auch hochspezifische Bindungstaschen für andere Moleküle ausbilden können. Als *Epitope* bezeichnet man die kurzen Anordnungen von Aminosäuren, die für diese hochspezifischen Bindungsstellen genutzt werden. Vermittelt wird die bindende Wechselwirkung meist nicht durch kovalente Bindungen, sondern durch Wasserstoffbrücken, elektrostatische oder hydrophobe Wechselwirkungen, Van-der-Waals-Kräfte und natürlich *sterische Effekte*<sup>3</sup> zwischen den Moleküloberflächen.

Kürzere lineare Polypeptide werden einfach als *Peptide* bezeichnet. In Organismen kommen auch viele Peptide mit biologischer Funktion vor, wie zum Beispiel Signalpeptide.

#### 1.1.4 Peptidsynthese im Labor

Für Laboranwendungen ist es inzwischen ein etabliertes Verfahren zur Produktion von Peptiden und Proteinen, mit den Methoden der Gentechnologie die Erbinformation von Mikroorganismen gezielt so zu verändern, dass diese das gewünschte Molekül auf dem üblichen Weg biosynthetisieren. Werden geeignete Lebensbedingungen in einem Bioreaktor zur Verfügung gestellt, können sich diese Organismen so weit vermehren, bis sie in ausreichender Anzahl vorhanden sind, um die gewünschte Menge des Moleküls zu produzieren. Danach werden die Organismen abgetötet, und das Protein wird mit verschiedenen chemischen und physikalischen Methoden aus den anderen Bestandteilen der

<sup>&</sup>lt;sup>1</sup> rechtsdrehend schraubenförmige Anordnung, mit den Seitenketten nach außen

<sup>&</sup>lt;sup>2</sup>einer Ebene aus mehreren parallelen geraden Strängen von Aminosäuren, deren Seitenketten jeweils im Wechsel über und unter die Ebene zeigen

<sup>&</sup>lt;sup>3</sup> sterische Effekte sind, vereinfacht gesagt, Auswirkungen der Tatsache, dass ein Bereich im Raum nur von einem Atom eingenommen werden kann, und dass dadurch die verschiedenen Bereiche der Ketten sich gegenseitig in den ihnen möglichen Bewegungen einschränken.

Organismen abgetrennt. Dieser Weg zur Erzeugung von Peptiden ist sehr aufwändig, vor allem wenn sehr viele verschiedene kurze Peptide isoliert erzeugt werden sollen.

Einfachere Verfahren zur Synthese von Peptiden im Labor wurden also gesucht. Die Hauptschwierigkeit hierbei lag in der Tatsache begründet, dass beim direkten Mischen von Peptiden im Reagenzglas zyklische Dipeptide entstehen. Erstmals 1881 wurde mit der *Azid-Methode* von Th. Curtius ein Verfahren entwickelt, das mit Hilfe von Schutzgruppen den Aufbau eines linearen Polypeptids ermöglichte [JAK73]. Die Verwendung von Schutzgruppen erlaubt es, in einem einfachen Laboraufbau Proteine wie in lebenden Zellen schrittweise aufzubauen. Basierend auf dem Konzept der Verwendung von Schutzgruppen wurden weitere Verfahren zur Peptidsynthese entwickelt.

Das erste technisch nutzbare Verfahren war die 1963 von R. B. Merrifield entwickelte Festphasen-Peptidsynthese [MER63]. Bei diesem Verfahren und den darauf aufbauenden Verfahren werden Aminosäuren einer Sorte mit der Karbonsäuregruppe an einen Träger gekoppelt. Die Aminogruppe dieser Aminosäuren ist frei und somit reaktionsfähig. Danach werden Aminosäuren zugegeben, deren Aminogruppe durch Bindung mit einer chemischen Gruppe reaktionsunfähig gemacht wurde. Somit können diese mit den schon am Träger gebundenen Aminosäuren reagieren und eine Peptidbindung bilden. Danach ist aber zunächst wegen der Schutzgruppe keine weitere Reaktion möglich. Überzählige Aminosäuren werden nun abgewaschen, so dass nur die gebundenen Peptide, mit der Schutzgruppe am N-Terminus verbleiben. Die Schutzgruppe ist so gewählt, dass sie sich zuverlässig durch Zugabe geeigneter Reagenzien abspalten lässt. Da diese Schutzgruppe nach jedem Reaktionsschritt entfernt wird, bezeichnet man sie auch als transiente Schutzgruppe. Bei der ursprünglichen Merrifield-Synthese wird hierfür eine Carbobenzoxy-Gruppe verwendet, die mit Hilfe von Wasserstoffbromid entfernt wird. Ein schonenderes Verfahren verwendet als Schutzgruppe eine FMOC-Gruppe und zur Abspaltung eine milde Base, in der Regel Piperidin.

Da die Seitenketten einiger Aminosäuren Karbonsäure- oder Aminogruppen enthalten, müssen auch diese mit Schutzgruppen blockiert werden. Diese *permanenten Seitenkettenschutzgruppen* dürfen allerdings erst nach Abschluss der gesamten Peptidsynthese entfernt werden. Sie müssen daher stabil gegen das Reagenz sein, das zur Entfernung der Schutzgruppen der Hauptkette verwendet wird, sich aber mit einem anderen Reagenz, oft einer starken Säure wie Trifluoressigsäure, abspalten lassen.

Mit der Festphasen-Peptidsynthese lassen sich zuverlässig Peptidketten von, je nach Verfahren und Peptid, maximal 15-35 Monomeren herstellen. Längere Peptidketten herzustellen ist schwierig, da benachbarte Peptidketten auf dem Träger bei diesen Kettenlängen beginnen können, miteinander in Kontakt zu geraten und je nach Seitenketten auch sich zu Aggregaten zusammenzulagern. Weiterhin werden bei langen Peptidketten sehr gute Umsetzungsraten für jeden einzelnen Kopplungsschritt nötig, um noch einen akzeptablen Anteil des gewünschten Peptids zu erhalten. Auf diese Problematik wird in Abschnitt 1.2.3.1 eingegangen.

\_

<sup>&</sup>lt;sup>1</sup> 9-<u>F</u>luorenyl<u>methyloxycarbonyl</u>

#### 1.2 Bioarrays und Biochips

#### 1.2.1 Der Begriff des Biochips

Wenn von "Genchips", "DNA-Chips", "Proteinchips" oder allgemein "Biochips" die Rede ist, wird der Begriff des Chips anders verwendet als in der Halbleiterphysik. Trotzdem hat dieser Begriff in beiden Bereichen die gleiche Wurzel: In der englischen Sprache steht "*Chip*" zunächst ganz allgemein für einen kleinen, handlichen Träger.

So sind *Halbleiterchips* Träger von elektronischen Bauelementen oder ganzen integrierten Schaltungen. Sie sind durch Verwendung eines Gehäuses um den Halbleiterkristall oder andere Techniken zu dessen Schutz handhabbar und von außen elektrisch kontaktierbar. So können sie von außen gestellte Anforderungen erfüllen. Auf Halbleiterchips wird in Kapitel 2 näher eingegangen.

Biochips werden als handliche Träger biologisch relevanter Moleküle an ihrer Oberfläche definiert [MÜL04-1]. Reaktionspartner können mit den an der Oberfläche fixierten Molekülen in Kontakt gebracht werden und Bindungswechselwirkungen zwischen den gebundenen Molekülen auf dem Chip und dem Reaktionspartner können nachgewiesen werden. Biochips existieren als Träger nur einer funktionalen Gruppe pro Chip oder als Träger eines ganzen Bioarrays. Sie sind konzipiert um mit einem System zur Auswertung der Bindungsereignisse zusammenzuarbeiten und können Teile dieses Auswertungssystems mit auf dem Träger unterbringen. Biochips können je nach Anforderungen aus sehr verschiedenen Materialien bestehen. Viele Biochips sind keine Halbleiterchips.

Protein- oder Peptidchips mit nur einer Sorte chemischer Gruppen pro Chip sind für einige Anwendungen gut geeignet und bereits weit verbreitet [KAM05-1]. Für viele Anwendungen ist es dagegen essenziell, die Wechselwirkung einer Substanz mit einer Vielzahl von verschiedenen Bindungspartnern möglichst schnell und kostengünstig zu testen. Um dieses Ziel zu erreichen bietet sich Parallelisierung an, also viele Tests in einem Arbeitsablauf gleichzeitig durchzuführen. Bei einem Weg dies zu erreichen, werden die Bindungspartner in Form von zweidimensionalen Feldern (in der biologischen Anwendung mit dem englischen Ausdruck "Arrays" bezeichnet) auf einen Träger aufgebracht. Diese Felder bestehen aus einer zweidimensionalen regelmäßigen Anordnung von verschiedenen Bindungsstellen mit verschiedenen Molekülen. Ausreichend miniaturisiert und auf einen Träger integriert lassen sich viele Bindungsstellen auf kleinem Raum als *Microarray* zusammenfassen. Solche Arrays sind immer aus Punkten identischer Bindungsstellen definierter Größe in regelmäßiger Anordnung aufgebaut. Die Bindungsstellen werden dann mit verschiedenen Molekülen beladen. In der biologischen Anwendung, vor allem bei Druckverfahren, werden diese Punkte "Spots" genannt. Mit geeignetem Werkzeug wie Vielfachpipetten, Pipetierrobotern und automatisierter Auswertung lassen sich so tausende von Bindungsexperimenten parallel in nur einem Arbeitsgang durchführen. Insbesondere im Bereich der Gen- oder DNA-Mikroarrays und "Genchips" sind hier in den vergangenen Jahren große Durchbrüche erzielt worden.

Seit der erfolgreichen Auslese und Niederschrift des menschlichen Genoms hat sich das Interesse unter anderem zu den Proteinen verschoben. Denn um zu verstehen, wie ein Organismus funktioniert, genügt es nicht, zu wissen welche Proteine durch welche Gene codiert werden. Die Wechselwirkung der Proteine untereinander und mit anderen Biomolekülen muss verstanden werden. Peptide bieten hier einen Ansatzpunkt, weil Proteine sich durch Peptide repräsentieren lassen: Peptidketten, die in ausreichendem Maß überlappend die gesamte Aminosäuresequenz des Proteins abbilden, geben dessen Primärstruktur für viele

Zwecke gut genug wieder. Bindungsstellen an Proteinen mit komplexen Bindungstaschen dagegen lassen sich mit dieser Technik nicht so einfach abbilden, da hier die Tertiärstruktur die Bindungseigenschaften bestimmt: Die Bindungstasche wird hier aus den Seitengruppen von Aminosäuren an verschiedenen, auch weit voneinander entfernt liegenden Stellen der Aminosäuresequenz gebildet. Zudem ist die exakte räumliche Anordnung, also die Tertiärstruktur und Quartärstruktur der Aminosäuren von großer Bedeutung, und diese wird erst durch das vollständige Protein vermittelt. Trotzdem können entsprechend angepasste Peptide auch hier Anhaltspunkte liefern.

#### 1.2.2 Anwendungen von Peptidarrays

#### 1.2.2.1 Antikörpernachweis

Ein in der Medizin üblicher Weg zur Diagnose von vielen Infektionskrankheiten ist der Nachweis von Antikörpern gegen einen Erreger im Blut des Patienten. Die hierfür bisher üblichen Methoden sind jedoch recht teuer und materialaufwändig. Hier kann ein Peptidchip ein kompakteres Format bieten, insbesondere wenn im Rahmen der Diagnostik auf mehrere Moleküle gleichzeitig getestet werden soll.

Für jeden Antikörper muss für diese Anwendung zunächst ein möglichst spezifisches Muster von bindenden und nicht bindenden Peptiden gefunden werden. Die für dieses spezifische Bindungsmuster nötigen Peptide werden dann zu einem Array zusammengefasst. Dieses Array kann nun beliebig oft reproduziert werden und steht dann für zukünftige Tests zur Verfügung.

Für viele Tests würde sogar ein einzelnes, sehr spezifisches Peptid ausreichen, das in einem einfachen Test ohne Arraytechnologie Verwendung finden könnte. Allerdings muss ein solches hochspezifisches Peptid erst einmal gefunden werden, und bei dieser Suche müssen wiederum viele Kandidaten untersucht werden – erneut ein Anwendungsgebiet für Peptidarrays.

Um das Blut eines Patienten zu testen, wird es (verdünnt) auf ein Array des für den Test benötigten Typs aufgebracht, die Bindungsereignisse werden ausgewertet, indem nach dem Muster oder den Mustern auf dem Chip gesucht wird.

#### 1.2.2.2 Peptid-Protein-Bindungen

Die für den Antikörpernachweis beschriebene Methode lässt sich auch auf andere Proteine verallgemeinern. Zum Beispiel könnten sich so Oberflächenproteine von Viren oder anderen Krankheitserregern nachweisen lassen. Medikamente, die diese Proteine inaktivieren, können mit Hilfe der Arraytechnologie gesucht und gefunden werden.

Eine andere medizinische Anwendung ist die systematische Suche nach Wirkstoffen auf Peptidbasis, die an Krankheitserreger oder auch an Krebszellen binden. Damit könnten schneller und leichter Stoffe gefunden werden, die Krankheitserreger inaktivieren, indem zum Beispiel bei Viren die Bindungsstelle für den Eintritt in Zellen gestört wird. Auch könnten zellschädigende Stoffe gezielt an auszuschaltende Zellen wie Krebszellen gebunden werden.

Weiterhin lässt sich mit Hilfe von Peptidarrays auch biologische Grundlagenforschung treiben, indem man qualitativ die Bindung zwischen Peptiden und Peptidsequenzen aus Proteinen zu anderen Proteinen untersucht. So lässt sich zum Beispiel nachweisen, welche

Region eines auf dem Array abgebildeten Proteins mit einem anderen, in Lösung zugegebenen Proteins wechselwirkt.

#### 1.2.2.3 Peptide als Katalysatoren

Proteine haben, besonders in Verbindung mit Metallatomen, in lebenden Organismen oft die Eigenschaft, als *Katalysator* bestimmte chemische Reaktionen durch Herabsetzung der Aktivierungsenergie stark zu beschleunigen (z.B. Metalloproteinasen). Für die chemische Industrie sind maßgeschneiderte Katalysatoren, die dort gewünschte Reaktionen beschleunigen, von großem Wert. Ein besonders wertvolles, aber noch nicht nachgewiesenes Beispiel hierfür wäre ein Enzym, das die Reaktion von Wasser zu Wasserstoff und Sauerstoff unter Energiezufuhr durch Licht katalysiert.

Komplexe Proteine sind schwierig zu synthetisieren – eigentlich sind sie nur durch aufwändige Extraktion aus gezüchteten genetisch veränderten Mikroorganismen zu gewinnen. An Oberflächen fixierte Peptide dagegen wären einfach herzustellen und zu handhaben. Jedoch müssen dafür zunächst geeignete Peptidsequenzen, eventuell mit daran gebundenen Metallatomen, gefunden werden. Peptidarrays bieten eine Möglichkeit, viele kurze Sequenzen parallel auf katalytische Aktivität zu testen. Allerdings wäre es hierzu nötig, möglichst ortsgenau und spezifisch einen Anstieg der Konzentration der gewünschten Reaktionsprodukte auf dem Array nachzuweisen. Gerade der Nachweis von Wasserstoff kann mit Verfahren, die auf der Veränderung der optischen oder elektrischen Eigenschaften von dünnen Metalloxidfilmen unter Wasserstoffeinwirkung basieren, erzielt werden. In den Abschnitten 5.3.4 und 6.4.3 wird hierauf näher eingegangen.

#### 1.2.3 Anforderungen an Peptidarrays und Stand der Technik

#### 1.2.3.1 Anzahl der Aminosäuren pro Peptid

Die Kettenlänge der auf einem Punkt des Arrays angebotenen Peptide ist eine wichtige Größe, um den Wert des Arrays für die Anwendung zu bestimmen. Längere Peptidketten erlauben größeren Überlapp für die Darstellung eines Proteins in Peptidketten. Alternativ können längere Peptidketten untersucht werden für Peptid-Protein-Wechselwirkungsexperimente oder bei der Suche nach peptidischen Katalysatoren. Daher ist es wünschenswert, möglichst lange Peptidketten erzeugen zu können. Stand der Technik bei der Festphasen-Peptidsynthese sind maximale Kettenlängen von 15 bis 35 Aminosäuren, sequenzabhängig auch länger.

Limitierender Faktor ist hierbei die Chemie: Jede einzelne Reaktion, bei der eine weitere Aminosäure an das Ende der Peptidkette gekoppelt wird, hat nur eine endliche Effizienz. Diese Kopplungseffizienz hängt stark von der Sequenz ab. Der Grund hierfür sind sterische Effekte zwischen dem Peptid und der neuen Aminosäure. Einige der Peptidketten auf einem Spot werden also fehlende Aminosäuren aufweisen und dementsprechend anders binden. Diese unerwünschten Peptide können das Ergebnis des Bindungsexperiments verfälschen. Daher muss ihr Anteil an der gesamten Peptidbeladung des Spots minimiert werden.

Der Anteil K der korrekten Peptide der Länge n auf einem Spot errechnet sich aus den Kopplungseffizienzen  $E_i$  der insgesamt n Kopplungsschritte<sup>1</sup> zu

$$K = \prod_{i=1}^{n} E_i . \tag{F1.1}$$

Für konstante Kopplungseffizienz E können wir dies nähern als

$$K = E^n . (F1.2)$$

Diese Näherung ist nur zulässig, wenn sterisch behinderte Aminosäuresequenzen bekannt sind und vermieden werden, für solche Peptide die Kopplungseffizienz stark verringert ist. Für eine erstrebenswerte Peptidkettenlänge von n=15 würde aber selbst eine 95%-ige Kopplungseffizienz nur einen Anteil von etwa 46% korrekten Peptidketten ergeben. Da allerdings alle anderen Peptidketten nur in jeweils sehr kleinen Anteilen vorkommen, wäre selbst ein Spot mit diesem Anteil an korrekten Peptiden noch sehr gut verwendbar.

#### 1.2.3.2 Anzahl der Peptide pro Chip

Eine wichtige Frage bei der Entwicklung von Arrays ist, wie viele verschiedene Felder dieses Array minimal zur Erfüllung der Aufgabe und im besten Falle zur Verfügung stellen sollte. Dabei hängt es stark von der Anwendung ab, wie viele verschiedene Peptide in einem Array benötigt werden.

Grundsätzlich ist natürlich wünschenswert, möglichst viele Peptide auf einem Array unterbringen zu können – vor allem für die "ungezielten" Anwendungen in der Proteomforschung oder die Suche nach Katalysatoren. Will man zum Beispiel das menschliche Proteom von etwa 40.000 Proteinen (bestehend aus im Mittel 500 Aminosäuren) aus 15-meren Peptiden mit 10 Aminosäuren Überlappung abbilden, benötigt man dafür schon 4.000.000 verschiedene Peptide im Array.

Will man gar alle denkbaren Sequenzen biogener Aminosäuren – ohne Berücksichtigung sterischer Behinderungen – untersuchen, so ergeben sich bei Kettenlänge n dann  $20^n$  mögliche Peptide – für n = 6 sind das  $6,4 * 10^7$ , für n = 15 bereits über  $3,2 * 10^{19}$ . Nimmt man nicht biogene Aminosäuren hinzu, was z.B. für die Suche nach Katalysatoren sinnvoll sein könnte, kann diese Zahl im Prinzip beliebig weiter wachsen.

Man sieht, dass für die genannten Anwendungen im Prinzip beliebig große Peptidarrays Anwendung finden könnten. Diese Anwendungen sind daher mit heute verfügbarer Technologie nicht wirtschaftlich realisierbar. Weniger anspruchsvoll sind dagegen die Anwendungen im Bereich des Antikörpernachweises. Hier finden heute bereits Arrays auf Glas- und anderen Trägern Verwendung. Ein Beispiel ist das PepSTAR Micro-Array der Jerini AG, das immerhin bis zu 30.000 Peptide auf einem Träger anbieten kann [MÜL04-2].

$<sup>^{1}</sup>$  ein Kopplungsschritt zwischen der ersten Aminosäure und dem Substrat und n - 1 Kopplungsschritte zwischen dem am Substrat wachsenden Peptid und der nächsten Aminosäure

#### 2. Anwendungsspezifische integrierte Schaltungen

#### 2.1 Elektronische Schaltungen im CMOS - Prozess

#### 2.2.1 Einleitung

Elektronische Schaltungen bestehen in der Regel sowohl aus passiven Elementen wie Widerständen, Kondensatoren und Spulen als auch aus aktiven Elementen wie Dioden und Transistoren. Die "klassische" elektronische Schaltung verbindet separat produzierte, so genannte "diskrete Bauteile", entweder mit Kabeln oder aufgelötet auf einer gedruckten Schaltungsplatine (auch bezeichnet als Leiterbahnplatine, Printed Circuit Board, PCB) mit entsprechenden Leiterbahnen.

Eine große Platzersparnis lässt sich beim Aufbau einer elektronischen Schaltung erzielen, wenn viele ihrer Komponenten gemeinsam, in für die Funktion der Schaltung hilfreicher Weise verbunden, auf einem kleinen Träger gefertigt werden. Einen solchen Träger bezeichnet man als elektronischen Mikrochip oder *integrierten Schaltkreis* bzw. *Integrated Circuit (IC)*. Die Kantenlänge dieser Chips liegt meist im Bereich von wenigen Millimetern, doch zum Einbau in eine gedruckte Schaltung werden sie in größere, handliche Gehäuse mit Kontaktstiften verpackt oder auch aufgeklebt.

Ermöglicht wird die Integrierte Schaltung durch die Verwendung eines Halbleitersubstrats, auf dem im so genannten CMOS – Prozess Dotierungen eingebracht und Strukturen aufgebracht werden. Besonders Feldeffekttransistoren, aber auch Widerstände, Kapazitäten und bipolare Transistoren können so auf kleinstem Raum miteinander zu elektronischen Schaltungen verbunden werden.

Die Abkürzung CMOS steht für *Complementary Metal-Oxide-Semiconductor*, also einen Prozess, der sowohl NMOS<sup>1</sup>- als auch PMOS<sup>2</sup>-Feldeffekttransistoren auf einem gemeinsamen Substrat zur Verfügung stellen kann. CMOS-Schaltungen bieten bessere Linearität und Kompaktheit sowie deutlich geringere Leistungsaufnahme als Schaltungen, die in Prozessen gefertigt werden, die nur entweder NMOS oder nur PMOS zur Verfügung stellen. Während diese einfachen Prozesse ausreichend waren für viele diskrete Halbleiterbauelemente, wurden andere Anwendungen – wie z.B. moderne Mikroprozessoren in PCs (bei Intel z.B. ab dem 80386-Prozessor) – erst durch die CMOS-Technologie ermöglicht. Bei heute möglichen Strukturgrößen von 90 Nanometern und weniger<sup>3</sup> werden so zum Beispiel in modernen Mikroprozessoren oder Speicherchips Schaltungen mit über 4\*10<sup>8</sup> Transistoren (z.B. Intel Itanium 2 – Prozessorfamilie) auf einem Chip realisiert [INT].

<sup>&</sup>lt;sup>1</sup> NMOS: Negative Conducting Channel Metal Oxide Semiconductor, Feldeffekttransistor: Gate durch Oxid vom Halbleiter getrennt, mit mehrheitlich negativen Ladungsträgern im Kanal

<sup>&</sup>lt;sup>2</sup> PMOS: Positive Conducting Channel Metal Oxide Semiconductor, Feldeffekttransistor: Gate durch Oxid vom Halbleiter getrennt, mit mehrheitlich positiven Ladungsträgern im Kanal

<sup>&</sup>lt;sup>3</sup> Als typische Strukturgröße wird in der Halbleitertechnik die Gatebreite verwendet. Die Dicke der Gateoxidschicht ist üblicherweise noch sehr viel geringer als die Gatebreite und liegt bei kleinen Strukturgrößen inzwischen im Bereich weniger Atomlagen.

Man kann integrierte Schaltungen nach ihrer Funktionalität in verschiedene Gruppen unterteilen:

- Allgemein verwendbare Schaltungen. Diese beinhalten einzelne diskrete Bauteile oder logische Gatter, wie zum Beispiel vier separat kontaktierte AND-Gatter auf dem 74HC03-Chip. Solche Chips werden fast wie diskrete Bauteile benutzt. In diese Kategorie fallen aber auch Operationsverstärker oder Analog-Digital-Wandler und auch komplexere Universal-Chips wie Prozessoren, Speicher und *FPGA*s<sup>1</sup>.

- Anwendungsspezifische integrierte Schaltungen (Application Specific Integrated Circuit, oder ASIC). Diese werden speziell für die geplante Anwendung entworfen und können so für ihr Einsatzgebiet ohne Rücksicht auf Flexibilität optimiert werden. Eingesetzt werden sie in vielen Bereichen, zum Beispiel in Triggerschaltungen für die schnelle Auswertung von Experimenten in der Hochenergiephysik oder für speziell optimierte Sensor- oder Steuerchips.

Unterschieden wird auch zwischen rein digitalen Schaltungen, die als Bauelemente nur Transistoren benötigen und die für elektrische Signale nur die zwei Zustände "niedrige Spannung" oder logische 0 und "hohe Spannung" oder logische 1 kennen und analogen Schaltungen, bei denen der exakte Wert der anliegenden Spannung verarbeitet wird. Beispiele für digitale Schaltungen sind Rechenwerke, Prozessoren, FPGAs und Speicher, während Operationsverstärker typische analoge Bauelemente sind. Darüber hinaus gibt es integrierte Schaltungen, die analoge und digitale Signale vereinen, so genannte Mixed-Signal-Schaltungen. Wichtigstes Beispiel sind hier die Analog-Digital- und Digital-Analog-Wandler, die Signale von analoger zu digitaler Darstellung, bzw. umgekehrt, umwandeln.

Im folgenden Abschnitt 2.1.2 wird zunächst auf den MOSFET, das grundlegende Bauelemet der CMOS-Technologie eingegangen und sein Aufbau und Verhalten beschrieben. In den Abschnitten 2.2 und 2.3 wird auf die für diese Arbeit wichtigen Möglichkeiten der Erweiterung des CMOS-Prozesses für die Integration von elektronischen Komponenten mit hohen Schaltspannungen und auf die optischen Eigenschaften des CMOS-Prozesses eingegangen.

#### 2.1.2 Der MOSFET: Aufbau und Verhalten

Der MOSFET als zentrales Element des CMOS-Prozesses verdient besondere Beachtung. Sowohl NMOS- als auch PMOS-Transistoren werden im CMOS-Prozess aufgebaut aus

• nahe der Oberfläche des *Substrats*<sup>2</sup> eingebrachten verschieden *dotierten*<sup>3</sup> Halbleiterbereichen und

<sup>2</sup> Als Substrat bezeichnet man das Stück defektarmer Halbleiterkristall von etwa 1mm Dicke, das als Ausgangsmaterial für die folgenden Prozessschritte dient.

<sup>&</sup>lt;sup>1</sup> Field-Programable Gate Array, etwa: programmierbares Feld von logischen Gattern

<sup>&</sup>lt;sup>3</sup> Als Dotierung bezeichnet man lokal eingebrachte Fremdatome in der regelmäßigen Struktur des Substrats. Im Falle von p-Dotierung wird dadurch ein lokaler Überschuss an positiven Ladungsträgern erzeugt, im Falle von n-Dotierung entsteht lokal ein Überschuss an negativen Ladungsträgern. Dotierungen können für verschiedene Zwecke verschiedene Tiefen im Substrat und verschiedene Dotierungsstärken (also verschiedene Fremdatomdichten, im Bereich zwischen 10<sup>10</sup>cm<sup>-3</sup> und 10<sup>19</sup>cm<sup>-3</sup>) aufweisen.

• auf dem Substrat aufgetragene Strukturen aus Metall, polykristallinem Silizium und Siliziumoxid mit Schichtdicken im Bereich 1µm bis 10nm.

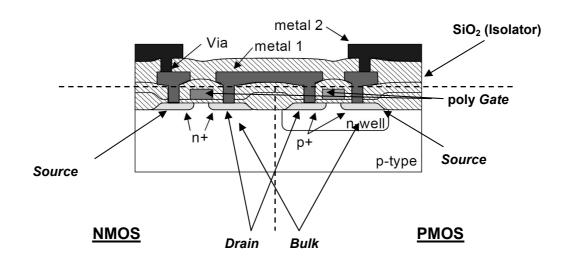

Abb. 2.1 zeigt NMOS- und PMOS-Transistor im Querschnitt für einen CMOS-Prozess mit p-dotiertem Substrat.

**Abb. 2.1:** Aufbau von NMOS und PMOS im p-Substrat-CMOS-Prozess. Über den Transistoren sind in zwei Metalllagen verbindende Leiterbahnen (Interconnect) dargestellt. Die schützende *Passivierung* über der obersten Metalllage ist nicht dargestellt. Die stark dotierten Bereiche (mit n+ bzw. p+ bezeichnet) stellen Drain- und Sourcekontakte der MOSFETs dar, das Gate aus polykristallinem Silizium ist mit poly bezeichet. Das mit p-type bezeichnete Substrat und der n-well (n-Wanne) sind schwach dotiert. (Entnommen aus [LIN04])

Ein Feldeffekttransistor verfügt über vier Kontakte:

- Der Eingang des Transistors, über dessen Potential der Stromfluss zwischen Drain und Source gesteuert werden kann, wird als *Gate* bezeichnet. Durch das Gate kann im Gegensatz zur Basis eines bipolaren Transistors in guter Näherung kein Strom fließen.

- Drain und Source sind die beiden Kontakte durch die in einem leitenden Transistor ein Strom fließt. Niederspannungstransistoren sind oft in ihrem Aufbau symmetrisch gegen eine Vertauschung von Drain und Source. Man bezeichnet dann als Source den Kontakt des Transistors, der näher an der zu dem Transistor gehörenden Versorgungsspannung liegt. Beim NMOS ist dies die niedere Versorgungsspannung Ground (in der Regel 0V), beim PMOS die hohe Versorgungsspannung V<sub>dd</sub>. Der Drain kann dann als Ausgang des Transistors betrachtet werden.

- Bulk ist die Bezeichnung für das Substrat oder die Wanne, in dem der Transistor liegt. Das

p-Substrat liegt immer auf Ground, n-Wannen meist auf Vdd oder auf dem Potential, das

an der Source der PMOS-Transistoren in der Wanne anliegt. Das Bulkpotential hat einen

Einfluss auf die analogen Eigenschaften des Transistors. Für digitale Anwendungen

werden Bulk und Source kurzgeschlossen und als ein Kontakt betrachtet.

Ein Feldeffekttransistor wird zwischen Drain und Source leitend für einen Strom  $I_D$ , wenn die Spannung zwischen Gate und Source  $V_{GS}$  die *Thresholdspannung* (Schwellenspannung,  $V_{th}$ ) überschreitet. Für einen Prozess mit  $V_{dd}$ =5V liegt die Schwellenspannung für den NMOS meist bei etwa 0,9V, für den PMOS bei etwa -0,9V. Das bedeutet, dass der NMOS für

Gatespannungen  $V_{GS}$  zwischen 0V und  $V_{th,NMOS}$  in Näherung nicht leitend ist und bei höheren Gatespannungen dann leitend wird. Der PMOS ist ebenfalls für Spannungen zwischen Gate und Source von 0V bis  $V_{th,PMOS}$  nichtleitend und wird leitend für  $V_{GS} < V_{th,PMOS}$ .

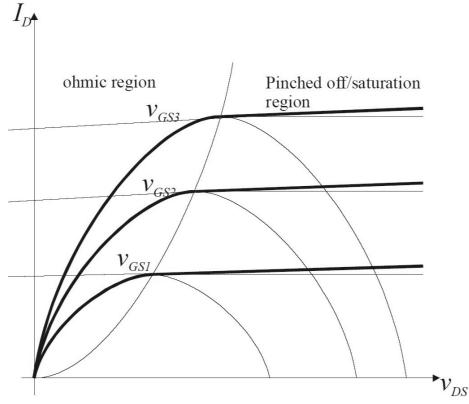

Im Detail wird das Verhalten des MOSFETs durch die Sah-Gleichung (F2.1) beschrieben. In Abb. 2.2 ist diese Gleichung für verschiedene  $V_{GS}$  grafisch dargestellt.

$$I_{D} \approx 0$$

$$f \text{ iii } V_{DS} < V_{T}$$

(Subthresholdbereich)

$$I_{D} = \frac{K'W}{2L} \Big[ 2(V_{GS} - V_{T})V_{DS} - V_{DS}^{2} \Big]$$

$$f \text{ iii } V_{DS} \ge V_{T} \text{ und } V_{DS} \le V_{GS} - V_{T}$$

(ohmscher Bereich)

$$I_{D} = \frac{K'W}{2L} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})$$

$$f \text{ iii } V_{DS} > V_{GS} - V_{T}$$

(Sättigungsbereich)

$$(F2.1)$$

mit

W = Breite des Gates

L =Länge des Gates

*K*'= Transkonduktanzparameter, Produkt aus Ladungsträgermobilität und Kapazität zwischen Gate und Kanal

$\lambda$  = Kanallängenparameter, prozessabhängig

**Abb. 2.2:** Grafische Darstellung der Sahgleichung. Im ohmschen Bereich (ohmic region) steigt der Strom durch den Drain mit der Drain-Source-Spannung. Im Sättigungsbereich nimmt der Strom bei zunehmender Spannung nur noch sehr wenig zu. (Entnommen aus [LIN04])

$<sup>^{1}</sup>$  Man beachte hierbei, dass  $V_{th,PMOS}$  negativ ist.  $V_{GS}$  ist beim PMOS auch meist negativ.

Für die theoretische Untersuchung des Halbleiterübergangs, die Herleitung der Sah-Gleichung, eine genauere Betrachtung parasitärer Effekte im MOSFET, für die Beschreibung weiterer in CMOS-Technologie realisierbarer analoger Bauteile und für den genauen Herstellungsprozess von elektronischen Bauteilen in integrierten Schaltungen wird auf die existierende Literatur verwiesen [LIN04, DEM96-1, GRA01, JOH97].

#### 2.2 CMOS und hohe Spannungen

#### 2.2.1 Einleitung

Die für integrierte Schaltungen in CMOS üblichen Betriebsspannungen variieren stark; im Bereich von 0,9V und weniger bis zu über 100V. Die maximal erreichbare Spannung hängt dabei stark von der Strukturgröße und den Dotierungen ab.

Der Trend geht in der Halbleiterindustrie schon immer hin zu kleineren Strukturgrößen, die höhere Integrationsdichten und schnellere Schaltungen ermöglichen. Im Allgemeinen nimmt die Betriebsspannung mit kleineren Strukturgrößen ab. Ein Grund hierfür ist, dass bei Veränderung der Strukturgröße näherungsweise mit konstantem elektrischem Feld skaliert wird. Die Strukturgröße und damit auch die Dicke des Gateoxids sinkt. Um das Feld im Kanal und im Gateoxid konstant zu halten und Durchbruch des Gateoxids zu verhindern, muss dann die Gatespannung und somit die Betriebsspannung sinken. Ein anderer Grund, die Betriebsspannung zu verringern, ist die Minimierung des Stromflusses und damit der entstehenden Wärme.

Als "hohe Spannungen" werden in diesem Zusammenhang alle Spannungen bezeichnet, die deutlich über der für die Strukturgröße des Prozesses üblichen Schaltspannung liegen.

Da für viele Anwendungen, wie z.B. die Ansteuerung von Motoren, Anzeigegeräten oder mikroelektromechanischen Systemen sowie verschiedene Audio- und Automobilanwendungen hohe Spannungen geschaltet werden müssen, bieten viele CMOS-Prozesse Erweiterungen, die zumindest NMOS-Transistoren oder PMOS-Transistoren für Drain-Source-Spannungen von bis zu 30V bereitstellen. Einige Prozesse wurden auch umfassend zu *Hochspannungsprozessen*<sup>1</sup> erweitert und stellen PMOS und NMOS – Transistoren für verschiedene hohe Spannungen deutlich über 5V zur Verfügung.

In aktuellen *Deep Submicron*<sup>2</sup> – Prozessen mit Betriebsspannungen von 0,9 bis 1,3V werden zudem für die Ein- und Ausgabe Spannungen von 3,3V bis 5V benötigt, um mit den gebräuchlichen Schaltungen außerhalb des Chips kommunizieren zu können. In diesen Prozessen sind 3,3V bis 5V hohe Spannungen, und ähnliche Techniken wie in den Hochspannungsprozessen werden verwendet, um diese Spannungen zu schalten.

Im folgenden Abschnitt werden die physikalischen Effekte erläutert, die die Spannung in CMOS – Prozessen limitieren, während das darauf folgende Unterkapitel auf die Möglichkeiten eingeht, diese Begrenzungen zu umgehen.

\_

<sup>&</sup>lt;sup>1</sup> Auch als High-Voltage- oder HV-Prozesse bezeichnet

$<sup>^2</sup>$  Prozesse mit einer Gate-Länge deutlich unter  $1\mu m$ . Heute wird damit der Bereich zwischen  $0.2\mu m$  und 90nm bezeichnet, in dem neue Probleme beim Aufbau der Transistoren erstmals auftreten.

#### 2.2.2 Physikalische Grenzen

#### 2.2.2.1 Abnutzung durch heiße Ladungsträger

In Abhängigkeit von Dotierung und Geometrie begrenzen verschiedene Effekte die maximale Spannung, die an einem Halbleiterbauelement angelegt werden kann. Die erste Gruppe grundlegender Effekte nach [BAL99] ist die Abnutzung durch heiße Ladungsträger.

Als hot carrier oder heiße Ladungsträger werden Elektronen oder Löcher bezeichnet, die im elektrischen Feld auf kinetische Energien  $E_{kin}$  beschleunigt werden. Diese Energien entsprechen nach  $E_{kin}=k_BT_e$  einer effektiven Temperatur  $T_e$ , die viel größer als die Temperatur des Substrats ist. Heiße Ladungsträger entstehen zum Beispiel im Feldeffekttransistor beim Übergang der Ladungsträger vom Kanal in die Drain-Region. Die im Feld des Kanals beschleunigten Elektronen werden in der stark dotierten Drain-Region durch Kollisionen mit dem Siliziumgitter abgebremst (die Effekte der Abbremsung durch Kollisionen mit dem Gitter bereits im Kanal werden in Abschnitt 2.2.2.2 beschrieben). Wenn ihre Energie bei der Kollision mit dem Gitter groß genug ist, um durch Ionisation neue Elektron-Loch-Paare zu erzeugen (in Silizium ab 1,3eV), treten unerwünschte Effekte in Form von zusätzlichen Substratströmen und, falls die Energie hoch genug ist um das Gateoxid zu durchdringen, auch Gateströmen auf. Einige der Ladungsträger dringen in das Gateoxid ein, haben aber nicht genug kinetische Energie um es zu durchdringen, werden darin gefangen und reichern sich dort an. Durch diese zusätzlichen fixierten Ladungsträger ändern sich die Thresholdspannung und andere elektrische Eigenschaften wie die Steilheit des Transistors.

Die Effekte heißer Ladungsträger sind abnutzend, d.h. ein Transistor kann bei entsprechenden Spannungen einige Zeit betrieben werden, bis die Effekte sich so weit akkumuliert haben, dass die ordnungsgemäße Funktion des Transistors gefährdet ist. Je nach Bedingungen tritt dieser Effekt nach unter einer Sekunde bis hin zu mehreren Jahren durchgehenden Betriebs ein.

#### 2.2.2.2 Durchbruchspannungen

Im Gegensatz zu den abnutzenden Effekten heißer Ladungsträger sind die schädigenden Effekte beim Überschreiten der Durchbruchspannung, die zweite Gruppe von Effekten die die schaltbaren Spannungen in Halbleiterbauteilen begrenzt, sofort zerstörend. Vier Arten des Durchbruchs sind zu unterscheiden. Bei dreien davon, Avalance-, Surface- und Snapback Breakdown fließen dabei Ströme durch einen als Diode in Sperrichtung wirkenden Halbleiterübergang, während beim Gate-Oxide Breakdown ein Strom durch ein Isolatormaterial fließt.

#### Avalance Breakdown (lawinenartiger Durchbruch)

Beim Avalance Breakdown erzeugt, wie bei den Effekten heißer Ladungsträger beschrieben, ein Elektron an einem Halbleiterübergang Elektron-Loch-Paare durch Ionisation. Hier jedoch erreichen diese bereits im starken Feld im Kanal im Mittel wieder ausreichend hohe Energien bis zur nächsten Kollision, um ihrerseits neue Ladungsträgerpaare zu erzeugen, die ebenfalls im Feld beschleunigt werden. Der Strom zwischen Drain und Source wächst lawinenartig an, bis thermische Effekte in kürzester Zeit das Bauteil zerstören [BAL99], [BLI81-1].

#### Surface Breakdown (Oberflächendurchbruch)

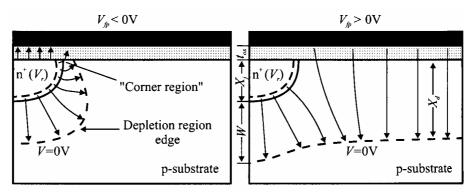

Surface Breakdown ist ein Sonderfall des Avalance Breakdown. Surface Breakdown beschreibt die Eigenschaft des Avalance Breakdown, zuerst im zylindrischen Bereich eines Halbleiterübergangs aufzutreten, da dort aufgrund der Krümmung der Verarmungszone das stärkste Feld vorliegt. Ladungen an der Oberfläche können diesen Effekt abschwächen oder verstärken, indem sie die Krümmung am Rand der Verarmungszone beeinflussen (Abb. 2.3a). Durch die Verlängerung des Transistor-Gates um eine Feldplatte (field plate) (Abb. 2.3b) lässt sich die Krümmung der Verarmungszone verringern. Damit wird der Effekt reduziert und der Transistor wird spannungsfester.

**Abb. 2.3a:** Verlauf der Verarmungszone (Bereich zwischen den gestrichelten Linien) und des elektrischen Feldes (Pfeile) am Rand eines gekrümmten n-p-Übergangs. Links: unter negativ geladener Leiterplatte. (Entnommen aus [BAL99])

**Abb. 2.3b:** Verlauf der Verarmungszone unter unterschiedlich geformten Feldplatten. (Entnommen aus [BAL99])

#### Snapback Breakdown (Durchbruch durch Zurückschnappen)

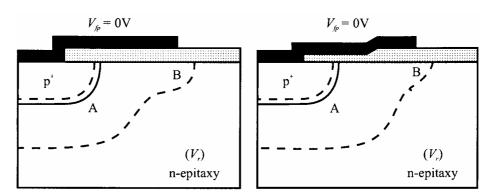

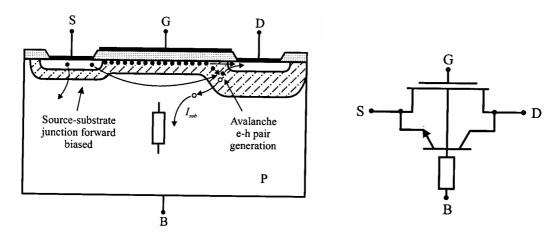

Snapback Breakdown entsteht beim Durchbruch des parasitären bipolaren Transistors parallel zum MOSFET (Abb. 2.2). Voraussetzung dafür ist, dass das Substrat, d.h. die Basis des bipolaren Transistors unter dem MOSFET durch am Drain erzeugte und ins Substrat injizierte Elektron-Loch-Paare auf eine höhere Spannung gehoben wird. Dann wird dieser parasitäre Transistor leitend und große Ströme sorgen für thermische Zerstörung des MOSFETs (Abb. 2.4).

**Abb. 2.4:** Links: Querschnitt eines MOSFETs beim Snapback Breakdown. Rechts entstehen Lawinen aus Elektron-Loch-Paaren. Rechts: Zugehörige Schaltskizze des MOSFETs mit parallelem bipolaren Transistor. (Entnommen aus [BAL99])

#### Gate-Oxide Breakdown (Durchbruch des Gateoxids)

Defektfreies Siliziumoxid kann elektrischen Feldern bis 12 MV/cm widerstehen; Defekte senken je nach ihrer Ausprägung diese maximale Feldstärke. Wird diese Feldstärke überschritten, führt dies zu einem Stromfluss durch das Oxid und zu dessen Zerstörung. Gateoxiddicken in CMOS-Prozessen liegen im Bereich einiger zehn Nanometer und sind üblicherweise so gewählt, dass sie gerade ausreichen, um die Betriebsspannung des Prozesses sicher schalten zu können. Bei einer Betriebsspannung von 4,5 bis 5,5 Volt wird zum Beispiel üblicherweise eine Spannungsfestigkeit des Gateoxids bis 7,0 Volt garantiert. Typische Gateoxiddicken liegen in solchen Prozessen im Bereich von 10nm bis 20nm.

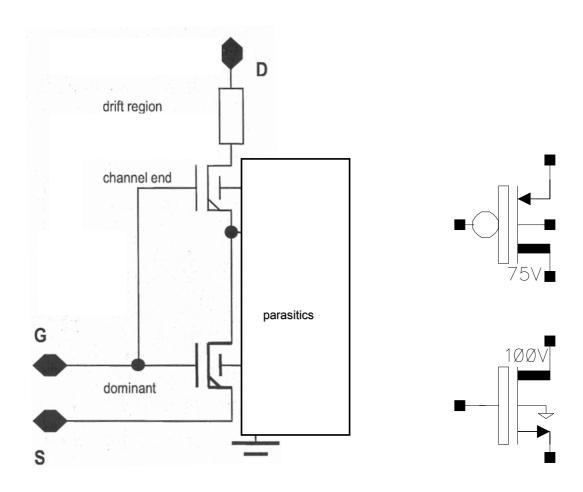

#### 2.2.3 Elektronik

#### 2.2.3.1 HV-Prozesstechnologie und HV-MOSFETs

Viele Möglichkeiten, die Probleme beim Betrieb von MOSFETs unter hohen Spannungen zu umgehen, wurden gefunden. Hochspannungstaugliche Transistoren, basierend auf verschiedenen Prinzipien, stehen in CMOS-Prozessen zur Verfügung [BAL99].

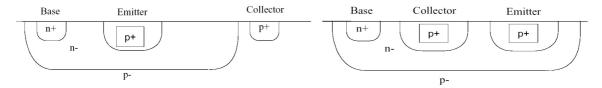

#### Bipolare Transistoren

In jedem CMOS – Prozess ist es prinzipiell auch möglich, bipolare Transistoren zu realisieren. Dabei werden die unterschiedlich dotierten Halbleiterzonen von Diffusion, Wanne und teilweise Substrat wie in Abb.2.5 gezeigt angeordnet. Diese Strukturen weisen die nötigen Halbleiterübergänge auf [LIN04]. Allerdings ist im unmodifizierten CMOS – Prozess immer nur ein Typ bipolarer Transistor mit den möglichen Anordnungen der Dotierungsregionen sinnvoll möglich. Für n-Well – CMOS-Prozesse ist das der PNP-Transistor.

**Abb 2.5:** Bipolare PNP-Transistoren im n-Well - CMOS-Prozess. Links: vertikaler PNP, rechts: lateraler PNP. (Entnommen aus [LIN04])

Die Abwesenheit eines Gates und damit von Gateoxid löst die Probleme des Gateoxiddurchbruchs und der abnutzenden Effekte am Gate. Auch Snapback Breakdown kann so nicht auftreten. Avalance Breakdown und Surface Breakdown betreffen jedoch bipolare Transistoren in ähnlicher Weise wie MOSFETs. Ähnliche Gegenmaßnahmen wie für Hochspannungs-MOSFETs (beschrieben weiter unten) sind bipolare Hochspannungstransistoren nötig. Zusätzlich ist in der Regel unerwünscht, dass im eingeschalteten Zustand durch die Basis des bipolaren Transistors immer ein nicht vernachlässigbarer Strom fließen muss. Überdies ist der Platzbedarf eines bipolaren Hochspannungstransistors in der Regel größer als der eines vergleichbaren Hochspannungs-MOSFETs. Auch die Schaltgeschwindigkeit eines hochspannungstauglichen bipolaren Transistors ist geringer als die eines vergleichbaren MOSFETs. Diese Umstände motivierten die Entwicklung von verschiedenen Hochspannungs-MOSFETs.

Vermeidung der lawinenartigen Ladungsträgergeneration in Hochspannungs-MOSFETs Im elektrischen Feld des Kanals im MOSFET bewegen sich elektrische Ladungsträger mit der  $Driftgeschwindigkeit\ v_d$ , die sich aus der Ladungsträgermobilität im Festkörper  $\mu$  und der elektrischen Feldstärke E errechnet zu:

$$v_d = \mu * E \quad \text{mit} \quad E = V/d \tag{F2.2}$$

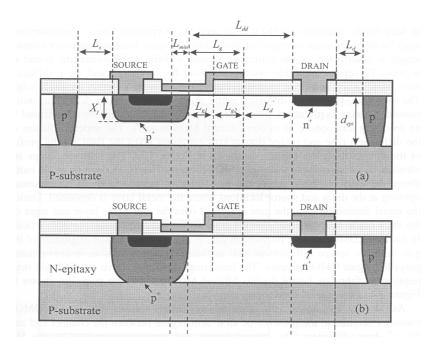

Die elektrische Feldstärke hängt wiederum für die Näherung des konstanten elektrischen Feldes von der anliegenden Spannung V und dem Abstand d ab. Die Idee liegt nahe, das elektrische Feld und damit die Driftgeschwindigkeit zu senken, indem man einfach den Abstand zwischen Drain und Source vergrößert. Dies ist jedoch nicht ausreichend, da das elektrische Feld beim MOSFET in Sättigung nicht konstant ist. Im  $pinch-off^d$  Bereich ist der elektrische Widerstand und damit die Spannungsdifferenz und das elektrische Feld viel größer als im restlichen Kanal. Eine andere Lösung muss also gefunden werden.

Eine solche Lösung ist die Verwendung eines schwach dotierten Drainbereiches oder Lightly Doped Drain (LDD) als Driftregion, die im Folgenden für den Fall des NMOS diskutiert werden soll. In einem gewöhnlichen Hochspannungstransistor wird für den Kanal schwach positiv dotiertes Silizium verwendet, für die Drain- und Sourcekontakte stark negativ dotiertes Silizium. Die Verarmungszone ist somit eher klein. Bringt man am Drain zwischen den stark negativ dotierten Bereich und den schwach positiv dotierten Bereich einen zusätzlichen schwach negativ dotierten Bereich ein, so vergrößert sich die Verarmungszone erheblich. Damit vergrößert sich auch der Bereich hohen Widerstands, die Spannung fällt über einen größeren Bereich ab und das elektrische Feld wird geringer.

Als zusätzliche Maßnahme kann der schwach dotierte Bereich zwischen Drainkontakt und Kanal vergrößert werden. Dieser Bereich dient dann als mit dem MOSFET in Serie geschalteter Widerstand, der die Spannung über dem Kanal weiter reduziert. Allerdings erhöht diese Vorgehensweise auch den Widerstand des MOSFETs im eingeschalteten Zustand. Da sich über diesem Bereich Feldoxid befindet und das Gate erst im Bereich der Verarmungszone beginnt, erhöht diese Technik auch die maximal mögliche Gate-Drain-Spannung, aber nicht die maximale Gate-Source-Spannung.

<sup>&</sup>lt;sup>1</sup> Als pinch-off region oder Abschnürungsbereich bezeichnet man bei einem MOSFET in Sättigung den kleinen Bereich nahe dem Drain, in dem der Kanal vom elektrischen Feld zwischen Drain und Source von der Verarmungszone abgeschnürt wird, d.h. der Kanal wird von Source zu Drain schmaler.

Man kann dann die über dem MOSFET abfallende Spannung  $V_{ds}$  unterteilen in:

$$V_{ds} = V_R + V_{depl} + V_{Ch}$$

mit

$$V_R = \text{Spannungsabfall am Widerstand (schwach dotierter Bereich)}$$

$$V_{depl} = \text{Spannungsabfall in der Verarmungszone}$$

(F2.3)

$V_{Ch}$  = Spannungsabfall am Kanal

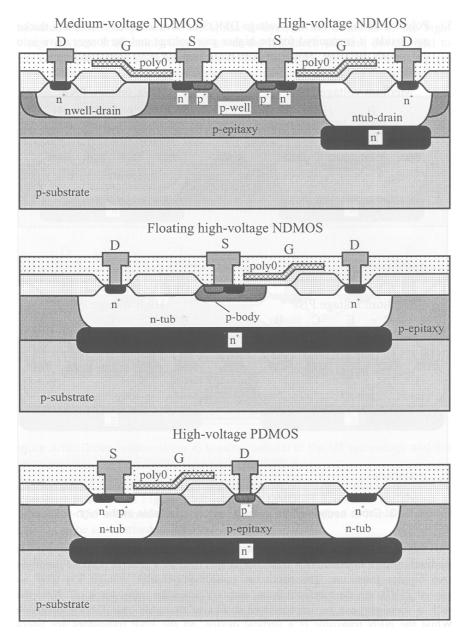

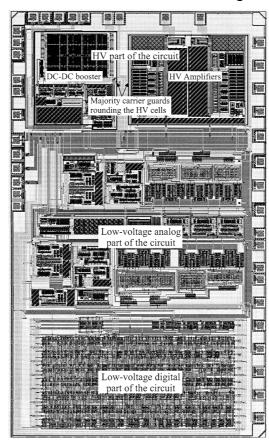

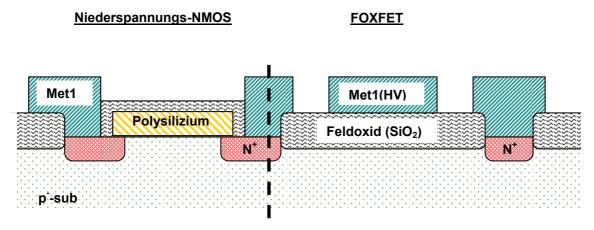

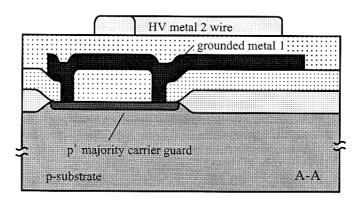

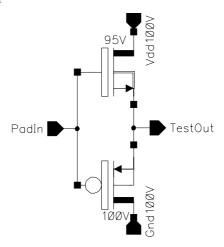

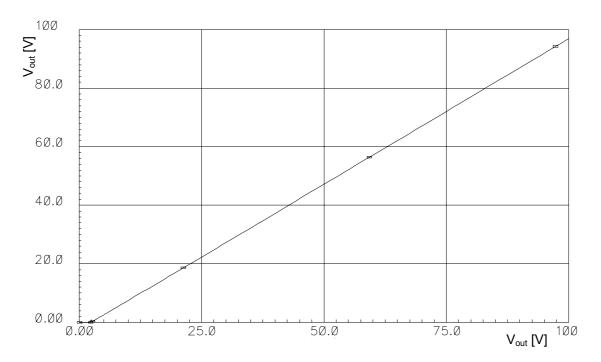

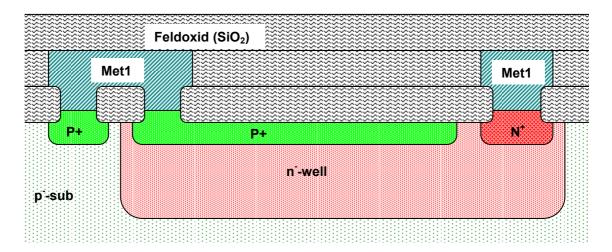

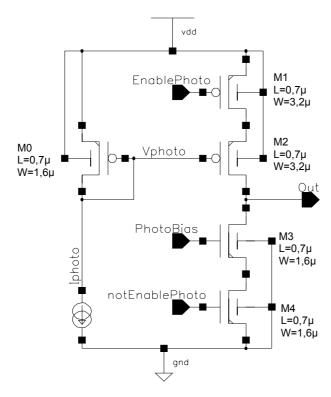

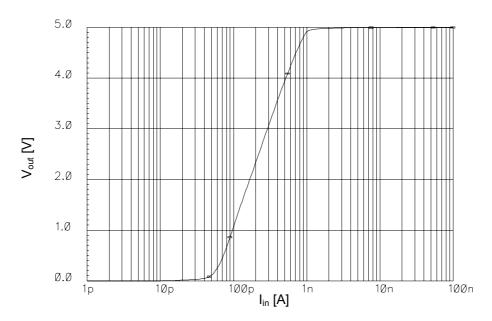

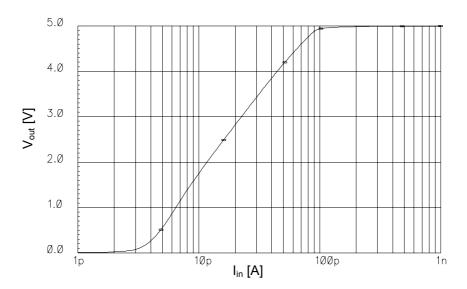

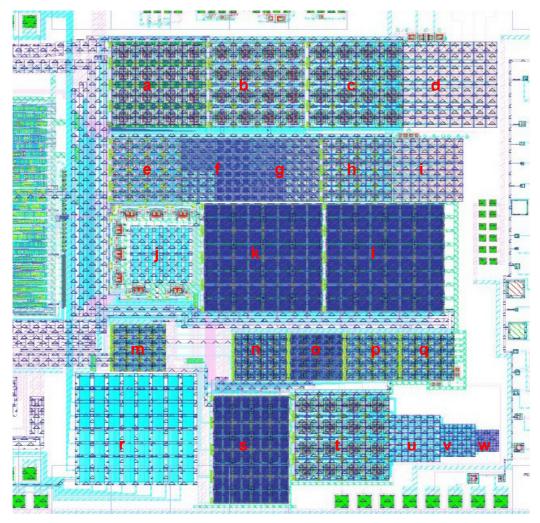

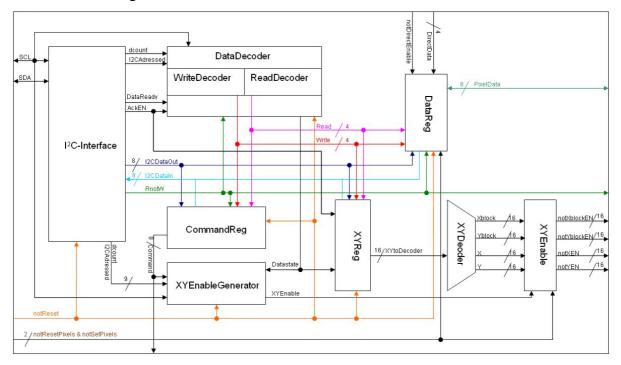

MOSFETs mit schwach dotiertem Drain und ähnlichen Techniken werden als *DMOS* bezeichnet, diese Abkürzung steht für *Double-diffused MOSFET*. Der Begriff ist abgeleitet von der Tatsache, dass der Drain des MOSFETs über zwei verschiedene Diffusionsbereiche, nämlich den hoch dotierten Drainkontakt und den schwach dotierten LDD-Bereich verfügt. DMOS ist die dominante Technologie bei der Herstellung von Hochspannungs-MOSFETs.